(54) ЦИФРОВОЙ ПРОПОРЦИОНАЛЬНО-ИНТЕГРАЛЬНОИзобретение относится к автомд1ти зированным системс1м регулирования с цифровым управлением и может найти применение в системах регулирования частоты вращения и положения, различ ных механизмов. Известен цифровой пропорционально-интегрально-дифференциальный регулятор (ПИД-регулятор) , содержащий реверсивные счетчики, сумматоры,запоминающие устройства, блок управления, схемы совпадения и переполнения и блок знака Cll. Недостатками известного регулятора являются сложность и низкое быстродействие. Наиболее близким к предлагаемому изобретению по технической сущности является цифровой ПИД-регулятор, содержащий дешифратор, тактовый генератор, управляемый ключ, блок управления, а также первые последовательно соединенные сумматор и регистр, вторые последовательно соеди ненные сумматор и регистр, третьи последовательно соединенные сумматор и регистр и четвертые последова тел1б.но соединенные сумматор и регист причем выход первого сумматора сое динен с первым входом третьего сум ДИФФЕРЕНЦИАЛЬНЫЙ РЕГУЛЯТОР матора, прямой выход первого регистра - с первыми входами второго и четвертого сумматоров, а выходы второго и третьего регистров подключены соответственно к второму и третьему входам четвертого сумматора Г 21. Однако известный регулятор сложен и обладает пониженным быстродействием в связи со. значительным количеством команд в цикле, которые составляют две операции сложения в суммирующем устройстве (14 команд), а на передачу информации и установку счетчиков в нулевое положение затрачивается семь команд. Всего 21 команда. Цель изобретения - повышение быстродействия и упрощение регулятора. Поставленная цель достигается тем, что инверсный выход первого регистра соединен со вторым входом третьего сумматора, вьисод второго регистра подключен к второму входу второго сумматора, вторые входы первого, второго, третьего и четвертого регистров соединены с соответств тощими выходами блока управления, вхсп которого через управляемый ключ подключен к выходу тактового генератора, а выход первого сумматора через дешифратор соединен с управляющим входом ключа.

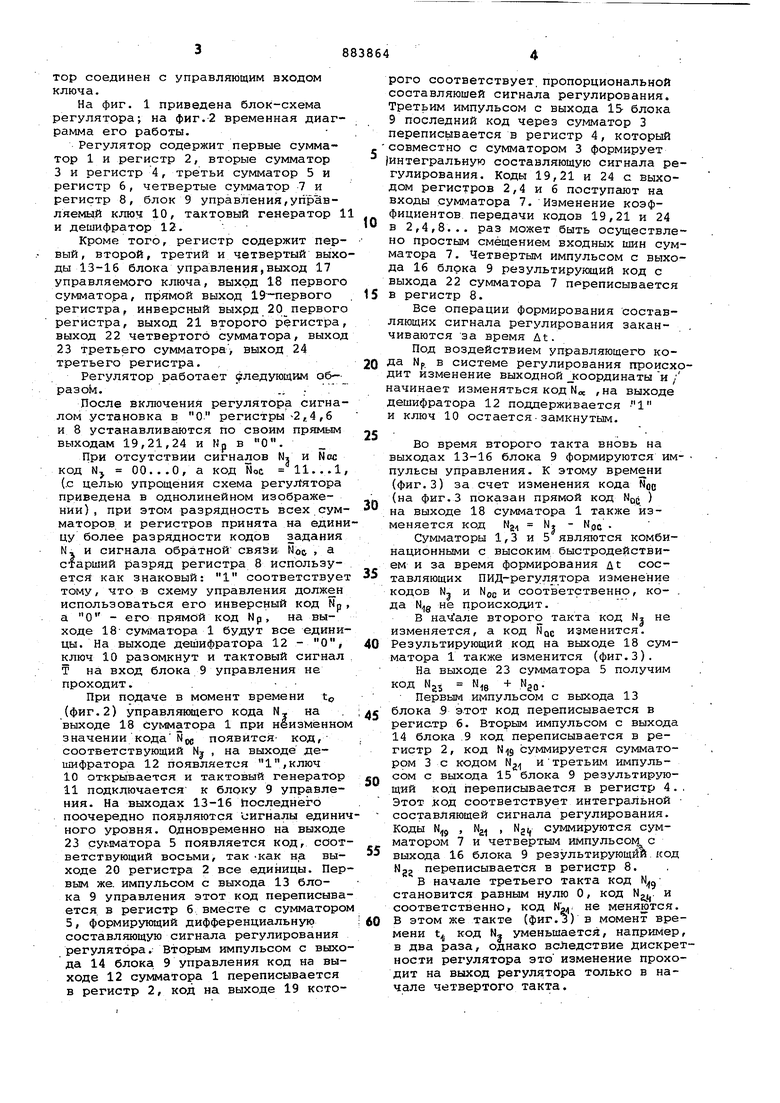

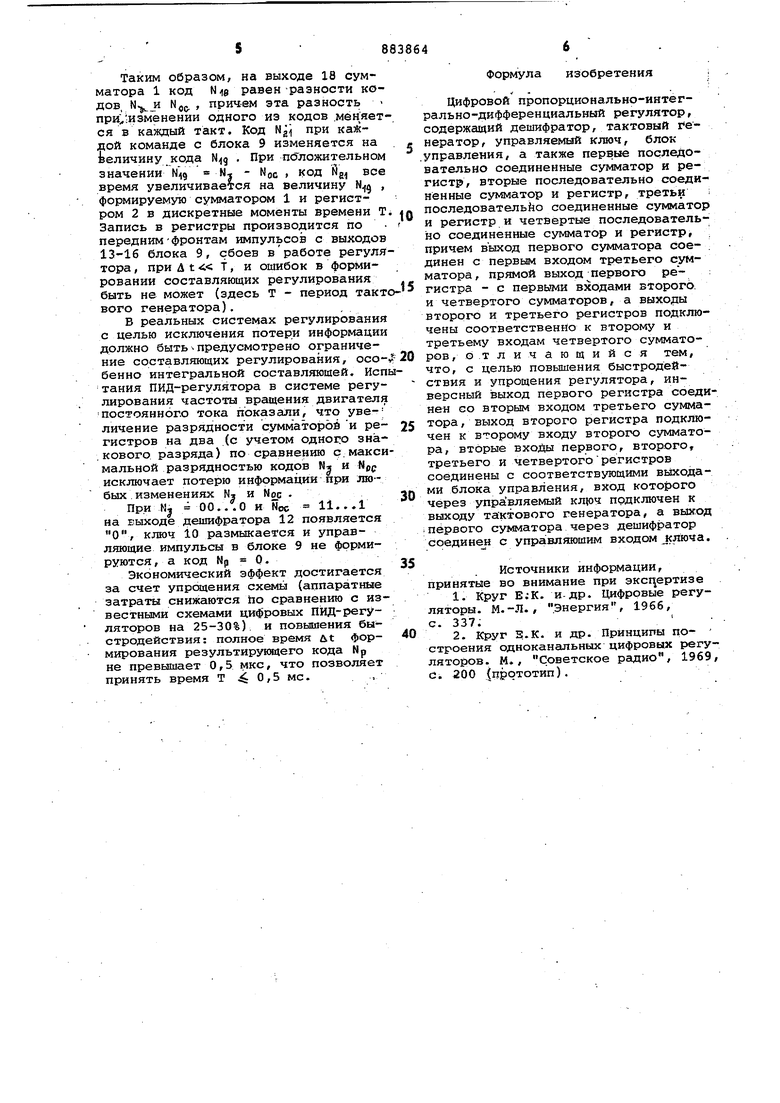

На фиг. 1 приведена блок-схема регулятора; на фиг.2 временная диаграмма его работы.

Регулятор содержит первые сумматор 1 и регистр 2, вторые сумматор 3 и регистр 4, третьи сумматор 5 и регистр 6, четвертые сумматор 7 и регистр 8, блок 9 управления,управляемый ключ 10, тактовый генератор 1 и дешифратор 12.

Кроме того, регистр содержит первый, второй, третий и четвертый выходы 13-16 блока управления,выход 17 управляемого ключа, выход 18 первого сумматора, прямой выход 19-первого регистра, инверсный выхрд 20 первого регистра, выход 21 второго регистра, выход 22 четвертого сумматора, выход 23 третьего сумматора , выход 24 третьего регистра.

Регулятор работает Следующим об- разой. .. ;

После включения регулятора сигналом установка в О регистры2,4 ,6 и 8 устанавливаются по своим прямым выходам 19,21,24 и Np в О.

При отсутствии сигналов N и Ысщ код NJ 00...О, а код Мое 11... 1, (с целью упрощения схема регулятора приведена в однолинейном изображении) , при этом разрядность всех сумматоров и регистров принята на единицу более разрядности кодов задания N, и сигнала обратной связи NOU , а старший разряд регистра 8 используется как знаковый: 1 соответствует тому, что в схему управления должен использоваться его инверсный код Np, а О - его прямой код Np, на выходе 18 сумматора 1 будут все единицы. На выходе дешифратора 12 - О, ключ 10 разомкнут и тактовый сигнал Т на вход блока 9 управления не проходит. .

При подаче в момент времени t, (фиг.2) управляквдего кода N, на . выходе 18 сумматора 1 при неизменном значении кодаЫ появится- код, соответствующий Nj , на выходе дешифратора 12 появляется 1,ключ

10открывается и тактовый генератор

11подключается к блоку 9 управления. На выходах 13-16 последнего поочередно появляются сигналы единичного уровня. Одновременно на выходе 23 сумматора 5 появляется код, соответствующий восьми, так -как на выходе 20 регистра 2 все единицы. Первым же. импульсом с выхода 13 блока 9 управления этот код переписывается в регистр 6 вместе с сумматором 5, формирующий дифференциальную составляющую сигнала регулирования регулятора. Вторым импульсом с выхода 14 блока 9 управления код на выходе 12 сумматора 1 переписывается

в регистр 2, код на выходе 19 которого соответствует, пропорциональной составляющей сигнала регулирования. Третьим импульсом с выхода IS блока 9 последний код через сугФ1атор 3 переписывается в регистр 4, который совместно с сумматором 3 формирует интегральную составляющую сигнала регулирования. Коды 19,21 и 24 с выходом регистров 2,4 и 6 поступают на входы сумматора 7.Изменение коэффициентов передачи кодов 19,21 и 24 в 2,4,8... раз может быть осуществлено простым смещением входных шин сумматора 7. Четвертым импульсом с выхода 16 блока 9 результирукядий код с выхода 22 сумматора 7 переписывается в регистр 8.

Все операции формирования составяющих сигнала регулирования заканчиваются за время At.

Под воздействием управляющего коа NP в системе регулирования происхоит изменение выходной координаты и / ачинает изменяться кодIjoc ,на выходе ешифратора 12 поддерживается ключ 10 остается-замкнутым.

Во время второго такта вновь на выходах 13-16 блока 9 формируются им- пульсы управления. К этому времени (фиг.З) за счет изменения кода HOC (на фиг.З показан прямой код NQJ ) на выходе 18 сумматора 1 также изменяется код Nj;, N, - NO(. .

Сумматоры 1,3 и 5 являются комбинационными с высоким быстродействием и за время формирования At составляющих ПИД-регулятора изменение кодов NJ и NOC и соответственно, ко- . да не происходит.

В начале второго такта код Nj не изменяется, а код NQ изменится. Результирующий код на выходе 18 сумматора 1 также изменится (фиг.З).

На выходе 23 сумматора 5 получим

код Nj5 NIB + 30

Первым импульсом с выхода 13 блока .9 этот код переписывается в регистр 6. Вторым импульсом с выхода 14 блока 9 код переписывается в регистр 2, код Ni9 суммируется сумматором 3 с кодом Nj итретьим импульсом с выхода 15 блока 9 результирующий код переписывается в регистр 4.. Этот код соответствует интегральной составляющей сигнала регулирования. Коды , Nj , Nji, суммируются сумматором 7 и четвертым импyльco l с выхода 16 блока 9 результирующий код

переписывается в регистр 8.

гг

в начале третьего такта код N становится равным нулю О, код Ну. и соответственно, код Ng,,. не меняются. В этом же такте (фиг.З) в момент времени t код N, уменьшается, например, в два раза, однако вследствие дискретности регулятора это изменение проходит на выход регулятора только в начале четвертого такта.

Таким образом, на выходе 18 сумматора 1 код NIB равен-разности кодов, N55. , прич-ем эта разность при;,:ИЗменении одного из кодов .мен яется в каждый такт. Код Nji при каждой команде с блока 9 изменяется на величину кода . При псУложительном значении Щд N, - NOC i код Ng, все время увеличивается на величину N , формируемую сумматором 1 и регистром 2 в дискретные моменты времени Т Запись в регистры производится по передним фронтам импульсозз с выходов 13-16 блока 9, сбоев вработе регулятора , при Д t« Т, и ошибок в формировании составляющих регулирования быть не может (здесь Т - период такт вого генератора).

В реальных системах регулирования с целью исключения потери информации должно быть предусмотрено ограничение составляющих регулирования, особенно интегрсшьной составляющей. Испытания ПИД-регулятора в системе регулирования частоты вращения двигателя постоянного тока показали, что уве-личение разрядности сумматорой и регистров на два (с учетом одного знакового разряда) по сравнению р.максимальной разрядностью кодов Nj и NOC исключает потерю информации при любых изменениях N, и NOC .

При К| 00...О и NOC 11.. на выходе дешифратора 12 появляется О, ключ 10 размыкается и управляющие импульсы в блоке 9 не формируются , а код Np О.

Экономический эффект достигается за счет упрощения схемы (аппаратные затраты снижаются ho сравнению с известными схемами цифровых ПЙД-регуляторов на 25-30%): и повьошения быстродействия: полное время ut формирования результируквдего кода Нр не превышает 0,5 мкс, что позволяет принять время Т 0,5 мс. .

Формула изобретения

Цифровой пропорционально-интегрально-дифференциальный регулятор, содержащий дешифратор, тактовый генератор, управляемый ключ, блок .управления, а также первые последовательно соединенные сумматор и регистр, вторые последовательно соединенные сумматор и регистр, третьи последовательйо соединенные сумматор и регистр и четвертые последовательно соединенные сумматор и регистр, причем выход первого сумматора соединен с первым входом третьего сумматора, прямой выход первогчэ регистра - с первыми входами второго, и четвертого сумматоров, а выходы второго и третьего регистров подключены соответственно к второму и третьему входам четвертого сумматоров, отличающийся тем, что, с целью повышения быстродействия и упрощения регулятора, инверсный выход первого регистра соединен со BTOpEJM входом третьего сумматора , выход второго регистра подключен к второму входу второго сумматора, вторые входы первого, второго, третьего и четвертого регистров соединены с соответствующими ВБ&содами блока управления, вход которого через управляемый ключ подключен к выходу тактового генератора, а выход первого сумматора через дешифратор соединен с упра вляющим входом ключа.

Источники информации, принятые во внимание при эксг ертизе

1.Круг Е;К. и-др. Цифровые регуляторы. М.-Л., Энергия, 1966,

с. 337.

2.Круг S..K. и др. Принципы построения одноканальных цифровых регуляторов. М., Советское радио, 1969 с. 200 {прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой пропорционально-интегрально-дифференциальный регулятор | 1984 |

|

SU1223206A2 |

| Преобразователь частота - код | 1987 |

|

SU1511864A1 |

| Цифровой пропорционально-интегрально-дифференциальный регулятор | 1988 |

|

SU1649501A1 |

| ЦИФРОВОЙ РЕГУЛЯТОР | 1992 |

|

RU2036502C1 |

| Цифровой регулятор | 1988 |

|

SU1718183A1 |

| Устройство для обработки радиосигналов | 1980 |

|

SU955083A1 |

| Цифровой вольтметр | 1985 |

|

SU1273825A1 |

| Система адаптивного управления параметром технологического процесса | 1988 |

|

SU1620989A1 |

| УСТРОЙСТВО ДЛЯ РЕГУЛИРОВАНИЯ ДАВЛЕНИЯ | 1992 |

|

RU2072548C1 |

| Цифровой экстраполятор | 1983 |

|

SU1126970A1 |

Авторы

Даты

1981-11-23—Публикация

1979-11-26—Подача