Изобретение относится к вычислительной техн1тое и может быть использовано в быстродействующих аналого-- циФровых вычислительных устройствах и устройствах контрольно-измерительной техники.

Цель изобретения повышение быстродействия.

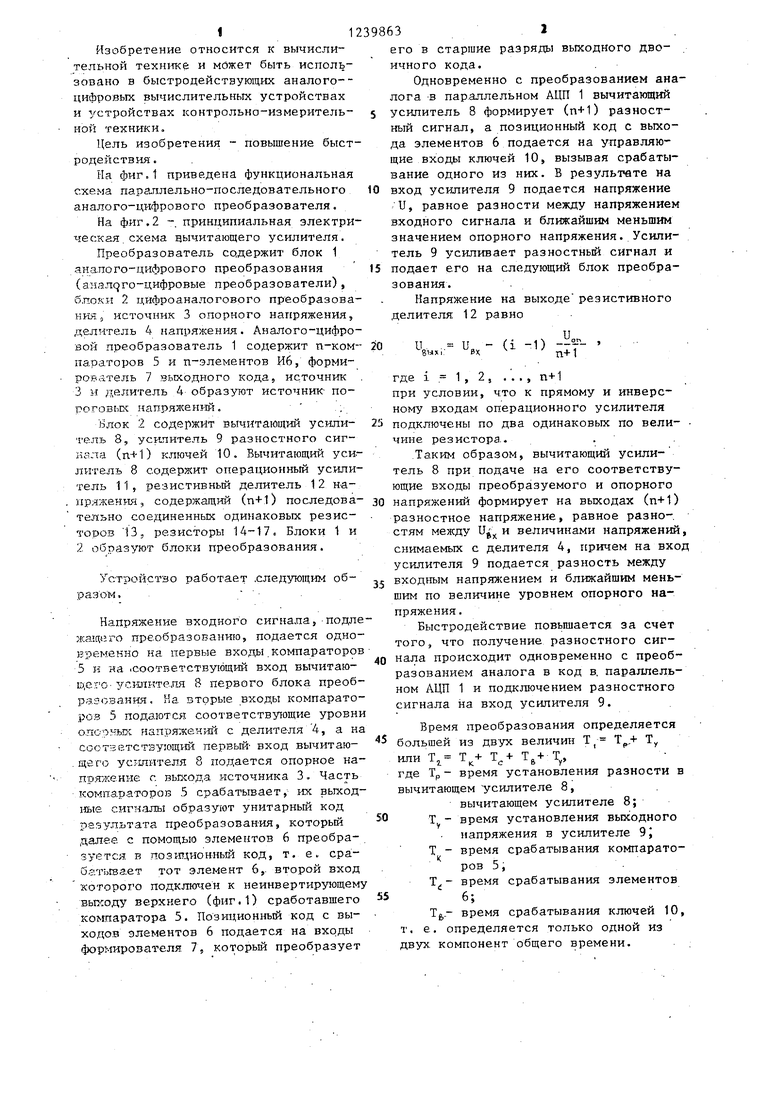

На фиг.1 приведена функциональная схема параплельно-последовательного аналого-цифрового преобразователя.

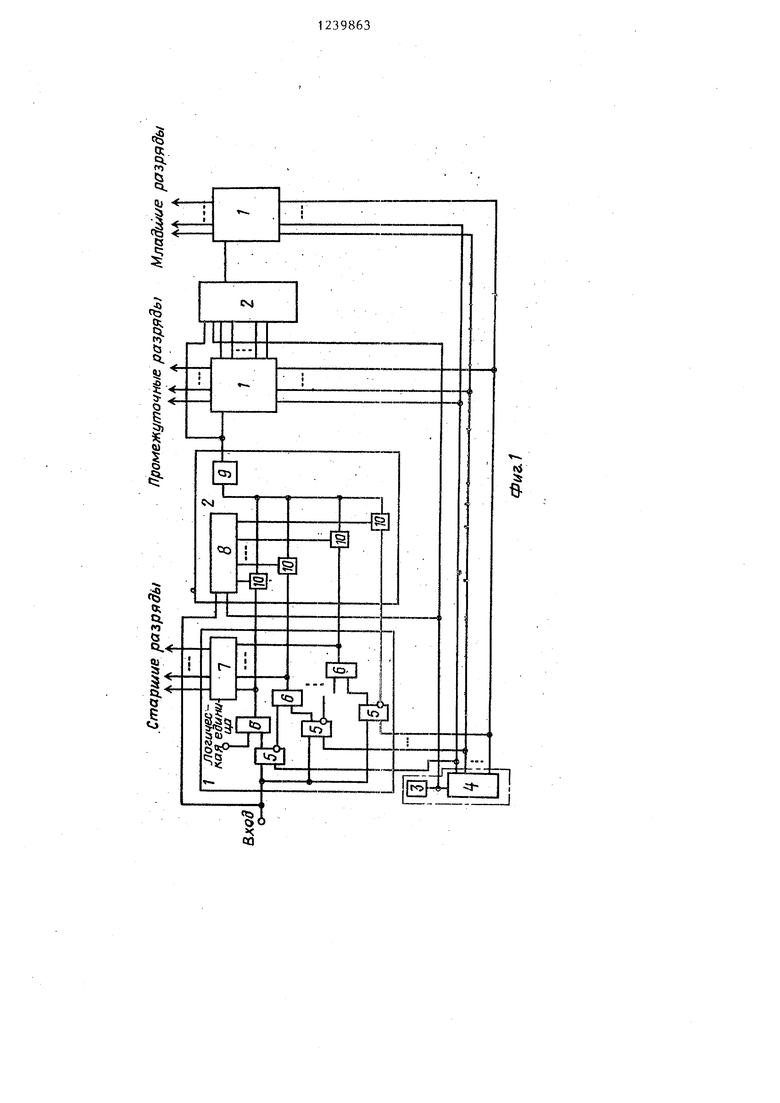

На фиг.2 . принципиальная электрическая, схема вычитающего усилителя.

Преобразователь содержит блок 1 аналого-цифрового преобразования (аналого-цифровые преобразователи), блоки 2 цифроаналоговрго преобразования источник 3 опорного напряжения, делитель 4 напряжения. Аналого-цифровой преобразователь 1 содержит п-ком- параторов 5 и п-элементов И6, формирователь 7 выходного кода, источник 3 и делитель 4 образуют источник- пороговых напрялсен1-1й. ,;

Блок 2 содержит вычитающий усилитель 8, усилитель 9 разностного сиг- кала (n-i-1) ключей 10. Вычитающий усилитель 8 содержит операционный усилитель 11 резистивный делитель 12 напряжения, содержащий (n+l) последовательно соединенных одинаковых резисторов 13, резисторы 14-17. Блоки 1 и 2 образуют блоки преобразования.

Устройство работает .следующим образом.

Напряжение входного сигнала,-подле жз.о;его преобразованию, подается одновременно на первые входы.компараторов 5 и на .соответствующий вход вычитаю- щег О усшткте.гш 8 первого блока преоб- раэования. На вторые входы компараторов 5 подаются соответствующие уровни олорньк напряжений с делителя 4, а на соотзетствующий первый- вход вычитаю- , щего уст-иоттеля 8 подается опорное напряжение с. выхода источника 3. Часть компараторов 5 срабатывает, их выходные сигналы образуют унитарный код результата преобразования, который далее с помощью элементов 6 преобра- зуется в позитдионный код, т. е. срабатывает тот элемент 6,. второй вход которого подключен к неинвертирующему выходу верхнего (фиг.1) сработавшего кo mapaтopa 5. Позиционный код с выходов элементов 6 подается на входы формирователя 7, которьй преобразует

его в старшие разряды выходного двоичного кода.

Одновременно с преобразованием аналога -в пар,аллельном АЦП 1 вычитающий

усилитель 8 формирует (п+1) разностный сигнал, а позиционный код с выхода элементов 6 подается на управляющие входы ключей 10, вызывая срабатывание одного из них. В результате на

вход усилителя 9 подается напряжение

и, равное разности между напряжением входного сигнала и ближайшим меньшим значением опорного напряжения. Усилитель 9 усиливает разностный сигнал и

подает его на следующий блок преобразования. .

Напряжение на выхо.де резистивного делителя 12 равно

%«,Г UBX- (i -1) ТГ

где i . 1 , 2, . . . , п+1 при условии, что к прямому и инверсному входам операционного усилителя

подключены по два одинаковых по вели- - чине резистора...

Таким образом, вычитающий усили- тель 8 при подаче на его соответствующие входы преобразуемого и опорного

напряжений формирует на выходах (п+1) разностное напряжение, равное разностям между и величинами напряжений, снимаемых с делителя 4, причем на вход усилителя 9 подается разность между

вход{гым напряясением и ближайшим меньшим по величине уровнем опорного напряжения.

Быстродействие повышается за счет того, что получение разностного сигнала происходит одновременно с преобразованием аналога в код в, параллельном АЦП 1 и подключением разностного сигнала на вход усилителя 9.

Время преобразования определяется большей из дв-ух величин Т 1,+ Т или Т, Т,+ Т,+ Т, где Тр- время установления разности в вычитающем усилителе 8,

вычитающем усилителе 8; X - время установления выходного

напряжения в усилителе 9 J Т - время срабатывания компараторов 5,

время срабатывания элементов 6;

Tg,.- время срабатывания ключей 10, т. е. определяется только одной из дв-ух. компонент общего времени.

Формула изобретения

1. Параллельно-последовательный .аналого-цифровой преобразователь, содержащий источник пороговых напряже-. НИИ и последовательно соединенные блоки преобразования, состоящие каждый из блока аналого-цифрового, преобразования, выполненного на п компараторах (где п 2 - 1, m - число разрядов), (п-1). элементах И и формирователе выходного кода и, кроме .последнего, из блока цифроаналогового преобразования выполненного на (п+1) ключах и усилителе разностного сигнала, первые входы компараторов в каждом блоке аналого-цифрового преобразования объединены и являются входной шиной каждого бло ка преобразования, вторые входы компараторов первого блока преобразования соединены с соответствующими первыми выходами источника пороговых напряжений, прямые выходы компараторов в каждом блоке аналого-цифрового преобразования, кроме первого компа- ратора, соединены с соответствующими первыми входами () элементов И, инверсные выходы компараторов, кроме п-го компаратора, соединены соответственно с вторыми входами (п-1) эле- ментов И, выходы (п-1) элементов И сси единены соответственно с (п-1) входа- ми формирователя выходного кода, выходы которого являются выходными шинами данного блока аналого-цифрового преобразования, первые входы п ключей в каждом блоке цифроаналогового, преобразования объединены с соответствующими входами формирователя выходного кода данного блока преобразования, а выходы (п+1) ключей объединены и соединены с входом усилителя разностного сигнала, выход которого является выходной шиной каждого блока преобразования, о т л и ч а ю щ и и с я тем, что, с целью повьшения быстродействия в каждый блок .аналого-цифрового преобразования введен дополнительный элемент И,а в каждый блок цифроаналогово

5 10, 15 20 25 Q- . 5

0

го преобразования введен вычитающий усилитель, первые входы всех вычитающих усилителей объединены и соединены с вторым выходом источника пороговых напряжений, второй вход каждого вычитаняцего усилителя является входной шиной соответствующего блока преобразования, (п+1) выходов вычитающего усилителя соединены соответственно с вторыми входами п ключей и первым входом (п+1)-го ключа, выход дополнительного элемента И соединен с первым входом первого ключа, первый вход дополнительного элемента И является шиной логической единицы, а второй вход соединен с прямым выходом первого компаратора, первые выходы источника пороговых напряжений соединены с соответствующими вторыми входами компа- раторов каждого блока аналого-цифрового преобразователя, кроме первого, второй вход (71+1)-го ключа соединен с инверсным выходом п-компаратора.

2. Преобразователь по п.1, о т л и- чающийся тем, что вычитающий усилитель выполнен на операционном усилителе, четырех резисторах, рези- стивном делителе напряжения, содержащем (п+1) последовательно соединенных резисторов, первый вход операционного усилителя соединен с первыми выводами , первого и второго резисторов, второй вывод первого резистора является первым входом вычитающего усилителя, второй вывод второго резистора объединен с первым входом резистивного делителя напряжения и является вторым входом вычитающего усилителя, (п+1) выходов резистивного делителя напряжения являются (п+1) выходами вычитающего усилителя, второчи вход резистивного делителя напряжения непосредственно соединен с выходом операционного уси- лителя и через третий резистор - с вторым входом операционного усилителя и первым выводом четвертого резистора, второй вывод которого является общей шиной.

ивш1 USbf)(l иВыхдившп-tl

о

Редактор А.Сабо

Составитель А.Титов Техред Л.Олейник

Заказ 3409/57Тираж 816Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

г

л

Фиг..

Корректор В.Бутяга

| название | год | авторы | номер документа |

|---|---|---|---|

| БЫСТРОДЕЙСТВУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ И СПОСОБ ЕГО КАЛИБРОВКИ | 2006 |

|

RU2341017C2 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1256201A1 |

| ИЗМЕРИТЕЛЬ СОПРОТИВЛЕНИЙ | 2002 |

|

RU2221254C2 |

| Цифровой акселерометр | 1984 |

|

SU1242831A1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2009 |

|

RU2433528C2 |

| Двухтактный аналого-цифровой преобразователь | 1985 |

|

SU1336236A1 |

| Устройство для контроля положения стационарных плужковых сбрасывателей | 1990 |

|

SU1813686A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ И СПОСОБ ЕГО КАЛИБРОВКИ | 2006 |

|

RU2335844C2 |

| СЛЕДЯЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1989 |

|

RU2028731C1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU949807A1 |

Изобретение относится к вычислительной технике и может быть использовано в быстродействующих аналого- цифровьк вычислительных устройствах. Изобретение позволяет повысить быстродействие устройства. Это достигается за счет того, что в устройство, содержащее последовательно соединенные блоки преобразования, содержащие блок аналого-цифрового преобразования, блок цифроаналогового преобразования, источник пороговых напряжений, выполненный на источнике опорного напряжения, делителе напряжения, блок цифроаналогового преобразования содержит (п+1) ключей, усилитель разностного сигнала, элемент И и вычитающий усилитель. Быстродействие достигается за счет того, что получение разностного сигнала в блоке цифроаналогового преобразования происходит параллельно с получением кода в аналого-цифровом преобразователе. 1 з.п. ф-л{)1, 2 ил. S (Л to О9 СО 00 9) СО

| Преобразователь напряжение-код | 1981 |

|

SU1003332A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Быхтияров Г.Д | |||

| Аналого-цифровые преобразователи.- М.: | |||

| Советское радио, 1980, с | |||

| Станок для изготовления из дерева круглых палочек | 1915 |

|

SU207A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1986-06-23—Публикация

1984-04-04—Подача