Изобретение относится к измерительной технике и предназначено для измерения амплитуд знакопеременных динамических сигналов с динамической погрешностью, не превышающей методической погрешности аналого-цифрового преобразователя.

Цель изобретения - расширение диапазона коррекции динамической погрешности измерения двуполярных динамических сигналов.

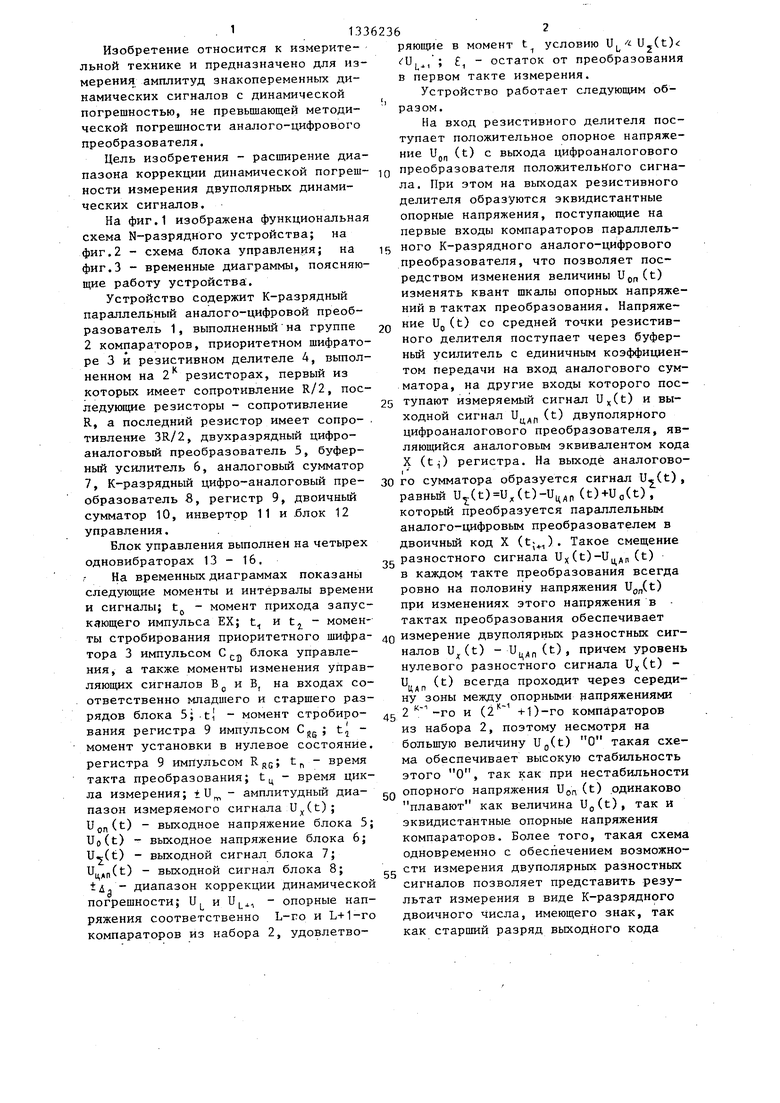

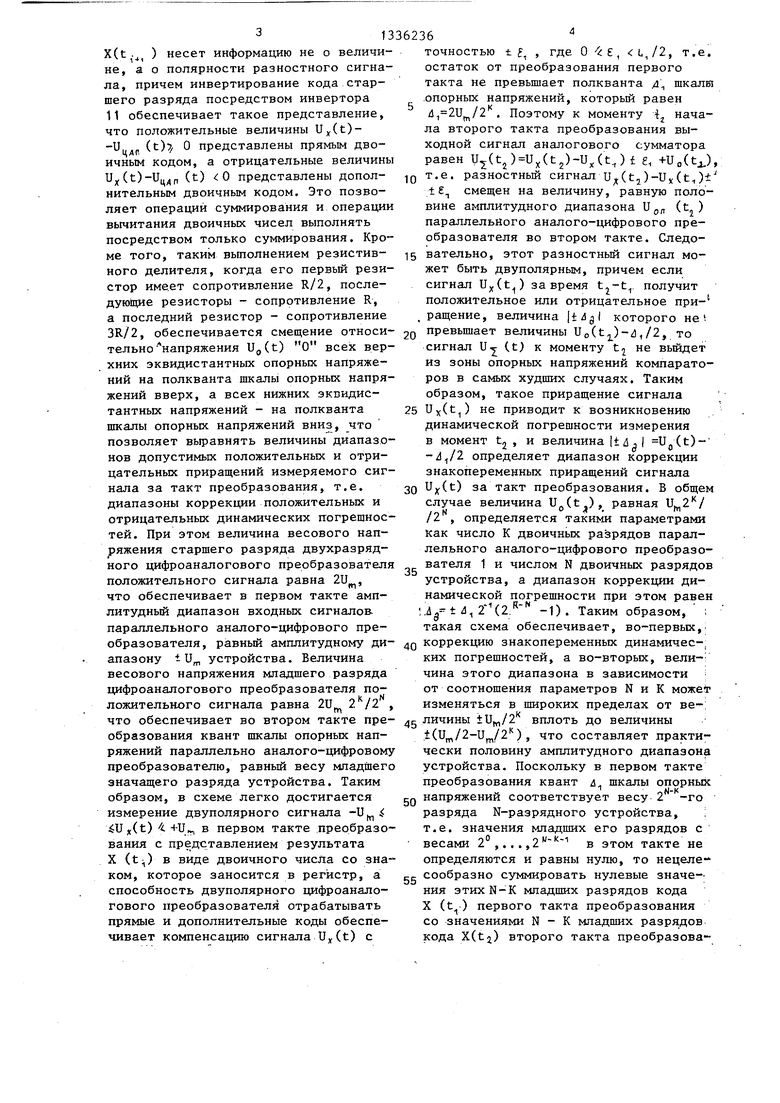

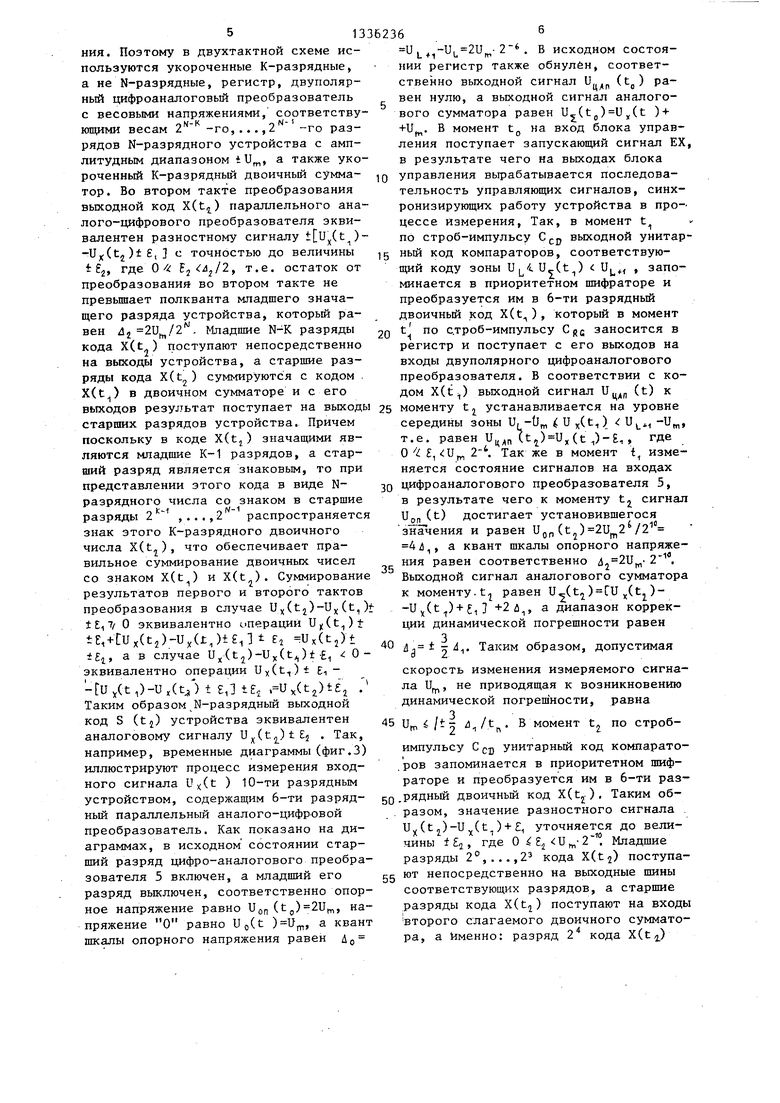

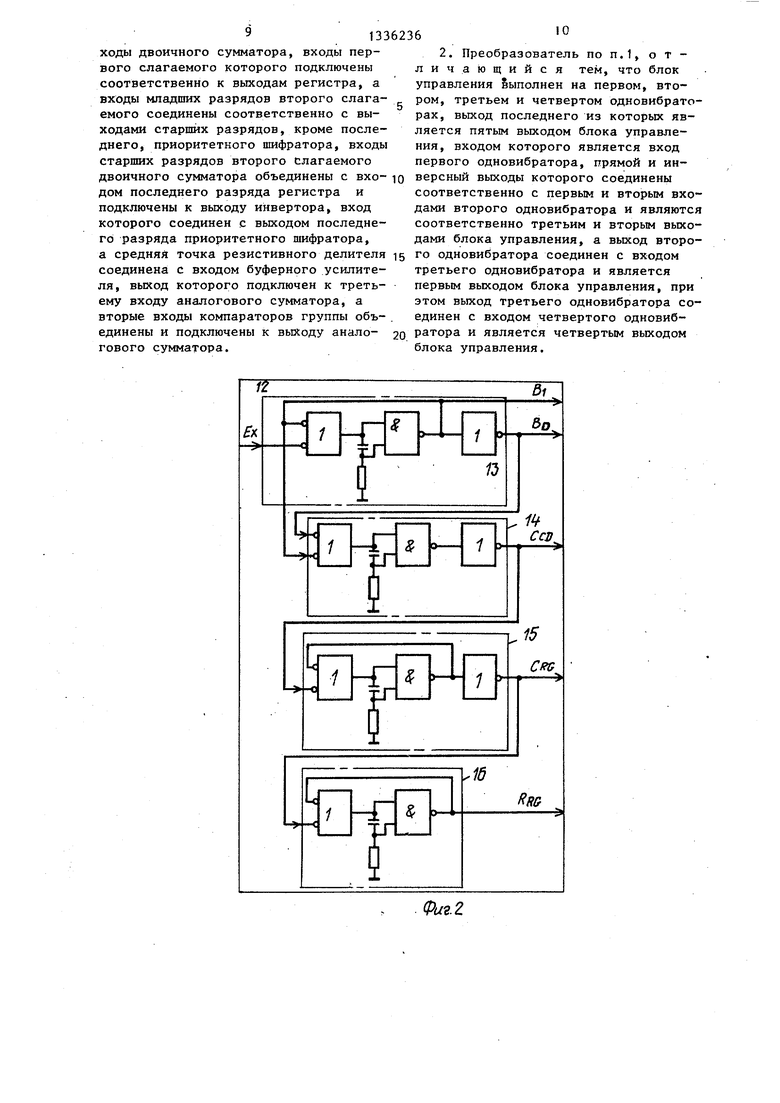

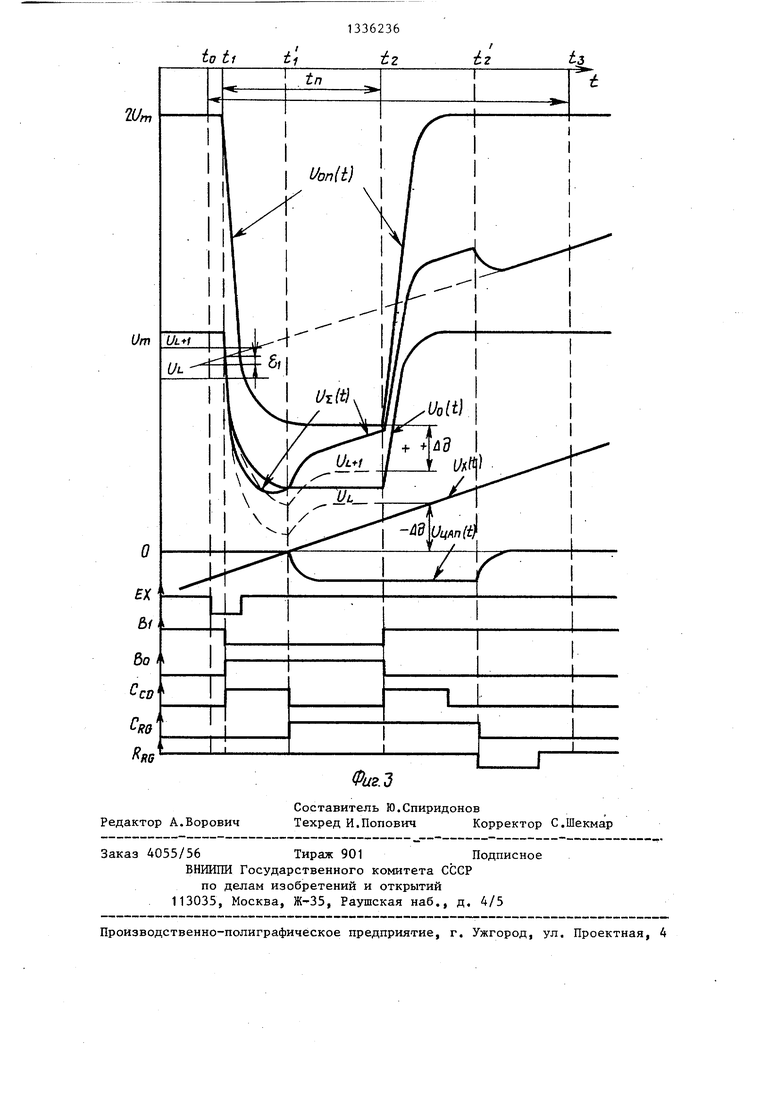

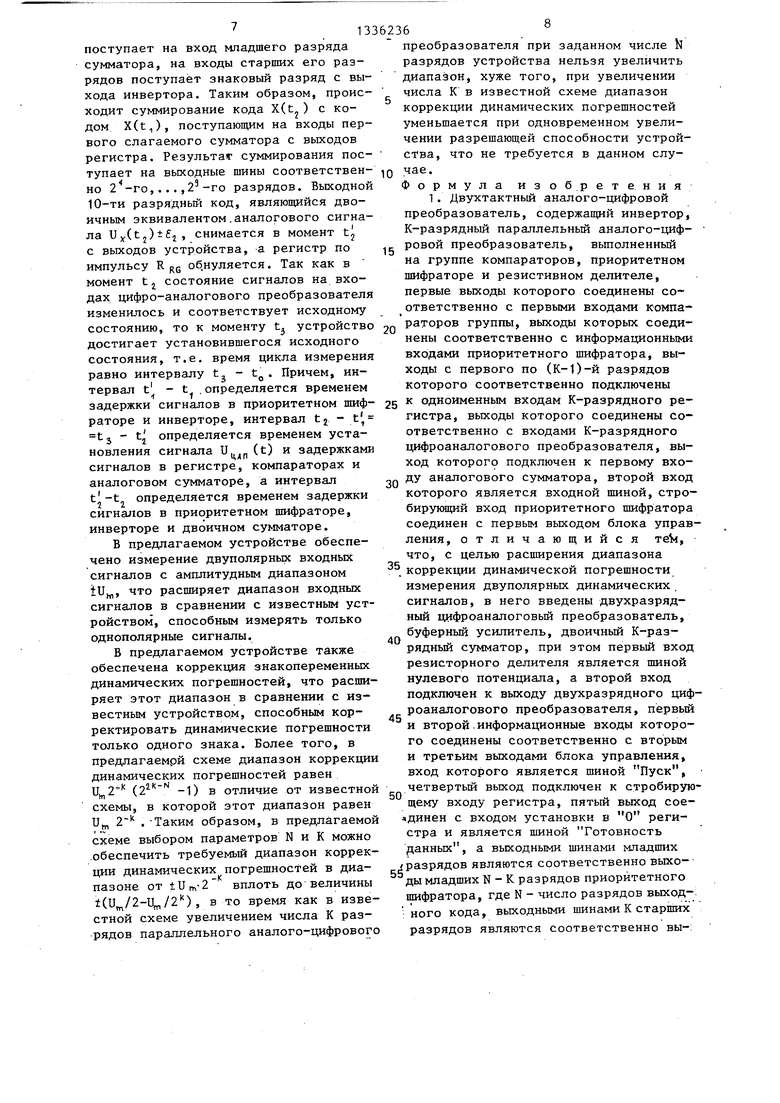

На фиг.1 изображена функциональная схема N-разрядного устройства; на фиг.2 - схема блока управления; на фиг.З - временные диаграммы, поясняющие работу устройства.

Устройство содержит К-разрядный параллельный аналого-цифровой преобразователь 1, выполненный на группе 2 компараторов, приоритетном шифраторе 3 и резистивном делителе 4, выполk

ненном на 2 резисторах, первый из которых имеет сопротивление R/2, последующие резисторы - сопротивление R, а последний резистор имеет сопро- тивление 3R/2, двухразрядный цифро- аналоговый преобразователь 5, буферный усилитель 6, аналоговый сумматор

7, К-разрядный цифро-аналоговый пре- зо го сумматора образуется сигнал U.(t) ,

равный U(t)U(t)(t)+Uo(t), который преобразуется параллельным аналого-цифровым преобразователем в двоичный код X (t;,). Такое смещение

образователь 3, регистр 9, двоичный сумматор 10, инвертор 11 и .блок 12 управления.

Блок управления выполнен на четырех одновибраторах 13-16.

На временньпс диаграммах показаны следующие моменты и интервалы времени и сигналы; t - момент прихода запускающего импульса ЕХ; t и tj - момен2g разностного сигнала Uj((t) (t)

в каждом такте преобразования всегда ровно на половину напряжения ) при изменениях этого напряжения в тактах преобразования обеспечивает ты стробирования приоритетного шифра- 40 измерение двуполярных разностных сиг- тора 3 импульсом С .д блока управле- налов U, (t) - - причем уровень

нулевого разностного сигнала U(t) - и„ (t) всегда проходит через середину зоны между опорными напряжениями

ния, а также моменты изменения управляющих сигналов В р и В, на входах соответственно младшего и старшего разрядов блока 5; -tl - момент стробирования регистра 9 импульсом tj - момент установки в нулевое состояние, регистра 9 имПульсом RRQ; t, - время такта преобразования; t - время цикла измерения; tU - амплитудный диапазон измеряемого сигнала U(t); U(,n(t) - выходное напряжение блока 5; Uo(t) - выходное напряжение блока 6; U(t) - выходной сигнал блока 7; (t) - выходной сигнал блока 8; Дд диапазон коррекции динамической погрешности; U и и, - опорные напряжения соответственно L-ro и L+1-го компараторов из набора 2, удовлетво45

-го и (2 +1)-го компараторов

50

из набора 2, поэтому несмотря на большую величину U(,(t) О такая схема обеспечивает высокую стабильность этого О, так как при нестабильности опорного напряжения Uon(t) одинаково плавают как величина ), так и эквидистантные опорные напряжения компараторов. Более того, такая схема одновременно с обеспечением возможно- gg сти измерения двуполярных разностных сигналов позволяет представить результат измерения в виде К-разряднрго двоичного числа, имеющего знак, так как старший разряд выходного кода

ряющие в момент t условию (t): U, ; , - остаток от преобразования в первом такте измерения.

Устройство работает следующим образом.

На вход резистивного делителя поступает положительное опорное напряжение Uj (t) с выхода цифроаналогового преобразователя положительного сигнала. При этом на выходах резистивного делителя образуются эквидистантные опорные напряжения, поступающие на первые входы компараторов параллель- ного К-разрядного аналого-цифрового преобразователя, что позволяет посредством изменения величины ) изменять квант шкалы опорных напряжений в тактах преобразования. Напряже

ние Up(t) со средней точки резистивного делителя поступает через буферный усилитель с единичным коэффициентом передачи на вход аналогового сумматора, на другие входы которого пос- тупают измеряемый сигнал U,((t) и выходной сигнал f (t) двуполярного цифроаналогового преобразователя, являющийся аналоговым эквивалентом кода X (t) регистра. На выходе аналоговоравный U(t)U(t)(t)+Uo(t), который преобразуется параллельным аналого-цифровым преобразователем двоичный код X (t;,). Такое смещен

2g разностного сигнала Uj((t) (t)

в каждом такте преобразования всег ровно на половину напряжения ) при изменениях этого напряжения в тактах преобразования обеспечивает 40 измерение двуполярных разностных с налов U, (t) - - причем уров

45

-го и (2 +1)-го компараторов

50

из набора 2, поэтому несмотря на большую величину U(,(t) О такая схема обеспечивает высокую стабильность этого О, так как при нестабильности опорного напряжения Uon(t) одинаково плавают как величина ), так и эквидистантные опорные напряжения компараторов. Более того, такая схема одновременно с обеспечением возможно- gg сти измерения двуполярных разностных сигналов позволяет представить результат измерения в виде К-разряднрго двоичного числа, имеющего знак, так как старший разряд выходного кода

31336236

X(t ., ) несет информацию не о величи- точностью t f , где О -i е, ij2, т.е.

не, а о полярности разностного сигнала, причем инвертирование кода старшего разряда посредством инвертора 11 обеспечивает такое представление, что положительные величины U(t)- и„.„ (t)/ О представлены прямым двоЦ А

ичным кодом, а отрицательные величины Ux(t) (t) ;0 представлены дополнительным двоичным кодом. Это позволяет операций суммирования и операции вычитания двоичных чисел выполнять посредством только суммирования. Кроме того, таким выполнением резистив- ного делителя, когда его первый резистор имеет сопротивление R/2, после- дуюйще резисторы - сопротивление R, а последний резистор - сопротивление

остаток от преобразования первого такта не превышает полкванта /i шкалш .опорных напряжений, который равен . Поэтому к моменту i начала второго такта преобразования выходной сигнал аналогового сумматора равен y(tj)Ux(t2)-U(t,)± е, +Uo(tJ, Q Т.е. разностный сигнал U(tj)-Ux(ti)i t е смещен на величину, равную половине амплитудного диапазона U

оп

(t,)

параллельного аналого-цифрового преобразователя во втором такте. Следо- 15 вательно, этот разностньй сигнал может быть двуполярным, причем если сигнал U(t) за время t,-t. получит положительное или отрицательное при- , ращение, величина i& которого не .

параллельного аналого-цифрового преобразователя во втором такте. Следо- 15 вательно, этот разностньй сигнал может быть двуполярным, причем если сигнал U(t) за время t,-t. получит положительное или отрицательное при- , ращение, величина i& которого не .

3R/2, обеспечивается смещение относи- 2о превышает величины Uo(tj),/2, то тельно напряжения Ug(t) О всех вер- сигнал U.J- (t) к моменту tj не выйдет

из зоны опорных напряжений компараторов в самых худших случаях. Таким образом, такое приращение сигнала 25 Ux(t) не приводит к возникновению динамической погрешности измерения в момент tj , и величина It Л, I U|.,(t)- -jy2 определяет диапазон коррекции знакопеременных приращений сигнала 30 U)f(t) за такт преобразования. В общем случае величина (t . , равная /2 , определяется такими параметрами как число К двоичных разрядов параллельного аналого-цифрового преобразоного цифроаналогового преобразователя вателя 1 и числом N двоичных разрядов положительного сигнала равна ZU, устройства, а диапазон коррекции динамической погрешности при этом равен -1). Таким образом, : такая схема обеспечивает, во-первых,i образователя, равный амплитудному ди- 40 коррекцию знакопеременных динамичес-, апазону tи„ устройства. Величина ких погрешностей, а во-вторых, вели- весового напряжения младшего разряда чина этого диапазона в зависимости цифроаналогового преобразователя по- от соотношения параметров N и К может ложительного сигнала равна 211, , изменяться в широких пределах от ве- что обеспечивает во втором такте пре- g личины вплоть до величины образования квант шкалы опорных нап- t() , что составляет практи- ряжений параллельно аналого-цифровому преобразователю, равный весу младшего значащего разряда устройства. Таким образом, в схеме легко достигается измерение двуполярного сигнала и,„ U(t) i. +U в первом такте преобразования с представлением результата X (t;,) в виде двоичного числа со знаком, которое заносится в регистр, а способность двуполярного цифроаналогового преобразователя отрабатывать

хних эквидистантных опорных напряжений на полкванта шкалы опорных напряжений вверх, а всех нижних эквидистантных напряжений - на полкванта шкалы опорных напряжений вниз, что позволяет выравнять величины диапазонов допустимых положительных и отрицательных приращений измеряемого сигнала за такт преобразования, т.е. диапазоны коррекции положительных и отрицательных динамических погрешностей. При этом величина весового напряжения старшего разряда двухразрядчто обеспечивает в первом такте амплитудный диапазон входных сигналов, параллельного аналого-цифрового пре50

чески половину амплитудного диапазона устройства. Поскольку в первом такте преобразования квант & шкалы опорных

- J-K

напряжений соответствует весу 2 -го разряда N-разрядного устройства, . т.е. значения младших его разрядов с

весами в этом такте не

определяются и равны нулю, то нецела- gg сообразно суммировать нулевые значе-- ния этихН-К младших разрядов кода X (t) первого такта преобразования со значениями N - К младших разрядов кода XCtj) второго такта преобразовапрямые и дополнительные коды обеспечивает компенсацию сигнала U(t) с

точностью t f , где О -i е, ij2, т.е.

остаток от преобразования первого такта не превышает полкванта /i шкалш .опорных напряжений, который равен . Поэтому к моменту i начала второго такта преобразования выходной сигнал аналогового сумматора равен y(tj)Ux(t2)-U(t,)± е, +Uo(tJ, Q Т.е. разностный сигнал U(tj)-Ux(ti)i t е смещен на величину, равную половине амплитудного диапазона U

оп

(t,)

параллельного аналого-цифрового преобразователя во втором такте. Следо- 5 вательно, этот разностньй сигнал может быть двуполярным, причем если сигнал U(t) за время t,-t. получит положительное или отрицательное при- , ращение, величина i& которого не .

о превышает величины Uo(tj),/2, то сигнал U.J- (t) к моменту tj не выйдет

вателя 1 и числом N двоичных разрядов устройства, а диапазон коррекции динамической погрешности при этом равен -1). Таким образом, : такая схема обеспечивает, во-первых,i 0 коррекцию знакопеременных динамичес-, ких погрешностей, а во-вторых, вели- чина этого диапазона в зависимости от соотношения параметров N и К может изменяться в широких пределах от ве- g личины вплоть до величины t() , что составляет практи-

0

чески половину амплитудного диапазона устройства. Поскольку в первом такте преобразования квант & шкалы опорных

- J-K

напряжений соответствует весу 2 -го разряда N-разрядного устройства, . т.е. значения младших его разрядов с

весами в этом такте не

определяются и равны нулю, то нецела- g сообразно суммировать нулевые значе-- ния этихН-К младших разрядов кода X (t) первого такта преобразования со значениями N - К младших разрядов кода XCtj) второго такта преобразования. Поэтому в двухтактной схеме используются укороченные К-разрядные, а не N-разрядные, регистр, двугюляр- ный цифроаналоговый преобразователь с весовыми напряжениями, соответствующими весам 2 -го, ..., 2 -го разрядов N-разрядного устройства с амплитудным диапазоном tU, а также укороченный К-разрядный двоичный сумма- тор. Во втором такте преобразования выходной код X(tj) параллельного аналого-цифрового преобразователя эквивалентен разностному сигналу (t)- -Vf;(t)± е., с точностью до величины t fj, где О i Ej jij/2, т.е. остаток от преобразования во втором такте не превьшает полкванта младшего значащего разряда устройства, который равен . Младшие N-K разряды кода X(t ) поступают непосредственно на выходы устройства, а старшие разряды кода XCt) суммируются с кодом . X(t) в двоичном сумматоре и с его

выходов результат поступает на выходы 25 моменту t устанавливается на уровне

старших разрядов устройства. Причем поскольку в коде X(tj) значащими являются младшие К-1 разрядов, а старший разряд является знаковым, то при представлении этого кода в виде N- разрядного числа со знаком в старшие разряды 2 ,...,2 распространяется знак этого К-разрядного двоичного числа X(t-), что обеспечивает правильное суммирование двоичных чисел со знаком X(t) и X(t ). Суммирование результатов первого и второго тактов преобразования в случае UxCtj)- (t, )t t Е, 7/ О эквивалентно операции )t ±E,+tUx(t2)-U/,)i,3 t , UK(tj)t , a в случае U(t,j)-Ux(t,)t , - 0- эквивалентно операции Ux(tT)± Ei - (t,)-U,(t/) t , t, .U(tpt / Таким образом N-разрядный выходной код S (tj) устройства эквивалентен аналоговому сигналу U (t,.,) t j . Так, например, временные диаграммы (фиг.3) иллюстрируют процесс измерения входного сигнала U(t ) 10-ти разрядным устройством, содержащим 6-ти разрядный параллельный аналого-цифровой преобразователь. Как показано на диаграммах, в исходном состоянии старший разряд цифро-аналогового преобразователя 5 включен, а младший его разряд выключен, соответственно опорное напряжение равно Uop(tр)2и„, напряжение О равно UoCt )Un,, а квант шкалы опорного напряжения равен Д5

середины зоны U,-()„ U Ct,) ., -U

tn

т.е. равен (t)и, (t,)-, , где

лт т-4 т

т fr

...

О 2 , :и . Так же в момент t, изменяется состояние сигналов на входах 30 цифроаналогового преобразователя 5, в результате чего к моменту t сигнал Up(t) достигает установившегося з:начения и равен U(,n (tj) 4 4 , а квант шкалы опорного напряжения равен соответственно iJ. 2 Выходной сигнал аналогового сумматора к моменту, t равен U-(t,, ) CU (t, )- -U(t) + 5,J +2li, a диапазон коррекции динамической погрешности равен

3 «4. Таким образом, допустимая

скорость изменения измеряемого сигна35

40

ла и,

m

не приводящая к возникновению

равна

динамической погрешности,

о

. В момент t

по строб50

импульсу С рд унитарный код компарато- , ров запоминается в приоритетном шифраторе и преобразуется им в 6-ти раз- .рядный двоичньм код X(tj), Таким об- . разом, значение разностного сигнала . Uj((tji)-U(t,) + :, уточняется до величины f 2 , где О j и - 2 Младшие разряды 2°,...,2 кода XCtj) поступа- gg ют непосредственно на выходные шины соответствующих разрядов, а старшие разряды кода X(tj) поступают на входы второго слагаемого двоичного сумматора, а именно: разряд 2 кода X(t)

и L , . В исходном состоянии регистр также обнулён, соответственно выходной сигнал U, Ч Р вен нулю, а выходной сигнал аналогового сумматора равен U,.(tj)U(t ) + +U|, В момент tjj на вход блока управления поступает запускающий сигнал ЕХ в результате чего на выходах блока управления вьфабатывается последовательность управляющих сигналов, синхронизирующих работу устройства в процессе измерения. Так, в момент t по строб-импульсу С J.JJ выходной унитарный код компараторов, соответствующий коду зоны U tU-Ct) и, , запоминается в приоритетном шифраторе и преобразуется им в 6-ти разрядный двоичный код X(t), который в момент t по с.троб-импульсу Сди заносится в регистр и поступает с его выходов на входы двуполярного цифроаналогового преобразователя. В соответствии с кодом X(t;,) выходной сигнал (t) к

моменту t устанавливается на уровне

моменту t устанавливается на уровне

середины зоны U,-()„ U Ct,) ., -U

tn

т.е. равен (t)и, (t,)-, , где

лт т-4 т

т fr

...

О 2 , :и . Так же в момент t, изменяется состояние сигналов на входах цифроаналогового преобразователя 5, в результате чего к моменту t сигнал Up(t) достигает установившегося з:начения и равен U(,n (tj) 4 4 , а квант шкалы опорного напряжения равен соответственно iJ. 2 Выходной сигнал аналогового сумматора к моменту, t равен U-(t,, ) CU (t, )- -U(t) + 5,J +2li, a диапазон коррекции динамической погрешности равен

3 «4. Таким образом, допустимая

скорость изменения измеряемого сигна

ла и,

m

не приводящая к возникновению

равна

динамической погрешности,

о

. В момент t

по строб50

импульсу С рд унитарный код компарато- , ров запоминается в приоритетном шифраторе и преобразуется им в 6-ти раз- .рядный двоичньм код X(tj), Таким об- . разом, значение разностного сигнала . Uj((tji)-U(t,) + :, уточняется до величины f 2 , где О j и - 2 Младшие разряды 2°,...,2 кода XCtj) поступа- gg ют непосредственно на выходные шины соответствующих разрядов, а старшие разряды кода X(tj) поступают на входы второго слагаемого двоичного сумматора, а именно: разряд 2 кода X(t)

поступает на вход младшего разряда сумматора, на входы старших его разрядов поступает знаковый разряд с выхода инвертора. Таким образом, происходит суммирование кода X(t ) с кодом X(t), поступающим на входы первого слагаемого сумматора с выходов регистра. Результат суммирования поступает на выходные шины соответственно 2 -го,... , разрядов. Выходной 10-ти разрядный код, являющийся двоичным эквивалентом.аналогового сигнала U(t2), снимается в момент tj с выходов устройства, а регистр по импульсу R pjg обнуляется. Так как в момент tj состояние сигналов на входах цифро-аналогового преобразователя изменилось и соответствует исходному состоянию, то к моменту t устройство

достигает установившегося исходного состояния, т.е. время цикла измерения равно интервалу терзал t| - задержки сигналов

1. Двухтактный аналого-цифровой преобразователь, содержащий инвертор, К-разрядный параллельный аналого-цифровой преобразователь, вьшолненный на группе компараторов, приоритетном шифраторе и резистивном делителе, первые выходы которого соединены соответственно с первыми входами компараторов группы, выходы которых соединены соответственно с информационными входами приоритетного шифратора, выходы с первого по (К-1)-й разрядов которого соответственно подключены

раторе и инверторе, интервал tj - tl,

j

ti

новления сигнала U (t)

30

35

tj - tg. Причем, ин- t .определяется временем

в приоритетном шиф- 25 одноименным входам К-разрядного регистра, выходы которого соединены соответственно с входами К-разрядного цифроаналогового преобразователя, выход которого подключен к первому входу аналогового сумматора, второй вход которого является входной шиной, стро- бирукяций вход приоритетного шифратора соединен с первым выходом блока управления, отличающийся TeVi, что, с целью расширения диапазона коррекции динамической погрешности измерения двуполярных динамических . сигналов, в него введены двухразрядный цифроаналоговый преобразователь, буферный усилитель, двоичный К-раз- рядный сумматор, при этом первый вход резисторного делителя является шиной нулевого потенциала, а второй вход подключен к выходу двухразрядного цифроаналогового преобразователя, первый и второй информационные входы которого соединены соответственно с вторым и третьим выходами блока управления, вход которого является шиной Пуск, четвертый выход подключен к стробирую- щему входу регистра, пятый выход сое- динен с входом установки в О регистра и является шиной Готовность

определяется временем устаи задержками

сигналов в регистре, компараторах и аналоговом сумматоре, а интервал t -t определяется временем задержки сигналов в приоритетном шифраторе, инверторе и двоичном сумматоре.

В предлагаемом устройстве обеспечено измерение двуполярных входных сигналов с амплитудным диапазоном tU, что расширяет диапазон входных сигналов в сравнении с известным устройством, способным измерять только однополярные сигналы.

В предлагаемом устройстве также обеспечена коррекция знакопеременных динамических погрешностей, что расширяет этот диапазон в сравнении с известным устройством, способным корректировать динамические погрешности только одного знака. Более того, в предлагаемрй схеме диапазон коррекции динамических погрешностей равен ( -1) в отличие от известной схемы, в которой этот диапазон равен и 2 .-Таким образом, в предлагаемой схеме выбором параметров N и К можно .обеспечить требуемый диапазон коррекции динамических погрешностей в диапазоне от tUm-2 вплоть до величины t(U /2-lI /2 ) , в то время как в известной схеме увеличением числа К разрядов параллельного аналого-цифрового

40

45

50

Данных, а выходными шинами младших f разрядов являются соответственно выходы младших N - К разрядов приоритетного шифратора, где N - число разрядов выход; ного кода, выходными шинами К старших разрядов являются соответственно вы-

10

6236°

преобразователя при заданном числе t разрядов устройства нельзя увеличить диапазон, хуже того, при увеличении числа К в известной схеме диапазон коррекции динамических погрешностей уменьшается при одновременном увеличении разрешающей способности устройства, что не требуется в данном случае .

Формула изобретения

1. Двухтактный аналого-цифровой преобразователь, содержащий инвертор, К-разрядный параллельный аналого-цифровой преобразователь, вьшолненный на группе компараторов, приоритетном шифраторе и резистивном делителе, первые выходы которого соединены соответственно с первыми входами компараторов группы, выходы которых соединены соответственно с информационными входами приоритетного шифратора, выходы с первого по (К-1)-й разрядов которого соответственно подключены

20

Данных, а выходными шинами младших f разрядов являются соответственно выходы младших N - К разрядов приоритетного шифратора, где N - число разрядов выход ного кода, выходными шинами К старших разрядов являются соответственно вы-

91336236

двоичного сумматора, входы перлл п

вого слагаемого которого подключены соответственно к выходам регистра, а входы младших разрядов второго слагаемого соединены соответственно с выходами старших разрядов, кроме последнего, приоритетного шифратора, входы старших разрядов второго слагаемого

двоичного сумматора объединены с вхо- ю версный выходы которого соединены

дом последнего разряда регистра и подключены к выходу инвертора, вход которого соединен с выходом последнего разряда приоритетного шифратора.

а средняя точка резистивного делителя 15 го одновибратора соединен с входом

соединена с входом буферного усилителя, выход которого подключен к третьему входу аналогового сумматора, а вторые входы компараторов группы объединены и подключены к выходу аналогового сумматора.

10

2. Преобразователь по п.1, о т - личающийся тем, что блок управления выполнен на первом, втором, третьем и четвертом одновибрато- рах, выход последнего из которых является пятым выходом блока управления, входом которого является вход первого одновибратора, прямой и инсоответственно с первым и вторым входами второго одновибратора и являются соответственно третьим и вторым выходами блока управления, а выход второ

третьего одновибратора и является первым выходом блока управления, при этом выход третьего одновибратора соединен с входом четвертого одновибратора и является четвертым выходом блока управления.

Фиг2

Фиг.д

Редактор А.Ворович

Составитель Ю.Спиридонов

Техред И.Попович Корректор С.Шекмар

Заказ 4055/56Тираж 901Подписное

ВНРШПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж 35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1985 |

|

SU1336237A1 |

| Следящий аналого-цифровой преобразователь | 1985 |

|

SU1361713A1 |

| Аналого-цифровой вычислитель логарифмической функции | 1985 |

|

SU1247904A1 |

| Аналого-цифровой инкрементный вычислитель экспоненциальной функции | 1985 |

|

SU1254511A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1317658A1 |

| Параллельный аналого-цифровой преобразователь | 1986 |

|

SU1332533A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1181144A1 |

| Аналого-цифровое устройство для вычисления полиномиальной функции | 1985 |

|

SU1262530A1 |

| Аналого-цифровой преобразователь в код системы остаточных классов | 1990 |

|

SU1765891A1 |

Изобретение относится к измерительной технике, предназначено для измерения амплитуд двуполярных :дина- мических сигналов с динамической погрешностью, не превьшающей методической погрешности аналого-цифрового преобразователя, В устройство, содержащее параллельный аналого-цифровой преобразователь 1, аналоговый сумматор 7,.К-разрядный цифроаналого- вый преобразователь 8, регистр 9, инвертор 11, блок управления 12, с целью распшрения диапазона коррекции динамической погрешности измерения двуполярных сигналов введены двухраз- рядньй цифроаналоговый преобразователь 5, буферный усилитель 6, двоичный сумматор 10. 1 з.п. ф-лы, 3 ил,i (Л

| Титце У., Шейк К | |||

| Полупроводниковая схемотехника | |||

| М.: Мир, 1982, с | |||

| Двигатель внутреннего горения | 1921 |

|

SU450A1 |

| Преобразование информации, в аналого-цифровых вычислительных устройствах и системах./Под ред | |||

| Г.М.Петрова | |||

| М.: Машиностроение, 1973, с | |||

| Прибор для измерения угла наклона | 1921 |

|

SU253A1 |

Авторы

Даты

1987-09-07—Публикация

1985-06-07—Подача