(54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь интегрирующего типа | 1977 |

|

SU752795A1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1695499A1 |

| Измерительный преобразователь для тензорезисторных весоизмерительных устройств | 1990 |

|

SU1830463A1 |

| Аналого-цифровой интегратор | 1981 |

|

SU1013978A1 |

| Устройство для измерения температуры | 1984 |

|

SU1268970A1 |

| Цифровой измерительный прибор | 1980 |

|

SU892309A1 |

| Цифровой интегрирующий вольтметр | 1989 |

|

SU1698813A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1481887A1 |

| Устройство для настройки систем автоматического регулирования | 1978 |

|

SU951242A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1981 |

|

SU1039025A1 |

1

Изобретение относится к электронной измерительной технике и используется при разработке цифровых вольтметров, тестеров контроля параметров цифроаналоговых и аналого-цифровых преобразователей и других изделий электронной техники.5

Известен аналого-цифровой преобразователь, содержащий первый операционный усилитель с емкостной отрицательной обратной связью, выход которого подключен к первому входу компаратора, и выполненный Q на четырех параллельно-перекрестных ключах коммутатор аналоговых сигналов, выходы которого соединены через резисторы с инвентирующими входами первого и второго операционных усилителей, а также блок управления, вход которого соединен с вы- 5 ходом компаратора, а первый л второй выходы - соответственно с отсчетным устройством и коммутатором аналоговых сигналов. Второй операционный усилитель охвачен резистивной отрицательной обратной 20 связью (усилитель - инвертор) и выход его через резистор соединен с инвертирующим входом первого операционного усилителя, а второй вход компаратора соединен с общей щиной 1.

Недостатком известного устройства является низкая точность преобразования.

Известен также аналого-цифровой преобразователь, представляющий собой двухканальный АЦП с дифференциальными входами, двумя интеграторами и трехходовым пороговым устройством, состоящим из двух пороговых устройств, первые входы которых подключены соответственно к выходам первого и второго интеграторов, а вторые объединены и подключены к источнику порогового уровня 2.

Недостатком данного устройства также является низкая точность преобразования.

Цель изобретения - повыщение точности преобразования.

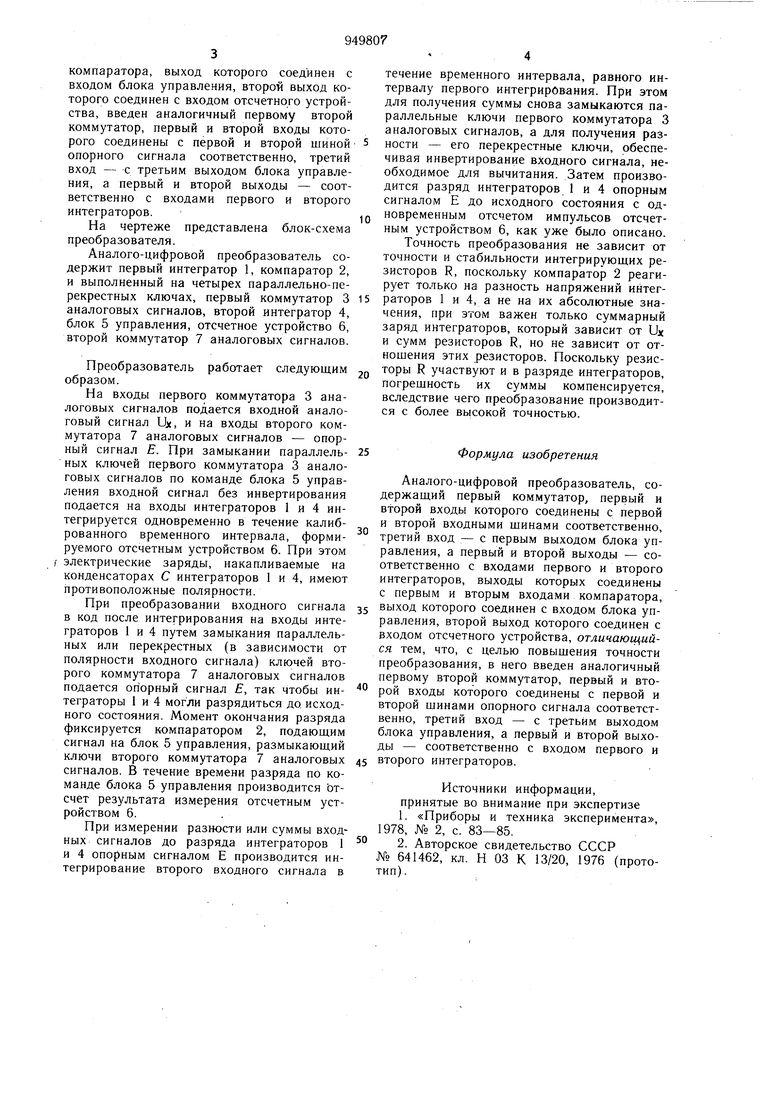

Поставленная цель достигается тем, что в известный аналого-цифровой преобразователь, содержащий первый ко.ммутатор, первый и второй входы которого соединены с первой и второй входными шинами соответственно, третий вход - с первым выходом блока управления, а первый и второй выходы - соответственно с входами первого и второго интеграторов, выходы которых соединены с первым и вторым входами компаратора, выход которого соединен с входом блока управления, второй выход которого соединен с входом отсчетного устройства, введен аналогичный первому второй коммутатор, первый и второй входы которого соединены с первой и второй шиной опорного сигнала соответственно, третий вход - с третьим выходом блока управления, а первый и второй выходы - соответственно с входами первого и второго интеграторов. На чертеже представлена блок-схема преобразователя. Аналого-цифровой преобразователь содержит первый интегратор 1, компаратор 2, и выполненный на четырех параллельно-перекрестных ключах, первый коммутатор 3 аналоговых сигналов, второй интегратор 4, блок 5 управления, отсчетное устройство 6, второй коммутатор 7 аналоговых сигналов. Преобразователь работает следующим образом. На входы первого коммутатора 3 аналоговых сигналов подается входной аналоговый сигнал Ux, и на входы второго коммутатора 7 аналоговых сигналов - опорный сигнал Е. При замыкании параллельных ключей первого коммутатора 3 аналоговых сигналов по команде блока 5 управления входной сигнал без инвертирования подается на входы интеграторов 1 и 4 интегрируется одновременно в течение калиброванного временного интервала, формируемого отсчетным устройством 6. При этом / электрические заряды, накапливаемые на конденсаторах С интеграторов 1 и 4, имеют противоположные полярности При преобразовании входного сигнала в код после интегрирования на входы интеграторов 1 и 4 путем замыкания параллельных или перекрестных (в зависимости от полярности входного сигнала) ключей второго коммутатора 7 аналоговых сигналов подается опорный сигнал Е, так чтобы интеграторы 1 и 4 могли разрядиться до исходного состояния. Момент окончания разряда фиксируется компаратором 2, подающим сигнал на блок 5 управления, размыкающий ключи второго коммутатора 7 аналоговых сигналов. В течение времени разряда по команде блока 5 управления производится отсчет результата измерения отсчетным устройством 6. При измерении разности или суммы входных сигналов до разряда интеграторов 1 и 4 опорным сигналом Е производится интегрирование второго входного сигнала в течение временного интервала, равного интервалу первого интегрирования. При этом для получения суммы снова замыкаются параллельные ключи первого коммутатора 3 аналоговых сигналов, а для получения разности - его перекрестные ключи, обеспечивая инвертирование входного сигнала, необходимое для вычитания. Затем производится разряд интеграторов 1 и 4 опорным сигналом Е до исходного состояния с одновременным отсчетом импульсов отсчетным устройством 6, как уже было описано. Точность преобразования не зависит от точности и стабильности интегрирующих резисторов R, поскольку компаратор 2 реагирует только на разность напряжений интеграторов 1 и 4, а не на их абсолютные значения, при этом важен только суммарный заряд интеграторов, который зависит от Uy и сумм резисторов R, но не зависит от отношения этих резисторов. Поскольку резисторы R участвуют и в разряде интеграторов, погрешность их суммы компенсируется, вследствие чего преобразование производится с более высокой точностью. Формула изобретения Аналого-цифровой преобразователь, содержащий первый коммутатор, первый и второй входы которого соединены с первой и второй входными шинами соответственно, третий вход - с первым выходом блока управления, а первый и второй выходы - соответственно с входами первого и второго интеграторов, выходы которых соединены с первым и вторым входами компаратора. выход которого соединен с входом блока управления, второй выход которого соединен с входом отсчетного устройства, отличающийся тем, что, с целью повышения точности преобразования, в него введен аналогичный первому второй коммутатор, первый и второй входы которого соединены с первой и второй шинами опорного сигнала соответственно, третий вход - с третьим выходом блока управления, а первый и второй выходы - соответственно с входом первого и второго интеграторов, Источники информации, принятые во внимание при экспертизе 1.«Приборы и техника эксперимента, 1978, № 2, с. 83-85. 2.Авторское свидетельство СССР № 641462, кл. Н 03 К 13/20, 1976 (прототип).

С

Авторы

Даты

1982-08-07—Публикация

1979-01-04—Подача