компаратор 6, цифроаналоговый преобразователь 7, триггер 8, схему 9 задержки, генератор 10, дешифраторы 11- 13, регистры 14 и 15 последовательного приближения, дифференциальные усилители 16 и 22, источник 17 опорного напряжения, регистры 18 и 19. цепной резистивньй делитель 20 напряжения, блок 21 сравнения, мультиплексор 23 и управляемьш инвертор- повторитель 24. Блок 21 выполнен в

Изобретение относится к измерительной технике и может быть использовано для преобразования в цифровой код выходного сигнала акселерометров датчиков угла и других первичных пре- образователей.

Цель изобретения - повышение быстродействия цифрового акселерометра.

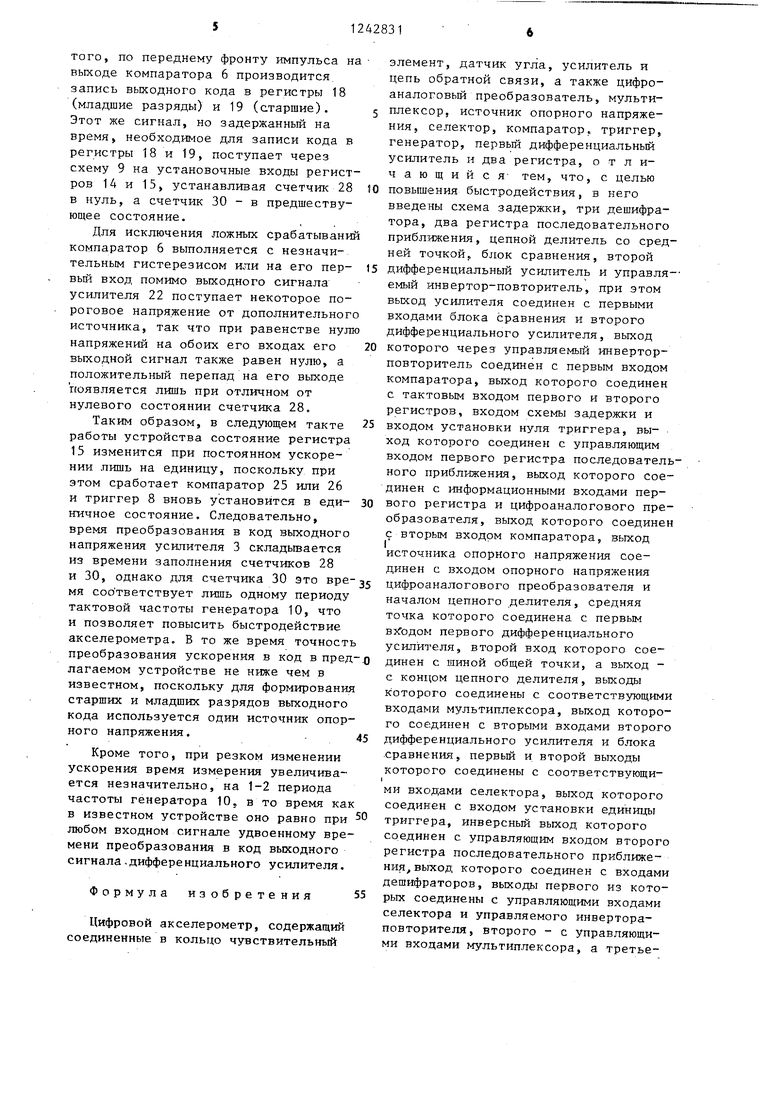

На чертеже представлена структур- ная схема цифрового акселерометра.

Акселерометр содержит чувствитель- ньй элемент 1, датчик 2 угла, предва- рительньй усилитель 3, цепь 4 обрат- oй связи, селектор 5, компаратор 6, цифроаналоговый преобраэователь 7, триггер 8, схему 9 задержки, генератор 10, дешифраторы 11-13, регистры 14 и 15 последовательного приближения, первый дифференциальньй усшш- тель 16, выполненный в виде операционного усилителя с коэффициентом передачи минус 1, источник 17 опорного напряжения, регистры 18 и 19, цепной резистивный делитель 20 напряже- ния, блок 21 сравнения, второй дифференциальный усилитель 22, мультиплексор 23 и управляемый инвертор- повторитель 24.

Блок 21 может быть выполнен в вид двух компараторов 25 и 26, причем первый вход блока 21 соединен с неинвертирующим входом компаратора 26 и инвертирующим входом компаратора 25, а второй вход блока 21 - с инверти- рующим входом компаратора 26 и инвертирующим входом компаратора 25. Регистр 14 может быть выполнен в вид

виде компараторов 25 и 26. Регистр 14 выполнен в виде элемента И 27 и двоичного счетчика 28. На выходы элемента И 27 поступает сигнал с частотой генератора 10 и выходной сигнал триггера 8, а вход установки нуля счетчика 28 соединен с установочным входом регистра 14. Регистр 15 выполнен в виде элементов И 29, реверсивного счетчика 30 и элемента И 31, соединенного со счетчиком 30. 1 ил.

последовательно соединенных элемента И и двои гного счетчика 28. На входы элемента 27 поступает сигнал с частотой генератора 10 и выходной сигнал триггера 8, а вход установки нуля счетчика 28 соединен с установочным входом регистра 14.

Регистр 15 может быт ь выполнен в виде последовательно соединенных элемента И 29, реверсивного счетчика 30 и элемента И 31, выход которого соединен с входом установки нуля счетчика 30. Входы элемента 29 соединены соответственно с выходом генератора 10 и инверсным выходом триггера 8. Сигнал с выхода элемента 29 поступает на суммирующий вход счет- чика 30, вычитающий вход которого соединен с установочным входом регистра 15.

Цепной делитель 20 представляет собой 2п последовательно соединенных резисторов. Один конец этой цепи соединен с выходом источника 17, второй - с выходом усилителя 16, а средняя точка - с инвертирующим входом последнего (под средней точкой цеп- ного резистивного делителя напряжени понимается точка соединения п-го и (п + 1)-го резисторов.

Мультиплексор 23 может быть выполнен в виде набора ключей, на входы которых поступают выходы цепного делителя 20, а выходы ключей объединены. Управляющие же входы ключей соединены соответствующими выходами дешифратора 12.

Источник 17, делитель 20, мультиплексор 23, блок 21, селектор 5, триггер 8, регистр 14, преобразователь 7 и компаратор 6 соединены последовательно, так же, как датчик 2, усилитель 3 и 22, инвертор-повторитель 24 и компаратор 6.

Устройство работает следующим образом.

Под действием ускорения чувствительный элемент 1 отклоняется из положения равновесия и на выходе датчика 2 появляется напряжение, которое после усиления на усилителе 3 посту- пает на первый вход блока 21, который осуществляет сравнение выходного сигнала усилителя 3 с напряжением на выходе мультиплексора 23.

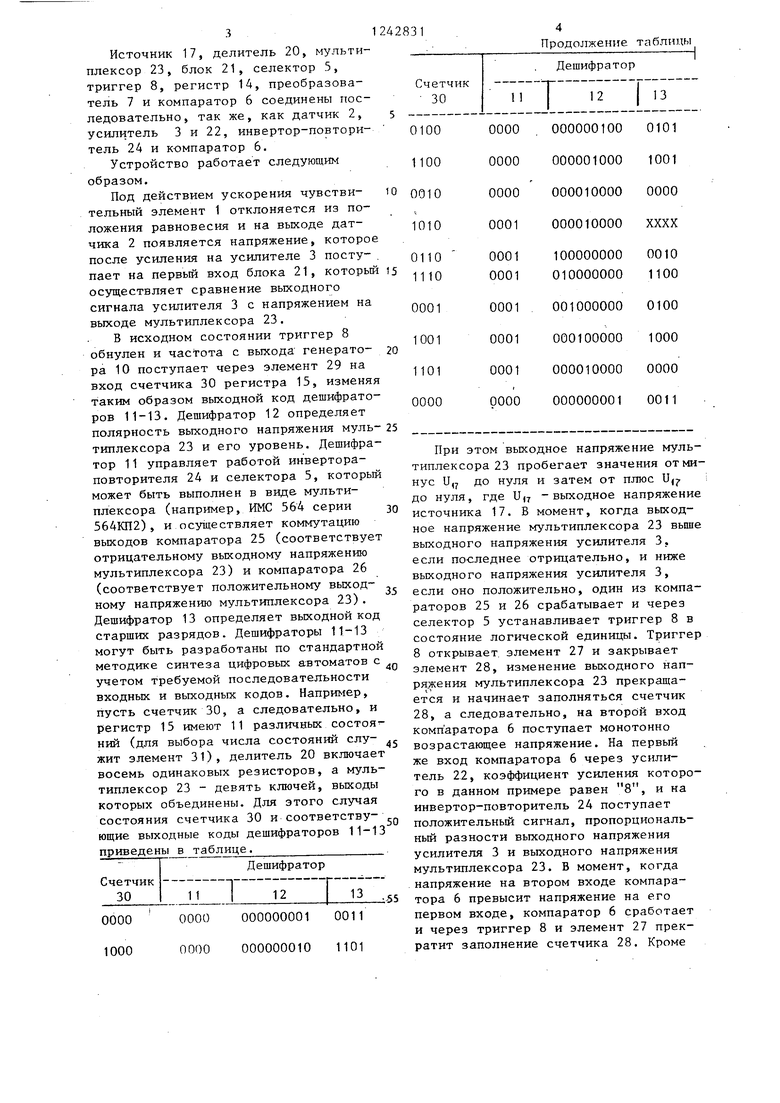

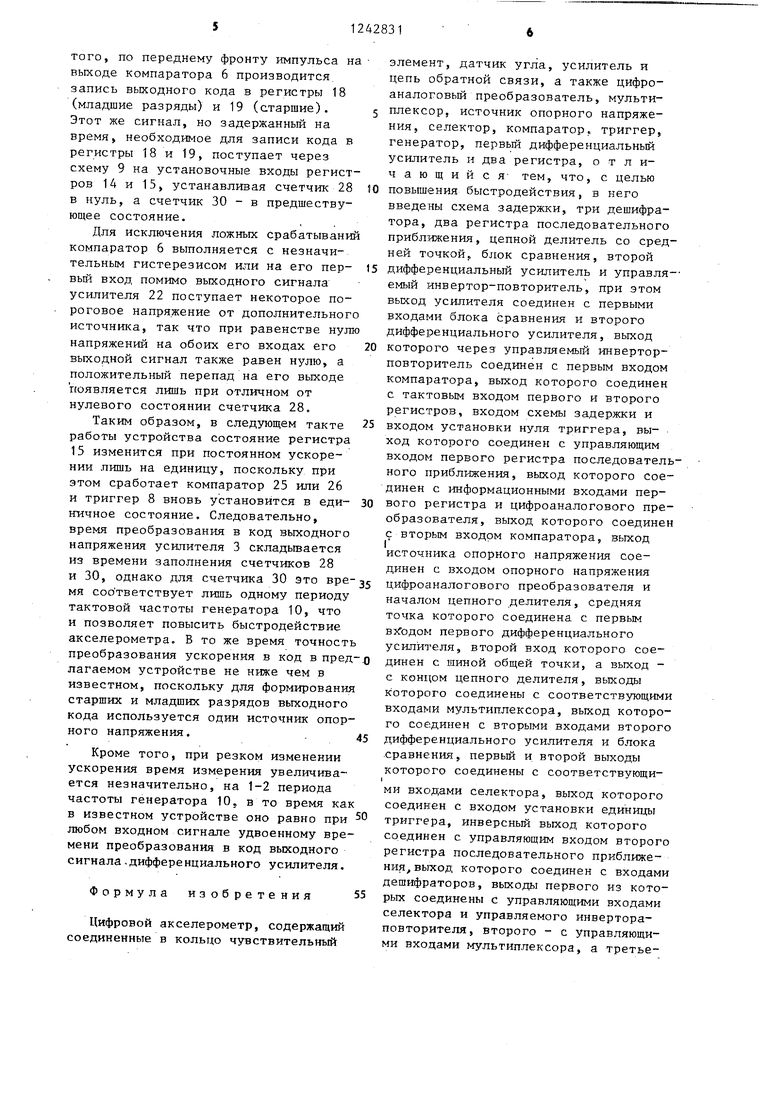

В исходном состоянии триггер 8 обнулен и частота с выхода генератора 10 поступает через элемент 29 на вход счетчика 30 регистра 15, изменяя таким образом выходной код дешифраторов 11-13. Дешифратор 12 определяет полярность выходного напряжения муль- типлексора 23 и его уровень. Дешифратор 11 управляет работой инвертора- повторителя 24 и селектора 5, который может быть выполнен в виде мультиплексора (например, ИМС 564 серии 564КП2), и осуществляет коммутацию выходов компаратора 25 (соответствует отрицательному выходному напряжению мультиплексора 23) и компаратора 26 (соответствует положительному выходному напряжению мультиплексора 23). Дешифратор 13 определяет выходной код старших разрядов. Дешифраторы 11-13 могут быть разработаны по стандартной методике синтеза цифровых автоматов с учетом требуемой последовательности входных и выходных кодов. Например, пусть счетчик 30, а следовательно, и регистр 15 имеют 11 различных состоя - ний (для выбора числа состояний слу- жит элемент 31), делитель 20 включает восемь одинаковых резисторов, а мультиплексор 23 - девять ключей, выходы которых объединены. Для этого случая состояния счетчика 30 и соответствующие выходные коды дешифраторов 11-13 приведены в таблице.

,

1000

0000

000000010 1101

10

15

20

25 зо

25 зо

35

0

При этом выходное напряжение мультиплексора 23 пробегает значения от минус U,j до нуля и затем от плюс U до нуля, где и,7 -выходное напряжение источника 17. В момент, когда выходное напряжение мультиплексора 23 вьш1е выходного напряжения усилителя 3. если последнее отрицательно, и ниже выходного напряжения усилителя 3, если оно положительно, один из компараторов 25 и 26 срабатывает и через селектор 5 устанавливает триггер 8 в состояние логической единицы. Триггер 8 открывает элемент 27 и закрывает элемент 28, изменение выходного напряжения мультиплексора 23 прекращается и начинает заполняться счетчик 28, а следовательно, на второй вход компаратора 6 поступает монотонно возрастающее напряжение. На первый же вход компаратора 6 через усилитель 22, коэффициент усиления которого в данном примере равен 8, и на инвертор-повторитель 24 поступает положительный сигнал, пропорциональный разности выходного напряжения усилителя 3 и выходного напряжения мультиплексора 23. В момент, когда напряжение на втором входе компаратора 6 превысит напряжение на его первом входе, компаратор 6 сработает и через триггер 8 и элемент 27 прекратит заполнение счетчика 28. Кроме

того, по переднему фронту импульса на выходе компаратора 6 производится запись выходного кода в регистры 18 (младшие разряды) и 19 (старшие). Этот же сигнал, но задержанный на время, необходимое для записи кода в регистры 18 и 19, поступает через схему 9 на установочные входы регистров 14 и 15, устанавливая счетчик 28 в нуль, а счетчик 30 - в предшествующее состояние.

Для исключения ложных срабатываний компаратор 6 выполняется с незначительным гистерезисом или на его пер- вый вход помимо выходного сигнала усилителя 22 поступает некоторое пороговое напряжение от дополнительного источника, так что при равенстве нулю напряжений на обоих его входах его выходной сигнал также равен нулю, а положительный перепад на его выходе появляется лишь при отличном от нулевого состоянии счетчика 28.

Таким образом, в следующем такте работы устройства состояние регистра 15 изменится при постоянном ускорении лишь на единицу, поскольку при этом сработает компаратор 25 или 26 и триггер 8 вновь установится в еди- нпчное состояние. Следовательно, время преобразования в код выходного напряжения усилителя 3 складьгоается из времени заполнения счетчиков 28 и 30, однако для счетчика 30 это время соо тветствует лишь одному периоду тактовой частоты генератора 10, что и позволяет повысить быстродействие акселерометра. В то же время точность преобразования ускорения в код в пред лагаемом устройстве не ниже чем в известном, поскольку для формирования старших и младших разрядов выходного кода используется один источник опорного напряжения.,

Кроме того, при резком изменении ускорения время измерения увеличивается незначительно, на 1-2 периода частоты генератора 10, в то время ка в известном устройстве оно равно при любом входном сигнале удвоенному времени преобразования в код выходного сигнала.дифференциального усилителя.

Формула изобретения

Цифровой акселерометр, содержащий соединенные в кольцо чувствительный

элемент, датчик угла, усилитель и цепь обратной связи, а также цифро- аналоговый преобразователь, мультиплексор, источник опорного напряжения, селектор, компаратор, триггер, генератор, первьш дифференциальный усилитель и два регистра, отличающийся- тем, что, с целью повышения быстродействия, в него введены схема задержки, три дешифратора, два регистра последовательного приближения, цепной делитель со средней точкой,, блок сравнения, второй дифференциальный усилитель и управля емый инвертор-повторитель, при этом выход усилителя соединен с первыми входами блока сравнения и второго дифференциального усилителя, выход которого через управляемый инвертор- повторитель соединен с первым входом компаратора, выход которого соединен с тактовым входом первого и второго регистров, входом схемы задержки и входом установки нуля триггера, выход которого соединен с управляющим входом первого регистра последователного приближения, выход которого соединен с информационными входами первого регистра и цифроаналогового преобразователя, выход которого соедине с вторым входом компаратора, выход источника опорного напряжения соединен с входом опорного напряжения цифроаналогового преобразователя и началом цепного делителя, средняя точка которого соединена с первым взйздом первого дифференциального усилителя, второй вход которого соединен с шиной общей точки, а выход - с концом цепного делителя, выходы которого соединены с соответствующим входами мультиплексора, вьгход которого соединен с вторыми входами второг дифференциального усилителя и блока .сравнения., первый и второй выходы которого соединены с соответствующими входами селектора, выход которого соединен с входом установки единицы триггера, инверсный выход которого соединен с управляющим входом второг регистра последовательного приближе- ния выход которого соединен с входам дешифраторов, выходы первого из которых соединены с управляющими входами селектора и управляемого инвертора- повторителя, второго - с управляющими входами мультиплексора, а третье712428318

го - с информационными входами второ- и второго регистров последовательного го регистра, причем выход генератора приближения, а выход схемы задержки - соединен с тактовыми входами первогос их установочными входами.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления | 1984 |

|

SU1229721A1 |

| Датчик угловой скорости | 1985 |

|

SU1296949A1 |

| Самонастраивающееся устройство управления | 1983 |

|

SU1130830A1 |

| Регулятор | 1987 |

|

SU1462232A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Масштабирующий преобразователь | 1982 |

|

SU1038880A1 |

| Система управления | 1987 |

|

SU1444707A1 |

| Способ маркирования информационных комбинаций в системах последовательной записи с двухчастотным кодированием и устройства записи и воспроизведения для его осуществления | 1987 |

|

SU1543445A1 |

| Широкодиапазонный логарифмический аналого-цифровой преобразователь | 1988 |

|

SU1580557A1 |

| Устройство для измерения произведения двух напряжений | 1983 |

|

SU1195265A1 |

Изобретение относится к измерительной технике и может быть использовано для преобразования в .цифровой код выходного сигнала акселерометров, датчиков угла и других первичных преобразователей. Цель изобретения - повышение быстродействия цифрового акселерометра. Устройство содержит чувствительный элемент 1, датчик 2 угла, предварительный усилитель 3, цепь 4 обратной связи, селектор 5, SuftiS «7 (Л Щшо (c/mfflUf)

| Коновалов С.Ф | |||

| и др | |||

| Гироскопические системы, ч | |||

| Ш, М.: Высшая школа, 1980, -с | |||

| Способ обработки медных солей нафтеновых кислот | 1923 |

|

SU30A1 |

| Авторское свидетельство СССР № 1167954, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-07-07—Публикация

1984-11-27—Подача