Изобретение относится к вычислительной технике и может быть использовано для организации обмена инфорацией между различными внешними устройствами и процессорами., а также между процессорами многопроцессорной вычислительной системы.

Цель изобретения - повышение коэффициента использования, оборудования и производительности многопроцес; сорной системы.

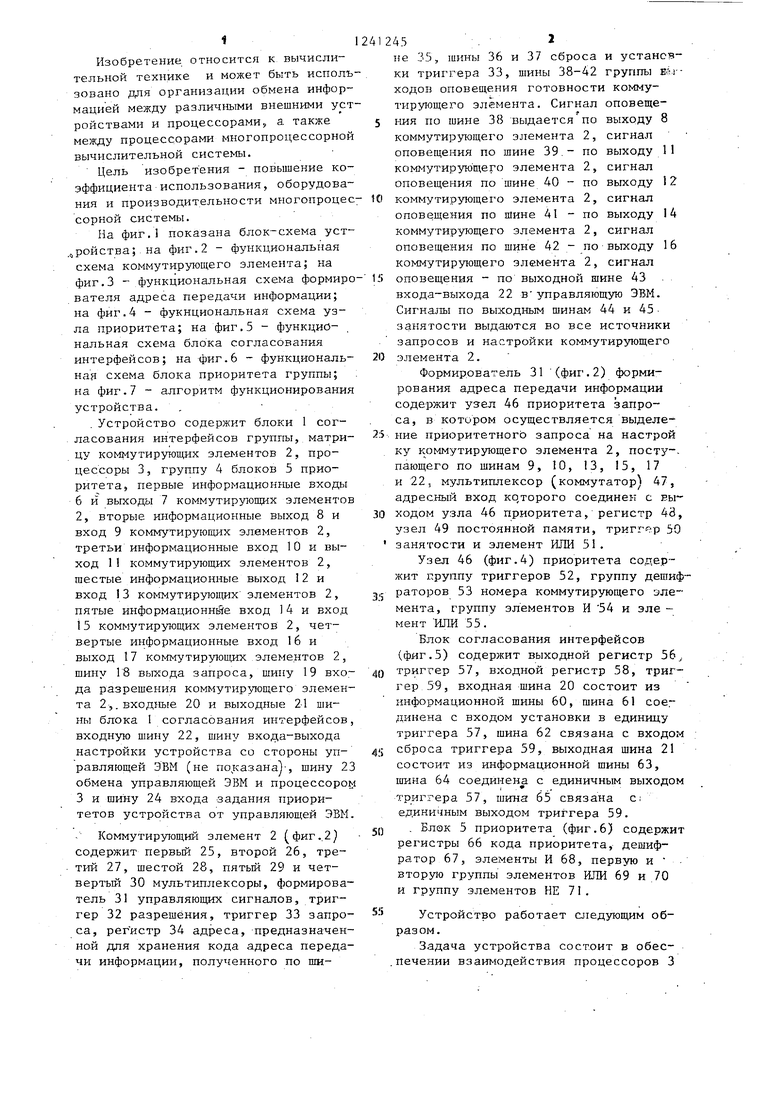

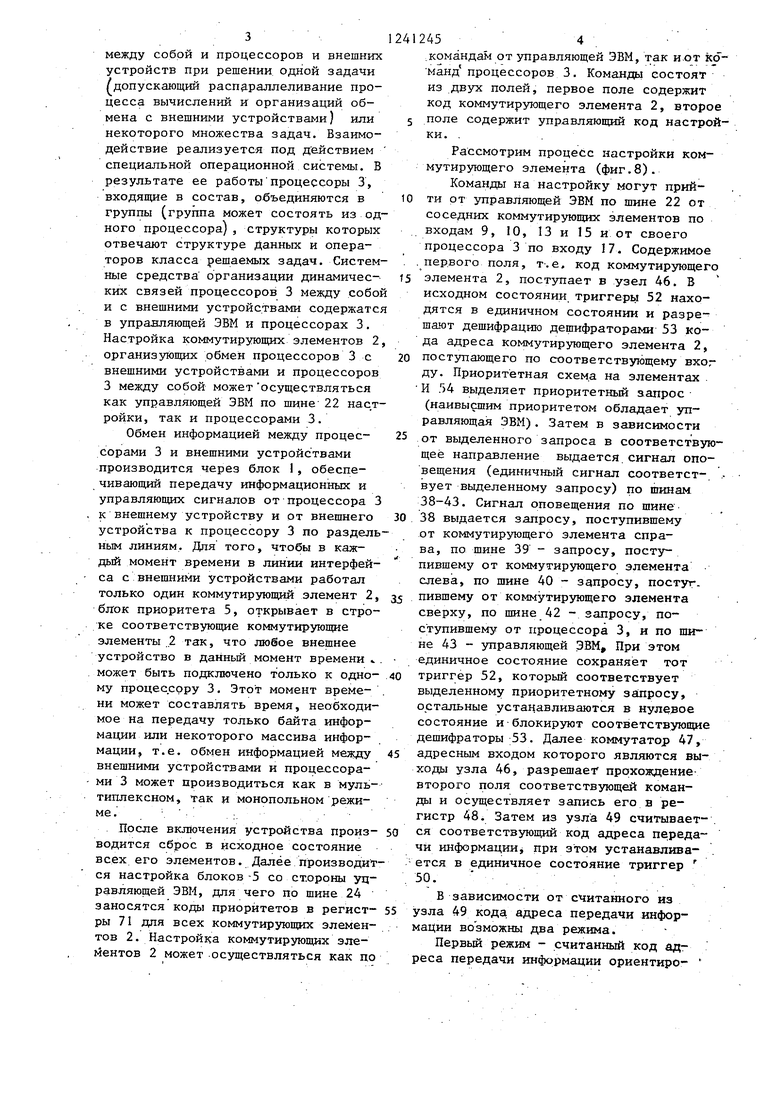

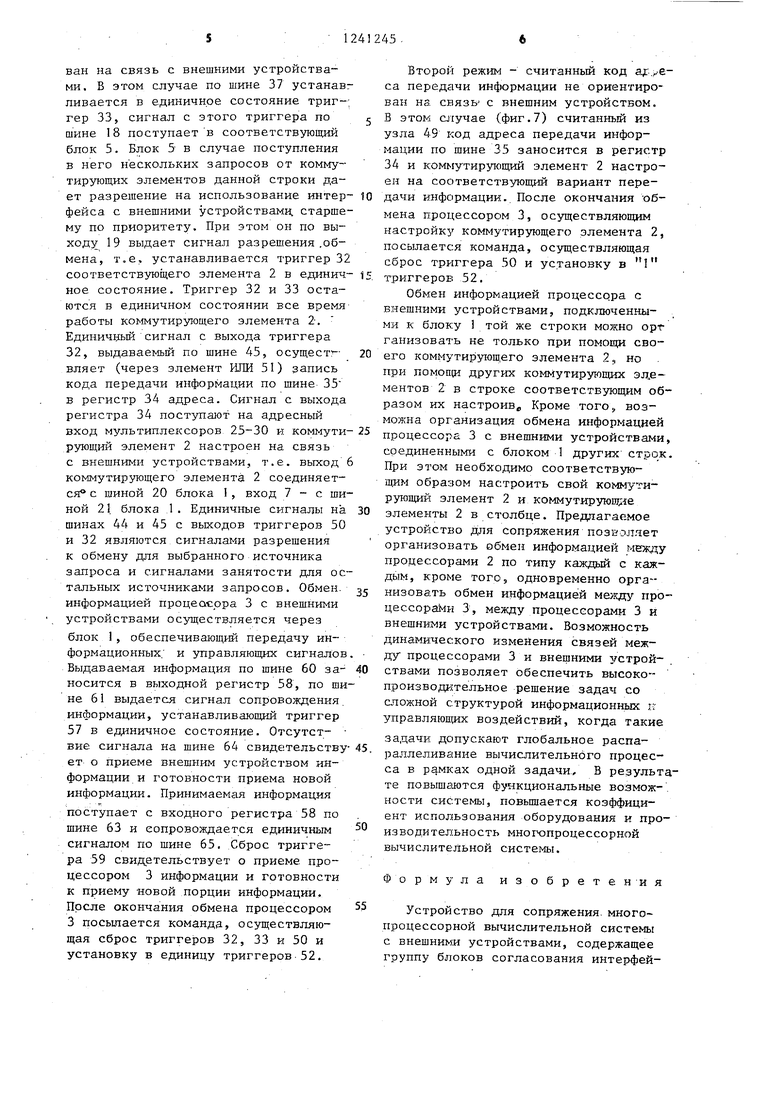

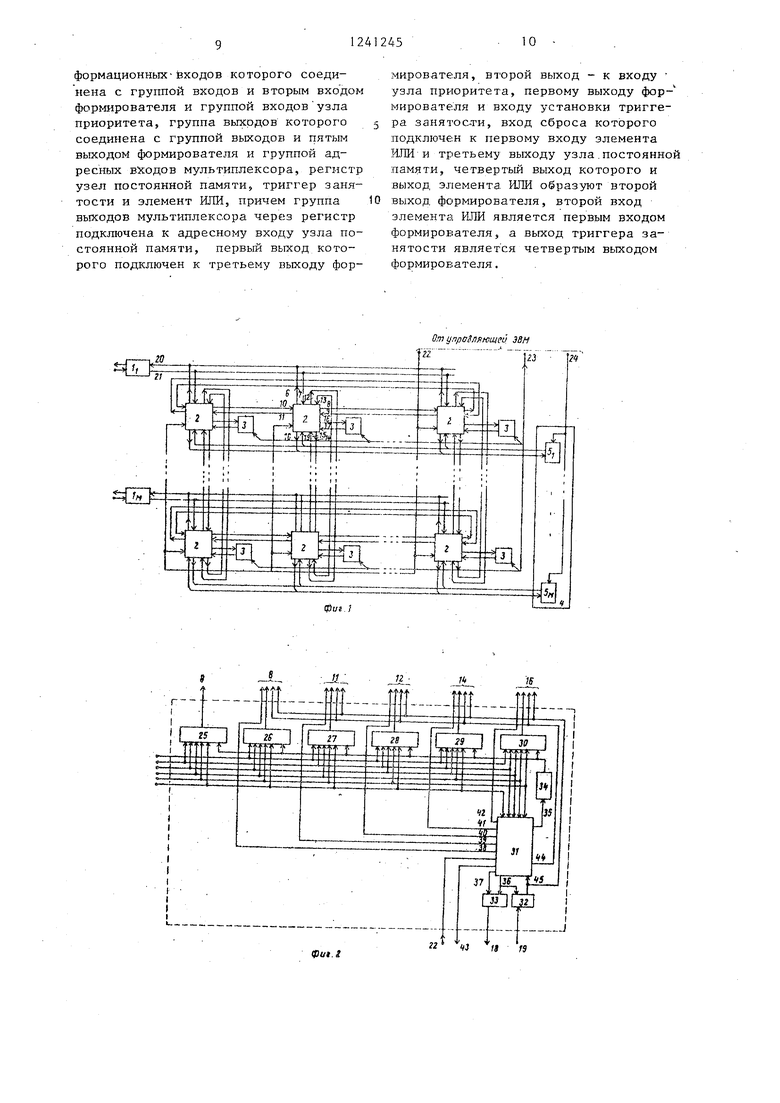

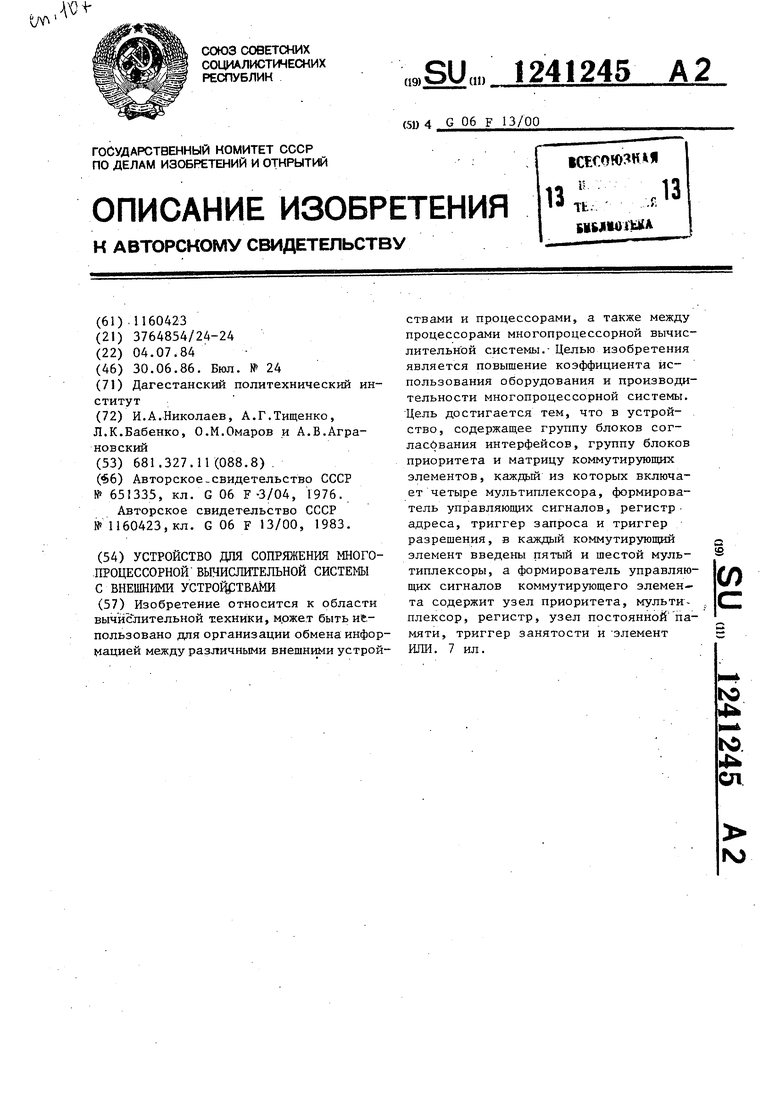

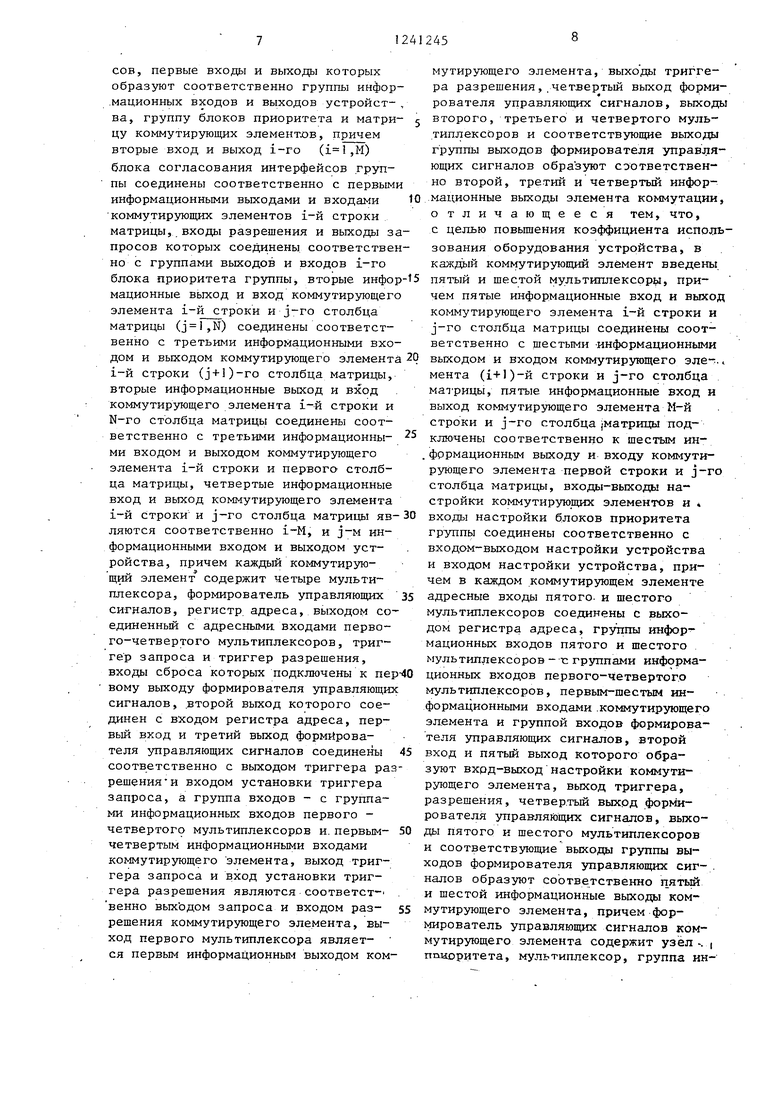

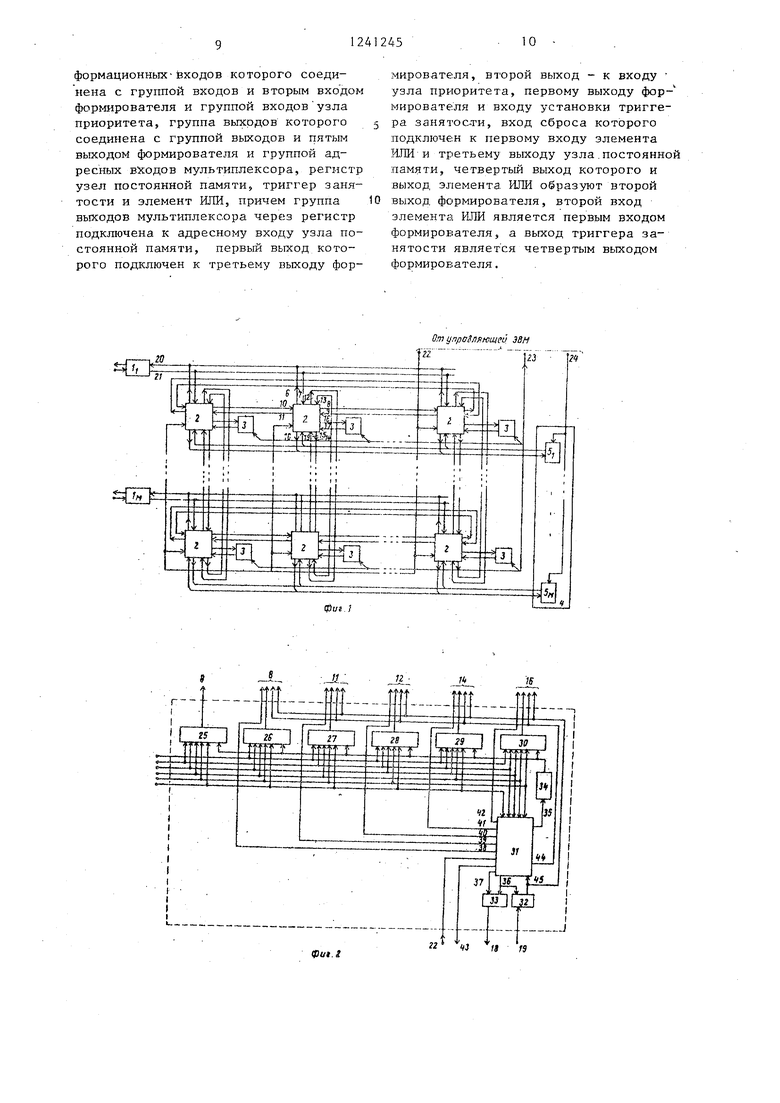

На фиг,1 показана блок-схема уст- ройства;. на фиг. 2 - функциональная схема коммутирующего элемента; на фиг.З - функциональная схема формиро вателя адреса передачи информации; на фиг.4 - фукнциональная схема уза приоритета; на фиг.5 - функциональная схема блока согласования интерфейсов; на фиг.6 - функциональная схема блока приоритета группы; на фиг.7 - алгоритм функционирования устройства. , .

Устройство содержит блоки 1 согасования интерфейсов группы, матрицу коммутирующих элe 5eнтoв 2, процессоры 3 5 группу 4 блоков 5 приоритета, первые информационные входы 6 и выходы 7 коммутируюшдх элементов 2, вторые информационные выход 8 и вход 9 коммутирующих элементов 2, третьи информационные вход 10 и выход 11 коммутирующих элементов 2, естые информационные выход 12 и вход 3 коммутируюцц1Х элементов 2, пятые информационнее вход 14 и вход 15 коммутирующих элементов 2, четвертые информационные вход 16 и выход 17 коммутируюищх элементов 2, шину 18 выхода запроса, щину 19 входа разрешения коммутирующего элемента 2,.вход11ые 20 и выходные Z1 шины блока I согласования интерфейсов, входную шину 22, шину входа-выхода настройки устройства со стороны управляющей ЭВМ (не по,казана)-, шину 23 обмена управляющей ЭВМ и процессором 3 и шину 24 входа задания приоритетов устройства от управляющей ЭВМ.

Коммутирующий элемент 2 (фиг.,2) одержит первьш 25, второй 26, треий 27, шестой 28, пятый 29 и четертый 30 мультиплексоры, формирователь 31 управляющих сигналов, триггер 32 разрешения, триггер 33 запроса, регистр 34 адреса, предназначенной для хранения кода адреса передаи информации, полученного по ши

К)

20

3:5

3f3

35

40

50

5

245 :. 2

не 35,, шины 36 и 37 сброса и установки триггера 33, шины 38-42 группы Eftr- ходов оповещения готовности коммутирующего элемента. Сигнал оповещения по шине 38 выдается по выходу В коммутирующего элемента 2, сигнал оповещения по шине 39.- по выходу 11 коммутирующего элемента 2, сигнал оповещения по шине 40 - по выходу 12 коммутирующего элемента 2, сигнал оповещения по шине 41 - по выходу 14 коммутирующего элемента 2, сигнал оповещения по шине 42 - по выходу 16 коммутирующего элемента 2, сигнал оповещения - по выходной шине 43 входа-выхода 22 в управляющую ЭВМ. Сигналы по выходным шинам 44 и 45 занятости выд.аются во все источники запросов и настройки коммутирующего элемента 2. .

Формирователь 31 (Фиг.2) формирования адреса передачи информации содержит узел 46 приоритета запроса, в котором осуществляется выделение приоритетного запроса на настрой ку коммутирующего элемента 2, посту - пающего по шинам 9, 10, 13, 15, 17 и 22, мультиплексор (коммутатор) 47, адресный вход которого соединен с ЕЫ- ходом узла 46 приоритета, регистр 48, узел 49 постоянной памяти, триггер 50 занятости и элемент ИЛИ 51.

Узел 46 (фиг.4) приоритета содержит круппу триггеров 52, группу дешифраторов 53 номера коммутирующего элемента, группу элементов И 54 и эле - мент ИЛИ 55.

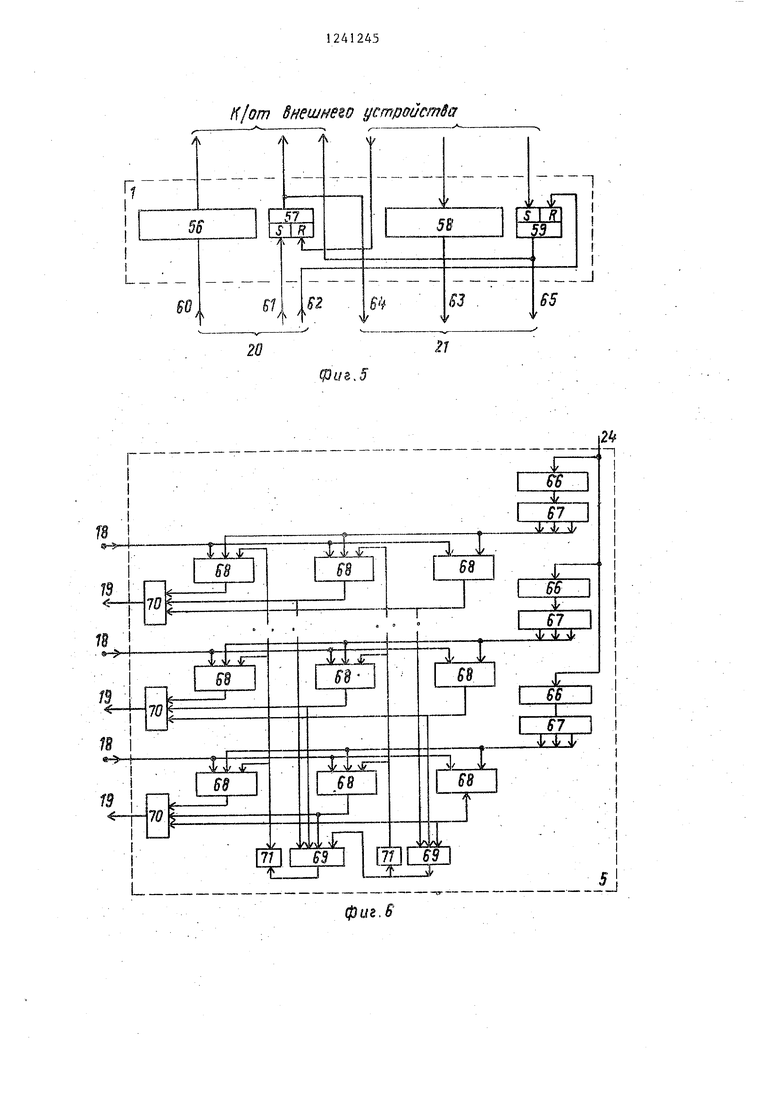

Блок согласования интерфейсов (фиг.5) содержит выходной регистр 56 триггер 57, входной регистр 58, триггер 59, входная шина 20 состоит из информационной шины 60, шина 61 соединена с входом установки в единицу триггера 57, шина 62 связана с входом сброса триггера 59, выходная шина 21 состоит из информационной шины 63, шина 64 соединена с единичным выходом триггера 57, шина 65 связана с; единичным выходом триггера 59.

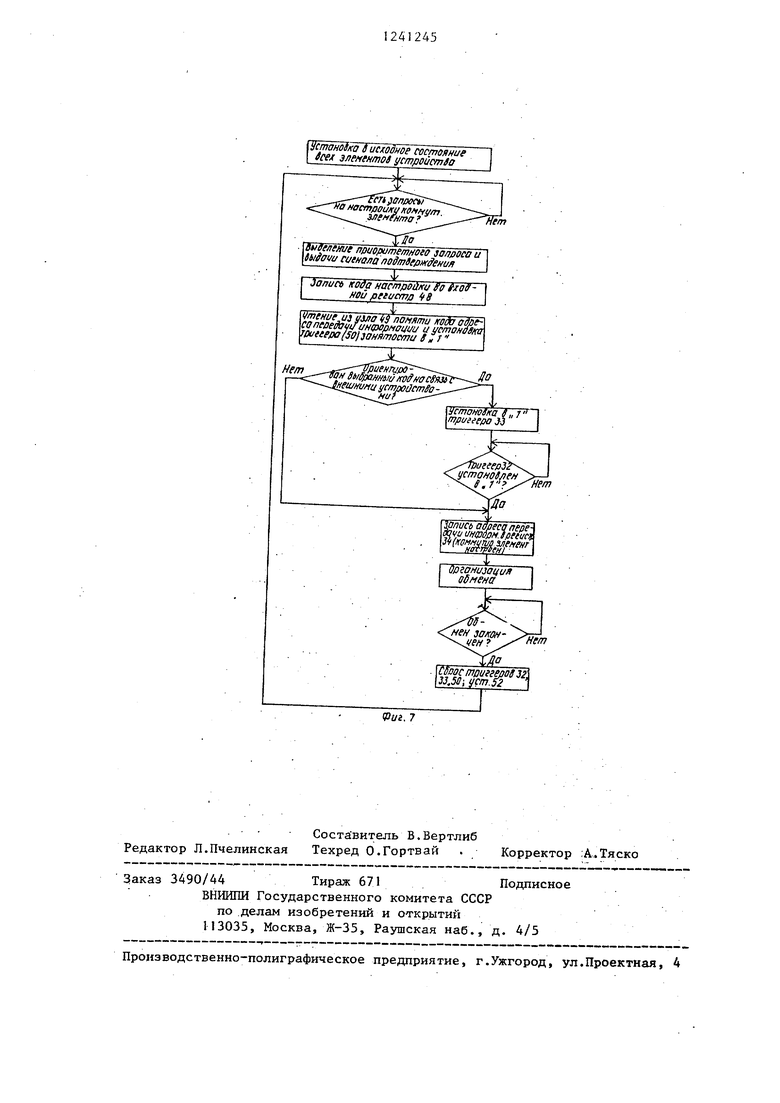

. Блек 5 приоритета (фиг.6) содержит регистры 66 кода приоритета, дешифратор 67, элементы И 68, первую и . вторую группы элементов ИЛИ 69 и 70 и группу элементов НЕ 71.

Устройство работает следующим образом.

Задача устройства состоит в обес- .печении взаимодействия процессоров 3

3

между собой и процессоров и внешних устройств при решении одной задачи /допускающий распараллеливание процесса вычислений и организаций обмена с внешними устройствами) или некоторого множества задач. Взаимодействие реализуется под действием специальной операционной системы. В результате ее работы процессоры 3, входящие в состав, объединяются в группы (группа может состоять из одного процессора), структуры которых отвечают структуре Данных и операторов класса решаемых задач. Систем- ные средства организации динамичес- ких связей процессоров 3 между собой и с внешними устройствами содержатся в управляющей ЭВМ и процессорах 3. Настройка коммутирзтащих элементов 2 организующих обмен процессоров 3 с внешними устройствами и процессоров 3 между собой может осуществляться как управляющей ЭВМ по шине 22 ройки, так и процессорами 3.

Обмен информацией между процес-

сорами 3 и внешними устройствами производится через блок 1, обеспечивающий передачу информационных и управляющих сигналов от процессора 3 к внешнему устройству и от внешнего устройства к процессору 3 по раздельным линиям. Для того, чтобы в каждый момент времени в линии интерфейса с внешними устройствами работал только один коммутирующий элемент 2, блок приоритета 5, открывает в строке соответствующие коммутирующие элементы 2 так, что любое внешнее устройство в данный момент времени .. может быть подключено только к одно- му процессору 3. Это т момент времени может составлять время, необходимое на передачу только байта информации или некоторого массива информации, т.е. обмен информацией между внешними устройствами и процессорами 3 может производиться как в мультиплексном, так и монопольном режиме. . - . :..

После включения устройства произ- водится сброс в исходное состояние всех его элементов. Далее производится настройка блоков -5 со стороны уц- равляющей ЭВМ, для чего по шине 24 заносятся коды приоритетов в регист- ры 71 дпя всех коммутирующих элементов 2. Настройка коммутирующих элементов 2 может осуществляться как по

454 .

.командам от управляющей ЭВМ, так и.от кр- макд процессоров 3. Команды состоят из двух полей, первое поле содержит код коммутирующего элемента 2, второе поле содержит управляющий код настройки. . .

Рассмотрим процесс настройки коммутирующего элемента (фиг.8).

Команды на настройку могут прийти от управляющей ЭВМ по шине 22 от соседних коммутирующих элементов по входам 9, 10, 13 и 15 и от своего процессора 3 по входу 17. Содержимое

первого поля, т.е. код коммутирующего элемента 2, поступает в узел 46. В исходном состоянии, триггеры 52 находятся в единичном состоянии и разрешают дешифрацию дещифраторами 53 кода адреса коммутирующего элемента 2, поступающего по соответствующему вхог ду. Приоритетная схема на элементах .

И 34 выделяет приоритетньш запрос (наивысшим приоритетом обладает управляющая ЭВМ). Затем в зависимости от вьщеленного запроса в соответствзго- щеё направление выдается, сигнал оповещения (единичный сигнал соответст-. вует выделенному запросу) по шинам 38-43. Сигнал оповещения по шине 38 выдается запросу, поступившему от коммутирующего элемента справа, по шине 39 - запросу, поступившему от коммутирующего элемента слева, по шине 40 - запросу, постуг. пившему от коммутирующего элемента сверху, по шине 42 - запросу, по- с тупившему от процессора 3, и по шине 43 - управляющей ЭВМ, При этом единичное состояние сохраняет тот триггер 52, который соответствует выделенному приоритетному заиросу, остальные устанавливаются в нулевое состояние и-блокируют соответствующие дешифраторы 53. Далее коммутатор 47, адресным входом которого являются выходы узла 46, разрешает прохождение- второго поля соответствующей команды и осуществляет запись его в регистр 48. Затем из узла 49 считывает- . ся соответствующий код адреса передачи информации при этом устанавлива- .

ется в единичное состояние триггер 50. .

В зависимости от считанного из зла 49 кода адреса передачи инфорации возможны два режима.

Первый режим - считанный код адеса передачи информации ориентире-

ван на связь с внешними устройствами. В этом случае по шине 37 устанавг ливается в единичное состояние триг-; гер 33, сигнал с этого триггера по шине 18 поступает в соответствующий блок 5. Блок 5 в случае поступления в него нескольких запросов от коммутирующих элементов данной строки дает разрешение на использование интер- фейса с внешними устройствами, старшему по приоритету. При этом он по выходу 19 выдает сигнал разрешения .обмена, т,е, устанавливается триггер 32 соответствующего элемента 2 в единич- ное состояние. Триггер 32 и 33 остаются в единичном состоянии все время работы коммутиру}ощего элемента 2. Единичньй сигнал с выхода триггера 32, выдаваемый по шине 45, осущест: - вляет (через элемент ИЛИ 51) запись кода передачи информации по шине 35 в регистр 34 адреса. Сигнал с выхода регистра 34 поступают на адресный вход мультиплексоров 25-30 и коммути- рующий элемент 2 настроен на связь с внешними устройствами, т.е. выход 6 коммутирующего элемента 2 соединяется с шиной 20 блока I, вход 7 - с шиной 21 блока .1. Единичные сигналы на шинах 44 и 45 с выходов триггеров 50 и 32 являются сигналами разрешения к обмену для выбранного источника запроса и сигналами занятости для остальных источниками запросов. Обмен. информацией процеасрра 3 с внешними устройствами осуществляется через блок I, обеспечивающий передачу информационных; и управляющих сигналов Выдаваемая информация по шине 60 за- носится в выходной регистр 58, по шине 61 выдается сигнал сопровождения информации, устанавливающий триггер 57 в единичное состояние. Отсутст- вие сигнала на шине 64 свидетельству ет о приеме устройством информации, и готовности приема новой информации. Принимаемая информация

поступает с входного регистра 58 по шине 63 и сопровождается единичным сигналом по шине 65. .Сброс триггера 59 свидетельствует о приеме процессором 3 информации и готовности к приему новой порции информации. После окончания обмена процессором 3 посылается команда, осуществляющая сброс триггеров 32, 33 и 50 и установку в единицу триггеров-52.

Второй режим - считанный код .е- са передачи информации не ориентирован на СВЯЗЬ с внешним устройством. В этом случае (фиг.7) считанный из узла 49 код адреса передачи информации по шине 35 заносится в регистр 34 и к:оммутир5аощий элемент 2 настроен на соответствующий вариант передачи информации.. После окончания обмена процессором 3, осуществляющим настройку коммутирующего элемента 2, посылается команда, осуществляющая сброс триггера 50 и ус,тановку в I триггеров 52.

Обмен информацией процессора с внешними устройствами, подключенными к блоку той же строки можно орг ганизовать не только при помощи своего коммутируюш.его элемента 2, но при помощи других коммутирующих эл,.е- ментов 2 в строке соответствующим образом их настроив Кроме того, возможна организация обмена информацией процессора 3 с внешними устройствами соединенными с блоком 1 других При этом необходимо соответствующим образом настроить свой коммутирующий элемент 2 и коммут,ируюш;ие элементы 2 в столбце. Предлагаемое устройство для сопряжения позволяет организовать обмен информацией между процессорами 2 по типу каждый с каждым, кроме того, одновременно организовать обмен информацией межцу процессорами 3, между процессорами 3 и внешними устройствами. Возможность динамического измейения связей между процессорами 3 и внещними устройствами позволяет обеспечить высоко- производ1:(тельное решение задач со апожной структурой информационных к управляющих воздействий, когда такие задачи допускают глобальное распараллеливание вычислительного процесса в рамках одной задачи/ В результте повьш 1ются функциональные возможности системы, повьш1ается коэффициент использования оборудования и производительность многопроцессорной вычислительной системы.

Формула изобретен ия

Устройство для сопряжения, многопроцессорной вычислительной системы с внешними устройствами, содержащее группу блоков согласования интерфейсов, первые входы и выходы которых образуют соответственно группы инфор- .мационных входов и выходов устройства, группу блоков приоритета и матри- цу коммутирующих элементов, причем вторые вход и выход i-ro (,M) блока согласования интерфейсов группы соединены соответственно с первыми информационными выходами и входами коммутирующих элементов i-й строки матрицы,,входы разрешения и выходы запросов которых соединены соответственно с группами выходов и входов i-ro блока приоритета группы, вторые инфор мационные выход и вход коммутирующего элемента i-й строки и j-ro столбца матрицы (,N) соединены соответственно с третьими информационными входом и выходом коммутирующего элемента i-й строки (j+l)-ro столбца матрицы, вторые информационные выход и вход коммутирующего элемента i-й строки и N-ro столбца матрицы соединены соответственно с третьими информационны- ми входом и выходом коммутирующего элемента i-й строки и первого столбца матрицы, четвертые информационные вход и выход коммутирующего элемента i-й строки и J-го столбца матрицы являются соответственно i-M, и j-м информационными входом и выходом устройства, причем каждый коммутирую- щий элемент содержит четыре мультиплексора, формирователь управляющих сигналов, регистр адреса, выходом соединенный с адресными, входами перво- го-четвертого мультиплексоров, триггер запроса и триггер разрешения, входы сброса которых подключены к пер вому выходу формирователя управляющих сигналов, второй выход которого соединен с входом регистра адреса, первый вход и третий выход формирователя управляющих сигналов соединены соответственно с выходом триггера разрешения и входом установки триггера запроса, а группа входов - с группами информационных входов первого - четвертого мультиплексоров и. первым- четвертым информационными входами коммутирующего элемента, выход триггера запроса и вход установки триггера разрешения являются соответст- венно вьк одом запроса и входом раз- решения коммутирующего элемента, выход первого мультиплексора являет- ся первым информационным выходом коммутирующего элемента, выходы триггера разрешения,.четвертый выход формирователя управляющих сигналов, выход второго, третьего и четвертого мультиплексоров и соответствующие выходы группы выходов формирователя управляющих сигналов образуют соответственно второй, третий и четвертый информационные выходы элемента коммутации отличающееся тем, что, с целью повьш1ения коэффициента исползования оборудования устройства, в каждай коммутирующий элемент введены пятый и шестой мультиплексор), причем пятые информационные вход и выхо коммутирующего элемента i-й строки и j-ro столбца матрицы соединены соответственно с щестыми -информационными выходом и входом коммутирующего эле-: мента (i+l)-й строки и j-ro столбца матрицы, пятые информационные вход и выход коммутирующего элемента М-й строки и j-ro столбца матрицы подключены соответственно к шестым ин- .фррмационным выходу и входу коммутирующего элемента первой строки и j-r столбца матрицы, входы-выходы настройки коммутирующих элементов и входы настройки блоков приоритета группы соединены соответственно с входом-выходом настройки устройства и входом настройки устройства, причем в каждом коммутирующем элементе адресные входы пятого, и шестого мультиплексоров соединены с выходом регистра адреса, грутгпы инфор- мационных входов пятого и шестого мультиплексоров-г группами информационных входов первого-четвертогр мультиплексоров, первым-шестым информационными входами .коммутирующего элемента и группой входов формирователя управляющих сигналов, второй вход и пятый выход которого образуют вхрд-выход настройки коммутирующего элемента, выход триггера, разрешения, четвер.тый выхрд формирователя управляющих сигналов, выходы пятого и шестого мультиплексоров и соответствующие выходы группы выходов формирователя управляющих сиг- налов образуют соответственно пятый и шестой информационные выходы коммутирующего элемента, причем формирователь управляющих сигналов коммутирующего элемента содержит узел-. I ппиоритета, мультиплексор, группа информационных-iBXOflOB которого соединена с группой входов и вторым входом формирователя и группой входов узла приоритета, группа выходов которого соединена с группой выходов и пятым выходом формирователя и группой адресных входов мультиплексора, регистр узел постоянной памяти, триггер занятости и элемент ШШ, причем группа выходов мультиплексора чер€;з регистр подключена к адресному входу узла постоянной памяти, первый выход которого подключен к третьему выходу фор

мирователя, второй выход - к входу узла приоритета, первому выходу фор- мирователя и входу установки триггера занятос-ти, вход сброса которого подключен к первому входу элемента ИЛИ и третьему выходу узла.постоянной памяти, четвертый выход которого и выход элемента ИЛИ образуют второй выход формирователя, второй вход элемента ИЛИ является первым входом формирователя, а выход триггера занятости является четвертым выходом формирователя.

От ijnpoSnfiHiaisu Эдн

Л

фиг.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения многопроцессорной вычислительной системы | 1983 |

|

SU1160423A1 |

| Устройство для сопряжения | 1981 |

|

SU964622A1 |

| Устройство для сопряжения | 1976 |

|

SU651335A1 |

| Устройство для сопряжения | 1982 |

|

SU1038933A1 |

| Устройство для сопряжения | 1990 |

|

SU1753478A1 |

| Коммутационное устройство | 1985 |

|

SU1285486A1 |

| Устройство для сопряжения каналов ввода-вывода с внешними устройствами | 1985 |

|

SU1277128A1 |

| Устройство для сопряжения | 1982 |

|

SU1056177A2 |

| Устройство для обмена информацией междуэлЕКТРОННОй ВычиСлиТЕльНОй МАшиНОй(эВМ) и уСТРОйСТВАМи ВВОдА и ВыВОдА | 1979 |

|

SU809140A1 |

| Устройство для сопряжения вычислительной машины с устройством ввода изображения | 1985 |

|

SU1260967A1 |

Изобретение относится к области вычис пительной техники, может быть ие- пользовано для организации обмена информацией между различными внешними устройствами и процессорами, а также между процессорами многопроцессорной вычислительной системы.- Целью изобретения является повышение коэффициента использования оборудования и производительности многопроцессорной системы. Цель достигается тем, что в устройство, содержащее группу блоков согласования интерфейсов, группу блоков приоритета и матрицу коммутирующих элементов, каждый из которых включает четыре мультиплексора, формирователь управляющих сигналов, регистр- адреса, триггер запроса и триггер разрешения, в каждый коммутирующий элемент введены пятый и шестой мультиплексоры, а формирователь управляющих сигналов коммутирующего элемента содержит узел приоритета, мультиплексор, регистр, узел постоянной памяти, триггер занятости и элемент ШШ. 7 ил. с ( (Л ND |;;ь ел N)

Фи1.1

22 « , VS

фцг.З

Внешнее устройстёа

20

фи&.з

L.

фив.б

27

.J -J

Рг/г. 7

Авторы

Даты

1986-06-30—Публикация

1984-07-04—Подача