чены соответственно к первому и второму информационным входам коммутирующего элемента, вторые информационные входы первого и второго мультиплексоров и третий информационный вход четвертого мультиплексора соединены с третьим информационным входом комму тир уюп1е го элемента, третьи информационные входы первого, второго и третьего мультиплексоров соединены с четвертым информационным входом коммутирующего элемента группа.входов команд формирователя управляющих сигналов соединена с третьим и четвертым информационными вх одами коммутирующего элемента, йыходы второго, третьего и четвертого мультиплексоров, гыход триггера разрешения, выход занятости и соответствующие выходы группы выходов запрета формирователя управляющих сигналов образуют соответственно второй,., третий и четвертый информационные выходы коммутирующего элемента, вход установки триггера, разрешения является входом разрешения коммутирующего элемента, причем формирователь управляющих

сигналов содержит узел приоритета, коммутатор, регистр, узел постоянной памяти, триггер занятости и элемент Ш|И, при этом группы информационных входов коммутатора и узла приоритета соединены с группой входов команд формирователя, группа выходов узла приоритета является группой выходов запрета формирователя и соединена с группой адресных входов коммутатора, выход которого подключен через регистр к входу узла постоянной памяти, первый и второй выходы которого являк)тся соответственно выходом запроса и выходом завершения цикла формирователя, третий выход соединен с входом сброса триггера занятости и первым входом элемента ИЛИ, второй вход которого является входом разрешения формирователя, второй выход узла постоянной памяти соединен с входом установки триггера занятости, выход которого является выходом занятости формирователя,четвертый выход узла постоянной памяти и выход элемента ИЛИ образуют адресный выход формирователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения многопроцессорной вычислительной системы с внешними устройствами | 1984 |

|

SU1241245A2 |

| Устройство для сопряжения каналов ввода-вывода с внешними устройствами | 1985 |

|

SU1277128A1 |

| Коммутационное устройство | 1985 |

|

SU1285486A1 |

| Устройство для сопряжения | 1982 |

|

SU1056177A2 |

| Устройство для сопряжения | 1981 |

|

SU964622A1 |

| Устройство для сопряжения | 1982 |

|

SU1038933A1 |

| Устройство для сопряжения вычислительной машины с устройством ввода изображения | 1985 |

|

SU1260967A1 |

| Устройство для сопряжения | 1976 |

|

SU651335A1 |

| Устройство для сопряжения | 1983 |

|

SU1115044A1 |

| Запоминающее устройство | 1985 |

|

SU1256096A1 |

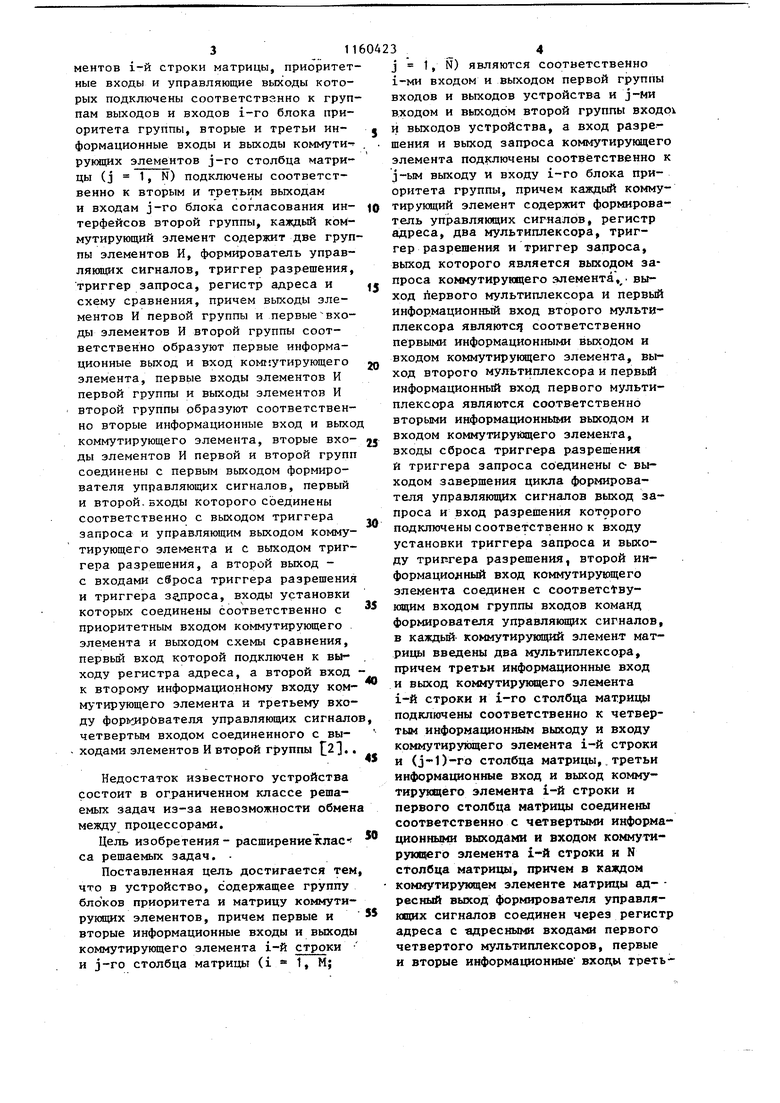

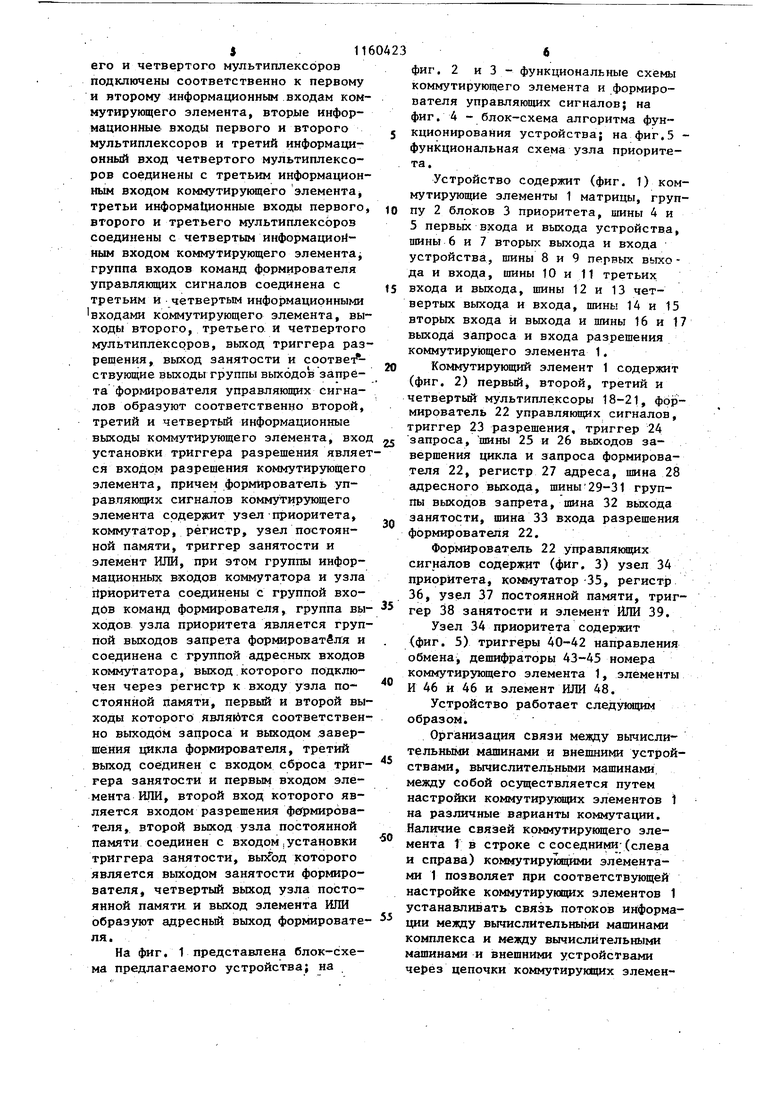

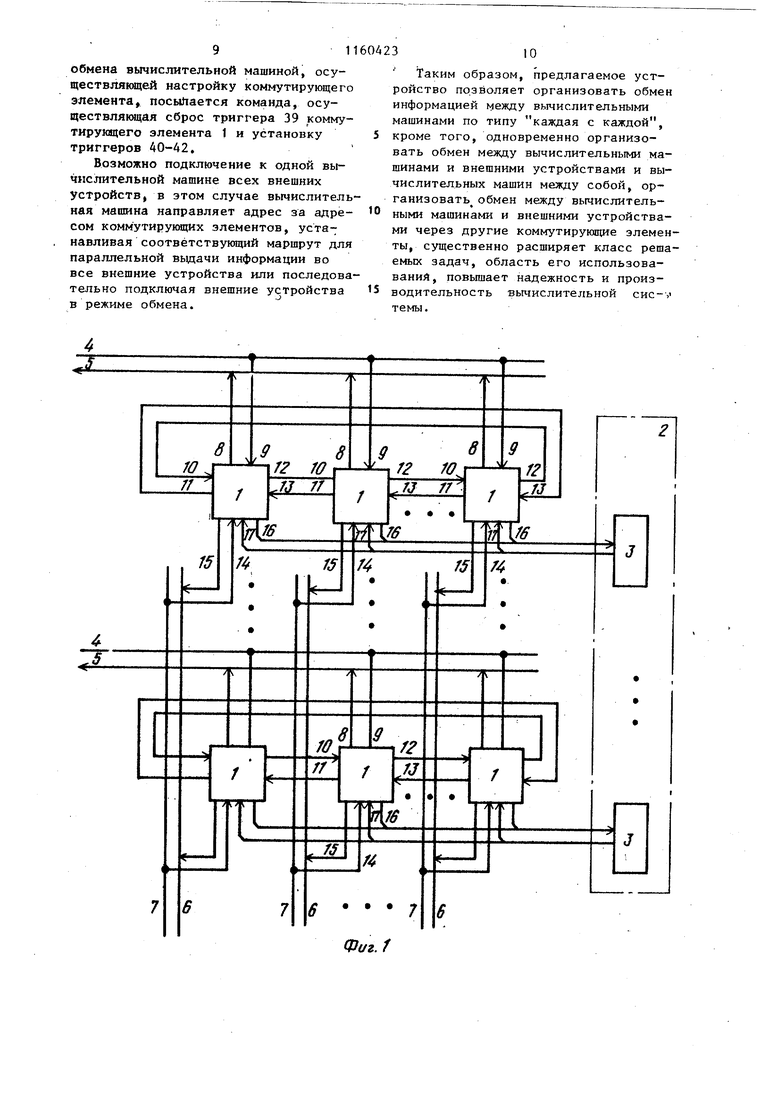

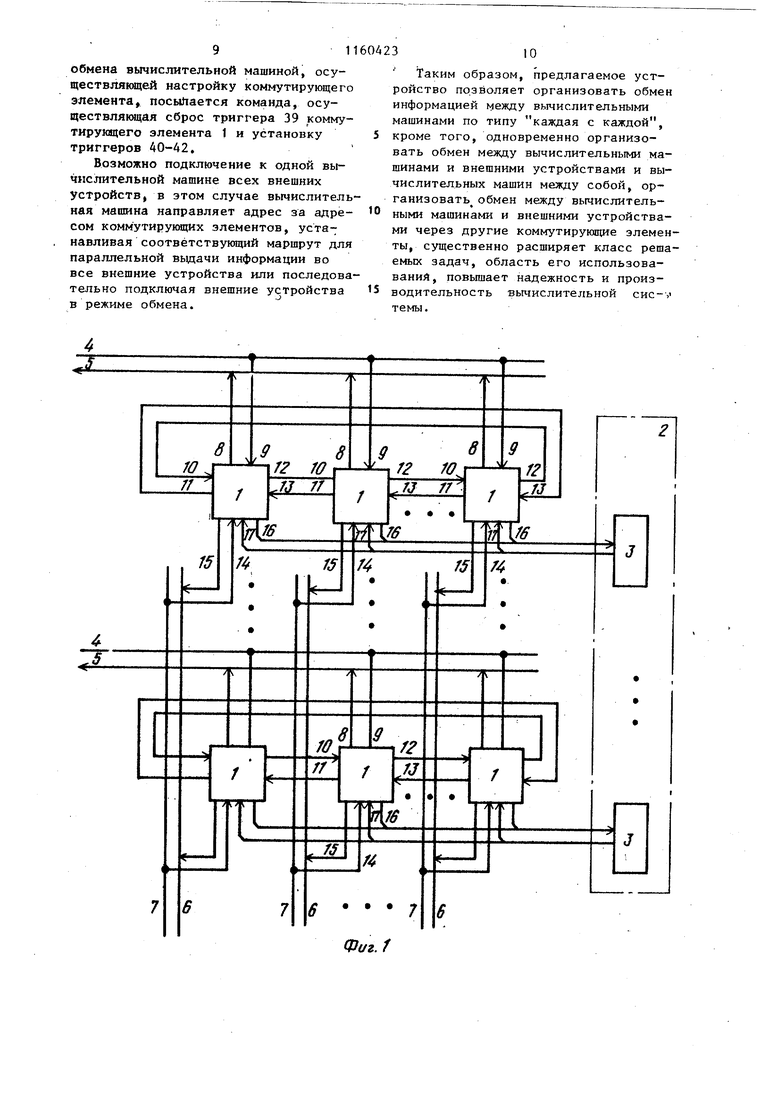

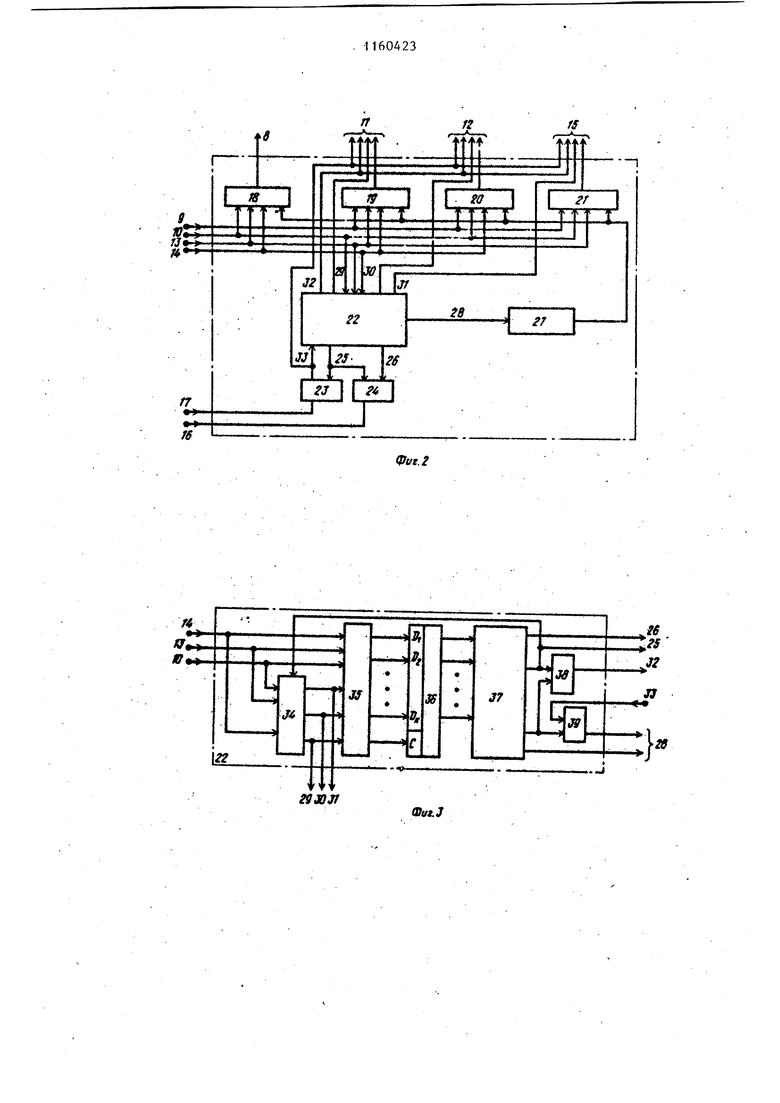

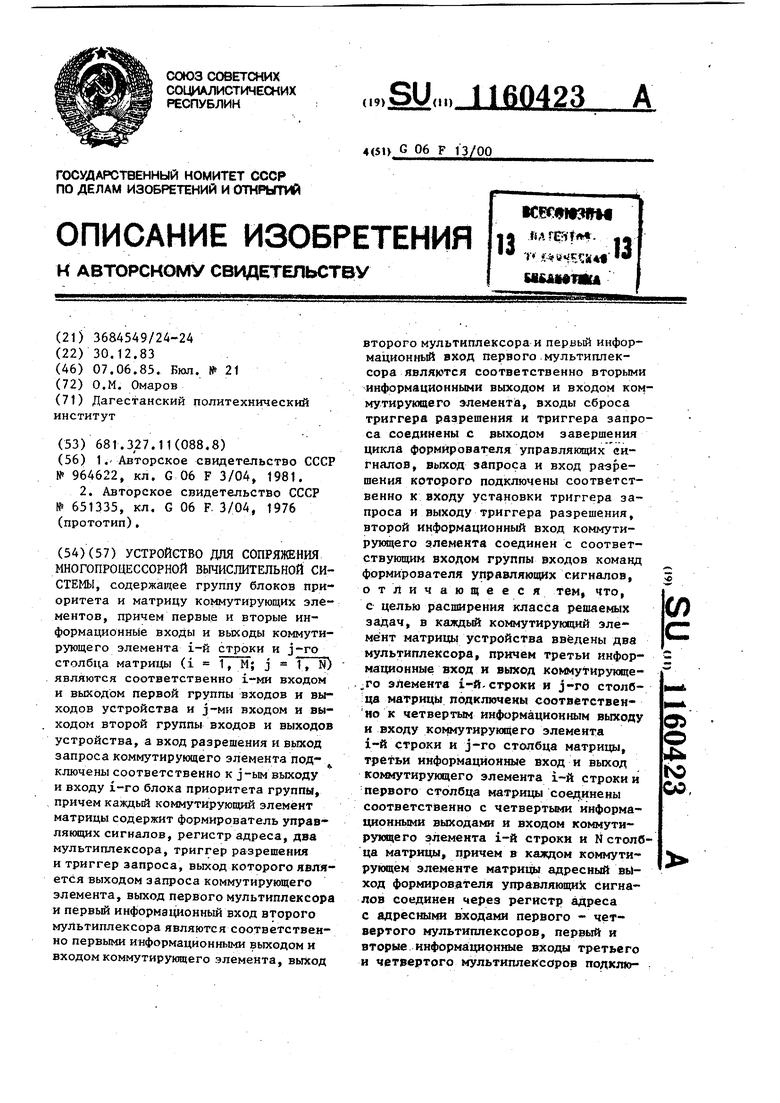

УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ МНОГОПРОЦЕССОРНОЙ ВЬГЧИСЛИТЕЛЬНОЙ СИСТЕМЫ, содержащее группу блоков приоритета и матрицу коммутирующих элементов, причем первые и вторые информационные входы и вькоды коммутирующего элемента i-й строки и j-ro столбца матрицы (г 1, М; j 1, N) являются соответственно i-ми входом и выходом первой группы входов и выходов устройства и j-MH входом и выходом второй группы входов и выходов устройства, а вход разрешения и выход запроса коммутирующего элемента подключены соответственно к j-ым выходу и входу i-ro блока приоритета группы, причем каждьй коммутирующий элемент матрицы содержит формирователь управляющих сигналов, регистр адреса, две мультиплексора, триггер разрешения и триггер запроса, выход которого является выходом запроса коммутирующего элемента, выход первого мультиплексора и первый информационный вход второго мультиплексора являются соответственно первыми информационными выходом и входом коммутирующего элемента, выход второго мультиплексора и первый информационный вход первого мультиплексора являются соответственно вторыми информационными выходом и входом коммутирующего элементна, входы сброса триггера разрешения и триггера запроса соединены с выходом завершения цикла формирователя управляющих сигналов, выход запроса и вход разрешения которого подключены соответственно к входу установки триггера запроса и выходу триггера разрешения, второй информационный вход коммутирукяцего элемента соединен с соответствующим входом группы входов команд формирователя управляющих сигналов, отличающееся тем, что, (Л с целью расширения класса решаемых задач, в каждый коммутирующий элес мент матриць устройства введены два мультиплексора, причем третьи информационные вход и выход коммутирующе. го элемента i-ft-строки и j-го столб ца матрицы подключены соответственно к четвертым информационным выходу а и входу коммутирующего элемента о и i-й строки и j-ro столбца матрицы, третьи информационные вход и выход isD ко№1утирукидего элемента i-й строки и 00. первого столбца матрицы соединены соответственно с четвертыми информационньши выходами и входом коммутирующего элемента i-й строки и N столбца матрицы, причем в каждом коммутирующем элементе матрицы адресный выход формирователя yпpaвляющиk Сигналов соединен через регистр адреса с адресными входами первого - четвертого мультиплексоров, первый и вторые информационные входы третьего и четвертого мультиплексоров подклкг- :

Изобретение относится к вычислительной технике и может быть использовано для организации обмена информацией между различными внешними устройствами и процессорами, а также между процессорами многопроцессорной вычислительной системы.

Известно устройство для сопряжения, содержащее матрицу коммутирующи элементов, причем вторые входы и выходы соответствующего блока согласойания интерфейсов первой группы и вторые вход и выход соответствующего блока согласования интерфейсов второй группы соединены соответственно с первыми выходами и входами и вторыми выходами и входами коммутирукяцего элемента соотве.тствующей строки и столбца матрицы, управляющие вход и выход которого подключены соответственно к соответствующим управляющим выходу и входу и 3.

Недостаток этого устройства состоит в низкой производительности

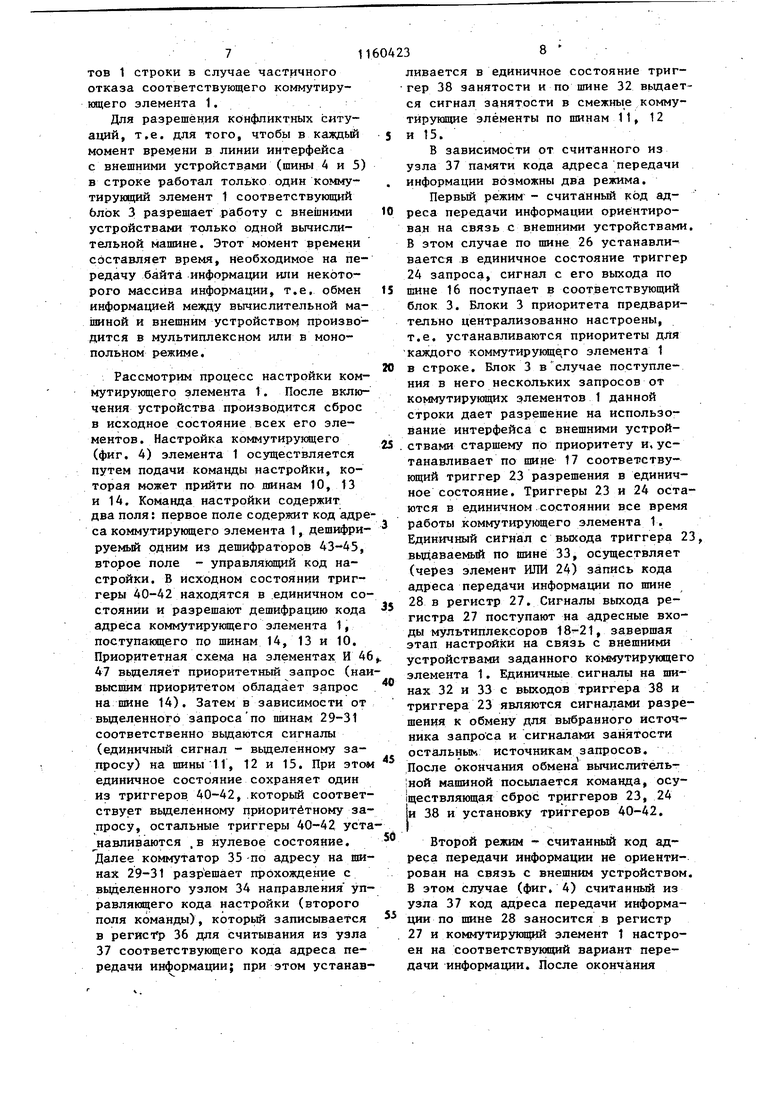

вычислительного комплекса, так как в устройстве невозможна организация обмена информацией между процессорами по принципу каждый с каждым,, а также в низкой надежности, так как « случае выхода из строя коммутирующих элементов связь с соответствующими внешними устройствами становится невозможной, Наиболее близким к изобретению по технической сущности является устройство для сопряжения, содержащее группу блоков приоритета, матрицу коммутирующих элементов и две группы блоков согласования интерфейсов, первые входы и выходы которых образуют соответственно первые и вто рые группы входов и выходов устройства, вторые и третьи входы и выходы i-ro блока согласования интерфейса первой группы (i 1, М) соединены соответственно с первыми информационными и первыми управляющими выходами и входами коммутирующих эле ментов i-й строки матрицы, приоритет ные входы и управляющие выходы которых подключены соответстванно к груп пам выходов и входов i-ro блока приоритета группы, вторые и третьи информационные входы и выходы коммутирующих элементов j-ro столбца матрицы (j 1, N) подключены соответственно к вторым и третьим вькодам и входам j-ro блока согласования интерфейсов второй группы, каждый коммутирующий элемент содержит две груп пы элементов И, формирователь управляющих сигналов, триггер разрешения, триггер запроса, регистр адреса и схему сравнения, причем выходы элементов И первой группы и первые входы элементов И второй группы соответственно образуют первые информационные вьгход и вход ком1 утирующего элемента, первые входы элементов И первой группы и выходы элементов И второй группы образуют соответственно вторые информационные вход и вьтхо коммутирующего элемента, вторые входы элементов И первой и второй групп соединены с первым выходом формирователя управляющих сигналов, первый и второй, входы которого соединены соответственно с выходом триггера запроса и управляющим выходом коммутирующего элемента и с выходом триггера разрешения, а второй выход с входами ceSpoca триггера разрешения и триггера запроса, входы установки которых соединены соответственно с приоритетным входом коммутирующего . элемента и выходом схемы сравнения, первый вход которой подключен к вы ходу регистра адреса, а второй вход к второму информационному входу коммутирующего элемента и третьему входу формирователя управляющих сигнало четвертым входом соединенного с выходами элементов И второй группы Недостаток известного устройства состоит в ограниченном классе решаемых задач из-за невозможности обмен между процессорами. Цель изобретения- расширениеклас- са решаемых згщач. Поставленная цель достигается тем что в устройство, содержащее группу блоков приоритета и матрицу коммутирующих элементов, причем первые и вторые информационные входы и выходы коммутирующего элемента i-й строки и j-ro столбца матрицы (i - 1, М; j 1, N) являются соответственно i-ми входом и выходом первой группы входов и выходов устройства и j-ми входом и выходом второй группы ВХОДО и выходов устройства, а вход разрешения и выход запроса коммутирукадего элемента подключены соответственно к j-ым выходу и входу i-ro блока приоритета группы, причем каждый коммутирукяций элемент содержит формирователь управляющих сигналов, регистр адреса, два мультиплексора, триггер разрешения и триггер запроса, выход которого является выходом запроса коммутиру ацего элемента,, выход первого мультиплексора и первый информационньй вход второго мультиплексора ЯВЛЯЮТС5} соответственно первыми информационными вьсходом и входом коммутирующего элемента, выход второго мультиплексора и первый информационный вход первого мультиплексора являются соответственно вторыми информационными выходом и входом коммутируйщего элемента, входы сброса триггера разрещения и триггера запроса соединены с- выходом завершения цикла формирователя управляющих сигналов выход запроса и вход разрешения которого подключены соответственно к входу установки триггера звпр:оса и выходу триггера разрешения, второй информациолный вход коммутирукяцего элемента соединен с соответс вующим входом группы входов команд формирователя управлякмцих сигналов, в каждый коммутирующий элемент матрищ 1 введены два мультиплексора, причем третьи информационные вход и выход коммутирующего элемента i-й строки и i-ro столбца матрицы подключены соответственно к четвертым информационным выходу и входу коммутирующего элемента i-й строки и (j-l)-ro столбца матрицы,, третьи информационные вход и выход коммутирующего элемента i-й строки и первого столбца матрицы соединены соответственно с четвертыми информа1Ц1онньми выходами и входом коммутирующего элемента 1-й строки и N столбца матрицы, причем в каждом коммутирующем элементе матрицы ад- ресный выход формирователя управляюцих сигналов соединен через регистр адреса с адресными входами первого четвертого мультиплексоров, первые и вторые информационные входы треть 511 его и четвертого мультиплексоров подключены соответственно к первому и второму информационным входам коммутирующего элемента, вторые информационные входы первого и второго мультиплексоров и третий информационный вход четвертого мультиплексоров соединены с третьим информационным входом коммутирукнцего элемента третьи информационные входы первого, второго и третьего мультиплексоров соединены с четвертым информациойным входом коммутирующего элементаj группа входов команд формирователя управляющих сигналов соединена с третьим и четвертым информационными входами коммутирующего элемента, выходы второго, третьего и четвертого мультиплексоров, выход триггера раз рещения, выход занятости и соответ ствующие выходы группы выходов эапрёта формирователя управляющих сигналов образуют соответственно второй, третий и четвертый информационные выходы коммутирующего элемента, вход установки триггера разрешения являе ся входом разрешения коммутирующего элемента, причем формирователь управ.пяквчих сигналов коммутирзгющего элемента содержит узел-приоритета, коммута:тор, регистр, узел постоянной памяти, триггер занятости и элемент ИЛИ, при этом группы информационных входов коммутатора и узла Приоритета соединены с группой входив команд формирователя, группа вы ходов узла приоритета является груп пой выходов запрета формирователя и соединена с группой адресных входов коммутатора, выход.которого подключен через регистр к входу узла по стоянной памяти, первый и второй вы ходы которого являйтся соответствен но выходом запроса и выходом завершения цикла формирователя, третий выход соединен с входом сброса триггера занятости и первым входом элемента ИДИ, второй вход которого является входом разрешения фегрмирователя, второй выход узла постоянной памяти соединен с входом .установки триггера занятости, вьпйэд которого является выходом занятости формирователя, четвертый выход узла постоянной памяти и выход элемента ИЛИ образуют адресный выход формирователя. На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг. 2 и 3 - функциональные схемы коммутирующего элемента и формирователя управляющих сигналов; на фиг.4 - блок-схема алгоритма функционирования устройства; на фиг.5 функциональная схема узла приоритета. Устройство содержит (фиг. 1) коммутирующие элементы 1 матрицы, группу 2 блоков 3 приоритета, шины 4 и 5 первых входа и выхода устройства, шины 6 и 7 вторых выхода и входа устройства, шины 8 и 9 первых выхо да и входа, шины 10 и 11 третьих входа и выхода, шины 12 и 13 четвертых выхода и входа, шины 14 и 15 вторых входа и выхода и шины 16 и 17 выхода запроса и входа разрешения коммутирующего элемента 1. Коммутирующий элемент 1 содержит (фиг. 2) первый, второй, третий и четвертый мультиплексоры 18-21, формирователь 22 управляющих сигналов, триггер 23 разрешения, триггер 24 запроса, шины 25 и 26 выходов завершения цикла и запроса формирователя 22, регистр 27 адреса, шина 28 адресного выхода, шины29-31 группы выходов запрета, шина 32 выхода занятости, шина 33 входа разрешения формирователя 22. Формирователь 22 управлякмдих сигналов содержит (фиг. 3) узел 34 приоритета, коммутатор 35, регистр 36, узел 37 постоянной памяти, триггер 38 занятости и элемент ШШ 39. Узел 34 приоритета содержит (фиг. 5) триггеры 40-42 направления обмена, дешифраторы 43-45 номера коммутирующего элемента 1, элементы И 46 и 46 и элемент ИЛИ 48. Устройство работает следующим образом. Организация связи между вычислительными машинами и внешними устройствами, вычислительными машинами между собой осуществляется путем настройки коммутирующих элементов 1 на различные варианты коммутации. Наличие связей коммутирующего элемента 1 в строке с соседними- (слева и справа) коммутирукицими элементами 1 позволяет при соответствующей настройке коммутирующих элементов 1 устанавливать связь потоков информации между вычислительными машинами комплекса и между вычислительными машинами и внешними устройствами через цепочки коммутирующих элемен71тов 1 строки в случае частичного отказа соответствующего ко11мутирующего элемента 1.. Для разрешения конфликтных ситуаций, т.е. для того, чтобы в каждый момент времени в линии интерфейса с внешними устройствами (шины 4 и 5) в строке работал только один коммутирующий элемент 1 соответствующий блок 3 разрешает работу с внешними устройствами только одной вычислительной машине. Этот момент времени составляет время, необходимое на передачу байта информации или некоторого массива информации, т.е. обмен информацией между вычислительной машиной и внешним устройством производится в мультиплексном или в монопольном режиме. Рассмотрим процесс настройки коммутирующего элемента 1. После включения устройства производится сброс в исходное состояние всех его элементов. Настройка коммутирукяцего (фиг. 4) элемента 1 осуществляется путем подачи команды настройки, которая может прийти по шинам 10, 13 и 14. Команда настройки содержит два поля: первое поле содержит код адре са коммутирующего элемента 1, дешифрируе в 1й одним из дешифраторов 43-45, второе поле - управляющий код настройки. В исходном состоянии триггеры 40-42 находятся в единичном состоянии и разрешают дешифрацию кода адреса коммутирующего элемента 1, поступакяц его по шинам 14, 13 и 10. Приоритетная схема на элементах И 46 47 вьделяет приоритетный запрос (наи высшим приоритетом обладает запрос на шине 14). Затем в зависимости от вьщеленного запросапо шинам 29-31 соответственно выдаются сигналы (единичный сигнал - вьщеленному запросу) на шины 11, 12 и 15. При этом единичное состояние сохраняет один из триггеров 40-42, который соответствует вьщеленному приоритетному запросу, остальные триггеры 40-42 уста навливаются ,в нулевое состояние. Далее коммутатор 35 -по адресу на шинах 29-31 разр ешает прохождение с выделенного узлом 34 направления управляющего кода настройки (второго поля команды), которьй записывается в регистр 36 для считывания из узла 37 соответствующего кода адреса передачи информации; при этом устанав3ливзется в единичное состояние триггер 38 занятости и по шине 32 вьщается сигнал занятости в смежные коммутирующие элементы по шинам 11, 12 и 15. В зависимости от считанного из узла 37 памяти кода адреса передачи информации возможны два режима. Первый режим - счита:нный код адреса передачи информации ориентирован на связь с внешними устройствами. В этом случае по шине 26 устанавливается в единичное состояние триггер 24 запроса, сигнал с его выхода по шине 16 поступает в соответствующий блок 3. Блоки 3 приоритета предварительно централизованно настроены, т.е. устанавливаются приоритеты для каждого коммутирукяце,го элемента 1 в строке. Блок 3 вслучае поступления в него нескольких запросов от коммутирующих элементов 1 данной строки дает разрешение на использование интерфейса с внешними устройствами старшему по приоритету и,устанавливает по шине 17 соответствующий триггер 23 разрешения в единичное состояние. Триггеры 23 и 24 остаются в единичном состоянии все время работы коммутирующего элемента 1. Единичный сигнал с выхода триггера 23, вьщаваемьй по пшнё 33, осуществляет (через элемент ИЛИ 24) запись кода адреса передачи информации по шине 28 в регистр 27. Сигналы выхода регистра 27 поступают на адресные входы мультиплексоров , завершая этап настройки на связь с внешними устройствами заданного коммутирующего элемента 1. Единичные сигналы на шинах 32 и 33 с выходов триггера 38 и триггера 23 являются сигналами разрешения к обмену для выбранного источника запроса и сигналами занятости остальные источникам запросов. После окончания обмена вычислитель;ной машиной посыпается команда, осу|ществляющая сброс триггеров 23, 24 и 38 и установку триггеров 40-42. Второй режим - считанный код адреса передачи информации не ориентирован на связь с внешним устройством. В этом случае (фиг, 4) считанный из узла 37 код адреса передачи информации по шине 28 заносится в регистр 27 и коммутирукяций элемент 1 настроен на соответствующий вариант передачи информации. После окончания обмена вычислительной машиной, осуществлякнцей настройку коммутирующего элемента, посылается команда, осуществляющая сброс триггера 39 коммутирующего элемента 1 и установку триггеров 40-42, Возможно подключение к одной вычислительной машине всех внешних устройств, в этом случае вычислитель ная машина направляет адрес за адресом коммутирующих элементов, устанавливая соответствующий маршрут для параллельной вьщачи информации во все внешние устройства или последова тельно подключая внешние устройства в режиме обмена.

Фиг.1 Таким образом, предлагаемое устройство позволяет организовать обмен информацией между вычислительными машинами по типу каждая с каждой, кроме того, одновременно организовать обмен между вычислительными машинами и внешними устройствами и вычислительных машин между собой, организовать обмен между вычислительными машинами и внешними устройствами через другие коммутирующие элементы, существенно расширяет класс решаемых задач, область его использоваваниА, повьш1ает надежность и производительность вычислительной сис-v темы.

29X31

t5

12

IDut.3

tycmotMim воеяоЛиов coc/nofftue 8cn f tMfanof tfemffffucmfa

оыЛемтх ff/n t/frfem/fotff 3ff/rfleco vdvdavff evtfmnr mf/rrgfa/ttA

ffi№t Kofa ffcc/rVofffrv / /Mttvcmp J7

Wrtftiff из ifJM Яко offflfca

neoeaottu tmtpqaftouvv vs/eyna. j fffafjfii

«y

Hem

tSfHfefewy

13Offirmoc/nt/

Ла

Усаю/в}вме$е91муц1 mpiateflffK r ooar

Cffffocayifetfflffgl

J,f4,39

Фиг. 5

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для сопряжения | 1981 |

|

SU964622A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для сопряжения | 1976 |

|

SU651335A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-06-07—Публикация

1983-12-30—Подача