тий и четвертый элементы НЕ и элемент ИЛИ, причем пятые входы и выходы каждого блока согласования интерфейсов соединены с соотзетствустдими вторыми управляющими входами и выходами устройства, 3 каждом коммутирующем блоке второй регистр -адреса выходом соединен с первым входом второй схемы сравнения, второй вход которой подключен к первому входу второго элемента И, выход второй схемы сравнения соединен с первым входом шестого элемента И, кыход которого соединен с единичным аходом второго триггера запроса, единичный выхо,ц которого соединен с первым входом седьмого элемента И, нулевой выход второго триггера запроса соединен с первым входом Bocaworo элемента И, выход которого соединен через третий элемент НЕ с втор1,|м входом шестого элемента И, третий вход которого соедмнен через четвертый элемент НЕ с нулевым входом второго триггера запросаS выходы четвертого и седьмого э 1аментов И соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого соединен с вторыми входами первого и второго элементов И, третий вход шестого элемента И и выход седьмого элемента И коммутирующего блока i-й строки и j-ro столбца матрицы подключены соответственно к шестым вы.ходу и входу i-ro блока согласования интерфейсов первой группы, единичный выход второго триггера запросов коммутирующего блока i-й строки и j-ro столбца матрицы подключен к шестому входу j-ro блока согласования интерфейсов второй группы, выход восьмого элемента И коммутирующего блока i-й строки и столбца матрицы подключен к вторым входам седьмого и восьмого элементов И коммутирующего блока (i-1)-й строки и J-ro столбца мат(рицы, шестой выход j-ro блока согласования интерфейсов второй группы соединен с вторыми входами седьмого и восьмого элементов И коммутирующего блока М-й строки и j-ro столбца матрицы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения | 1981 |

|

SU964622A1 |

| Устройство для сопряжения | 1976 |

|

SU651335A1 |

| Устройство для сопряжения | 1983 |

|

SU1118993A1 |

| Коммутационное устройство | 1985 |

|

SU1285486A1 |

| Устройство для сопряжения электронных вычислительных машин с внешними устройствами | 1985 |

|

SU1257655A1 |

| Устройство для сопряжения | 1990 |

|

SU1784984A1 |

| Устройство для сопряжения электронных вычислительных машин с внешними устройствами | 1985 |

|

SU1305699A2 |

| Устройство для сопряжения многопроцессорной вычислительной системы | 1983 |

|

SU1160423A1 |

| Устройство для сопряжения группы из М вычислительных машин с группой из К абонентов | 1986 |

|

SU1310830A1 |

| Устройство для сопряжения многопроцессорной вычислительной системы с внешними устройствами | 1984 |

|

SU1241245A2 |

Изобретение относится к вычислительной технике и может быть исползовано для построения систем обмена информацией между различными устройствами вычислительных комплексов.

Известно устройство для сопряжения, содержаиГее две группы блоков согласования интерфейсов, узел настройкк, содержащий блок управления и блоки приоритетов, а также матрицу коммутирующих элементов t 1

Недостатками данного устройства являются большие аппаратурные затраты, обусловленные наличием узла настройки и формирователя управляющих си налов в коммутирующих элементах,а также низкая надежность(Обусловленная тем, что отказ узла настройки может привести к отказу всего устройства,

Наиболее близким к предлагаемому по технической сущности является устройство для сопряжения, содержащее дав группы блоков согласования интерфейсов и матрицу коммутирующих

2

узлов, каждый из которых включает регистр адреса, схему сравнения, пять элементов И, триггер запроса,два элемента НЕ, причем первые и вторые входы и выходы каждого блока согласования интерфейсов соединены с соответствующими информационными и управляющими входами и выходами устройства, в каждом коммутирующем узле регистр адреса выходом соединен с первым входом схемы сравнения, второй вход которой подключен к первому входу первого элемента И, третьи выход и вход i-ro (i iT М) блока Согласования интерфейсов первой группь1, третьи выход и вход j-ro (j 1,N) блока согласования интерфейсов второй группы соединены соответственно с первым входом второго элемента И, выходом и входом первого элемента И и выходом второго элемента И коммутирующего узла i-й строки и j-ro столбца матрицы, единичный выход триггера запроса которого подклчен к четвертому -входу i-ro блока согласования интерфейсов первой группы. в каждом коммутирующем узле выход схе мы сравнения -соединен с первым входом третьего элемента И, выход которого соединен с единичным входом триггера запроса, единичный выход которого соединен с первым входом чет вертого элемента И,нулевой выход триг гера, запроса соединен с первым входом пятого элемента И, выход которого соединен через первый элемент НЕ с вт рым входом третьего элемента И,третий вход которого соединен через второй элемент НЕ с нулевым входом три1- гера запроса, выход четвертого элемента И соединен с вторыми входами первого и второго элементов И, третий входтретьего элемента И и выход четвертого элемента И коммутирующего узла i-й строки и j-ro столбца матрицы подключены соответственно к четвер тым выходу и входу j-ro блока согласования интерфейсов второй группы,выхсд пятого элемента.И коммутирующего узла i-й строки и j-ro столбца матрицы подключен к вторым входам чет вертого и пятого элементов И коммутирующего узла i-й строки и (j-l)-ro столбца матрицы, четвертый выход i-ro блока согласования интерфейсов первой группы соединен с вторыми входами че вертого и пятого элементов И коммутирующего узла i-й строки и N-ro стол бца матрицы, 8 указанном устройстве обмен информацией между,например, вычислитель ными машинами (ВМ) и внешними абонентами (ВА) осуществляется через устрой ство сопряжения по интерфейсу, обеспе чивающему передачу информационных и управляющих сигналов от ВМ к ВА и от ВА и ВМ по раздельным линиям .Интерфейс ВМ проходит по столбцам, а интер фейс ВА - по строкам матрицы коммутирующих узлов. Обмен информацией, например,между j-й ВМ и i-м ВА через блоки coi- ласования интерфейсов начинается с выдачи j-й ВМ адреса коммутирующего узла.и управляющего сигнала выборки, которые воспринимаются всеми коммутирующими узлами j-ro столбца коммутациЬнной матрицы. При этом код адреса сравнивается с содержимым регистра адреса на схеме сравнения. При сраанении адресов в одном из коммутирующих узлов j-ro столбца матрицы сигнал с триггера запроса выдается к I-му ВА. В ответ на сигнал запроса

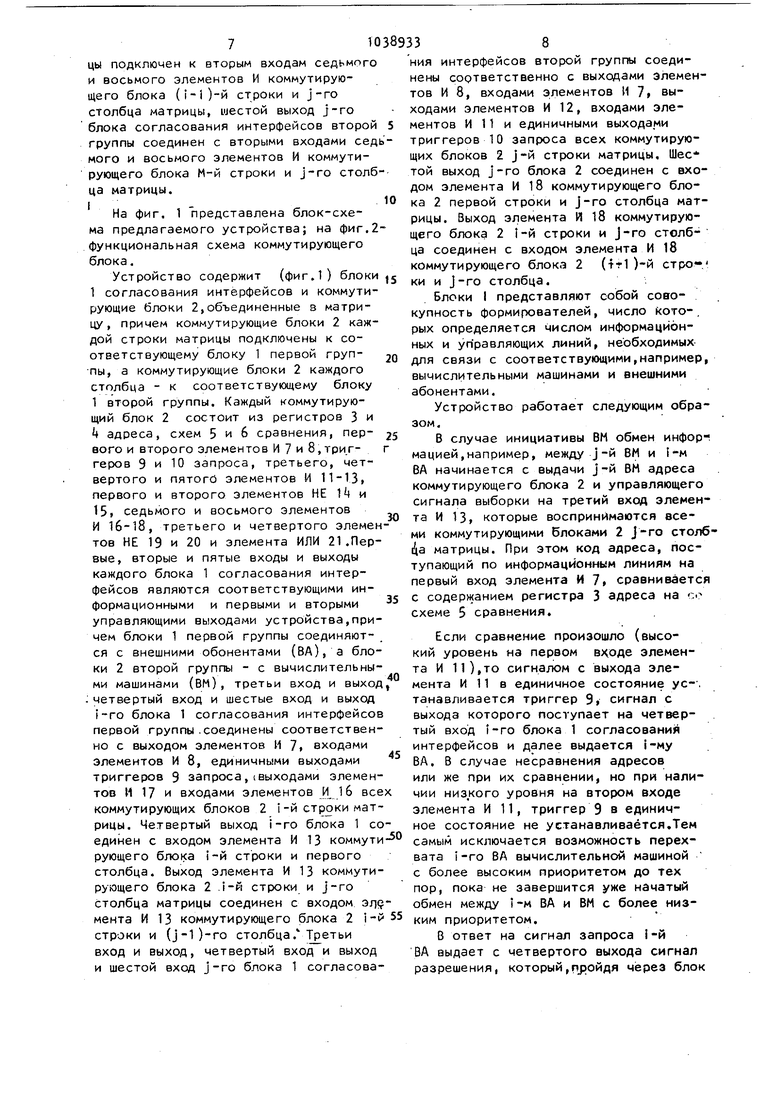

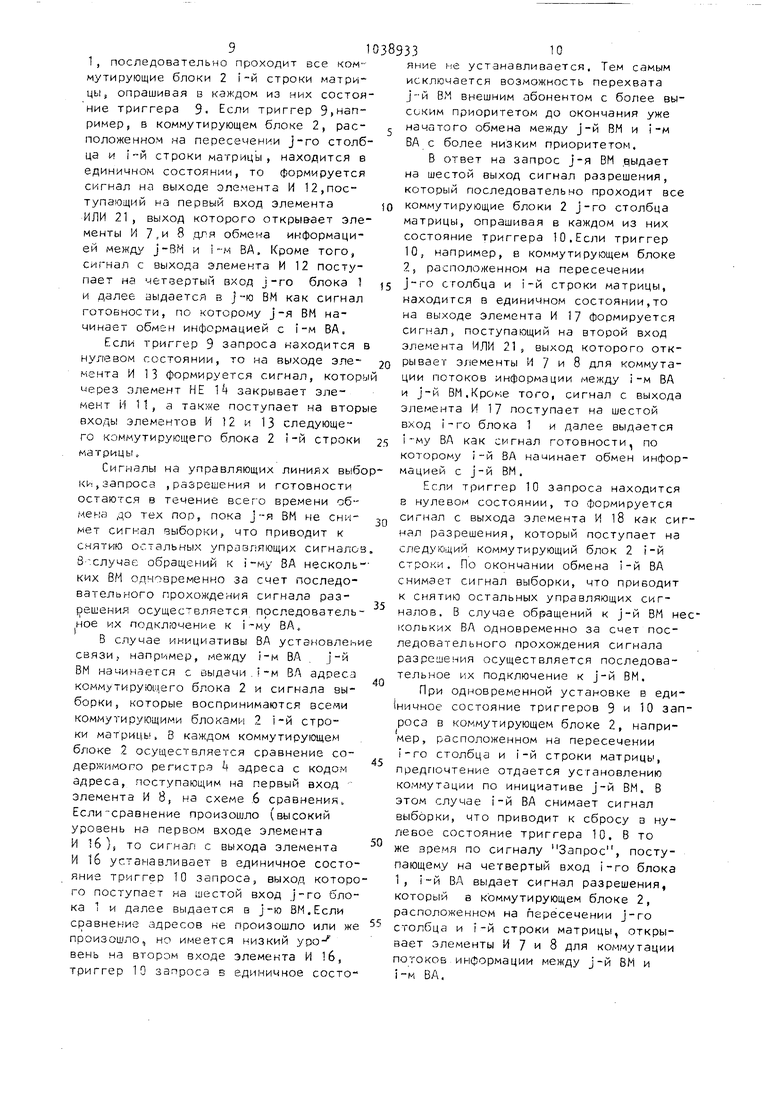

ки от УВВ, выставляя требование на обслуживание (ТРБ-А). Не обеспечивается также работа с различными пункi-й ВА выдает сигнал разрешения,который, пройдя через 1-и блок.согласования интерфейсов, последовательно проходит все коммутирующие узлы i-й строки матрицы, опрашивая в каждом из них состояние триггера запроса. . Таким образом, приоритет коммутирующих узлов в i-й строке матрицы определяется их местонахождением, чем ближе к i-й строке матрицы коммутирующий узел расположен к i-му блоку согласования интерфейсов,тем выше его приоритет, а следовательно, и приоритет соответствующей ВМ. Если триггер запроса в коммутирующем узле на пересечении j-ro столбца и i-й строки матрицы находится в единичном состоянии, то формируется сигнал готовности для выдачи в j-ю ВМ и открываются два элемента И для обмена / информацией между j-й ВМ и i-м ВА.По сигналу готовности j-я ВМ начинает обмен информацией с i-м ВА. Сигналы на управляющих шинах выборки, запроса, разрешения и готовности остаются в течение всего времени обмена. После окончания обмена j-я ВМ снимает сигнал выборки, что приводит к снятию сигнала запроса, поступающего на 1-й ВА, в свою очередь ВА снимает сигнал разрешения, что приводит к закрыванию элементов И выдачи информации и снятия сигнала готовности, поступающего с выбранного коммутирующего узла на j-ю ВМ. При необходимости обращения к нескольким ВА из одной ВМ последняя осуществляет последовательное подключение ВА за счет поочередной выдачи адресов необходимых ВА и вьтолнения соответствующих обменов C2l. Недостатком известного устройства является ограниченная область его применения, так как оно не обеспечивает работу с вычислительными машинами по инициативе внешних абонентов. Так, например,не обеспечивается работа с внешними .устройствами ЕС ЭВМ, которые для передачи второго байта состояния при монопольном режиме работы, а также для передачи очередного байта данных или первого и второго байта состояния при мультиплексном режиме начинают по своей инициативе последовательность сигналов выбортами управления, автоматизированными рабочими местами, удаленными терминалами и абонентами вычислительных сетей. Цель изобретения - расширение области применения устройства за счет работы с вычислительной машиной по инициативе внешних абонентов. Поставленная цель достигается тем что в устройство для сопряжения,содержащем две группы блоков согласования интерфейсов и матрицу коммутирующих блоков, каждый из которых вкл чает первый регистр адреса, первую схему сравнения, пять элементов И, n вый триггер запроса и два элемента НЕ, причем первые и вторые входы и выходы каждого блока согласования ин терфейсов соединены с соответствую1цими информационными и первыми управ ляющими входами и выходами устройства, в каждом коммутирующем блоке пер вый регистр адреса выходом соединен первым входом первой схемы сравнения второй вход кото.рой подключен к первому входу первого элемента И, трет выход и вход i-ro (i ,Н) блока со ласования интерфейсов первой группы третьи выход и вход J-ro ( ,N) бло ка согласования интерфейсов второй группы соединены соответственно с первым входом второго элемента И. выходом и входом первого элемента И и Bfa xofiOM второго элемента И коммутирующего блока i-й строки и j-ro столбца матрицы, единичный выход первого триггера запроса которого по ключен к четвертому входу j-ro блока согласования интерфейсов первой группы, в каждом коммутирующем блоке выход первой схемы сравнения соединен с первым входом третьего элемента И, выход которого соединен с единичным входом первого-три1- гера запроса, единичный выход которо го соединен с первым входом четвертого элемента И, нулевой выход первого триггера запроса соединен с пер вым входом пятого элемента И, выход которого соединен через первый элемент НЕ с вторым входом третьего элемента. И, третий вход которого сое динен через второй элемент НЕ с ну левым входом первого триггера запроса, третий вход третьего элемента И И выход четвертого элемента И к мутирующего блока i-й строки и j-ro столбца матрицы подключены соответственно к четвертым выходу и входу 3 j-ro блока согласования интерфейсов второй группы, выход пятого элемента И коммутирующего блока i-й строки и j-ro столбца матрицы подключен к вторым входам четвертого и пятого элементов И коммутирующего блока 1-й строки и (j-l)-ro столбца матрицы, четвертый выход i-ro блока согласования интерфейсов первой группы соединен с вторыми входами четвертого и пятого элементов И коммутирующего блока i-й строки и N-ro столбца матрицы, в каждый коммутирующий блок устройства введены второй регистр адреса, вторая схема сравнения, шестой седьмой и восьмой элементы И,второй триггер запроса, третий и четвертый элементы НЕ и элемент ИЛИ, причем пятые входы и выходы каждого блока согласования интерфейсов соединены с соответствующими вторыми управляощими входами и выходами устройства, в каждом коммутирующем блоке второй регистр адреса выходом соединен с первым входом второй схемы сравнения, второй вход которой подключен к первому входу второго элемента Mj выход второй схемы сравнения соединен с первым входом шее-того элемента И, выход которого соединен с единичным входом второго триггера запроса, единичный выход которого соединен с первым входом седьмого элемента И,нулевой выход второго триггера запроса соединен с первым входом восьмого элемента И,выход которого соединен через третий элемент НЕ с вторым входом шестогочэлемента И, третий вход которого соединен через четвертый элемент НЕ с нулевым входом второго триггера запроса, выходы четвертого и седьмого элементов И соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого соединен с вторыми входами первого и второго элементов И, третий вход шестого элемента И и выход седьмого элемента И коммутирующего блока i-й строки и j-ro столбца матрицы подключены соответственно к шестым выходу и входу I-го блока согласования интерфейсов первой группы, единичный выход второго триггера запросов коммутирующего блока i-й строки и j-ro столбца матрицы подклю g шестому входу j-ro блока согласования интерфейса второй группы,выход восьмого элемента И коммутирующего блока i-й строки и j-ro столбца матрицы подключен к вторым входам седьмого и восьмого элементов И коммутирующего блока (-1)-й строки и j-ro столбца матрицы, шестой выход j-ro блока согласования интерфейсов второй группы соединен с вторыми входами сед мого и восьмого элементов И коммутирующего блока М-й строки и j-ro столб ца матрицы. IНа фиг. 1 представлена блок-схема предлагаемого устройства; на фиг.2 функциональная схема коммутирующего блока. Устройство содержит (фиг.1) блоки 1 согласования интерфейсов и коммутирующие блоки 2,объединенные в матрицу, причем коммутирующие блоки 2 каждой строки матрицы подключены к соответствующему блоку 1 первой группы, а коммутирующие блоки 2 каждого столбца - к соответствующему блоку 1 второй группы. Каждый коммутирующий блок 2 состоит из регистров 3 и k адреса, схем 5 и 6 сравнения, первого и второго элементов И 7 и В.три.ггеров 9 и 10 запроса, третьего, четвертого и пятого элементов И 11-13 первого и второго элементов НЕ и 15 седьмого и восьмого элементов И 16-18, третьего и четвертого элемен тов НЕ 19 и 20 и элемента ИЛИ 21.Первые, вторые и пятые входы и выходы каждого блока 1 согласования интерфейсов являются соответствующими информационными и первыми и вторыми управляющими выходами устройства,причем блоки 1 первой группы соединяются с внешними обонентами (ВА), а блоки 2 второй группы - с вычислительными машинами (ВМ), третьи вход и выход четвертый вход и шестые вход и выход блока 1 согласования интерфейсов первой группы .соединены соответственно с выходом элементов И 7 входами элементов И В, единичными выходами триггеров 9 запроса,(Выходами элементов И 17 и входами элементов И 16 все коммутирующих блоков 2 i-и строки матрицы. Четвертый выход i-ro блока 1 со единен с входом элемента И 13 коммути рующего блока i-й строки и первого столбца. Выход элемента И 13 коммутирующего блока 2 .i-й строки и j-ro столбца матрицы соединен с входом эг( мента И 13 коммутирующего блока 2 i-й строки и (j-l)-ro столбца.Третьи вход и выход, четвертый вход и выход и шестой вход j-ro блока 1 согласования интерфейсов второй группы соединены соответственно с выходами элементов И 8, входами элементов И 7 выходами элементов И 12, входами элементов И П и единичными выходами триггеров 10 запроса всех коммутирующих блоков 2 j-й строки матрицы. Шее той выход j-ro блока 2 соединен с входом элемента И 18 коммутирующего блока 2 первой строки и j-ro столбца матрицы. Выход элемента И 18 коммутирующего блока 2 1-й строки и j-ro столбца соединен с входом элемента И 18 коммутирующего блока 2 (ftl )-й стро-. ки и j-ro столбца. Блоки I представляют собой совокупность формирователей, число ROTO-, рых определяется числом информационных и управляющих линий, необходимых для связи с соответствующими,например, вычислительными машинами и внешними абонентами. Устройство работает следующим образом. В случае инициативы ВМ обмен инфорг мацией,например, между j-и ВМ и i-M ВА начинается с выдачи j-й ВМ адреса коммутирующего блока 2 и управляющего сигнала выборки на третий вход элемента И 13 которые воспринимаются всеми коммутирующими Блоками 2 j-ro столб4а матрицы. При этом код адреса, поступающий по информационным линиям на первый вход элемента И 7, сравнивается с содержанием регистра 3 адреса на со схеме 5 сравнения. Если сравнение произошло (высокий уровень на первом входе элемента И 11),то сигналом с выхода элемента И 11 в единичное состояние ус-. танавливается триггер 9 сигнал с выхода которого поступает на четвертый вход I-го блока 1 согласования интерфейсов и далее выдается i-му ВА. В случае несравнения адресов или же при их сравнении, но при наличии уровня на втором входе элемента И 11, триггер 9 в единичное состояние не устанавливается.Тем самым исключается возможность перехвата i-ro ВА вычислительной машиной с более высоким приоритетом до тех пор, пока не завершится уже начатый обмен между i-м ВА и ВМ с более низким приоритетом. В ответ на сигнал запроса i-й ВА выдает с четвертого выхода сигнал разрешения, который,пройдя через блок 1, последовательно проходит все коммутирующие блоки 2 1-й строки матрицы, опрашивая в каждом из них состоя ние триггера 9. Если триггер 9 например, в коммутирующем блоке 2, расположенном на пересечении j-ro столб ца и строки матрицы, находится в единичном состоянии, то формируется сигнал на выходе элемента И 12,поступающий на первый вход элемента ИЛИ 21, выход которого откры&ает эле менты И 7, и 8 для обмема информацией J-BM и i-м ВА, Кроме того, сигнал с выхода элемента И 12 поступает на четвертый вход блока I и далее выдается в -ю ВМ как сигнал готовности, по которому j-я ВМ начинает обмен информацией с i-м ВА. Если триггер 9 запроса находится нулевом состоянии, то на выходе эле мента И 13 формируется сигнал, котор через элемент НЕ 1 закрывает элемент И 11, а также поступает на втор входы элементов И 12 и 13 следующего коммутирующего блока 2 1-й строки матрицы, Сигналы на управляющих линиях выб ки,запроса .разрещения и готовности остаются в течение всего времени обмена до тех пор, пока J-я ВМ не снимет сигнал выборки, что приводит к снятию остальных управляющих сигнало 8--.случае обращений к i-му ВА несколь ких ВМ одновременно за счет последовательного прохождения сигнала разрешения осуществляется последователь ное их подключение к ВА, В случае инициативы ВА устэновлеьи связи, например, между i-м ВА -й ВМ начинается с выдачи J-м ВА адреса коммутирующего блока 2 и сигнала выборки, которые воспринимаются всеми коммутирующими блоками 2 i-й строки матриць, В каждом коммутирующем блоке 2 осуществляется сравнение содержимого регистра k адреса с кодом адреса, поступающим на первый вход элемента И 8, на схеме .6 сравнения. Если сравнение произошло (высокий уровень на первом входе элемента И 1б )( то сигнал с выхода элемента И 1б устанавливает в единичное состояние триггер 10 запроса, выход которо го поступает на шестой вход .го блока 1 и далее выдается в j-ю ВМ.Если сравнение адресов не произошло или же произошло, но имеется низкий уровень на втором входе элемента И 1б, триггер 10 запроса в единичное состояние не устанавливается. Тем самым исключается возможность перехвата j-й ВМ внешним абонентом с более высоким приоритетом до окончания уже начатого обмена между j-й ВМ и i-м ВА с более низким приоритетом. В ответ на запрос j-я ВМ .рыдает на шестой выход сигнал разрешения, который последовательно проходит все коммутирующие блоки 2 j-ro столбца матрицы, опрашивая в каждом из них состояние триггера 10.Если триггер 10, например, в коммутирующем блоке 2, расположенном на пересечении столбца и строки матрицы, находится в единичном состоянии,то на выходе элемента И 17 формируется сигнал, поступающий на второй вход элемента ИЛИ 21, выход которого открывает элементы И 7 и 8 для коммутации потоков информации между i-м ВА и j-й ВМ.Кроме того, сигнал с выхода элемента И 17 поступает на шестой вход i-ro блока 1 и далее выдается 1-му ВА как сигнал готовности, по которому i-й ВА начинает обмен информацией с j-й ВМ. Если триггер 10 запроса находится в нулевом состоянии, то формируется cигнvaл с выхода элемента И 18 как сигнал разрешения, который поступает на следующий коммутирующий блок 2 I-и строки. По окончании обмена 1-й ВА снимает сигнал выборки, что приводит к снятию остальных управляющих си1- налов. В случае обращений к j-й ВМ нескольких ВА одновременно за счет последовательного прохождения сигнала разрешения осуществляется последовательное их подключение к j-й ВМ, При одновременной установке в единичное состояние триггеров 9 и 10 запроса в коммутирующем блоке 2, например, расположенном на пересечении -го столбца и i-й строки матрицы, предпочтение отдается установлению коммутации по инициативе j-й ВМ. В этом случае i-й ВА снимает сигнал выборки, что приводит к сбросу ЕЗ нулевое состояние триггера 10. В то же зремя по сигналу Запрос, поступающему на четвертый вход i-ro блока 1, ВА выдает сигнал разрешения, который в коммутирующем блоке 2, расположенном на пересечении j-ro столбца и 1-й строки матрицы, открывает элементы И 7 и 8 для коммутации потоков информации между j-й ВН и -м ВА,

Таким образом, предлагаемое устройство обеспечивает обмен информацией между вычислительными машинами и внешними абонентами по инициативе

ntiii niiii

1038933

8М или ВА. Это позволяет применять устройство для сопряжения в системах, решающих более широкие классы задач.

mill

Mill

(pus.i

Авторы

Даты

1983-08-30—Публикация

1982-03-05—Подача