Изобретение относится к электросвязи, конкретно к системам передачи и приема дискретных сообщений с асинхронным вводом и выводом информации, и может быть использовано в устройствах асинхронного сопряжения скоростей потоков на приемной стороне.

Целью изобретения является повышение степени ослабления временных флюктуаций тактового сигнала путем выделения постоянной составляющей управляющего сигнала.

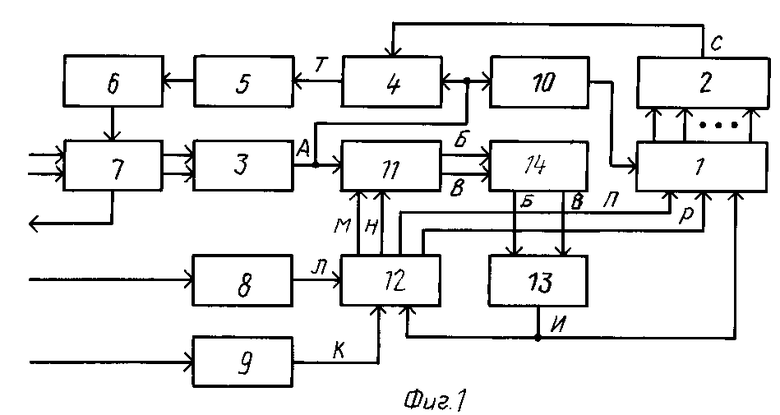

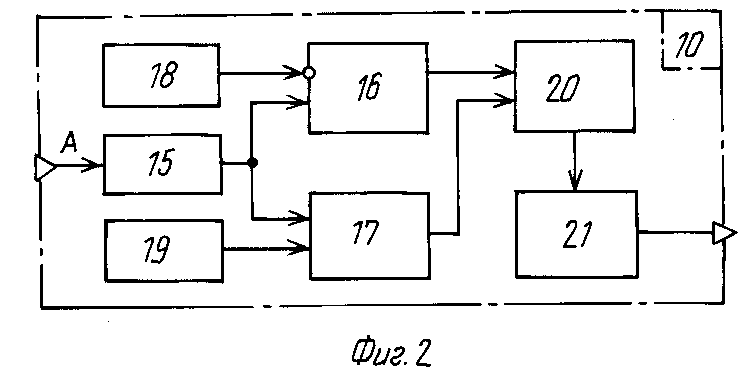

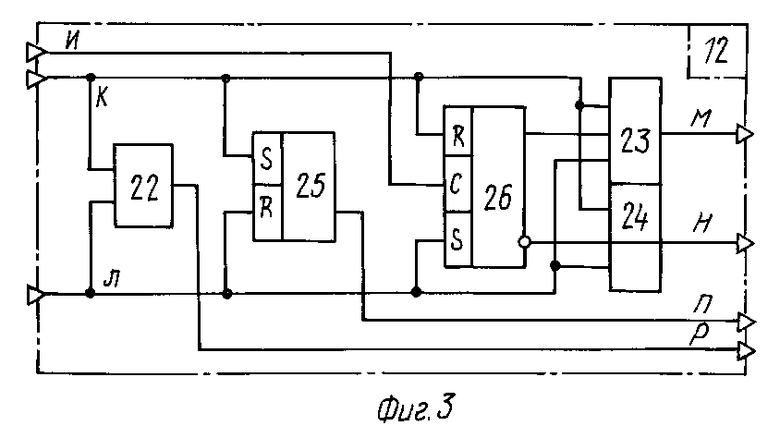

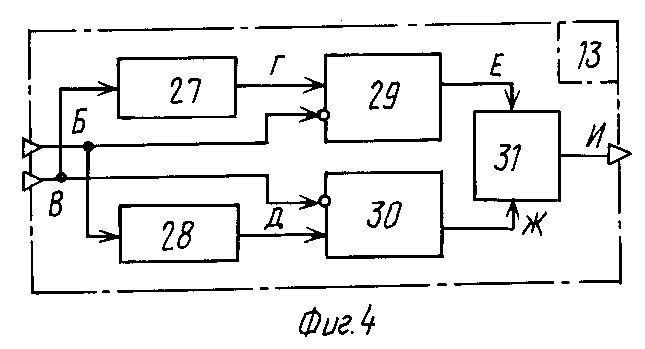

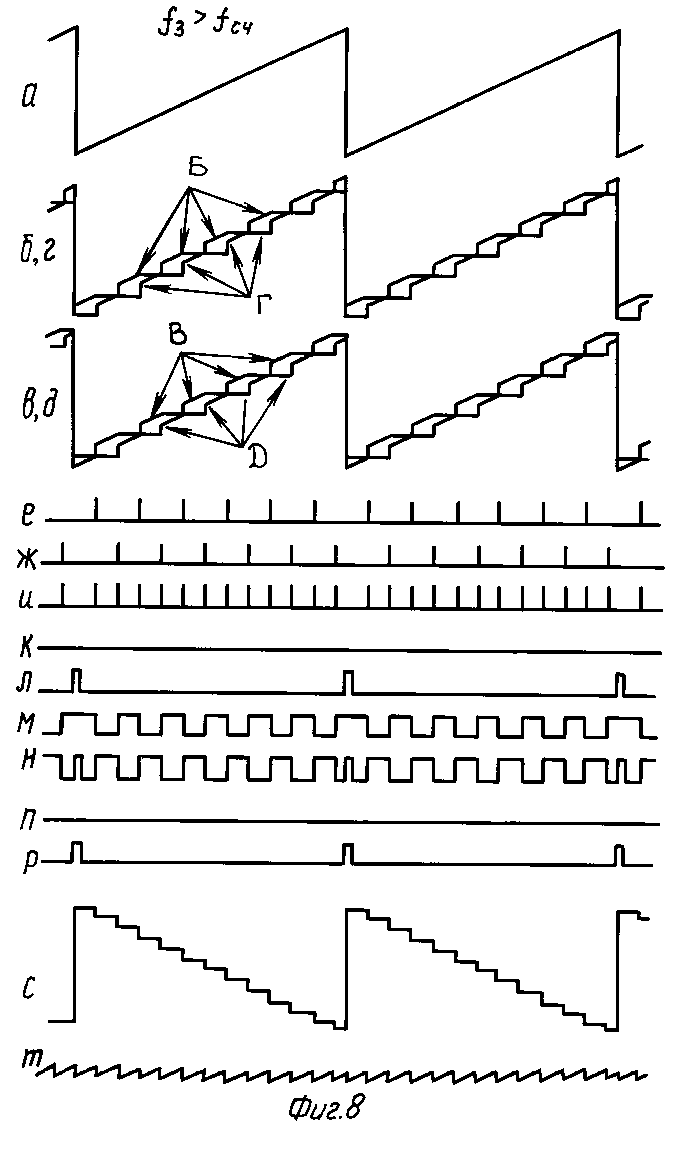

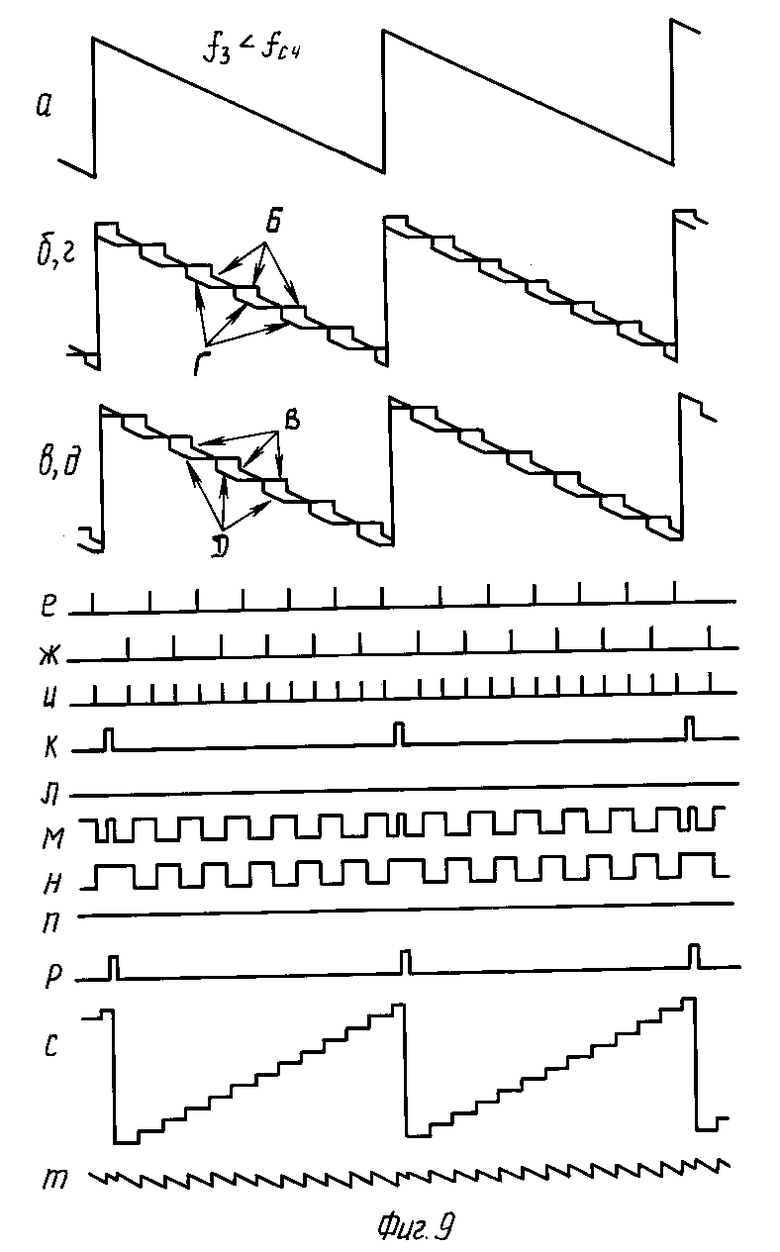

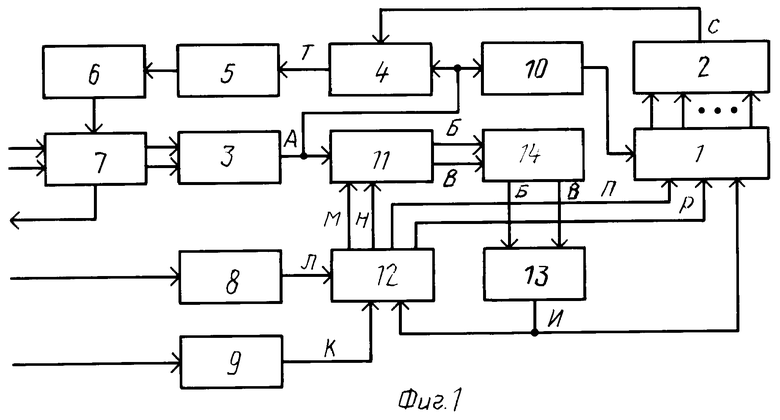

На фиг. 1 представлена структурная электрическая схема устройства фазовой автоподстройки частоты; на фиг. 2 - блока контроля; на фиг. 3 - блока управления; на фиг. 4 - блока квантования; на фиг. 5 - блока хранения напряжений; на фиг. 6 - блока динамической памяти; на фиг. 7 - реверсивного счетчика; на фиг. 8, 9 представлены временные диаграммы. поясняющие работу устройства фазовой автоподстройки частоты.

Устройство (фиг. 1) содержит реверсивный счетчик 1, цифроаналоговый преобразователь (ЦАП) 2, временной детектор 3, сумматор 4, фильтр 5 нижних частот (ФНЧ), генератор 6 тактовых импульсов, блок 7 динамической памяти, первый и второй ждущие мультивибраторы 8 и 9, блок 10 контроля, коммутатор 11, блок 12 управления, блок 13 квантования, блок 14 хранения напряжений.

Блок 10 контроля (фиг. 2) содержит дифференцирующую цепь 15, первый и второй компараторы 16 и 17, первый и второй источники 18 и 19 опорного напряжения, элемент ИЛИ 20, ждущий мультивибратор 21.

Блок 12 управления (фиг. 3) содержит первый, второй и третий элементы ИЛИ 22, 23 и 24, RS-триггер 25, T= триггер 26.

Блок 13 квантования (фиг. 4) содержит первый и второй преобразователи 27 и 28 уровня, первый и второй компараторы 29 и 30, элемент ИЛИ 31.

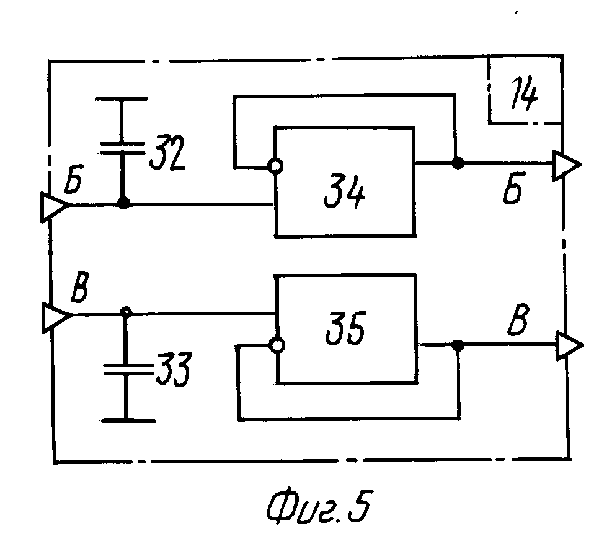

Блок 14 хранения напряжений (фиг. 5) содержит первый и второй конденсаторы 32 и 33, первый и второй усилители 34 и 35 постоянного тока.

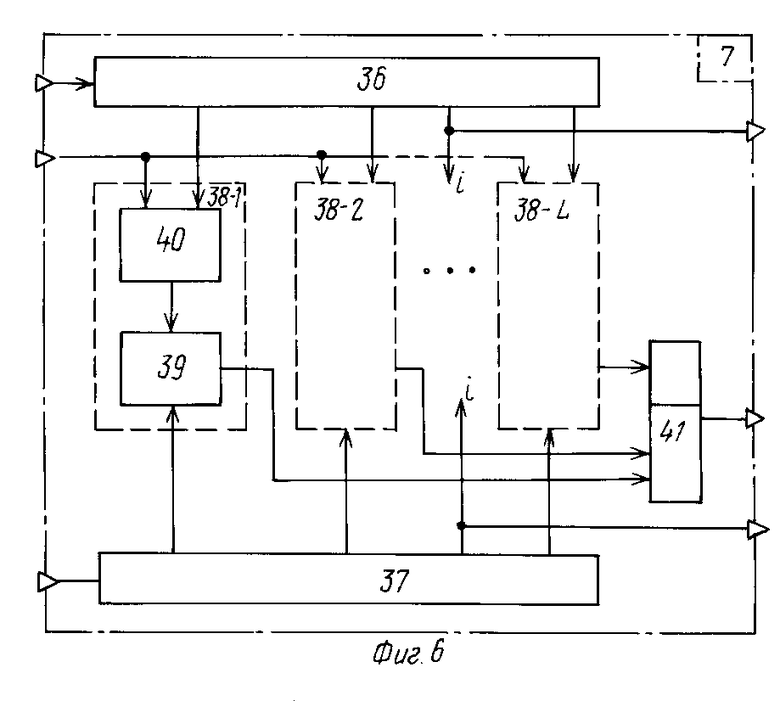

Блок 7 динамической памяти (фиг. 6) содержит распределитель 36 записи, распределитель 37 считывания, ячейки 38-1 38-L памяти, состоящие из элемента И 39, элемента 40 памяти, элемент ИЛИ 41.

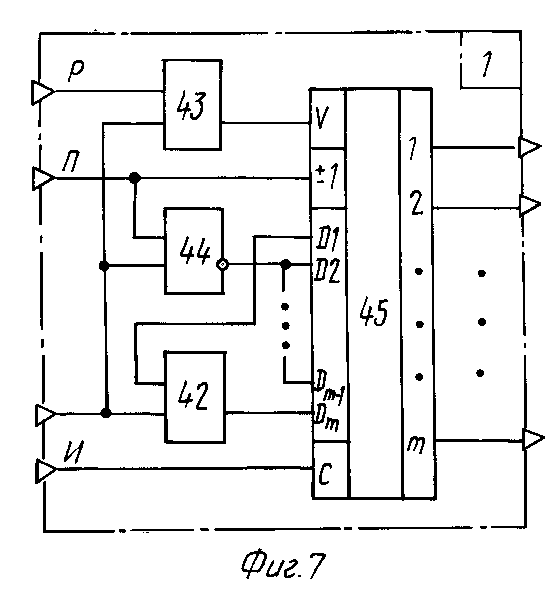

Реверсивный счетчик 1 (фиг. 7) содержит первый и второй элементы ИЛИ 42 и 43, элемент ИЛИ-НЕ 44, двоичный реверсивный счетчик 45.

Устройство фазовой автоподстройки частоты работает следующим образом.

При срыве автоподстройки частоты на вход блока 10 контроля поступает сигнал пилообразной формы с нарастающей (фиг. 8 а) или спадающей (фиг. 9 а) пологой частью и размахом от уровня логического "0" до уровня логической "1" и подается на вход дифференцирующей цепи 15, с выхода которой продифференцированный сигнал поступает на прямой вход первого компаратора 16 и на инверсный вход второго компаратора 17, На инверсном входе первого компаратора 16 установлено опорное напряжение, равное половине амплитуды положительных импульсов, а на прямом входе второго компаратора 17 - равное половине амплитуды отрицательных импульсов. При входном сигнале (фиг. 8 а) формируются импульсы на выходе второго компаратора 17 и поступают на второй вход элемента ИЛИ 20. При входном сигнале (фиг. 9 а) на выходе первого компаратора 16 формируются импульсы и поступают на первый вход элемента ИЛИ 20, С выхода элемента ИЛИ 20 импульсы поступают на вход ждущего мультивибратора 21 с перезапуском, который устанавливается в состояние логической "1" (сигнал аварии). Это состояние сохраняется, пока на вход блока поступает упомянутый сигнал.

При захвате автоподстройки размах пилообразной составляющей входного сигнала уменьшается в L раз, где L - количество ячеек памяти в блоке 7 динамической памяти. Импульсы на входах компараторов 16, 17 не достигают опорных напряжений, и на их выходах импульсы не формируются. Ждущий мультивибратор 21 возвращается в состояние логического "0", и на выходе блока 10 контроля прекращается формирование сигнала аварии (потенциал логического "0" свидетельствует об установившемся режиме).

Блок 12 управления предназначен для формирования управляющих сигналов и работает следующим образом.

На первый и второй управляющие входы блока 12 управления поступают импульсы положительного и отрицательного стаффинга соответственно (фиг. 8 и 9 к и л). С помощью первого элемента ИЛИ 22 названные импульсы объединяются и поступают на четвертый управляющий выход блока 12 управления (фиг. 8 и 9 p).

Импульсами положительного стаффинга RS-триггер 25 устанавливается в состояние логического "0", а импульсами отрицательного стаффинга - в состояние логической "1". С выхода RS-триггера 25 этот потенциал поступает на третий управляющий выход блока 12 управления (фиг. 8 и 9 п).

Импульсами положительного стаффинга T-триггер 26 устанавливается в начальное состояние логической "1", а импульсами отрицательного стаффинга - в состояние логического "0". Через второй и третий элементы ИЛИ 23 и 24 названные импульсы проходят на первый и второй управляющие выходы блока. В промежутках между названными импульсами на первых и вторых входах второго и третьего элементов ИЛИ 23 и 24 присутствуют потенциалы логического "0", а T= триггер 26 осуществляет подсчет импульсов (деление частоты на два), поступающих на C-вход (фиг. 8 и 9 и). С прямого и инверсного выходов T-триггера 26 через второй и третий элементы ИЛИ 23 и 24 соответственно импульсы поступают на соответствующие (первый и второй) управляющие выходы блока 12 управления (фиг. 8 и 9 м, н).

Блок 13 квантования предназначен для формирования уровней квантования входного сигнала, формирования импульсов при переходе мгновенного значения входного сигнала с одного уровня квантования на другой и работает следующим образом.

На первый и второй входы блока 13 квантования поступают входные сигналы (фиг. 8 и 9 б и в) и подаются на инверсные входы первого и второго компараторов 29 и 30 и на входы второго и первого преобразователей 28 и 27 уровня. С помощью преобразователей 27 и 28 уровня осуществляется смещение входного сигнала на один уровень квантования в сторону отрицательных значений и с их выходов поступают на прямые входы первого и второго компараторов 29 и 30 (фиг. 8 и 9). Если отличие входных сигналов не более одного уровня квантования, на прямых входах обоих компараторов 29, 30 потенциалы ниже, чем на инверсных, а на выходах - потенциалы логического "0" (фиг. 8 и 9 е, м). При отличии входных сигналов более чем на один уровень квантования, на входе компаратора с меньшим уровнем входного сигнала разность потенциалов обратная указанной выше, а на выходе его формируется потенциал логической "1". После уменьшения отличия входных сигналов до значения, меньшего одного уровня квантования, на выходах обоих компараторов 29, 30 устанавливаются потенциалы логического "0". Отсюда видно, что при каждом превышении разности входных сигналов значения одного уровня квантования на выходе одного из компараторов (компаратора с меньшим уровнем входного сигнала) формируется импульс положительной полярности длительностью, равной времени превышения указанной разности. Упомянутые импульсы с выходов компараторов 29, 30 поступают на одноименные входы элемента ИЛИ 31, с помощью которого объединяются в один поток и поступают на выход блока 13 квантования (фиг. 8 и 9 и).

Блок 14 хранения напряжений предназначен для поочередного запоминания уровней квантования входного сигнала и работает следующим образом.

Входной сигнал поступает на первый и второй входы блока 14 хранения напряжений поочередно (фиг. 8 и 9 б, в). Предположим, что в рассматриваемом временном интервале сигнал поступает на первый вход блока 14. Входным напряжением заряжается конденсатор 32, а с помощью усилителя 34 постоянного тока, включенного по схеме повторителя напряжения, сигнал передается на первый выход блока 14 хранения напряжений (фиг. 8 и 9 б). В следующем временном интервале входной сигнал поступает на второй вход блока, заряжает конденсатор 33 и через усилитель 35 постоянного тока, включенный по схеме повторителя напряжения, передается на второй выход блока 14 (фиг. 8 и 9 б). На конденсаторе 32 сохраняется напряжение, которое имел входной сигнал в момент переключения на второй вход, и через повторитель 34 напряжение поступает на первый вход блока (фиг. 8 и 9 б). В следующем временном интервале сигнал поступает на первый вход блока. На конденсаторе 33 сохраняется напряжение, которое имел входной сигнал в момент переключения на первый вход, и через повторитель 35 напряжение поступает на второй выход блока 14 хранения напряжений (фиг. 8 и 9 в). Далее все повторяется.

Блок 7 динамической памяти предназначен для переноса информационного сигнала с тактовой частоты записи fз на тактовую частоту считывания fсч путем исключения из него в процессе записи и считывания имеющихся в нем импульсов (положительного или отрицательного стаффинга) и синхросигнала и работает следующим образом.

На вход распределителя 36 записи поступает последовательность тактовых импульсов записи (fз). Эта последовательность содержит только импульсы, совпадающие по времени с теми символами цифрового сигнала, которые необходимо перенести на частоту считывания (fсч), а импульсы, совпадающие с исключаемыми символами цифрового сигнала (например, с символами синхросигнала), из тактовой последовательности исключены, т. е. образуется пауза.

В любом тактовом интервале формируется импульс только на одном из выходов распределителя 36 записи. В следующем тактовом интервале импульс формируется на следующем выходе и т. д., до последнего выхода. В следующем тактовом интервале импульс формируется на первом выходе, и этот процесс повторяется. Во время паузы в последовательности входных тактовых импульсов импульс, сформированный на одном из выходов, на следующий выход не продвигается. Дальнейшее продвижение импульса по выходам возобновляется по окончании паузы.

Аналогично работает распределитель 37 считывания. Отличие состоит только в том, что на его вход тактовые импульсы поступают непрерывно, т. е. без пауз.

Импульсы, формируемые распределителем 36 записи, используются для управления процессом записи цифрового сигнала в ячейки памяти, который поступает на первые (информационные) входы элементов 40 памяти всех ячеек 38 памяти. Запись символов цифрового сигнала в ячейки 38 памяти осуществляется в том же порядке, как и формирование импульсов на выходах распределителя записи. Символы, совпадающие с паузами в тактовой последовательности записи, в ячейки памяти не записываются.

С выхода элемента 40 памяти символ цифрового сигнала поступает на первый вход элемента И 39, при поступлении на второй вход которого импульса считывания названный символ проходит на его выход, т. е. на выход соответствующей ячейки 38 памяти. Считывание символов цифрового сигнала из ячеек памяти осуществляется в том же порядке, как и формирование импульсов на выходах распределителя 37 считывания. Считываемые символы цифрового сигнала объединяются с помощью элемента ИЛИ 41 и поступают на выход блока 7 динамической памяти.

Реверсивный счетчик 1 предназначен для подсчета входных импульсов.

При наличии на втором входе реверсивного счетчика 1 потенциала логического "0" двоичный реверсивный счетчик 45 осуществляет подсчет импульсов, поступающих на его C-вход. Направление счета и потенциалы на всех mD-входах задаются потенциалом, поступающим на третий вход реверсивного счетчика 1. При наличии потенциала логической "1" на D-входах устанавливается логическая комбинация вида 00...0 и счет идет на увеличение числа, а при логическом "0" - комбинация вида 11...1 и счет идет на уменьшение числа. Импульсами, поступающими с четвертого входа реверсивного счетчика 1 через второй элемент ИЛИ 43 на V-вход двоичного реверсивного счетчика 45, осуществляется предварительная запись упомянутой выше комбинации в счетчик.

При наличии на втором входе реверсивного счетчика 1 потенциала логической "1" на m-1 младших D-входов поступает комбинация вида 00...0, а на m-й D-вход - потенциал логической "1". Двоичный реверсивный счетчик 45 переводится в режим предварительной записи, и на его выходы передается комбинация вида 10...0.

Коммутатор 11 предназначен для поочередной коммутации входного сигнала на два выхода.

При наличии на первом входе коммутатора 11 потенциала логической "1", на втором - логического "0", сигнал коммутируется на первый выход, при обратных значениях управляющих потенциалов - на второй выход, а при логической "1" на обоих входах - на оба выхода коммутатора 11.

Временной детектор 3 предназначен для формирования пропорциональных временному сдвигу входных импульсов и работает следующим образом.

Импульсами, поступающими на S-вход, триггер устанавливается в состояние логической "1", а поступающими на R-вход - в состояние логического "0". Отсюда ясно, что на выходе триггера формируются импульсы длительностью, равной временному сдвигу входных импульсов, а на выходе сглаживающей цепи - усредненное значение напряжения, пропорциональное указанному сдвигу.

Устройство фазовой автоподстройки частоты работает при номинальных значениях тактовых частот записи и считывания, определяемых выражением fз.ном= fсч.ном+ +fсл.ном, где fсл.ном - номинальное значение частоты следования служебных символов (например, синхросигнала, вставок и пр.). Причем последовательность тактовых импульсов содержит только импульсы, совпадающие по времени с теми символами цифрового сигнала, которые необходимо перенести на частоту считывания (например, с информационными символами), а импульсы, совпадающие с исключаемыми символами цифрового сигнала (например, символами синхросигнала, вставок и пр., т. е. служебными символами), из тактовой последовательности исключены, т. е. образуется пауза. Описанная последовательность тактовых импульсов поступает на второй вход блока 7 динамической памяти, на первый вход которого поступает информационный сигнал. На третий вход поступает непрерывная последовательность тактовых импульсов считывания с частотой fсч. Так как fз>fсч, то временной интервал между моментами записи и считывания изменяется после каждого считывания на Δ t=Tз - Tсч, где Tз= 1/fз, Tсч=1/fсч, на эту же величину изменяется временной сдвиг между импульсами на втором и третьем выходах блока 7 динамической памяти.

Названные импульсы поступают на первый и второй входы временного детектора 3. Временной интервал между импульсами на втором и третьем выходах блока 7 динамической памяти изменяется по линейному закону в следующих пределах: в установившемся (рабочем) режиме на величину Tсч, а при срыве автоматической подстройки на величину LTсч, где L - количество ячеек памяти в блоке 7 динамической памяти. В тех же пределах изменяется длительность импульсов на выходе RS-триггера, временного детектора 3, а усредненное значение напряжения на выходе временного детектора 3 изменяется от уровня логического "0" до уровня логической "1", спадает и снова нарастает и т. д., т. е. изменяется по пилообразному закону с периодом 1/|fз-fсч-fсп| в установившемся режиме (фиг. 8 и 9 а) и L/|fз-fсч-fсп| при срыве автоподстройки.

Указанный сигнал с выхода временного детектора 3 поступает на первый вход сумматора 4, с выхода которого через ФНЧ 5 поступает на вход генератора 6 тактовых импульсов, состоящего из последовательно соединенных усилителя постоянного тока, генератора, управляемого напряжением, и компаратора. Тактовые импульсы с выхода генератора 6 тактовых импульсов поступают на третий вход блока 7 динамической памяти. Описанные выше блоки являются аналоговой петлей автоматической подстройки частоты.

При включении устройства до момента захвата или после срыва автоподстройки регулирование осуществляется по аналоговой петле, так как блок 10 контроля формирует сигнал аварии (потенциал логической "1"), которым реверсивный счетчик 1 устанавливается в состояние, при котором на его выходах формируется комбинация вида 10...0. Эта комбинация поступает на входы ЦАП 2, а на его выходе формируется постоянный потенциал, равный среднему значению диапазона изменения выходного сигнала, и поступает на второй вход сумматора 4. В сумматоре на этот потенциал накладывается сигнал, поступающий на его первый вход. Суммарный сигнал через ФНЧ 5 поступает на вход генератора 6 тактовых импульсов. Полоса ФНЧ 5 выбирается из условия обеспечения необходимой полосы захвата устройства, что обеспечивает малое время вхождения в синхронизм (малое время захвата). Уменьшению времени вхождения в синхронизм способствует постоянный потенциал, формируемый ЦАП 2, который через сумматор 4 и ФНЧ 5 поступает на вход генератора 6 тактовых импульсов, устанавливая его частоту в середину диапазона перестройки.

После вхождения устройства в режим синхронизма (автоподстройки частоты) пилообразный сигнал на выходе временного детектора 3 уменьшается в L раз, а на выходе блока 10 контроля формируется потенциал логического "0", которым разрешается работа реверсивного счетчика 1.

Импульсы отрицательного или положительного стаффинга поступают на входы первого или второго ждущих мультивибраторов 8, 9 соответственно. Эти мультивибраторы формируют импульсы длительностью, равной времени перезаряда конденсаторов 32, 33, расположенных в блоке 14 хранения напряжений, от одного экстремального значения до другого. Упомянутые импульсы (фиг. 8 и 9 к, л) поступают на второй или первый управляющие входы блока 12 управления соответственно, устанавливая RS-триггер 25 и T-триггер 26 в исходное состояние, а также проходят на первый, второй и четвертый управляющие входы блока 12 управления через соответствующие элементы ИЛИ 22, 23 и 24 (фиг. 8 и 9 м. н. р). Под действием импульсов (фиг. 8 и 9 м. н.) коммутатор 11 пропускает входной сигнал на оба выхода (фиг. 8 и 9 в), которые поступают на входы блока 14 хранения напряжений.

По окончании импульса (фиг. 8 и 9 к или л) T-триггер 26 начинает счет импульсов (деление на два), поступающих на C-вход. С прямого и инверсного выходов этого триггера импульсы через соответствующие элементы ИЛИ 23 и 24 поступают на первый и второй выходы блока 12 управления (фиг. 8 и 9 м, н) соответственно. Так как эти импульсы противофазны, то коммутатор 11 коммутирует входной сигнал на первый и второй выходы поочередно (фиг. 8 и 9 б, в), которые проходят через блок 14 хранения напряжений и поступают на одноименные входы блока 13 квантования. Один из них имеет постоянное значение, а другой изменяется. При изменении этого сигнала на величину одного уровня квантования на выходе блока 13 квантования формируется импульс (фиг. 8 и 9 и), которым изменяется значение числа в реверсивном счетчике 1 на (-1) или (+1), в зависимости от того, импульсы положительных или отрицательных вставок поступают на соответствующий вход устройства, и T-триггер 26 устанавливается в противоположное состояние. При этом изменяются значения сигналов (фиг. 8 и 9 м, и) на противоположные, переключается коммутатор 11. Постоянный и изменяющийся сигналы на выходах блока 14 хранения напряжений меняются местами. При изменении изменяющегося сигнала на величину одного уровня квантования на выходе блока 13 квантования формируется импульс (фиг. 8 и 9 и) и описанный выше процесс повторяется. Каждым импульсом (фиг. 8 и 9 и) значение числа на выходе реверсивного счетчика 1 изменяется на единицу. Текущее число с выхода реверсивного счетчика 1 поступает на входы ЦАП 2, на выходе которого формируется ступенчатый сигнал (фиг. 8 и 9 с), он поступает на второй вход сумматора 4. Этот сигнал складывается в сумматоре с сигналом (фиг. 8 и 9 а), и суммарный сигнал (фиг. 8 и 9 т) с выхода сумматора через ФНЧ 5 поступает на вход генератора 6 тактовых импульсов, управляя его частотой. Амплитуда пилообразных импульсов на выходе сумматора 4 в 2 m/L раз меньше амплитуды пилообразных импульсов на первом выходе (А), что уменьшает временные флюктуации тактовых импульсов во столько же раз. Кроме того, частота импульсов в 2 m/L раз выше, поэтому они более эффективно сглаживаются ФНЧ 5, что также способствует уменьшению временных флюктуаций тактовых импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство фазовой автоподстройки частоты | 1991 |

|

SU1811020A1 |

| Устройство фазовой автоподстройки частоты | 1991 |

|

SU1826135A1 |

| УСТРОЙСТВО ЦИФРОВОЙ ФАЗОВОЙ АВТОМАТИЧЕСКОЙ ПОДСТРОЙКИ ЧАСТОТЫ | 1991 |

|

RU2013862C1 |

| Многоканальный интерфейс | 1990 |

|

SU1751774A1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1990 |

|

RU2024194C1 |

| Устройство для дельта-модуляции | 1983 |

|

SU1132359A1 |

| АДАПТИВНЫЙ ЛАЗЕРНЫЙ ДОПЛЕРОВСКИЙ ЛОКАТОР | 1990 |

|

RU2012013C1 |

| Универсальный дельта-кодек | 1982 |

|

SU1078612A1 |

Использование: в электросвязи, конкретно в системах передачи и приема дискретных сообщений с асинхронным вводом и выводом информации, в устройствах асинхронного сопряжения скоростей цифровых потоков на приемной стороне. Сущность изобретения: устройство содержит реверсивный счетчик 1, цифроаналоговый преобразователь 2, временной детектор 3, сумматор 4, фильтр 5 нижних частот, генератор 6 тактовых импульсов, блок 7 динамической памяти, первый и второй ждущие мультивибраторы 8 и 9, блок 10 контроля, коммутатор 11, блок 12 управления, блок 13 квантования, блок 14 хранения напряжений. Устройство обеспечивает повышение степени ослабления временных флюктуаций тактового сигнала путем выделения постоянной составляющей управляющего сигнала. 4 з.п. ф-лы, 9 ил.

Авторы

Даты

1994-06-15—Публикация

1991-07-22—Подача