(S) АНАЛОГОВОЕ ЗАПОНИНАЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифровой записи-воспроизведения цифровой информации | 1990 |

|

SU1788521A1 |

| Устройство для цифровой записи воспроизведения речевой информации | 1988 |

|

SU1573470A1 |

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ РЕЧЕВОЙ ИНФОРМАЦИИ | 1992 |

|

RU2008728C1 |

| Устройство для измерения средних значений нестационарных сигналов | 1985 |

|

SU1337784A1 |

| Устройство для дискретной записи и воспроизведения функций | 1981 |

|

SU982034A1 |

| Устройство для магнитной записи-воспроизведения звуковых сигналов | 1989 |

|

SU1712957A1 |

| Устройство для регистрации сейсмических сигналов | 1989 |

|

SU1681288A1 |

| Устройство для воспроизведения служебной информации многоканального аналогового магнитографа | 1978 |

|

SU698041A1 |

| ЦИФРОВОЙ МАГНИТОФОН | 1992 |

|

RU2054715C1 |

| Устройство для контроля параметров магнитофона | 1984 |

|

SU1144150A1 |

Изобретение относится к вычислительной технике, в частности к анал говым запоминающим устройствам, и может быть использовано для запоминания непрерывных аналоговых сигналов . Известно аналоговое запоминающее устройство для запоминания диск ретных значений аналоговых непрерыв ных сигналов, характеризующееся тем что в качестве аналоговых запоминающих элементов в нем использованы конденсаторы, которые в режиме записи поочередно через ключи подключаются к источнику входного сигнала на время, соответствующее шагу квантования. В хранения -инфо мации все конденсаторы отключены. В режиме воспроизведения конденсато ры, в том же масштабе времени пооче редно подключаются к выходному повторителю. А в режиме стирания все конденсаторы закорочены tl3. Недостатком устройства является низкая точность воспроизведения записываемой информации. В известное устройство, с целью уменьшения погрешностей, возникающих в процессе воспроизведения при коммутации элементов памяти,в цепь. обратной связи усилителей-повторителей воспроизведения введены корректирующие . Несмотря на указанные меры по повышению точности воспроизведения записываемой информации, недостатки известных устройств полностью не устраняются. Эти устройства воспроизводят записываемый непрерывный сигнал в форме ступенчатой аппроксимации, для дальнейшего использования которого приходится приводить его .к исходному виду« т.е. сглажи- . вать (, интегрировать). Интегрирование ступенчатой функции напротяжении всего периода воспроизведе- :

ния .способствует накоплению npi- ч решностей.

Наиболее близким по технической сущности является устройство, которое содержит группу запоминающих конденсаторов, выходной усилитель постоянного тока и корректирующую цепь, включающую резисторы, конденсаторы, ключ, дополнительный усилитель. Источник входного сигнала через ключ подключен к входу выходного усилителя, в цепь обратной связи которого подключены через ключи группа запоминающих конденсаторов,а также корректирующая .цепь., причем выход выходного усилителя подключен к входу дополни ельного усилителя через элемент связи, например резистор, а вход выходного усилителя подключен к выходу дополнительного усилителя через элемент связи, например конденсатор, в цепь обратной связи дополнительного усилителя подключены параллельно соединенные конденсатор, резистор и ключ З.

Запись информации в устройстве производится путем поочередного подключения запоминающих конденсаторов к источнику входного сигнала. При этом также заряжаются паразитные емкости. В период хранения информации ключ в цепи обратной связи дополнительного усилителя замыкается, что обеспечивает разряд паразитных емкостей и восстановление машинных нулей усилителей. В режиме воспроизведения этот ключ опять размыкается и в цепь обратной связи выходного усилителя подключается корректирующая Цепь, которая препятствует разряду запоминающих конденсаторов, которые поочередно подключаются к выходному усилителю. Это приводит к уменьшению инструментальной погрешности, возникающей в процессе воспроизведения записанной информации.

Недостатком известного устройства несмотря на то, что точность воспроизведения записанной информации несг колько увеличивается, является сохранение существенных погрешностей в форме выходного сигнала, т.е. все еще низкая точность, так как воспроизводится не сам входной сигнал, а лишь его ступенчатая аппроксимация.

Другой недостаток устройства - уз кая область его применения. При проведении различных вычислений, например при вычислении рекурентных

функций, возникает необходимость, производить одновременно запись новой информации и воспроизведение ранее записанной в одном блоке памяти, что

упрощает организацию вычислительного процесса, способствует повышению точности аналоговых вычислений.

Это устройство не позволяет одновременно проводить запись, воспроизведение и стирание информации, т.е. обладает низкой оперативностью. Цель изобретения - повышение точности устройства и расширение области его применения за счет одновреS менного осу1 |ествления записи, воспроизведения и стирания информации.

Поставленная цель достигается тем, что в аналоговое запоминающее устройство, содержащее первый блок

памяти, первый вход которого соединен с входом устройства, второй, третий и четвертый входы первого блока памяти соединенысоответст- венно с первым, вторым -и третьим выходами блока управления, шину записи и шину выбора шага квантования, соединенные с входами блока управления, введены второй блок памяти, дифференциальный усилитель, первый и второй ключи, первый и второй интеграторы, повторитель напря хения и сумматор, выход которого соединен с выходом устройства, входы сумматора соединены . соответственно с выходами интеграторов и выходом повторителя напряжения, вход которого подключен к одному из входов дифференциального усилителя, входы интеграторов соединены с выходами ключей, первые входы которых соединены с выходом дифференциального усилителя, входы которого соединены с выходами блоков памяти, вторые входы ключей соединены с четвертым выходом блока управления, первый вход второго блока памяти соединен с входом устройства, пятый, шестой и седьмой выходы блока управления соединены соответственно с вторым, третьим и четвертым входами второго блока памяти.

0

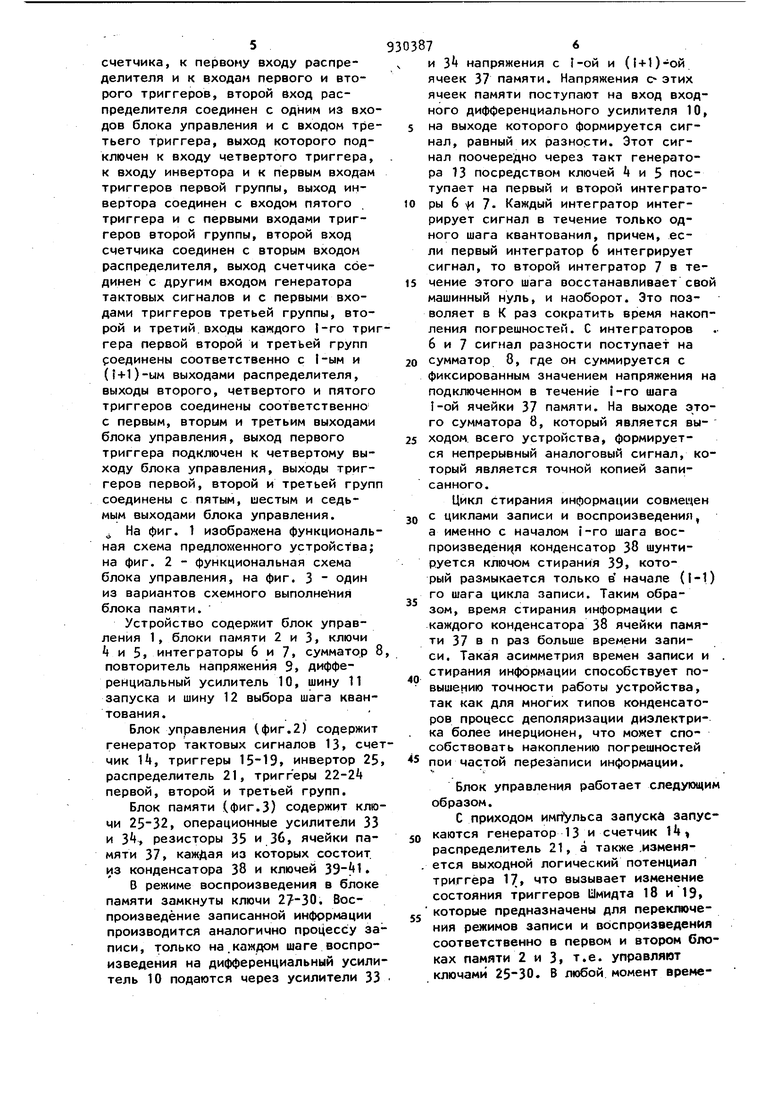

Блок управления содержит счетчик, распределитель, первую, вторую и третью группы триггеров, инвертор, первый, второй, третий, чет. вертый и пятый триггеры и генератор

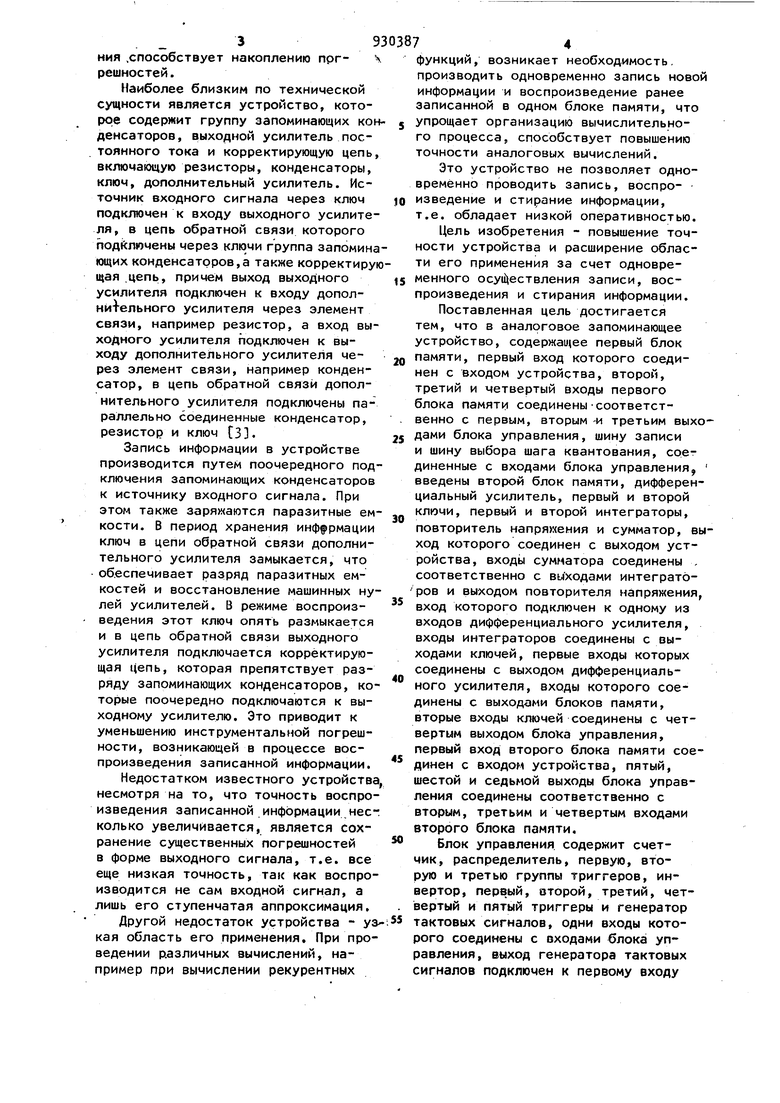

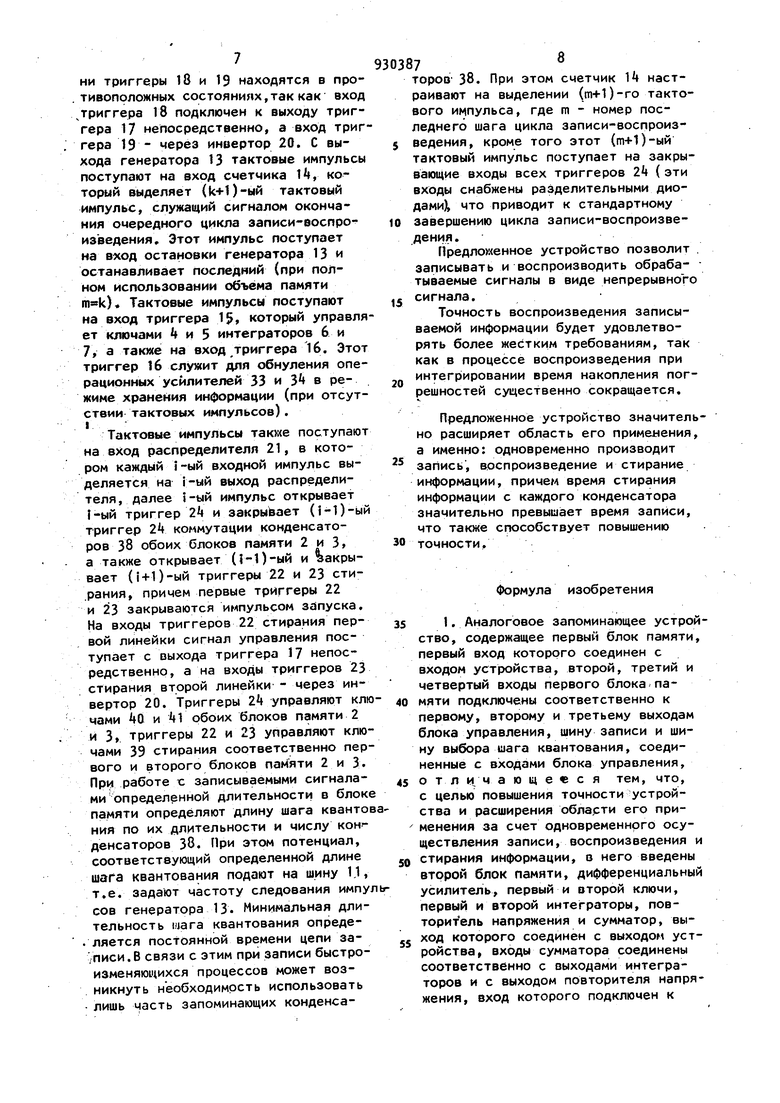

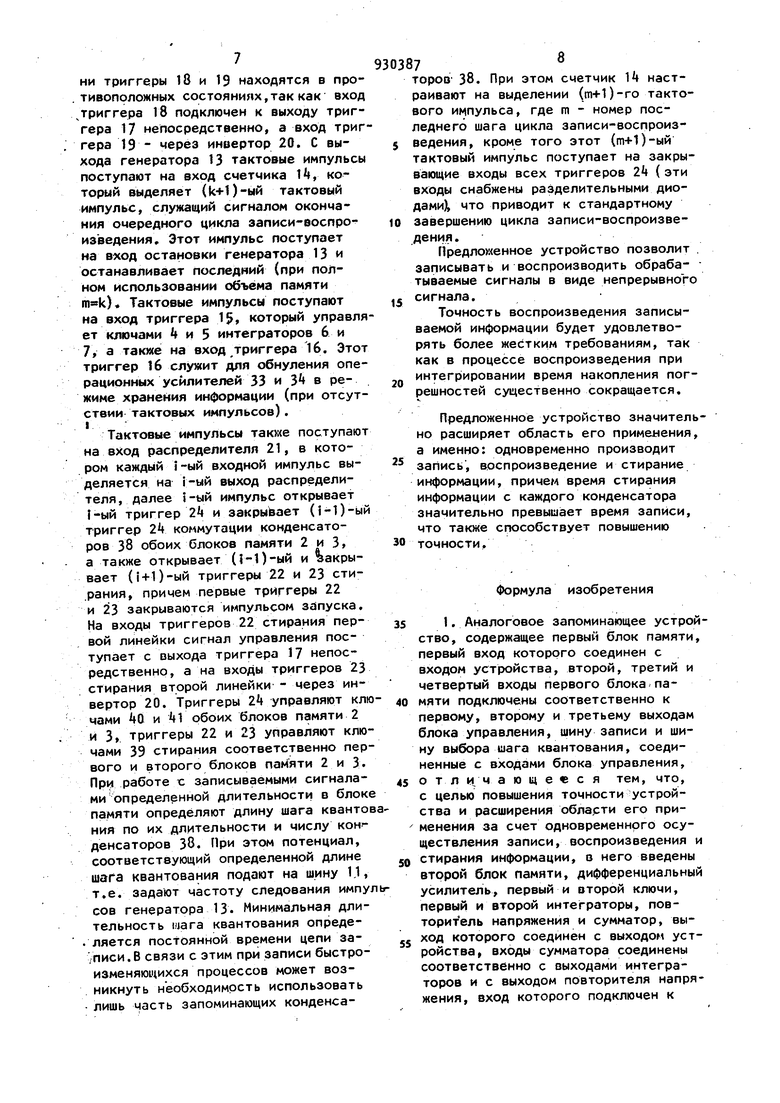

5 тактовых сигналов, одни входы которого соединены с входами блока управления, выход генератора тактовых сигналов подключен к первому входу счетчика, к первому входу распределителя и к входам первого и второго триггеров, второй Вход распределителя соединен с одним из входов блока управления и с входом третьего триггера, выход которого подключен к входу четвертого триггера, к входу инвертора и к первым входам триггеров первой группы, выход инвертора соединен с входом пятого триггера и с первыми входами триггеров второй группы, второй вход счетчика соединен с вторым входом распределителя, выход счетчика соединен с другим входом генератора тактовых сигналов и с первыми входами триггеров третьей группы, второй и третий входы каждого 1-го триг гера первой второй и третьей групп соединены соответственно с 1-ым и (+1)-ым выходами распределителя, выходы второго, четвертого и пятого триггеров соединены соответственно с первым, вторым и третьим выходами блока управления, выход первого триггера подключен к четвертому выходу блока управления, выходы три1- геров первой, второй и третьей групп соединены с пятым, шестым и седьмым выходами блока управления. На фиг. 1 изображена функциональная схема предлох енного устройства; на фиг. 2 - функциональная схема блока управления, на фиг. 3 - один из вариантов схемного выполнения блока памяти. Устройство содержит блок управления 1, блоки памяти 2 и 3, ключи j и 5 интеграторы 6 и 7. сумматор 8 повторитель напряжения Э дифференциальный усилитель 10, шину 11 запуска и шину 12 выбора шага квантования. Блок управления (фиг.2) содержит генератор тактовых сигналов 13 сче чик Н, триггеры 15-19, инвертор 25 распределитель 21, триггеры 22-24 первой, второй и третьей групп. Блок памяти (фиг.З) содержит клю чи 25-32, операционные усилители 33 и 3, резисторы 35 и Зб, ячейки памяти 37, каждая из которых состоит, из конденсатора 38 и ключей В режиме воспроизведения в блоке памяти замкнуты ключи 27-30. Воспроизведение записанной информации производится аналогично процессу за писи, только на.каждом шаге воспроизведения на дифференциальный усили тель 10 подаются через усилители 33 и З напряжения с 1-ой и (1 + 1)-ой ячеек 37 памяти. Напряжения ячеек памяти поступают на вход входного дифференциального усилителя 10, на выходе которого формируется си|- нал, равный их разности. Этот сигнал поочередно через такт генератора 13 посредством ключей и 5 поступает на первый и второй интеграторы 6 «fi 7- Каждый интегратор рирует сигнал в течение только одного шага квантования, причем, если первый интегратор 6 интегрирует сигнал, то второй интегратор 7 в течение этого шага восстанавливает свой машинный нуль, и наоборот. Это позволяет в К раз сократить время накопления погрешностей. С интеграторов 6 и 7 сигнал разности поступает на сумматор 8, где он суммируется с фиксированным значением напряжения на подключенном в течение i-ro шага 1-ой ячейки 37 памяти. На выходе этого сумматора 8, который является выходом всего устройства, формируется непрерывный аналоговый сигнал, который является точной копией записанного. Цикл стирания информации совмещен с циклами записи и воспроизведения, а именно с началом 1-го шага воспроизведен1 я конденсатор 38 шунтируется ключом стирания 39, который размыкается только в начале (1-1) го шага цикла записи. Таким образом, время стирания информации с каждого конденсатора 38 ячейки памяти 37 в п раз больше времени записи. Такая асимметрия времен записи и . стирания информации способствует повышению точности работы устройства, так как для многих типов конденсаторов процесс деполяризации диэлектрика более инерционен, что может способствовать накоплению погрешностей пои частой перезаписи информации. Блок управления работает следующим образом. С приходом импульса запуска запускаются генератор 13 и счетчик k распределитель 21, а также .изменяется выходной логический потенциал триггера 17, что вызывает изменение состояния триггеров Шмидта 18 и 19, которые предназначены для переключения режимов записи и воспроизведения соответственно в первом и втором блоках памяти 2 и 3, т.е. управляют ключами 25-30. В любой момент аренени триггеры 18 и 19 находятся в про. тивоположных состояниях,так как вход триггера 18 подключен к выходу триггера 17 непосредственно, а вход триг гера 19 - через инвертор 20. С выхода генератора 13 тактовые импульсы поступают на вход счетчика k, который выделяет {k+1)-ый тактовый импульс, служащий сигналом окончания очередного цикла записи-воспроизведения. Этот импульс поступает на вход остановки генератора 13 и останавливает последний (при полном использовании объёма памяти msk) Тактовые импульсы поступают на вход триггера 1, который управля ет ключами k и S интеграторов 6 и 7, а такие на входдриггера 16. Этот триггер 16 служит для обнуления операционных усилителей 33 и З в режиме хранения информации (при отсутствии тактовых импульсов). I Тактовые импульсы поступают на вход распределителя 21, в котором каждый i-ый входной импульс выделяется на 1-ый выход распределителя, далее i-ый импульс открывает 1-ый триггер и закрывает (|-1)-ый триггер 24 коммутации конденсаторов 38 обоих блоков памяти 2 и 3, а также открывает (1-1)-ый и закрывает (1+1)-ый триггеры 22 и 23 стирания, причем первые триггеры 22 и 23 закрываются импульсом запуска. На входы триггеров 22 стирания первой линейки сигнал управления поступает с выхода триггера 17 непосредственно, а на входы триггеров 23 стирания второй линейки - через инвертор 20. Триггеры 2 управляют кл чами 40 и 41 обоих блоков памяти 2 и 3, триггеры 22 и 23 управляют клю чами 39 стирания соответственно пер вого и второго блоков памяти 2 и 3. При работе с записываемыми сигналами определенной длительности в блок памяти определяют длину шага кванто ния по их длительности и числу кон денсаторов ЗЗ. При этом потенциал, соответствующий определенной длине шага квантования подают на шину 1.1, т.е. задают частоту следования импу сов генератора 13. Минимальная длительность шага квантования опреде. ляется постоянной времени цепи за/писи.В связи с этим при записи быстроизменяющихся процессов может возникнуть необходимость использовать лишь часть запоминающих конденса7торов 38. При этом счетчик 14 настраивают на выделении (т+1)-го тактового импульса, где m - номер последнего шага цикла записи-воспроизведения, кроме того этот (т+1)-ый тактовый импульс поступает на закрывающие входы всех триггеров 24 ( эти входы снабжены разделительными диодами), что приводит к стандартному завершению цикла записи-воспроизведения. Предложенное устройство позволит . записывать и воспроизводить обраба- тываемые сигналы в виде непрерывного сигнала. Точность воспроизведения записываемой информации будет удовлетворять более жестким требованиям, так как в процессе воспроизведения при интегрировании время накопления noi- решностей существенно сокращается. Предложенное устройство значительно расширяет область его применения, а именно: одновременно производит запись, воспроизведение и стирание информации, причем время стирания информации с каждого конденсатора значительно превышает время записи, что также способствует повышению точности. Формула изобретения 1. Аналоговое запоминающее устройство, содержащее первый блок памяти, первый вход которого соединен с входом устройства, второй, третий и четвертый входы первого блока памяти подключены соответственно к первому, второму и третьему выходам блока управления, шину записи и шину выбора шага квантования, соединенные с входами блока управления, отличающееся тем, что, с целью повышения точности устройства и расширения области его применения за счет одновременного осуществления записи, воспроизведения и стирания информации, в него введены второй блок памяти, дифференциальный усилитель, первый и второй ключи, первый и второй интеграторы, повторитель напряжения и сумматор, выход которого соединен с выходом устройства, входы сумматора соединены соответственно с выходами интеграторов и с выходом повторителя напряжения, вход которого подключен к

одному из входов дифференциального усилителя, входы интеграторов сое динены с выходами ключей, первые вхо ды которых соединены с выходом дифференциального усилителя, входы которого соединены с выходами блоков памяти, вторые входы ключей соединены с четвертым выходом блока управления, первый вход второго блока памяти соединен с входом устройства, пятый, шестой и седьмой выходы блока управлений - соответственно с вторым, третьим и четвертым входами второго блока памяти.

3038710

и к первым входам триггеров первой группы, выход инвертора соединен с входом пятого триггера и с первыми входами триггеров второй группы, второй вход счетчика соединен с вторым

входом распределителя, выход счет. чика другим входом генератора тактовых сигналов и с первыми входами триггеров третьей группы, второй

to и третий входы каждого J-ro триггера первой, второй и третьей групп соединены соответственно с 1-ым и (1-|-1)-ым выходами распределителя, выходы второго, :четвертого и пятого

J5 триггеров, соединены соответственно с первым, вторым и третьим выходами блока управления, выход первого триггера подключен к четвертому выходу блока управления, выходы триггеров

2р первой, второй и третьей групп соединены с пятым, шестым и седьмым выходами блока управления.

Источники информации, принятые во внимание при экспертизе

3foff

Авторы

Даты

1982-05-23—Публикация

1979-12-17—Подача