п- 10

15

20

25

12431

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении цифровых устройств различного назначения при повышенных требованиях к 5 их надежности.

Целью изобретения является расширение частотного диапазона за счет мажоритарного выбора входных сигналов различной, в TOW числе изменяю щейся, частоты. .

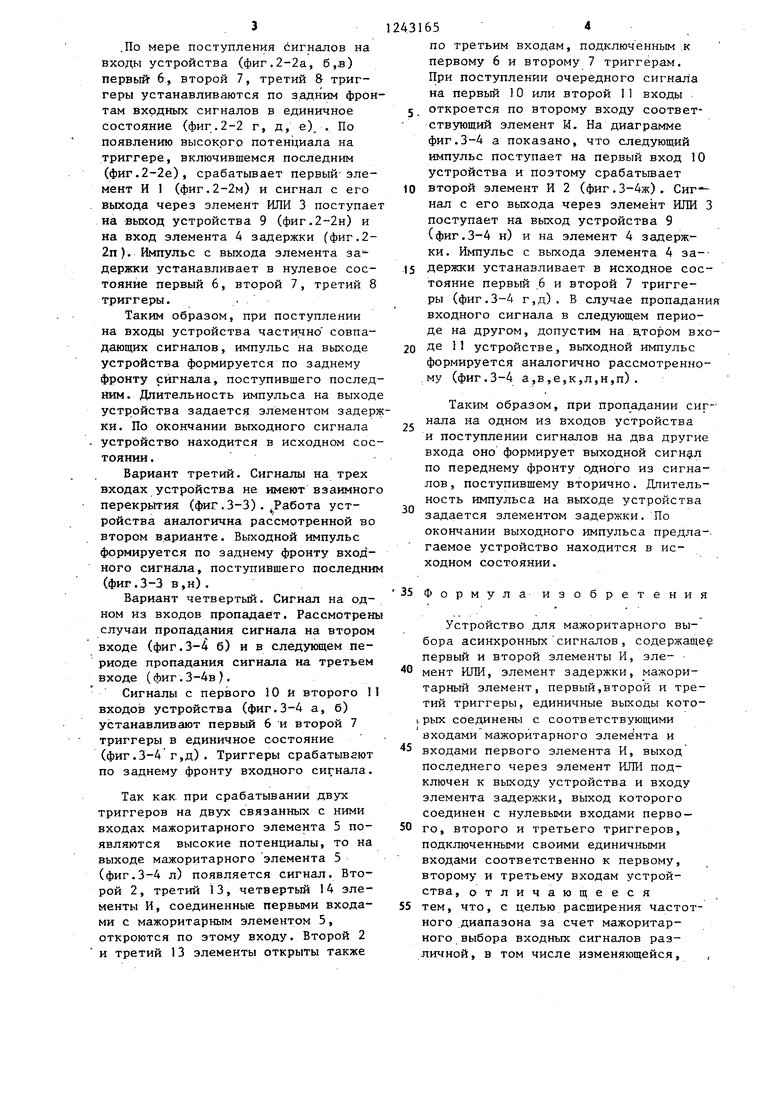

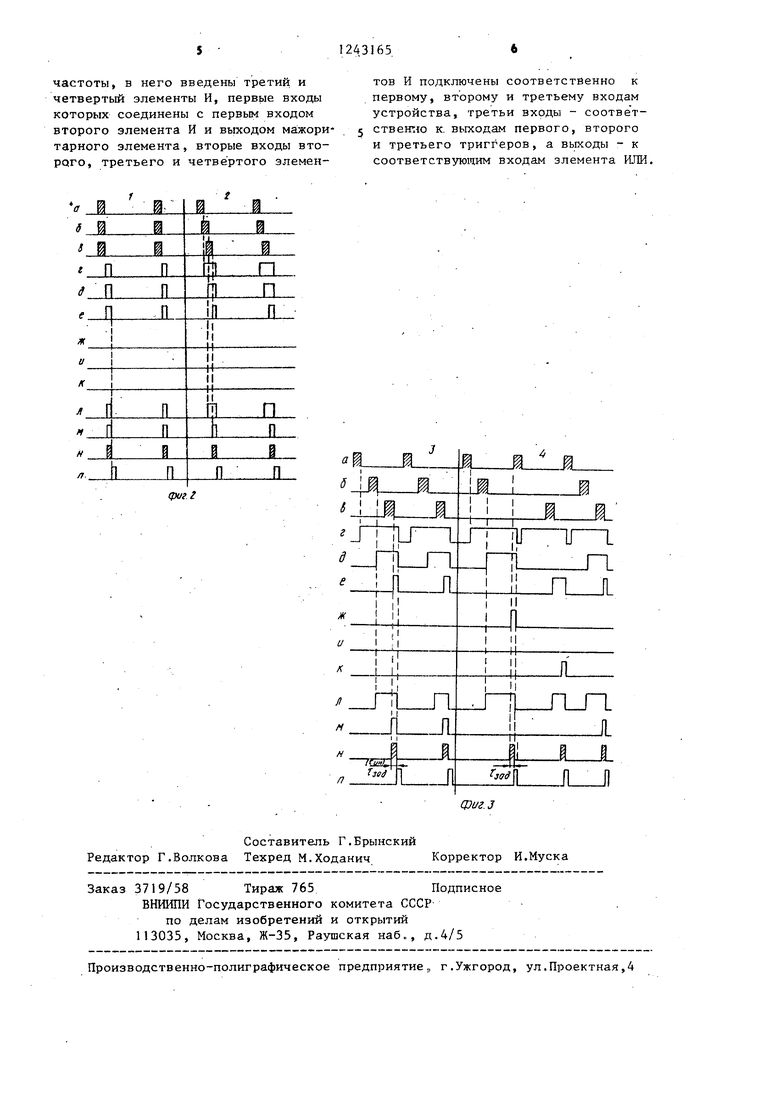

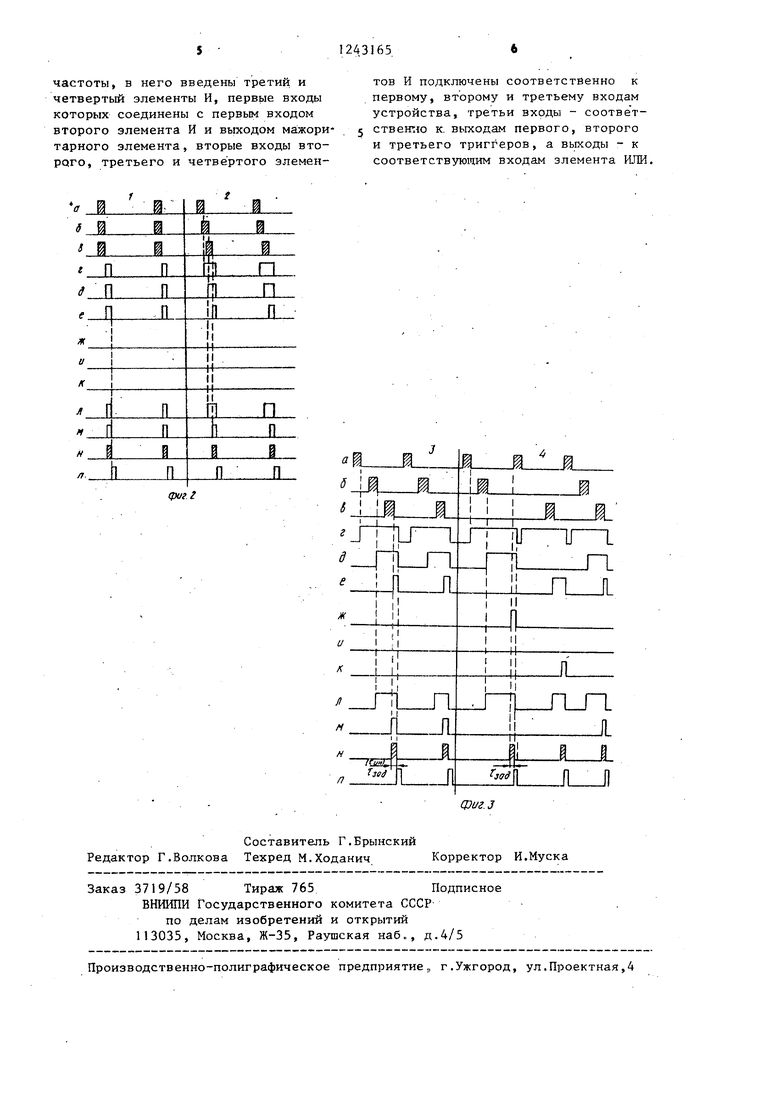

На фиг.1 представлена функциональная схема предлагаемого устройства; на фиг . 2 и 3 - диаграш 1Ь, иллюстрирующие работу устройства.

Устройство содержит первый 1 и второй 2 элементы И, элемент ИЛИ 3, элемент 4 задержки, мажоритарный элемент 5, перщый 6, второй 7 и третий 8 триггеры, единичные зькоды которых ооединены с соответствующими входами мажоритарного элемента 5 и входами первого элемента И 1, выход последнего чер.ез элемент ИЛИ 3 подключен к выходу устройства 9 и входу элемента 4 задержки выход которого соединен с нулевыми входами первого 6, второго 7 н третьего 8 триггеров,подключенными своими единичными входами 30 .соответственно к первому 10,. второму II и третьему 2 входам устройства, третий 13 и четвертый 14 элементы И, первые входы которых соединены с первым входом второго элемента .И 2 . 35 и выходом м ажоритарного элемента 5, вторые входы второго 2, третьего 13 и четвертого 14 элементов И подключены соответственно к первому IО и третьему 12 входам устройства, 40 третьи входы - соответственно к единичным выходам первого 6, второго 7 и третьего 8 триггеров, а выходы - к соответствующим входам элемента J ЛИ 3., 45

Устройство.может быть реализовано а интегральных микросхемах серии 30,133, 530 и других. Элемент заержки может быть реализован на линии адержки ЛЗТ. Время задержки, форми- 50 уемое элементом задержки, должно ыть больше времени срабатывания риггеров и меньше длительности - ходных сигналов.

Устройство работает следующим 55 бразом.

Перед началом работы импульсом броса первый 6, второй 7, третий 8

65 .2

триггеры устанавливаются в нулевое состояние любым известным способом (цепи сброса не показаны).

Рассмотрим работу устройства при различ -1ых временных соотношениях входньк сигналов.

Вариант первый. Сигналы на трех входах устройства совпадают пол- ностью (фиг.2- ). На диаграмме а - сигналы на первом входе 10 устрой- . ства; (5 - сигналы на втором входе 11 устройства; в - сигналы на третьем входе 12 устройства; г - единичный выход первого триггера 6; д - единичный выход второго триггера 7; е - единичный выход третьего триггера 8;

.ж - второго элемента И 2; выход третьего элемента И 13; к - выход четвертого элемента И 14; л - выход мажоритарного элемента 5; м - .выход первого элемента И 1 ; н - выход элемента ИЛИ 3 (выход устройства 9); п - выход элемента 4 задержки.

Сигналы со входов 1П - 12 совпадающие во времени (фиг.2-1 а, б,в) поступают на единичные входы первого 6, второго 7, третьего 8 триггеров соответственно, устанавливая их в единичное состояние по своему заднему фронту (фиг.2-1 г,д,е). Высокие потенциалы с выходов первого 6, второго 7, третьего 8 триггеров (фиг.2- 1 г, д., е), поступая на первый, вто- рой, третий входы первого элемента И 15 формируют на его выходе сигнал. С выхода первого элемента И 1 сигнал через элемент ИЛИ 3 поступает на выход устройства 9 (фиг.2-1н) и на вход элемента 4 задержки. Задержанный элементом 4 задержки на время, достаточное для срабатывания триггеров (фиг.2-1п), сигнал устанавливает первый 6, второй 7, третий 8 триггеры в нулевое исходное состояние.

Таким образом, при поступлении на входы устройства совпадающих во времени сигналов, устройство формирует на своем выходе импульс, привязанный во времени к задним фронтам входных сигналов, длительность выходного сигнала задается элементом задержки. По окончании Е ЫХОДНОГО импульса устройство находится в -ис-. ходном состоянии.

Вариант второй. Сигналы на трех входах устройства совпадают частично (фиг.2-2).

3

.По мере поступления Сигналов на входы устройства (фиг.2-2а, б,в) первый 6, второй 7, третий 8 триггеры устанавливаются по з.аднкм фронтам входных сигналов в единичное состояние (фиг.2-2 г, д, е), , По появлению высокого потенциала на триггере, включившемся последним (фиг.2-2е), срабатывает первый элемент И 1 (фиг.2-2м) и сигнал с его выхода через элемент ИЛИ 3 поступает на выход устройства 9 (фиг.2-2н) и на вход элемента 4 задержки (фиг.2- 2п). Импульс с выхода элемента за держки устанавливает в нулевое состояние первый 6, второй 7, третий 8 триггеры. .

Таким образом, при поступлении на входы устройства частично совпадающих сигналов, импульс на выходе устройства формируется по заднему фронту сигнала, поступившего послед- йим. Длительность импульса на выходе устройства задается элементом задержки. По окончании выходного сигнала устройство находится в исходном состоянии.

Вариант третий. Сигналы на трех входах устройства не имеют взаимного перекрытия (фиг.3-3). работа устройства аналогична рассмотренной во втором варианте. Выходной импульс формируется по заднему фронту входного сигнала, поступившего последним (фиг.3-3 в,н).

Вариант четвертый. Сигнал на одном из входов пропадает. Рассмотрены случаи пропадания сигнала на втором входе (фиг.3-4 б) и в следующем периоде пропадания сигнала на третьем входе (фиг.3-4в).

Сигналы с первого 10 и второго 11 входов устройства (фиг.3-4 а, б) устанавливают первый 6 и второй 7 триггеры в единичное состояние (фиг.3-4 г,д). Триггеры срабатывают по заднему фронту входного сигнала.

Так как. при срабатывании двух триггеров на двух связанных с ними входах мажоритарного элемента 5 появляются высокие потенциалы, то на выходе мажоритарного элемента 5 (фиг.3-4 л) появляется сигнал. Второй 2, третий 13, четвертый 14 элементы И, соединенные первыми входами с мажоритарным элементом 5, откроются по этому входу. Второй 2 и третий 13 элементы открыты также

431654

по третьим входам, подключенным к первому 6 и второму 7 триггерам. При поступлении очередного сигнала на первый 10 или второй 11 входы

5. откроется по второму входу соответствующий элемент И. На диаграмме фиг.3-4 а показано, что следующий импульс поступает на первый вход 10 устройства и поэтому срабатьшает

10 второй элемент И 2 (фиг.3-4ж). Сиг- нал с его выхода через элемент ИЛИ 3 поступает на выход устройства 9 (фиг.3-4 н) и на элемент 4 задержки. Импульс с выхода элемента 4 за-15 держки устанавливает в исходное состояние первый ,6 и второй 7 триггеры (фиг.3-4 г,д). В случае пропадания входного сигнала в следующем периоде на другом, допустим на атором вхо20 Де П устройстве, выходной импульс формируется аналогично рассмотренному (фиг.3-4 а,в,е,к,л,н,п).

образом, при пропадании сигнала на одном из входов устройства и поступлении сигналов на два другие входа оно формирует выходной сигн51л по переднему фронту одного из сигналов , поступившему вторично. Длительность импульса на выходе устройства задается элементом задержки. По окончании выходного импульса предла-. гаемое устройство находится в исходном состоянии.

35 Формула изобретения

Устройство для мажоритарного выбора асинхронных сигналов, содержаще первый и второй элементы И, эле-

0 мент ИЛИ, элемент задержки, мажоритарный элемент, первый,второй и третий триггеры, единичные выходы кото- 1-рых соединены с соответствующими входами мажоритарного элемента и

5 входами первого элемента И, выход последнего через элемент ИЛИ подключен к выходу устройства и входу элемента задержки, выход которого соединен с нулевыми входами перво50 го, второго и третьего триггеров, подключенными своими единичными входами соответственно к первому, второму и третьему входам устройства, отличающееся

55 тем, что, с целью расширения частотного .диапазона за счет мажоритарного выбора входных сигналов различной, в том числе изменяющейся, ,

частоты, в него введены третий и четвертый элементы И, первые входы которых соединены с первым входом второго элемента И и выходом мажоритарного элемента, вторые входы второго, третьего и четвертого элеменЗаказ 3719/58 Тираж 765Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие,, г.Ужгород, ул.Проектная,4

тов И подключены соответственно к первому, второму и третьему входам устройства, третьи входы - соотве т- ствешю к. выходам первого, второго и третьего триггеров, а вькоды - к соответствующим входам элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Трехканальное устройство для мажоритарного выбора асинхронных сигналов | 1984 |

|

SU1241243A1 |

| Устройство для контроля последовательности импульсов | 1987 |

|

SU1520654A1 |

| Устройство для контроля @ -разрядного распределителя импульсов | 1984 |

|

SU1166118A1 |

| Устройство для контроля импульсов | 1979 |

|

SU792576A2 |

| Устройство для мажоритарного выбора асинхронных сигналов | 1988 |

|

SU1522211A1 |

| Устройство для мажоритарного выбора асинхронных сигналов | 1983 |

|

SU1160419A1 |

| Устройство для контроля последовательности импульсов | 1982 |

|

SU1064444A1 |

| Цифровой частотный дискриминатор | 1983 |

|

SU1119162A1 |

| N-канальное устройство для мажоритарного выбора асинхронных сигналов | 1986 |

|

SU1406780A1 |

| Устройство для разделения входных импульсов | 1984 |

|

SU1287282A1 |

Изобретение может быть использовано при построении цифровых устройств различного назначения и при повышенных требования к их -надежности. Цель изобретения - расширение- частотного диапазона. Устройство содержит элементы И 1 и 2, элемент ИЛИ 3, элемент 4 задержки, мажоритарный элемент 5 и тригг еры 6-8. Введение в устройство элементов И 13 и 14 позволяет осуществлять мажоритарный выбор входных сигналов различной, в том числе изменяющейся частоты. В описании приведены следующие возможные варианты работы устройства: сигналы на трех входах устройства совпадают полностью; сигналы на трех входах устройства совпадают частично; сигналы на трех .входах устройства не имеют взаимного перекрытия; сигнал на одном из входов пропадает. 3 ил. (О (Л to 4;а Од О) 01

Авторы

Даты

1986-07-07—Публикация

1985-01-04—Подача