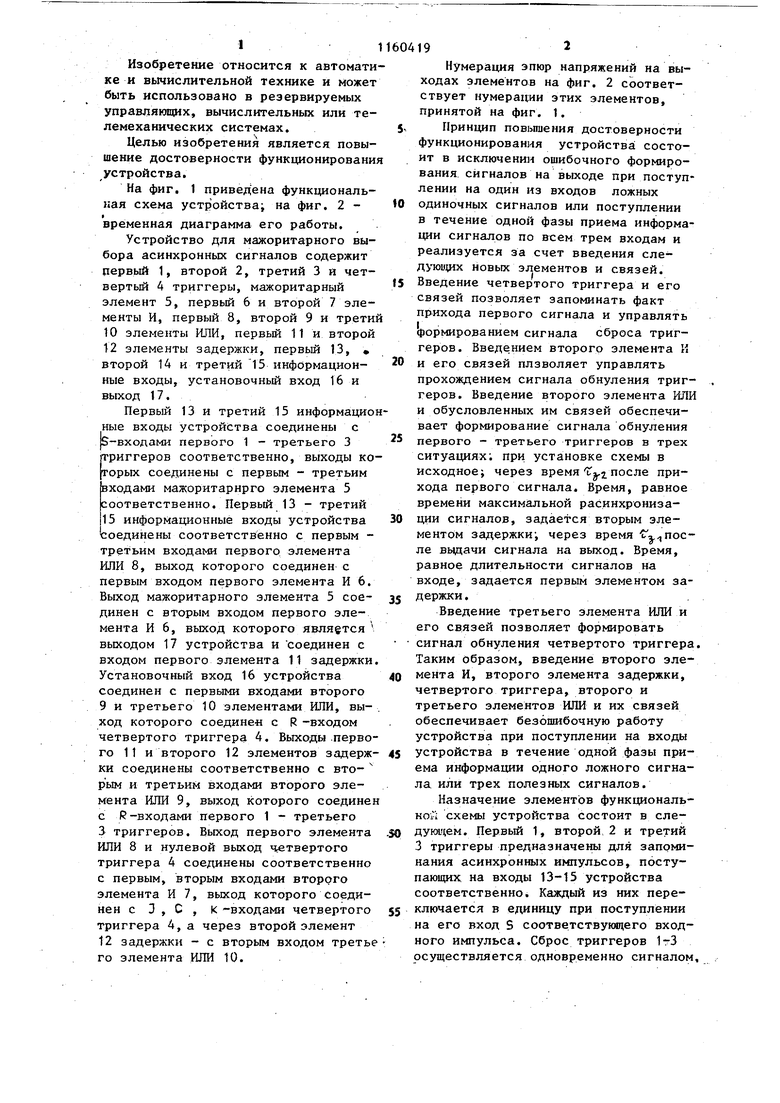

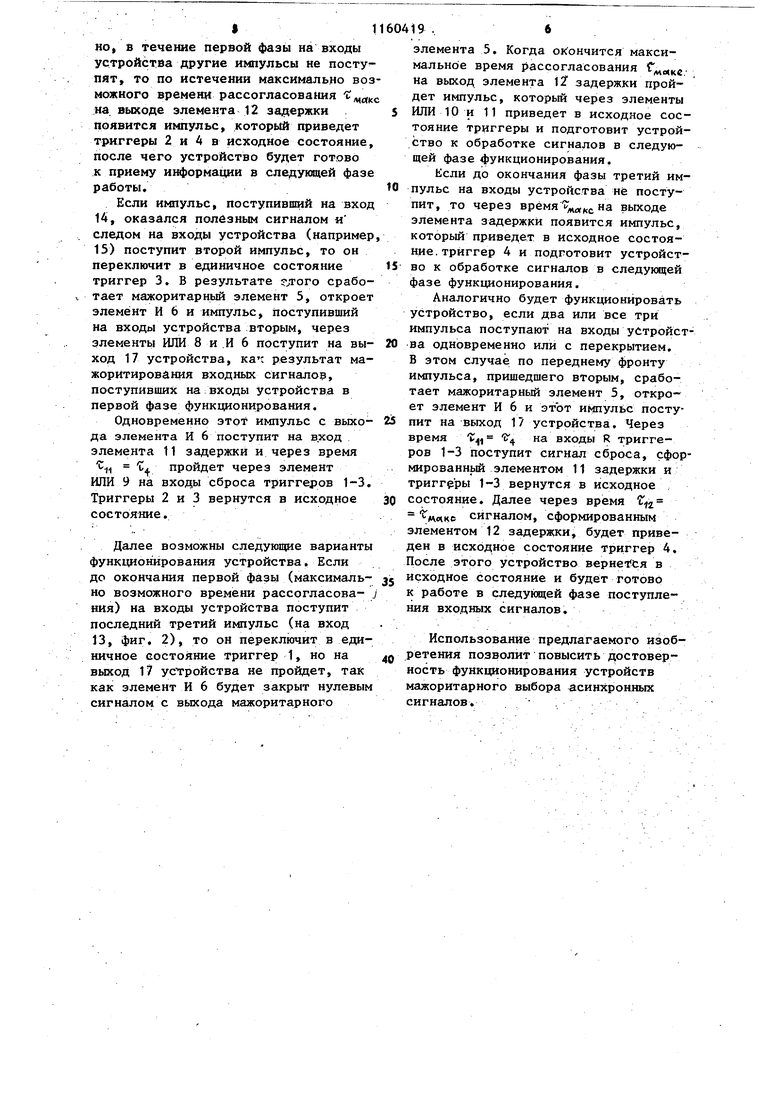

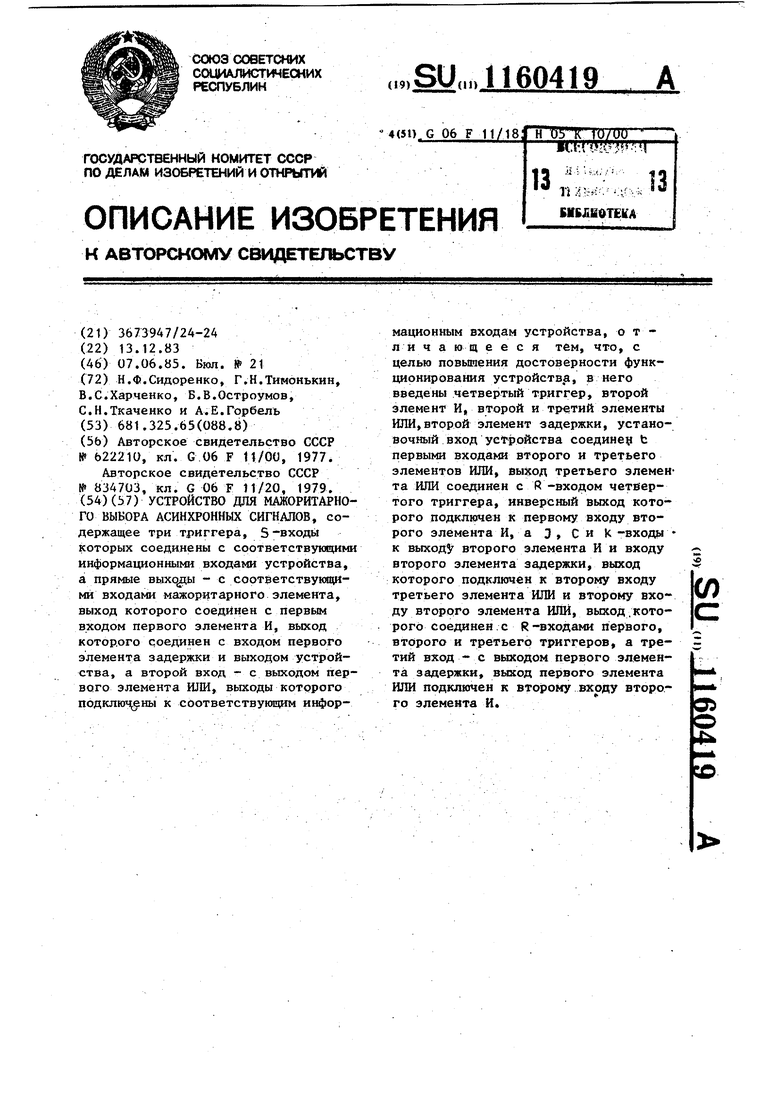

1 Изобретение относится к автомати ке и вычислительной технике и может быть использовано в резервируемых управляющих, вычислительных или телемеханических системах. Целью изобретения является повышение достоверности функционировани устройства. На фиг. 1 приведена функциональная схема устройства на фиг. 2 временная диаграмма его работы. Устройство для мажоритарного выбора асинхронных сигналов содержит первый 1, второй 2, третий 3 и четвертьй 4 триггеры, мажоритарный элемент 5, первый 6 и второй 7 элементы И, первый 8, второй 9 и трети 10 элементы ИЛИ, первый 11 и второй 12 элементы задержки, первый 13, второй 14 и третий 15 информационные входы, установочный вход 16 и выход 17. Первый 13 и третий 15 информацио ные входы устройства соединены с 5-входами первого 1 - третьего 3 триггеров соответственно, выходы ко торых соединены с первым - третьим входами мажоритарнрго элемента 5 соответственно. Первый 13 - третий 15 информационные входы устройства соединены соответственно с первым третьим входами первого элемента ИЛИ 8, выход которого соединен с первым входом первого элемента И 6. Выход мажоритарного элемента 5 соединен с вторым входом первого элемента И 6, выход которого является выходом 17 устройства и соединен с входом первого элемента 11 задержки Установочный вход 16 устройства соединен с первыми входами второго 9 и третьего 10 элементами ИЛИ, выход которого соедине« с R -входом четвертого триггера 4. Выходы .перво го 11 и второго 12 элементов задерж ки соединены соответственно с вторым и третьим входами второго элемента ИЛИ 9, выход которого соедине с R-входами первого 1 - третьего 3 триггеров. Выход первого элемента ИЛИ 8 и нулевой выход четвертого триггера 4 соединены соответственно с первым, вторым входами второго элемента И 7, выход которого соединен с J , С , К -входами четвертого триггера 4, а через второй элемент 12 задержки - с вторым входом треть го элемента ЩМ 10. 192 Нумерация эпюр напряжений на выходах элементов на фиг. 2 соответствует нумерации этих элементов, принятой на фиг. 1. Принцип повьпиения достоверности функционирования устройства; состоит в исключении ошибочного формирования сигналов на выходе при поступлении на один из входов ложных одиночных сигналов или поступлении в течение одной фазы приема информации сигналов по всем трем входам и реализуется за счет введения следуюищх новых элементов и связей. Введение четвертого триггера и его связей позволяет запоминать факт прихода первого сигнала и управлять формированием сигнала сброса триггеров. Введением второго элемента И и его связей плзволяет управлять прохождением сигнала обнуления триггеров. Введение второго элемента ИЛИ и обусловленных им связей обеспечивает формирование сигнала обнуления первого - третьего триггеров в трех ситуациях; при установке схемы в исходное; через времяZTj-i после прихода первого сигнала. Время, равное времени максимальной расинхронизации сигналов, задается вторым элементом задержки , через время v после выдачи сигнала на выход. Время, равное длительности сигналов на входе, задается первым элементом задержки. Введение третьего злемента ИЛИ и его связей позволяет формировать сигнал обнуления четвертого триггера. Таким образом, введение второго элемента И, второго элемента задержки, четвертого триггера, второго и третьего элементов ИЛИ и их связей обеспечивает безошибочную работу устройства при поступлении на входы устройства в течение одной фазы приема информации одного ложного сигнала или трех полезных сигналов. Назначение элементов функциональной схемы устройства состоит в следукн.чем. Первый 1, второй. 2 и третий 3 триггеры предназначены для запоминания асинхронных импульсов, поступающих на входы 13-15 устройства соответственно. Каждый из них переключается в единицу при поступлении на его вход S соответствующего входного импульса. Сброс триггеров 1-3 осуществляется одновременно сигналом. 31 вырабатываемым элементом ИЛИ 9 и noc тупающим на входы Р этих триггеров, Триггер 4 запоминает факт поступления первого из асйнхронных сигналов на входы устройства, разрешает его прохождение через элементы И 7, задержки 1Z и ИЛИ 9 в цепь сброса триггеров 1-3, запрещает прохождение асинхронных импульсов, пришедших вторым и третьим на входы 13-15 устройства. Триггер 4 переключается в единичное состояние входным импульсом,, пришедшим на входы устройства первым, который через открытый элемент И 7 проходит на объединенные Л, С и К-входы триггера 4. Переключившись по его заднему фронту, триггео 4 нулевым сигналом с инверсного выхода закрывает элемент И 7, запрещая тем самым прохождение импульсов пришедших позже, на вход элемента 12 задержки. Сброс триггера 4 в исходное состояние осуществляется выходным сигналом, формируемым элементом ИЛИ 10. Мажоритарный элемент 5 peaлизует логическую функцию z + XjXj + , где XT, Xj, Хз - сигналы, снимаемые с единичных выходов триггеров 1-3. Он открывает элемент 6 после поступления на входы 13-15 устройства асинхронного импуль са, пришедшего вторым и разрешает тей самым его прохождение через элемент И 6 на выход 17 устройства. Элемент ИЛИ 8 обеспечивает прохождение любого из трех выходных импульсов на входы элементов И 6 и 7. Элемент ИЛИ 9 формирует сигнал сброса триггеров 1-3 при поступлении сигналов сброса на вход 16 устройства или с выхода элементов 11 и 12 задержки. Элемент ИЛИ 10 формирует сигнал сброса триггера 4 при поступлении сигналов сброса на вход 16 устройства или с выхода элемента 11 и 12 задержки. Элемент ИЛИ 10 формирует сигнал сброса триггера 4 при поступлении сигналов сброса на вход 16 устройства или с выхода элемента 12 задержки. Элемент 11 задержки предназначен для формирования сигнала сброса триггеров 1-3 при поступлении на выход 17 устройства импульса. Время задержки этого элемента Т, , где t - длительность вькодного импульса устройства. Указанное требование к времени задерж194ки 11 элемента обеспечивает вьдачу на выход 17 устройства входного импульса без уменьшения его длитель ности, которое может произойти при Г.. С или вообще при отсутствии элемента 11 задержки. Так, (или 4 0) сигнал сброса поступит на входы Р триггеров 1-3 и до окончания входного импульса сбросит их в ноль. Это, в свою очередь, приведет к появлению нулевого сигнала на входе элемента И 6 и прекращению выдачи имПульса на вькоде 17 устройства. Элемент 12 задержки предназначен для формирования сигнала сброса триггеров 1-4 после окончания времени максимально возможного рассогласования (,; ) между пришедшими и входными импульсами, при-: шедшими первым и последним. Время задержки этого элемента, таким образом, определяется Iиз условия: watte И вход элемента 12 задержки через элемент И 7 поступает импульс, пришедший на один из входов устройства первым. Через время мм на выходе элемента 12 появляется импульс, который через элементы ИЛИ 9 и 10 поступает на входы р. 1триггеров 1-4, приводит их в исходное состояние, подготавливая устройство к повторному циклу функционирования. Устройство для мажоритарного выбора асинхронных сигналов работает следующим образом. После включения питания на вход 16 устройства подается сигнал сброса, который приходит через элементы ИЛИ 9 и 10 и устанавливает триггер 1-4 в исходное состояние. Устройство готово к работе. Пусть в первой фазе работы на один из входов устройства (например 14) поступает импульс. Он устанавливает триггер 2 в единичное состояние и через элементы ИЛИ 8 и И 7 проходит на входы триггера 4 и элемента 12 задержки («Иг. 2), по заднему фронту этого импульса триггер 4 устанавливается в единичное состояние и запрещает прохождение импульсов, пришедших вторым и третьим, через элемент И 7. На выход элемента И 6, закрытого нулевым сигналом мажоритарного элемента И 6, этот импульс не проходит. Если поступивший импульс оказался ложным (помехой) и, следователь- . но, в течение первой фазы на входы устройства другие импульсы не поступят, то по истечении максимально воз можного времени рассогласования ячдк на выходе элемента 12 задержки появится импульс, который приведет триггеры 2 и А в исходное состояние, после чего устройство будет готово к приему информации в следующей фазе работы. Если иьшульс, поступивший на вход 14, оказался полезным сигналом и следом на входы устройства (например 15) поступит второй импульс, то он переключит в единичное состояние триггер 3. В результате того сработает мажоритарный элемент 5, откроет элемент И 6 и импульс, поступивший на входы устройства вторым, через элементы ИЛИ 8 и И 6 поступит на выход 17 устройства, результат мажорИтирования входных сигналов, поступивших на входы устройства в первой фазе функционирования. Одновременно этот импульс с выхода элемента И 6 поступит на вход элемента 11 задержки и через время С If пройдет через элемент ИЛИ 9 на входы сброса триггеров 1-3. Триггеры 2 и 3 вернутся в исходное состояние. далее возможны следующие варианты функционирования устройства. Если до окончания первой фазы (максимально возможного времени рассогласования) на входы устройства поступит последний третий импульс (на вход 13, фиг. 2), то он переключит в единичное состояние триггер 1, но на выход 17 устройства не пройдет, так как элемент И 6 будет закрыт нулевым сигналом с выхода мажоритарного 1 19 ,6 элемента 5. Когда окончится максимальное время рассогласования На выход элемента 12 задержки пройдет импульс, который через элементы ИЛИ 10 и 11 приведет в исходное состояние триггеры и подготовит устройство к обработке сигналов в следующей фазе функционирования. Ксли до окончания фазы третий импульс на входы устройства не поступит, то через время ,J, на выходе элемента задержки появится импульс, который приведет в исходное состояние, триггер 4 и подготовит устройство к обработке сигналов в следующей фазе функционирования. Аналогично будет функционировать устройство, если два или все три импульса поступают на входы устройства одновременно или с перекрытием. В этом случае; по переднему фронту импульса, пришедшего вторым, сработает мажоритарный элемент 5, откроет элемент И 6 и этот И1«1ульс поступит на выход 17 устройства. Через время входы R триггеров 1-3 поступит сигнал сброса, сформированньй элементом 11 задержки и триггеры 1-3 вернутся в исходное состояние. Далее через время t сигналом, сформированным элементом 12 задержки, будет приведен в исходное состояние триггер 4. После этого устройство вернется в исходное состояние и будет готово к работе в следуннцей фазе поступления входных сигналов. Использование предлагаемого изобретения позволит повысить достоверность функщюнирования устройств мажоритарного выбора асинхронных сигналов.

Фиг. 1

45

f

П

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для мажоритарного выбора асинхронных сигналов | 1988 |

|

SU1522211A1 |

| Устройство для контроля @ -разрядного распределителя импульсов | 1984 |

|

SU1166118A1 |

| Устройство для мажоритарного выбора асинхронных сигналов | 1985 |

|

SU1243165A1 |

| Трехканальное устройство для мажоритарного выбора асинхронных сигналов | 1984 |

|

SU1241243A1 |

| Устройство для управления с контролем | 1983 |

|

SU1156074A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| Устройство для мажоритарного выбора асинхронных сигналов | 1984 |

|

SU1218503A1 |

| Устройство для мажоритарного выбора асинхронных сигналов | 1986 |

|

SU1372326A1 |

| Устройство для мажоритарного выбора асинхронных сигналов | 1986 |

|

SU1420661A1 |

| Устройство для мажоритарного выбора асинхронных сигналов | 1991 |

|

SU1820386A1 |

УСТРОЙСТВО ДЛЯ МАЖОРИТАРНОГО ВЫБОРА АСИНХРОННЫХ СИГНАЛОВ, содержащее три триггера, 5 входы которых соединены с соответствующими информационными входами устройства, а прямые выходы - с соответствующими входами мажоритарного элемента, выход которого соединен с первым входом первого элемента И, вькод которого соединен с входом первого элемента задержки и выходом устройства, а второй вход - с выходом первого элемента ШШ, выходы которого подключены к соответствующим информационным входам устройства, о т ли ч а ю щ е е с я тем, что, с целью повьшения достоверности функционирования устройств,а, в него введены четвертый триггер, второй элемент И, второй и третий элементы ИЛИ,второй элемент задержки, установочный вход устройства соединен t первыми входами второго и третьего элементов ИЛИ, выход третьего элемента ШШ соединен с R -входом четвертого триггера, инверсный выход которого подключен к первому входу второго элемента И, а Э Си k-входы к выходу второго элемента И и входу второго элемента задержки, выход которого подключен к второму входу (П третьего элемента ШШ и второму входу второго элемента ИЛИ, выход,которого соединен .с R-входами первого, второго и третьего триггеров, а третий вход - с ВЕЛходом первого элемента задержки, выход первого элемента ИЛИ подключен к второму входу второО) го элемента И. О 4 ;о

fff-r,

a

n

iwrr

пп.

П

4

/ t t

П

fl

t

t

| Устройство для мажоритарного выбора сигналов | 1977 |

|

SU622210A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для мажоритарного выбораАСиНХРОННыХ СигНАлОВ | 1979 |

|

SU834703A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-06-07—Публикация

1983-12-13—Подача