Изоб;)етение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть использовано при создании аналго-цифровых преобразователей и устройств связи с объектом.

Целью изобретения является повышение быстродействия устройства и расширение области его применения за счет увеличения динамического диапазона.

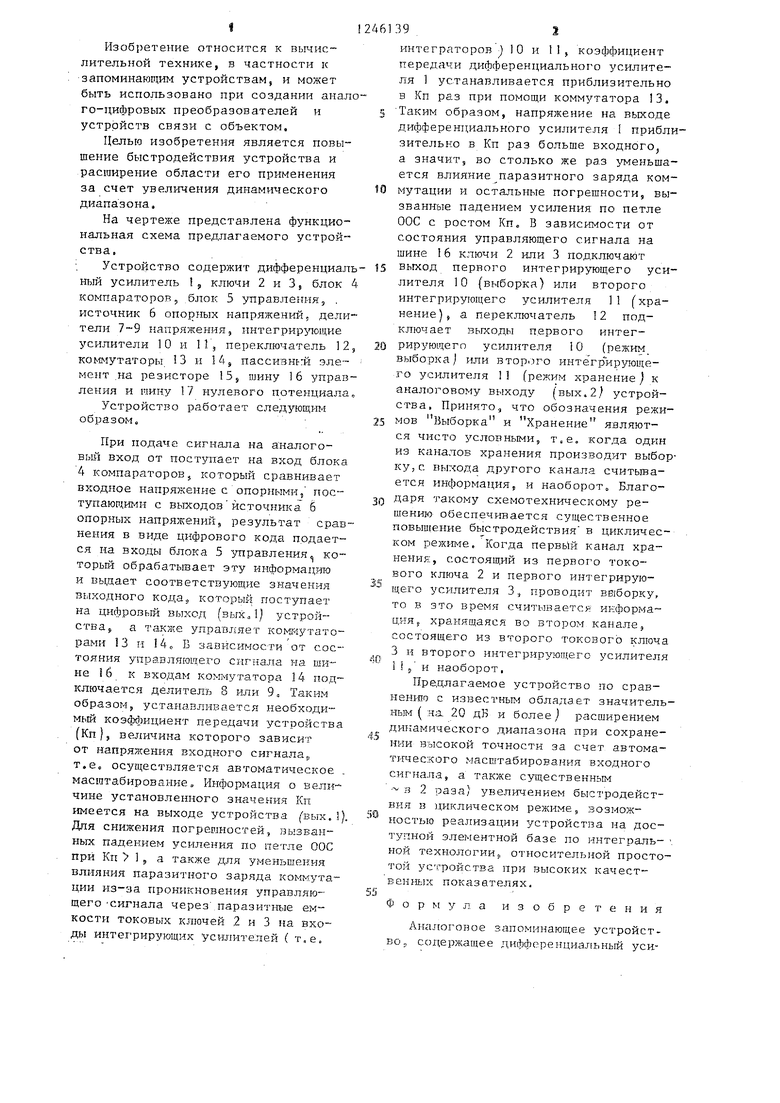

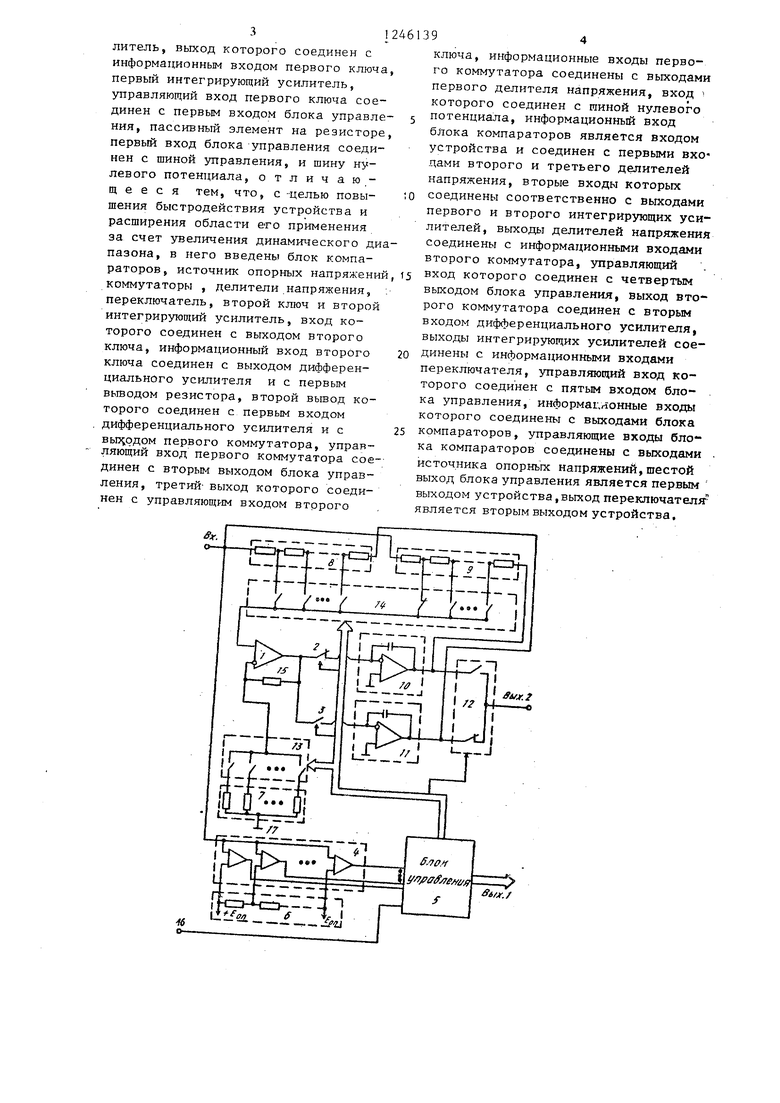

На чертеже представлена функциональная схема предлагаемого устройства,

-. Устройство содержит дифференциалный усилитель , ключи 2 и 3, блок компараторов, блок 5 управления, . источник 6 опорных напряжений, делители 7-9 напряжения, интегрирующие усилители 10 и П, переключатель 12 коммутаторы 13 и 14, пaccизн :й элемент .на резисторе 15, шину 16 управления и гаину 17 нулевого потенциала

Устройство работает следующем образом.

При подаче сигнала на аналого- вьй вход от поступает на вход блока 4 компараторов, которь й сравнивает входное напряжение с опорными. пос- тупаюп;и1 и с выходов источника 6 опорных напряжений, результат сравнения в виде цифрового кода подается на входы блока 5 управления, ко- торьрл обрабатьюает эту информацию и вьщает соответствующие значения выходного кода; который поступает на циЛровый выход (вых 1 устройства а такзсе управляет коммутаторами 13 и 4о Б зависимости от состояния управляющего сигнала на шине 16 к входам коммутатора 14 подключается делитель 8 или 9, Таким образом, устанавливается необходи- мьй коэфб ициент передачи устройства (Кп), величина которого зависит от напрялсения входного сигнала „ т.е„ осуществляется автоматическое масштабирование Информация о вели-- чине установленного значения Кп имеется на выходе устройства (вых. 1 Для снижения погреошостей, вызванных падением усиления по петле ООС при Кп 15 а также для уменьшения влияния паразитного заряда коммутации из-за проникновения управляющего -сигнала через паразитн ае емкости токовых ключей ,2 и 3 на входы интегрирующих ус ллителей ( т.е.

5

5

0

5

интеграторов-} 10 и 11, коэффициент передачи дифференциального усилителя 1 устанавливается приблизительно Б Кп раз при помощи коммутатора 13. Таким образом, напряжение на выходе дифференциального усилителя I приблизительно в Кп раз больше входного, а значит, во столько же раз уменьшается влияние паразитного заряда коммутации и остальные погрешности, вызванные падением усиления по петле ООС с ростом Кп. В зависимости от состояния управляющего сигнала на шине 16 ключи 2 или 3 подключают выход первого интегрирующего усилителя 10 (выборка) или второго интегрирующего усилителя 11 fхранение J, а переключатель 12 подключает выходы первого интегрирующего усилителя 10 (режим выборка) или втор.эго интегр ирующе- го усилителя 1 (режим хранение ) к аналоговому выходу (вых.2/ устройства, Принято, что обозначения режимов Выборка и Хранение являются чисто условными, т,е„ когда один из каналов хранения производит выборку, с выхода другого канала считывается информация5 и наоборот. Благодаря такому схемотехническому решению обеспечршается существенное повышение быстродействия в циклическом режрме. Когда первь1й канал хранения, состоящий из первого токового ключа 2 и первого интегрирующего усилителя 3j проводит вВ1борку, то в зто время считывается информация хранящаяся во втором канале, состоящего из второго токового ключа 3 и второго интегрирующего усилителя 1 1 р и наоборот.

Предлагаемое устройство по сравнению с известным обладает значительным ( н;1 20 дБ и более расширением динамического диапазона при сохранении высокой точности за счет автоматического масштабирования входного сигнала, а также существенным - в 2 раза) увеличением быс1 родейст- вня в циклическом режиме, возможностью реализации устройства на доступной элементной базе по интеграль- , ной технологии., относительной простотой устройства при высоких качест- BCHi-JbJx показателях,

Формула изобретения

Ан 1логовое запоминающее устройство, содержащее дифференциальный уси3

литель, выход которого соединен с информационным входом первого ключа первый интегрирующий усилитель, управляющий вход первого ключа соединен с первым входом блока управле ния, пассивный элемент на резисторе первый вход блока управления соединен с шиной управления, и шину нулевого потенциала, отличающееся тем, что, с -целью повы- шения быстродействия устройства и расширения области его применения за счет увеличения динамического дипазона, в него введены блок компараторов, источник опорных напряжени коммутаторы , делители напряжения, переключатель, второй ключ и второй интегрируюп1ий усилитель, вход которого соединен с выходом второго ключа, информационный вход второго ключа соединен с выходом дифференциального усилителя и с первым вьюодом резистора, второй вывод которого соединен с первым входом дифференциального усилителя и с вьщ;рдом первого коммутатора, управляющий вход первого коммутатора соединен с вторым выходом блока управления, третий- выход которого соединен с управляющим входом второго

5 О ,15 20 25 394

ключа, информационные входы первого коммутатора соединены с вьпсодамн первого делителя напряжения, вход которого соединен с шиной нулевого потенциала, информационный вход блока компараторов является входом устройства и соединен с первыми входами второго и третьего делителей напряжения, вторые входы которых соединены соответственно с выходами первого и второго интегрирующих усилителей, выходы делителей напряжения соединены с информационными входами второго коммутатора, управляющий вход которого соединен с четвертым выходом блока управления, выход второго коммутатора соединен с вторым входом дифференциального усилителя, выходы интегрирующих усилителей соединены с информационными входами переключателя, управляющий вход которого соединен с пятым входом бло- . ка управления, информационные входы которого соединены с выходами блока компараторов, управляющие входы блока компараторов соединены с выходами .

источника опорных напряжений, шестой выход блока управления является первым выходом устройства,выход переключателя является вторым выходом устройства.

-« о-

Lii/2i / :b

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАСКАДНЫЙ УСИЛИТЕЛЬ | 1992 |

|

RU2106740C1 |

| Емкостно-электронный преобразователь перемещения | 1989 |

|

SU1721434A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ СОВМЕЩЕННОГО ИНТЕГРИРОВАНИЯ | 1992 |

|

RU2036559C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С ПРОМЕЖУТОЧНЫМ ПРЕОБРАЗОВАНИЕМ В ЧАСТОТУ | 1990 |

|

RU2007029C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ФАЗОЧУВСТВИТЕЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЕ - КОД | 1992 |

|

RU2094946C1 |

| Генератор пилообразного напряжения с переменной крутизной | 1987 |

|

SU1495982A1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В НАПРЯЖЕНИЕ | 1987 |

|

RU2056700C1 |

| Интегрирующий аналого-цифровой преобразователь | 1988 |

|

SU1681384A1 |

| Измерительный преобразователь дифференциального емкостного датчика | 1990 |

|

SU1781637A1 |

| Интегратор | 1988 |

|

SU1728871A1 |

Изобретение относится к вычислительной технике, в частности к за-.. поминающим устройствам,и может быты использовано при создании аналого- цифровых преобразователей и устройств связи с объектом. Цель изобретения - повышение быстродействия и расширение области применения устройства за счет увеличения динамического диапазона-достигается введением блока компараторов, источника опорных напряжений, коммутаторов, делителей напряжения, переключателя, второго ключа и второго интегрирующего усилителя. Введение новых блоков и элементов позволило увеличить в предложенном устройстве в два раза. быстродействие и более чем на 20 дБ расширить динамический диапазон. 1 ил. о (О (Л

| Шило В.Л | |||

| Линейные интегральные схемы в радиоэлектронной аппаратуре, М.: Советское радио, 1979, с.328 | |||

| Ленк Дж. | |||

| Руководство для пользователей операционных усилителей | |||

| М.: Связь, 1978, с.226. |

Авторы

Даты

1986-07-23—Публикация

1984-12-07—Подача