Изобретение относится к импульсной технике, в частности к аналого-цифровым преобразователям (АЦП) с промежуточным преобразованием напряжения в частоту импульсов.

Цель изобретения - повышение быстродействия.

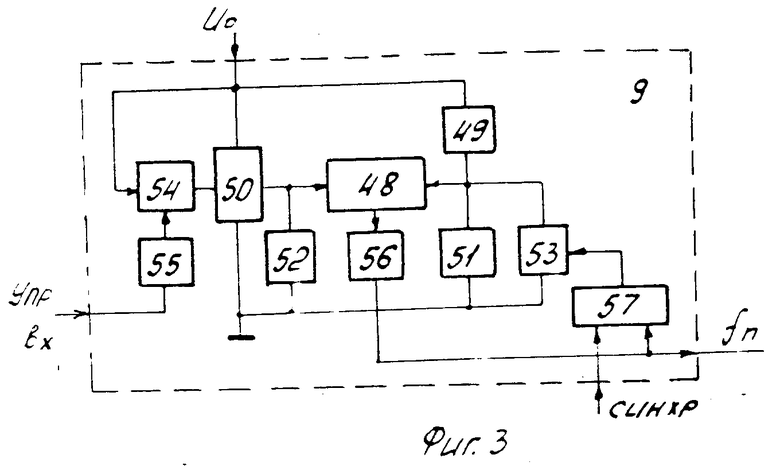

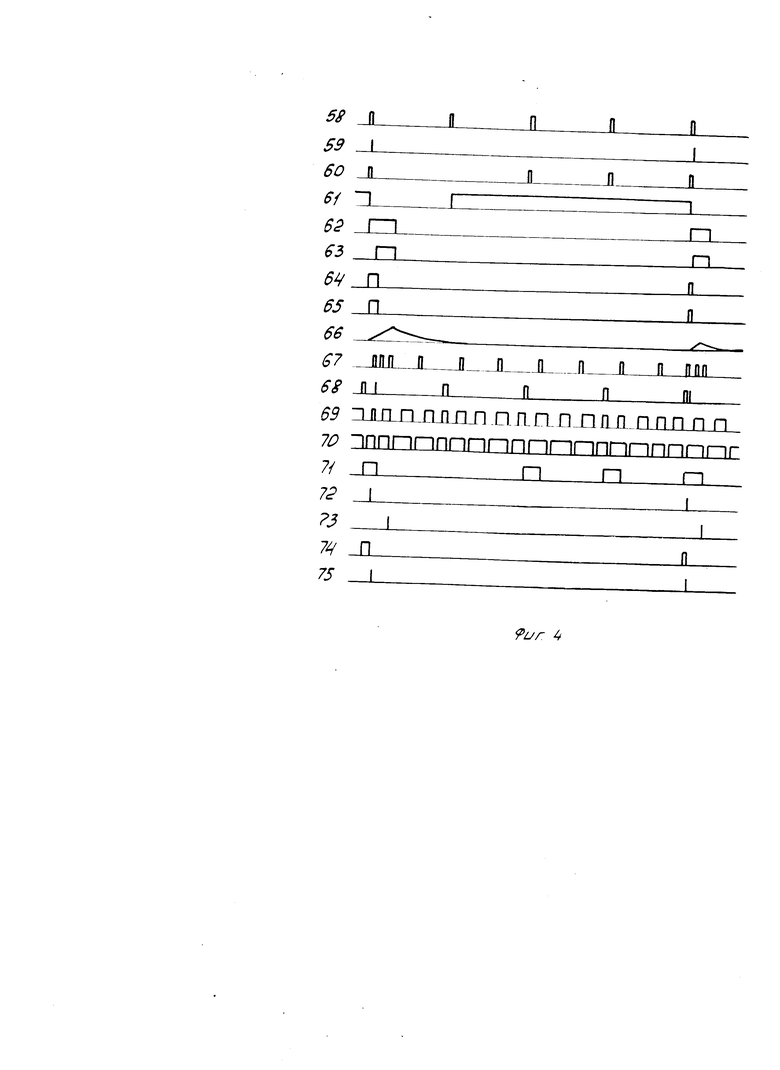

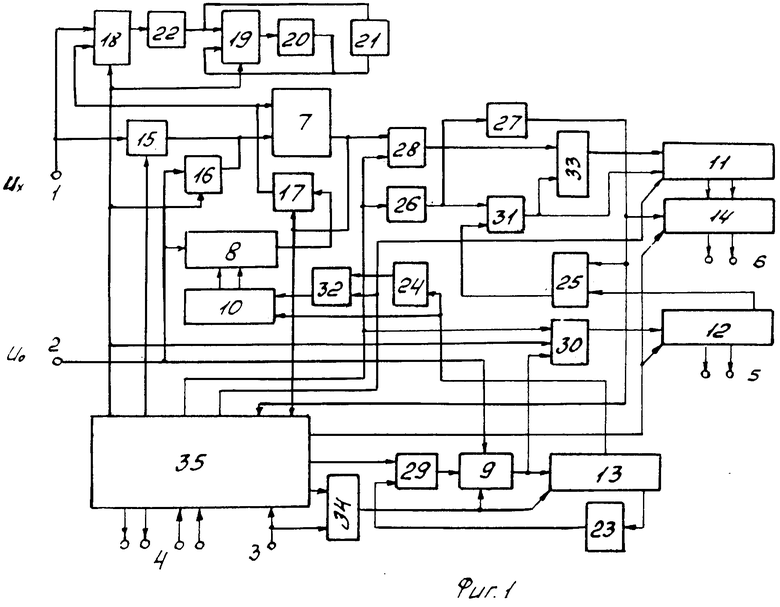

На фиг. 1, 2 и 3 приведены блок-схемы АЦП, его блока управления и управляемого генератора; на фиг. 4 - временная диаграмма работы АЦП.

АЦП содержит шины входного 1 Ux и опорного 2 Uo напряжений, шину 3 синхронизации АЦП, входные и выходные интерфейсные шины 4, шины 5, 6 результата преобразования, преобразователь 7 напряжения в частоту импульсов (ПНЧ), цифроаналоговый преобразователь (ЦАП) 8, управляемый генератор 9, с первого по четвертый счетчики 10-13, регистр 14, с первого по третий ключи 15-17, в которых вход соединяется с выходом при наличии сигнала на управляющем входе, первый 18 и второй 19 переключатели, у которых выход соединяется с первым входом при наличии сигнала на управляющем входе и с вторым входом при его отсутствии, операционный усилитель 20, конденсатор 21, резистор 22, первый 23 и второй 24 одновибраторы, триггер 25, первый 26 и второй 27 формирователи импульсов, с первого по пятый 28-32 элементы И, первый 33 и второй 34 элементы ИЛИ, блок 35 управления.

Блок управления (фиг. 2) содержит счетчик 36, блок 37 сравнения кодов, делитель 38 числа импульсов, с первого по третий триггеры 39-41, первый 42 и второй 43 формирователи импульсов, c первого по третий элементы И 44-46, элемент ИЛИ 47.

Управляемый генератор (фиг. 3) содержит компаратор 48, источник 49 тока, делитель 50 напряжения, конденсаторы 51, 52, ключи 53, 54, формирователи 55, 56 импульсов, элемент ИЛИ 57.

АЦП работает следующим образом.

Время измерения Ти входного напряжения Uх формируется по коду q, получаемому по входным интерфейсным шинам 4, с помощью синхронизирующих импульсов 58, имеющих частоту fc. Эти импульсы подсчитываются счетчиком 36, и при получении в нем кода q срабатывает блок 37 сравнения. По его выходному сигналу формирователь 42 вырабатывает импульс 59, который соответствует окончанию предыдущего и началу очередного такта измерения Ux, имеющих длительность Ти = q/fc.

Информация об окончании очередного Ти передается по одной из выходных интерфейсных шин 4 сигналом 61 с выхода элемента ИЛИ 47. Сигнал 61 отсутствует при нулевом коде в счетчике 36, и в это время допускается смена задания на величину Ти путем изменения кода q в интерфейсных шинах 4.

Импульсы 58 используются в АЦП для подстройки, во-первых, частоты генератора 9, формирующего временной квант работы tп = 1/fп, и, во-вторых, величины коэффициента Кп преобразования в ПНЧ 7. Благодаря выполнению этих подстроек обеспечиваются следующие соотношения:

fп = nofo и fo = pfc, где fo - частота ПНЧ 7 при преобразовании опорного напряжения Uo, а Tи= q/fc= qp/fo= nopq/fп и fп = nopfc.

Подстройка fп под fc выполняется с помощью генератора 9, который может быть выполнен по схеме на фиг. 3. В нем делитель 50 напряжения состоит из трех резисторов, два из которых, включенных между Uo и общей шиной, имеют величины сопротивлений, значительно превышающие величину сопротивления третьего резистора, подсоединенного к выходу ключа 54. Входами генератора 9 являются опорное напряжение Uo, подаваемое на делитель 50 и источник 49 тока, вход для изменения частоты, соединенный через формирователь 55 с управляющим входом ключа 54, и вход синхронизации, соединенный с входом элемента ИЛИ 57, а выходом fп - выход формирователя 56. В генераторе 9 импульсы синхронизации с помощью ключа 53 разряжают конденсатор 51. После этого напряжение на нем начинает увеличиваться от тока заряда источника 49. Это напряжение сравнивается компаратором 48 с напряжением на выходе делителя 50, зашунтированного конденсатором 52. По достижении равенства этих напряжений компаратор 48 срабатывает и запускает формирователь 56, его импульс проходит через элемент ИЛИ 57. Процесс повторяется, на выходе генератора 9 возникают импульсы fп. Величину частоты fп можно уменьшить путем увеличения напряжения на конденсаторе 52, подавая на него дополнительный заряд от Uo с помощью ключа 54. При его импульсном включении затем в течение длительного времени на конденсаторе 52 поддерживаются измененный уровень напряжения и измененная частота fп.

Для поддержания величины fп = nopfс с помощью счетчика 13, имеющего емкость nop и подсчитывающего импульсы генератора 9, начиная с момента установки в нем нулевого кода импульсом 68, сформированным из импульса 58, прошедшим через элемент ИЛИ 34, до его переполнения, формируется интервал времени Тс= nop/fп . В этот момент сигнал с его старшего разряда снимается и запускает одновибратор 23. Выходной импульс 71 этого одновибратора разрешает работу элемента И 29, на второй вход которого поступают импульсы 60, сформированные из импульсов 58 элементами И 44 и ИЛИ 47, среди которых первый импульс после начала Тиотсутствует, так как в это время в АЦП выполняется подстройка Кп и Тс≠ nop/fc.

Если импульсы 60 и 71 перекрываются, что соответствует неравенству Тс < 1/fс или fп > nopfc, на выходе элемента И 29 появляется сигнал, который запускает формирователь 55, и частота уменьшается. Подстройка fп заканчивается при отсутствии совпадения импульсов 60 и 71, когда генератор 9 имеет частоту fп = nopfc.

Подстройка Кп выполняется в начале каждого Ти. Для этого импульс 59 устанавливает в "1" триггер 39, а его сигналы 62 с нулевого выхода с помощью ключей 15 и 16 отключают от ПНЧ 7 напряжение Uх и подключают Uo. Сигналы 62 с первого выхода триггера 39 разрешают работу элемента И 45, через который проходит первый импульс 72 из импульсов формирователя 43, сформированных по импульсам fo = KпUo 67 ПНЧ 7, и устанавливает в "1" триггер 41 (сигнал 63). Сигнал с его нулевого выхода снимается и устанавливает в исходное состояние делитель 38 импульсов, а импульс 72 проходит через ИЛИ 34 и устанавливает такое же состояние в генераторе 9 и в счетчике 13. С этого момента без каких-либо потерь времени начинаются подсчет импульсов fп в последнем и пересчет импульсов формирователя 43 делителем 38, имеющим коэффициент деления S ≥ 1. Выбор величины S осуществляется из условия обеспечения требуемой точности подстройки Кп при наличии ограничений на динамические характеристики используемой в АЦП элементной базы. Последний из S импульсов формирователя 43 появляется на выходе делителя 38 и проходит через элемент И 46, импульс 73 которого устанавливает в "0" триггеры 39 и 41, сигналы 62 и 63 которых снимаются.

За время сигнала 63, имеющего длительность tи = S/fo, в счетчик 13 поступает ns импульсов fп, ns = tиfп = Sfп/fo. Емкость младших разрядов, включая средний разряд, счетчика 13 равна Ns = Sno. Поэтому при равенстве fo = fп/no через время tи сигнал 69 с выхода среднего разряда счетчика 13 снимается и запускается одновибратор 24. Совпадение его импульса с импульсом 73 означает выполнение этого равенства и правильность настройки: tн = S/fo = Sno/fп;

Kп= fo/Uo= fп/noUo= pnofc/noUo= pfc/Uo

Сигнал 70 с нулевого выхода одновибратора 24 разрешает работу элемента И 32, на второй вход которого подается импульс 73, а выход соединен со счетным входом счетчика 10. Для случая равенства fo = fп/noимпульс 73 через элемент И 32 не проходит и в счетчике 10 код не изменяется.

По этому коду в ЦАП 8 формируется сигнал, используемый для изменения Кп ПНЧ 7 и подаваемый с помощью ключа 17 на его второй вход. При этом, если ПНЧ 7 выполнен, например, по схеме компенсации заряда интегрирующего конденсатора, то напряжение Uo, а затем и Ux, подключается к его первому входу и далее через резистор с величиной сопротивления R к входу операционного усилителя, имеющего конденсатор в цепи обратной связи. Вход этого операционного усилителя является вторым токовым входом ПНЧ 7, на который в течение фиксированного интервала времени tэ подаются ток -Тэ от внутреннего источника напряжения и ток Тп от ЦАП 8, подключаемый ключом 17. Заряд -q = (Iп - Iэ)tэ, получаемый конденсатором, компенсируется током Uo/R до нуля за время to, т. е.

-q+(Uo/R)·to= 0,

откуда fo= 1/to= UoRq ;

fo= Uo/R(Iп-Iэ)tэ= Kп·Uo;

Kп= 1/R(Iп-Iэ)tэ .

Изменяя ток Тп, можно изменять величины Кп и fo. Увеличение Тпприводит к уменьшению величины -q и к увеличению Кп и fo, а уменьшение Тп - к их уменьшению.

При неравенстве fo ≠ fп/no импульс 73 проходит через элемент И 32 и изменяет код в счетчике 10. Если импульс 73 приходит до появления импульса одновибратора 24, что соответствует неравенству fo > fп/no, то в счетчике 10 код уменьшается на единицу, так как сигнал 69 включает в нем режим вычитания. Ток Тп уменьшается, уменьшая Кп и fo. Появление импульса 73 после импульса одновибратора 24, когда fo < fп/no, ведет к увеличению на единицу кода в счетчике 10 и увеличению Кп. Благодаря такой подстройке величина Кп поддерживается равной pfc/Uo.

По окончании подстройки Кп сигнал 62 снимается и отключает от ПНЧ 7 напряжение Uo и подключает Ux для его преобразования до окончания Ти. Длительность сигнала 62 равна t1.

Для исключения потери информации о величине Ux за время t1 по сигналу 62 переключатель 18 подключает напряжение Ux через резистор 22 и переключатель 19 к входу операционного усилителя 20, в цепи обратной связи которого включен конденсатор 21. За время t1 в этом конденсаторе накапливается заряд

Q= (1/R) Ux(t)dt

Ux(t)dt

C окончанием t1 переключатель 18 подключает резистор 22 к токовому входу ПНЧ 7, а переключатель 19 отключает конденсатор 21 и резистор 22 от входа операционного усилителя 20, который переключателем 19 подсоединяется к его выходу. На последнем устанавливается нулевой потенциал общей шины, и заряд конденсатора 21 через резистор 22 уменьшается до нуля (сигнал 66), увеличивая через ПНЧ 7 ток от входного напряжения Ux.

Преобразование Ux продолжается до окончания Ти в течение сигнала с нулевого выхода триггера 39. За это время ПНЧ 7 от Ux получает заряд Q2= (1/R) Ux(t)dt и заряд Q1.

Ux(t)dt и заряд Q1.

Суммарный заряд, преобразуемый ПНЧ 7, равен

Qx= Q1+Q2= (1/R) Ux(t)dt= (1/R)[(1/Tи)

Ux(t)dt= (1/R)[(1/Tи)  Ux(t)dt] Iп= (1/R)

Ux(t)dt] Iп= (1/R) (Tи)- Iи,

(Tи)- Iи,

где  (Tи) - среднее значение напряжения Ux(t) за время Ти.

(Tи) - среднее значение напряжения Ux(t) за время Ти.

Заряд Qx соответствует среднему значению Ux за время Ти без потерь информации в течение выполнения настройки Кп и fп.

Этот заряд преобразуется ПНЧ 7 в импульсы 67, последний из которых в большинстве случаев не совпадает с окончанием Ти, это может привести к дополнительной погрешности в результате преобразования. Для ее исключения по сигналу 62, как было показано выше, к ПНЧ 7 подключается опорное напряжение Uo, и в течение времени tk до появления импульса 72 оно участвует в формировании последнего импульса 67. За это время ПНЧ 7 получает дополнительный заряд Qк= (Uo/R)·tк, а в счетчик 12, который установлен импульсом 59 в исходное нулевое состояние и работает на вычитание от генератора 9 через элемент И 30, работа которого разрешена в течение сигнала 74, поступают n импульсов fп. n = tkfп.

Выполнение вычитания в счетчике 12 фиксируется триггером 25, который устанавливается в "1" сигналом с выхода старшего разряда счетчика 12. Если емкость этого счетчика равнa no, то в нем к окончанию tk получен код nk = no - n.

Сигнал с нулевого выхода триггера 41, устанавливаемый в "0" импульсом 73 и в "1" импульсом 72, разрешает работу элемента И 28, через который с выхода ПНЧ 7 проходят импульсы 67 и далее через элемент ИЛИ 33 на счетный вход счетчика 11, установленного в "0" импульсом 73. Количество этих импульсов определяется общим зарядом Qx + Q1,2) и равно

N = Kп[Ux(Ти)Iи + Uotk] .

Используя значения

Kп= (fсp)/Uo; Iи= q/fc; tи = n/fп и fп = nopfc

и подставляя их в N, получают

N= fcp/Uo[ (Tи)(q/fc)+Uo(n/nopfc)] = [

(Tи)(q/fc)+Uo(n/nopfc)] = [ (Tи)/Uo] pq+n/no.

(Tи)/Uo] pq+n/no.

Величина N не соответствует результату преобразования Nx= [ (Iи)/Uo] pq и отличается от него на n/no<1, поэтому Nx= N-n/no . Для получения Nxкод счетчика 11 уменьшается на единицу, если имеется сигнал 65 на выходе триггера 25, который разрешает прохождение через элемент И 31 от формирователя 26 импульса, сформированного по снятию сигнала 63. Этот импульс проходит через элемент ИЛИ 33 на счетный вход счетчика 11 и на вход включения в нем режима вычитания.

(Iи)/Uo] pq и отличается от него на n/no<1, поэтому Nx= N-n/no . Для получения Nxкод счетчика 11 уменьшается на единицу, если имеется сигнал 65 на выходе триггера 25, который разрешает прохождение через элемент И 31 от формирователя 26 импульса, сформированного по снятию сигнала 63. Этот импульс проходит через элемент ИЛИ 33 на счетный вход счетчика 11 и на вход включения в нем режима вычитания.

В счетчике 11 образуется код N-1. Он записывается в регистр 14 импульсом 75 формирователя 27, так как в счетчике 11 накапливается новое значение.

Коды N-1 регистра 14 и no-n счетчика 12 образуют общий код Х результата преобразования, в котором к младшим разрядам относятся разряды счетчика 12, а к старшим - разряды регистра 14. При этом младший разряд последнего имеет вес no и записанный в регистре 14 код имеет величину (N-1)no. В этом случае общий код результата преобразования равен

X = (N - 1)no + (no - n) = noN - n.

Можно определить величину

noN-n= [ (Tи)/Uo] pqno,

(Tи)/Uo] pqno,

откуда

X= [ (Tи)/Uo] pqno= [

(Tи)/Uo] pqno= [ (Tи)] /Δ, где Δ= Uo/pqno - квант АЦП.

(Tи)] /Δ, где Δ= Uo/pqno - квант АЦП.

Поэтому в счетчике 12 и регистре 14 получен общий код Х, соответствующий точному среднему значению Ux(t) за время измерения Ти = q/fc с квантом преобразования Δ, величина которого зависит от длительности последнего, т. е. может изменяться в зависимости от значения q, принимаемого по интерфейсным шинам 4.

Сигналы с выходов разрядов счетчика 12 и регистра 14 передаются по шинам 5 и 6 результата преобразования.

Информация о недостоверном коде Х, который имеет место в моменты изменения информации в разрядах счетчика 12 при получении кода no - n и при записи кода N - 1 в регистр 14, формируется с помощью триггера 40, устанавливаемого в "1" и в "0" соответственно импульсами 59 и 75, и передается сигналом 64 по одной из выходных интерфейсных шин 4.

Таким образом, в АЦП за каждый такт Ти формируется результат преобразования без каких-либо потерь его значений, соответствующих временным интервалам коррекции результата преобразования Х и подстройки коэффициента К. При этом временной интервал tи прототипа перед началом Ти отсутствует, а в течение времени t1, равного сумме tk и tи, выполняется интегрирование Ux дополнительным интегратором, результаты которого учитываются при формировании общего интервала от Ux за Ти, т. е. интегрирование Ux выполняется без временных промежутков и потери информации о величине Ux не происходит.

Такая работа АЦП без временных промежутков в процессе измерения Ux(t), которые требовались в прототипе на выполнение коррекции в течение tи и tk, а также на подстройку Кп в течение tп, повышает его быстродействие.

Необходимо отметить, что в прототипе временные затраты tп и tkмогут иметь наибольшую величину to = 1/fo, а tp занимает время нескольких периодов частоты синхронизации fc. В примере реализации прототипа tp = r/fc. Работа прототипа проходит при синхронизации от fc и с Ти = q/fc, что определяет величину временных затрат Т1 на получение одного результата преобразования:

Т1 = tп + tk + r/fc+q/fc

Величины tи и tk меньше 1/fc, но разность времени между ними использовать нельзя из-за синхронизации работы АЦП частотой fc, откуда Т1 = q+4/fc . Поэтому в прототипе значительная часть времени в Т1расходуется не на измерение входного сигнала и в течение этого времени информация о его величине пропадает. Это приводит к тому, что при необходимости непрерывного измерения входного сигнала в его представлении дискретными значениями имеют место дополнительные погрешности, Этот вид погрешностей в предлагаемом АЦП исключен благодаря тому, что время преобразования Ти = q/fc, а быстродействие повышено в Kв= T1/Tп= (q+4)/q= 1+4/q раз. В примере реализации прототипа q = 6, поэтому для этого случая Кв = 1,66, а с уменьшением q величина Кв увеличивается.

Все это показывает, что в заявляемом АЦП устранены недостатки прототипа, по сравнению с которым повышено быстродействие. Это достигнуто благодаря исключению затрат времени, необходимых в прототипе на окончательное формирование результата преобразования, дополнительно к времени измерения входного напряжения. В АЦП получаемые результаты соответствуют средним значениям преобразуемого напряжения для соприкасающихся во времени тактов его работы, синхронизируемых по внешним сигналам. (56) Авторское свидетельство СССР N 1441479, кл. Н 03 М 1/60, 1987.

Авторское свидетельство СССР N 1644382, кл. Н 03 М 1/60, 1989.

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1992 |

|

RU2037267C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012132C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1992 |

|

RU2038694C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1992 |

|

RU2062549C1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012130C1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012131C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ СОВМЕЩЕННОГО ИНТЕГРИРОВАНИЯ | 1992 |

|

RU2036559C1 |

| Аналого-цифровой преобразователь | 1991 |

|

SU1800617A1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1728968A1 |

| Аналого-цифровой преобразователь с частотным преобразованием | 1990 |

|

SU1725396A1 |

Изобретение относится к импульсной технике, в частности к преобразователям напряжения в цифровой код с промежуточным преобразованием напряжения в частоту импульсов, и может быть использовано в устройствах сбора аналоговой информации систем контроля и испытаний изделий и управления технологическими процессами. Целью изобретения является повышение быстродействия за счет исключения дополнительных затрат времени на коррекцию результата преобразования. АЦП содержит преобразователь напряжения в частоту импульсов, три ключа, цифроаналоговый преобразователь, управляемый генератор, четыре счетчика, одновибратор, триггер, два формирователя импульсов, логические элементы И и ИЛИ, блок управления. Новым является введение двух переключателей, операционного усилителя, конденсатора, резистора и одновибратора, благодаря которым совмещаются во времени подстройка АЦП, коррекция результата преобразования и измерение входного напряжения, дополнительных затрат времени по сравнению с временем измерения входного напряжения не требуется и тем самым повышается быстродействие преобразователя. 1 з. п. ф-лы, 4 ил.

Авторы

Даты

1994-01-30—Публикация

1990-10-25—Подача