Изобретение относится к автоматике и вычислительной технике и может найти применение для программного управления технологическими агрегатами с синхронно-синфазной связью координат: роботами, обслуживающими поточные и автоматические линии, намоточными и металлорежущими станками, ткацкими и бумагоделательными машинами,

Цель изобретения - повьшение скорости обучения благодаря организации автоматического разбиения формируемой программы на кадры и занесения информации в память без останова станка.

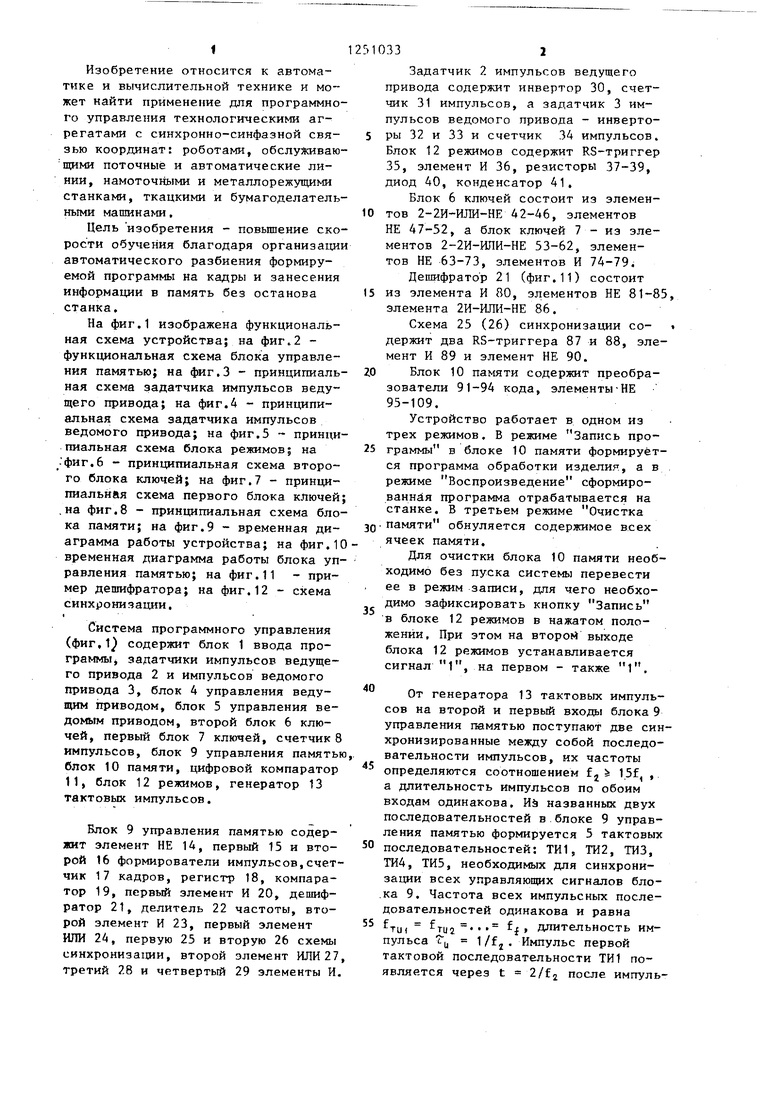

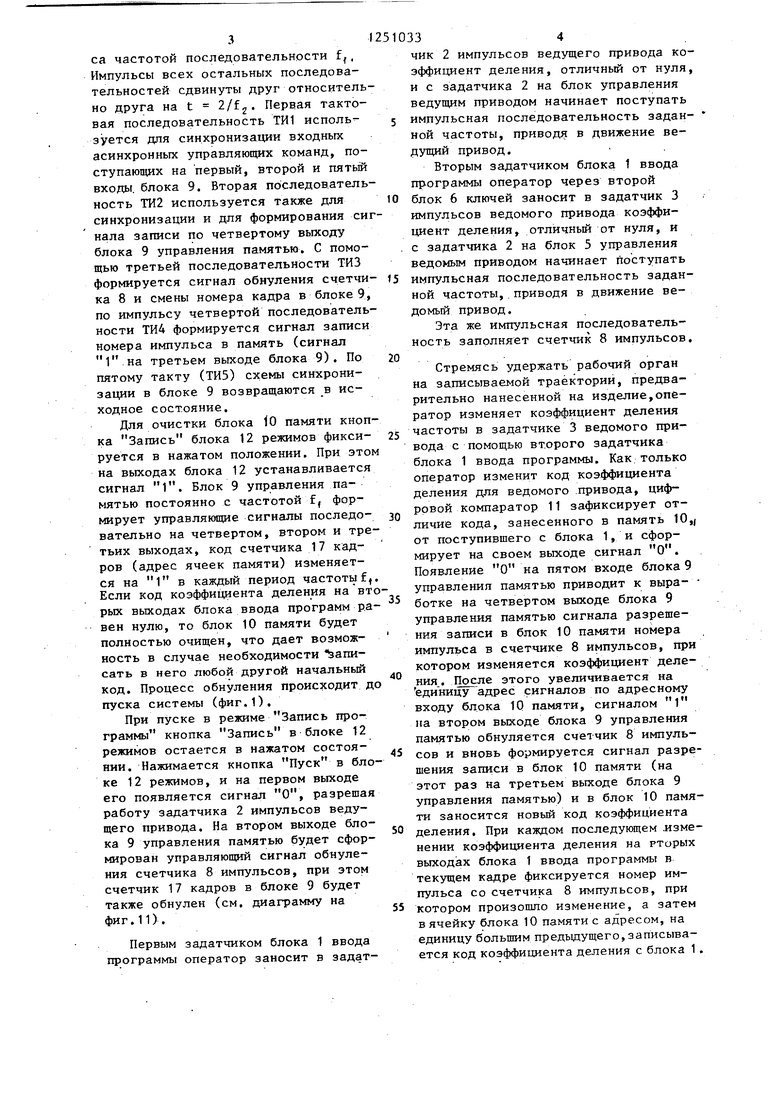

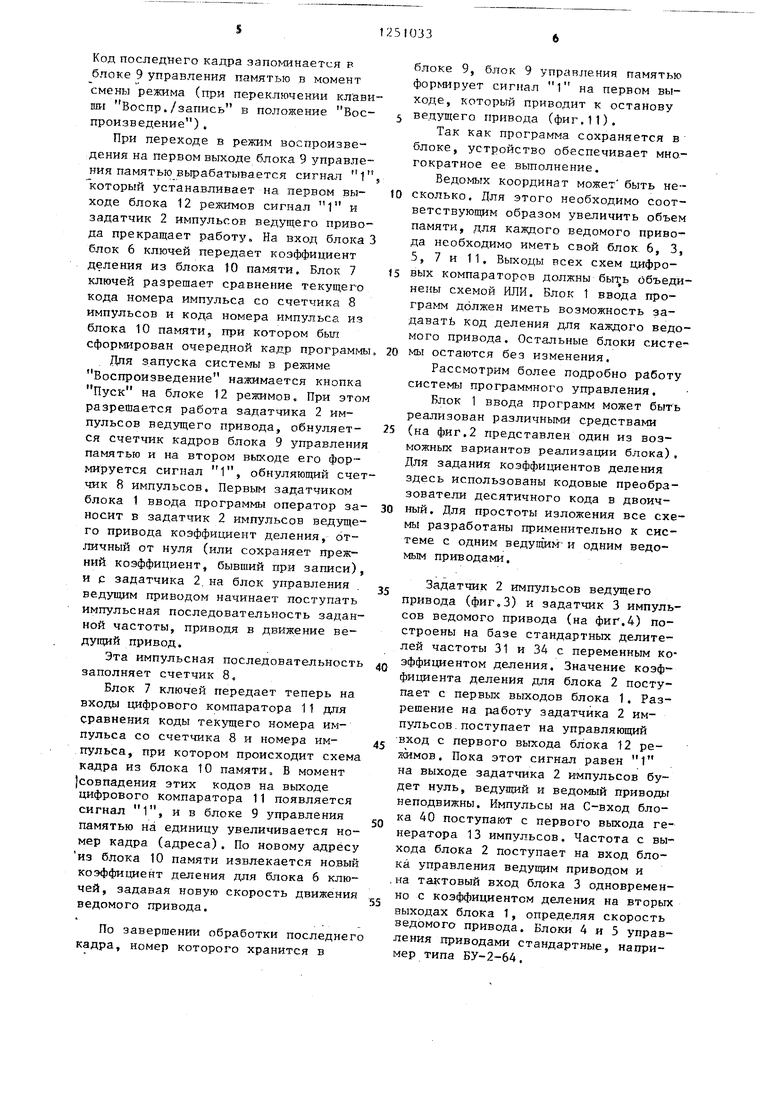

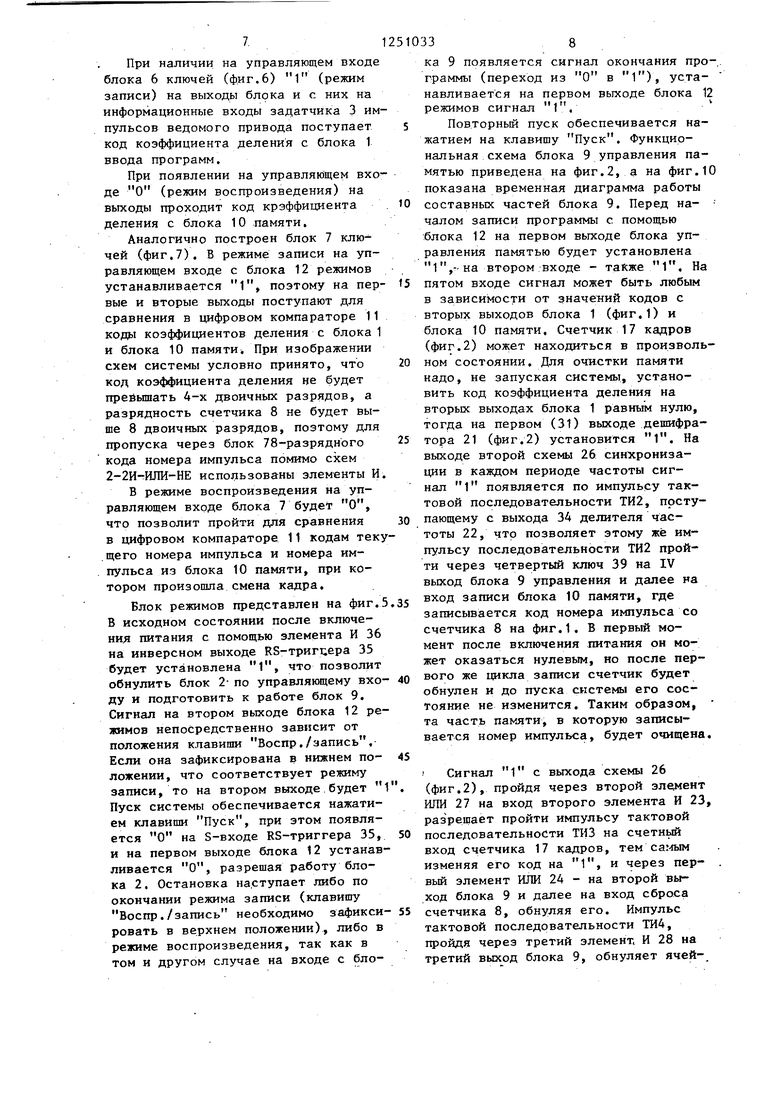

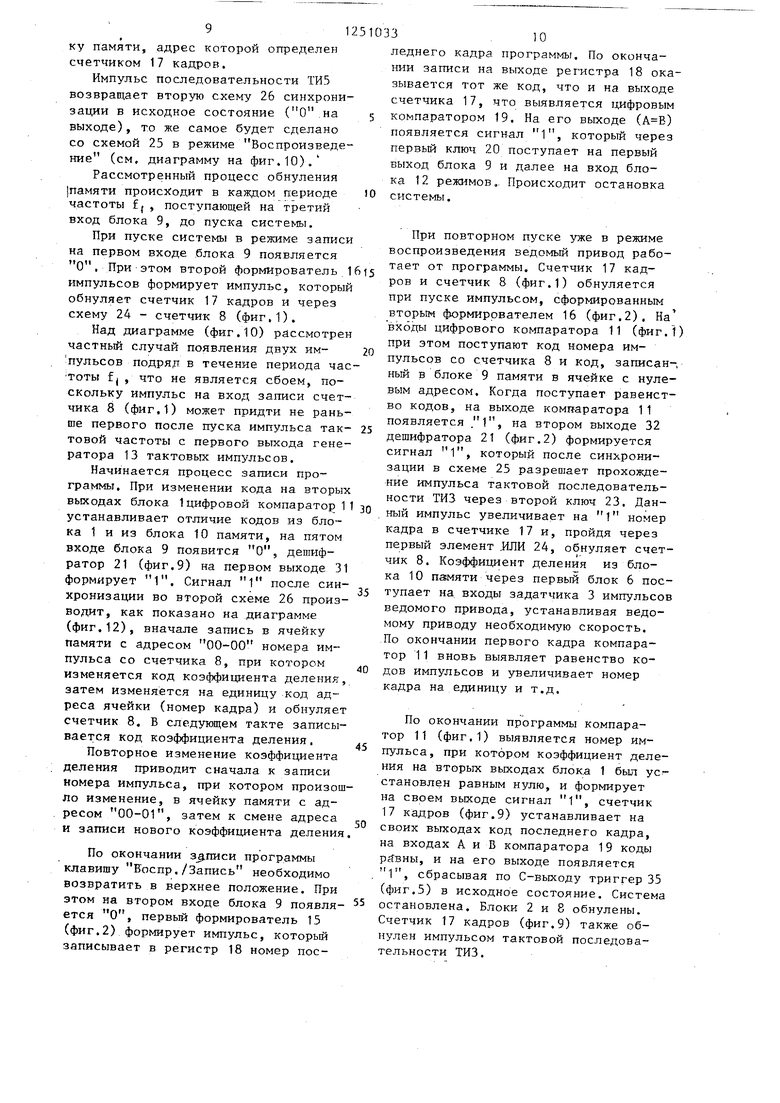

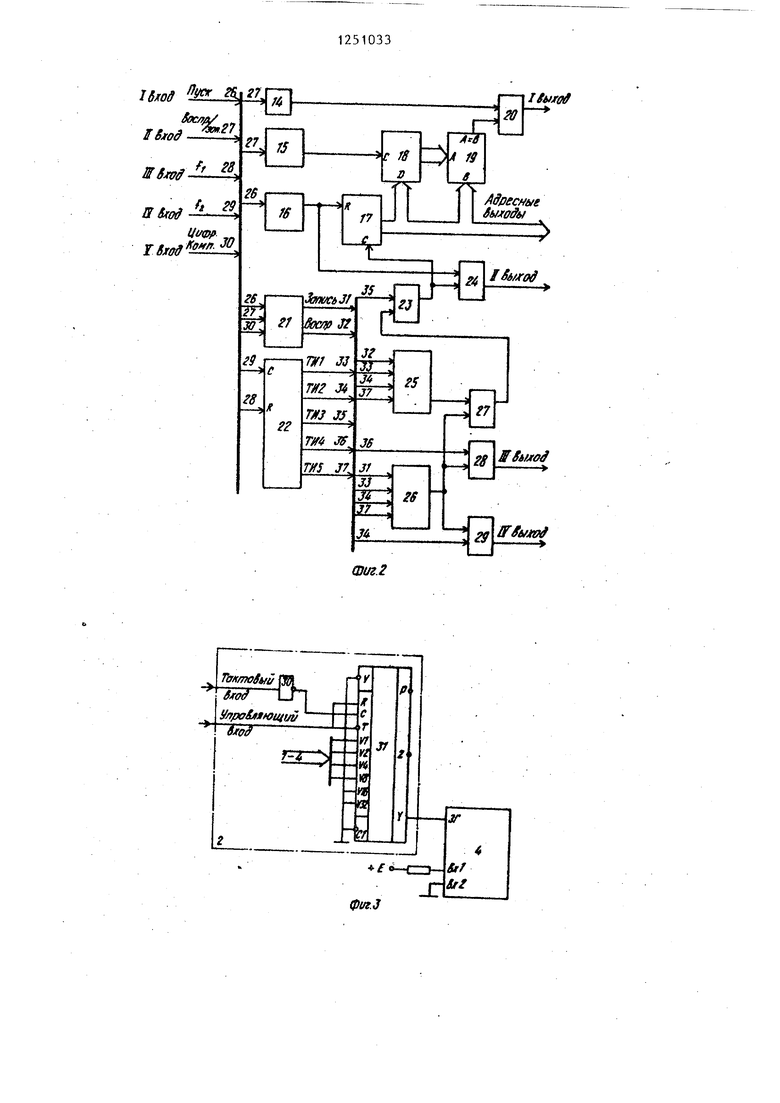

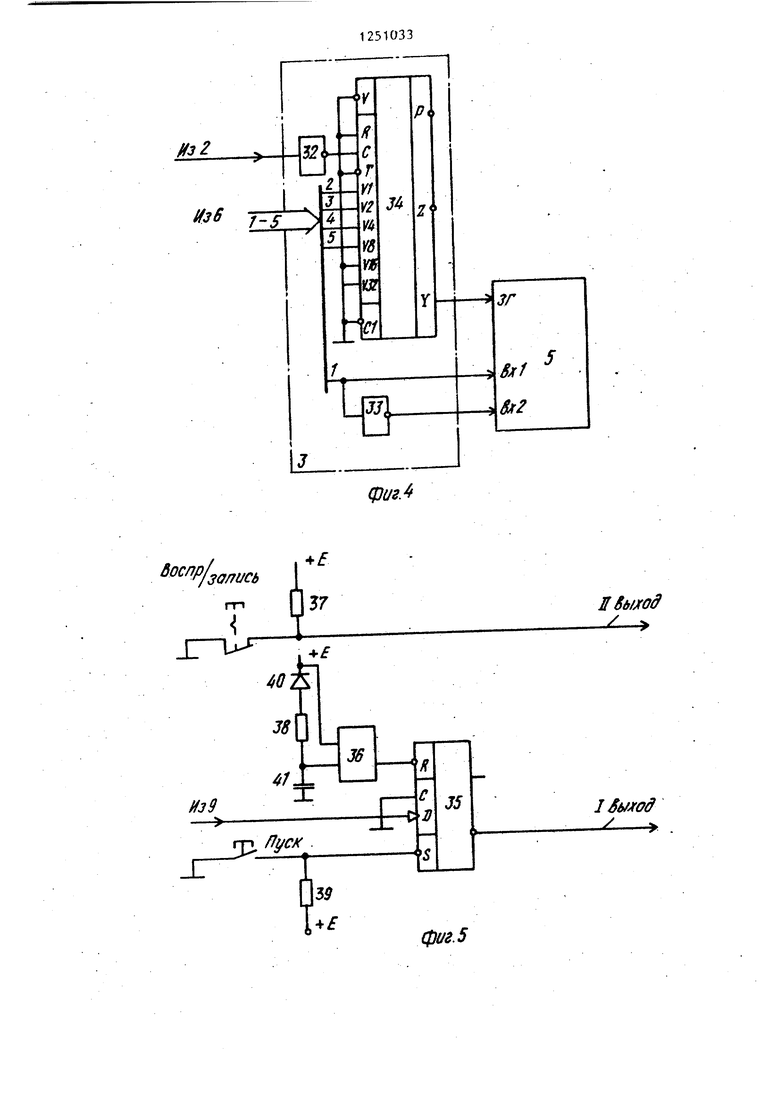

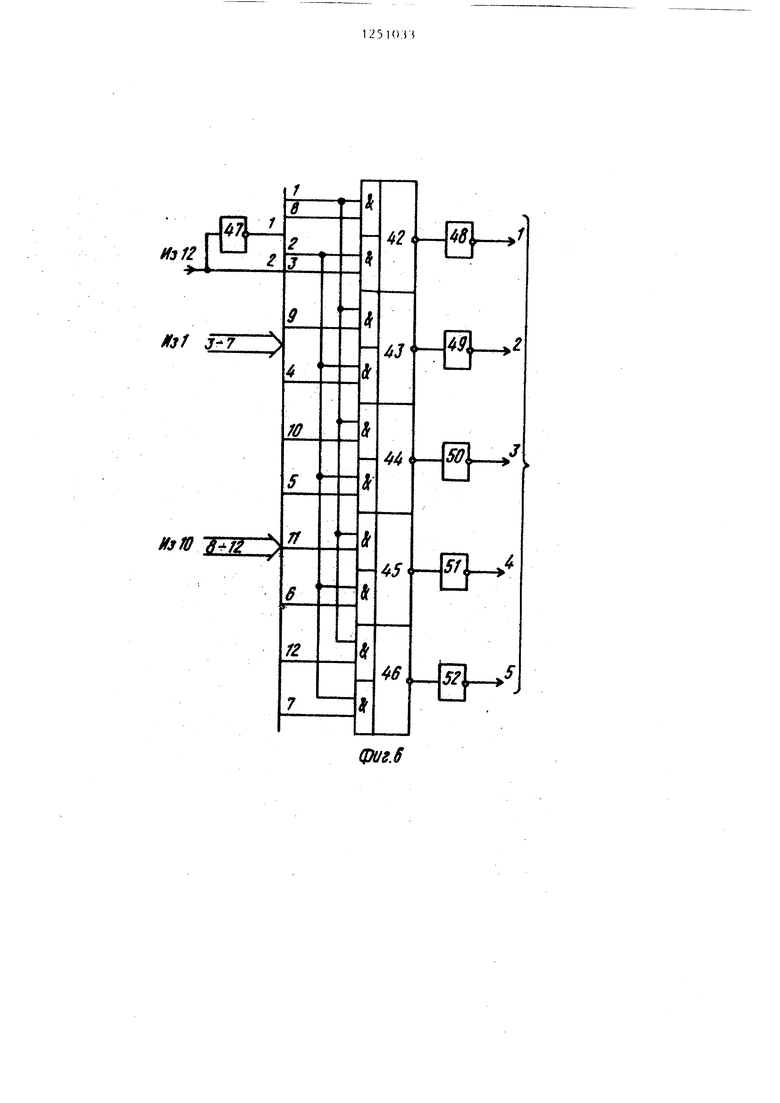

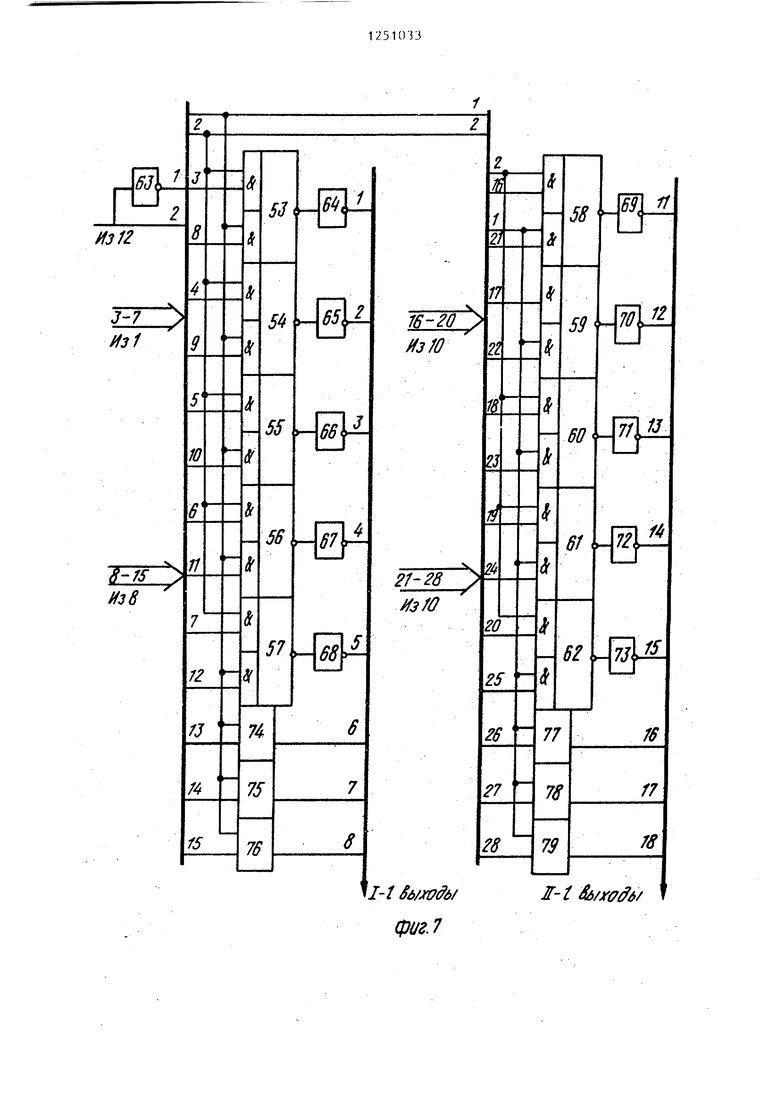

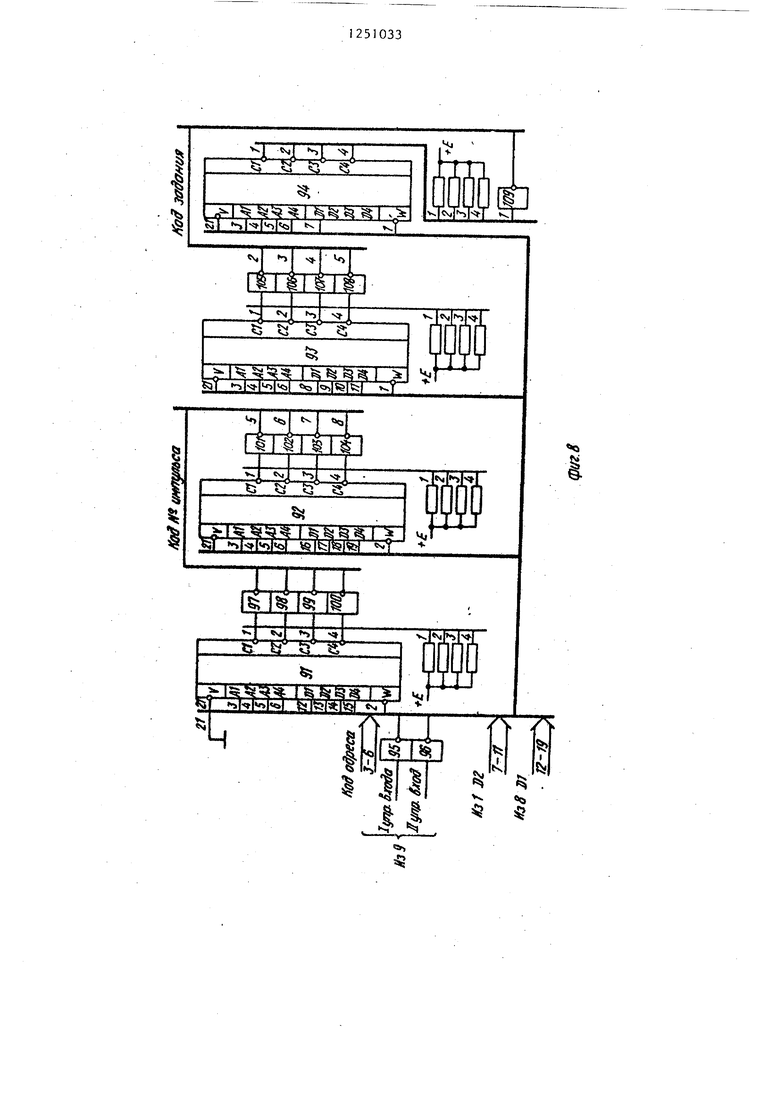

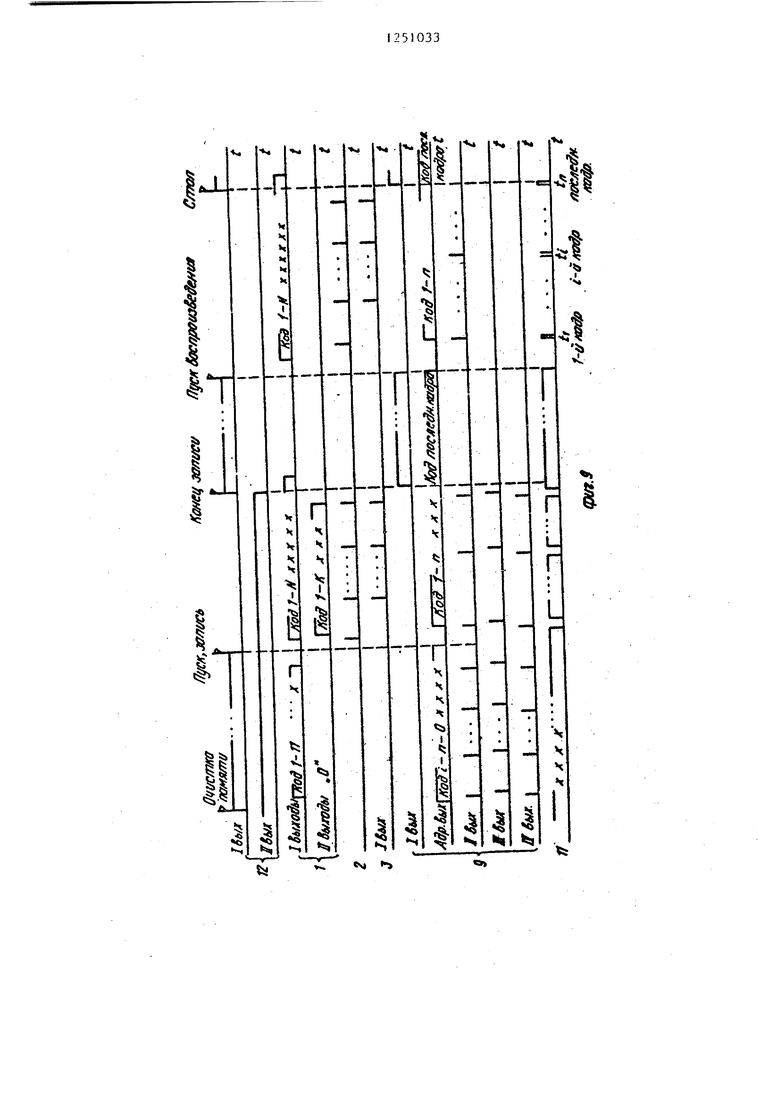

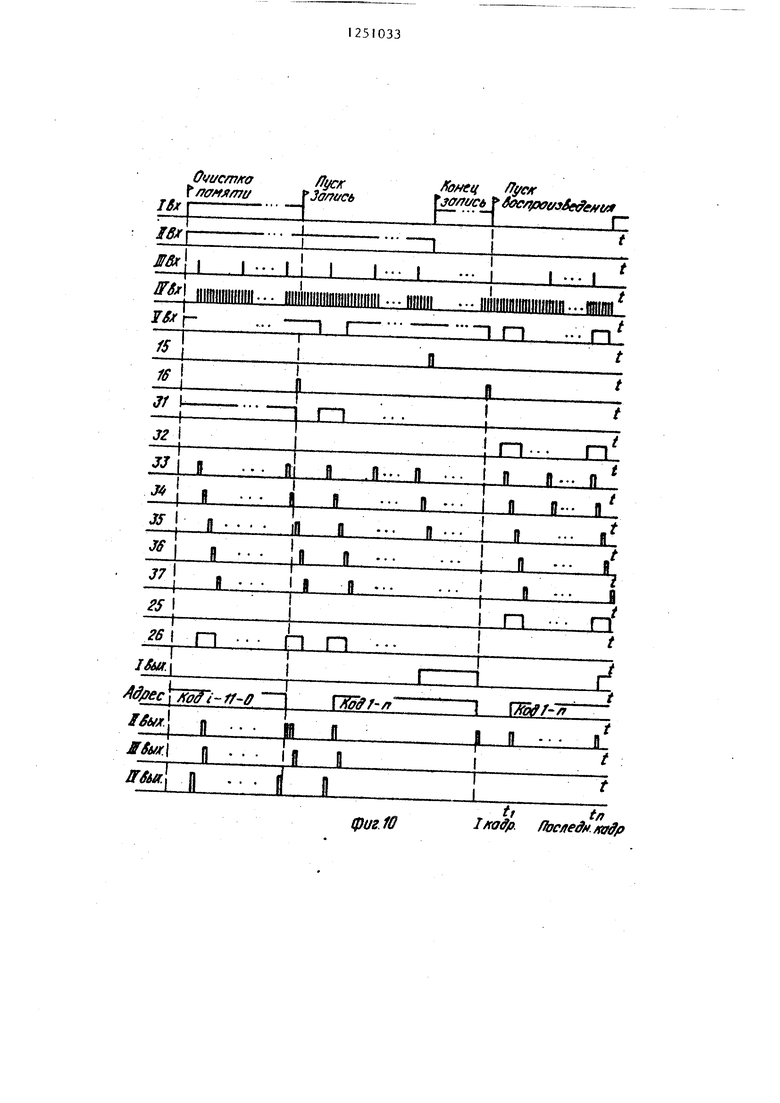

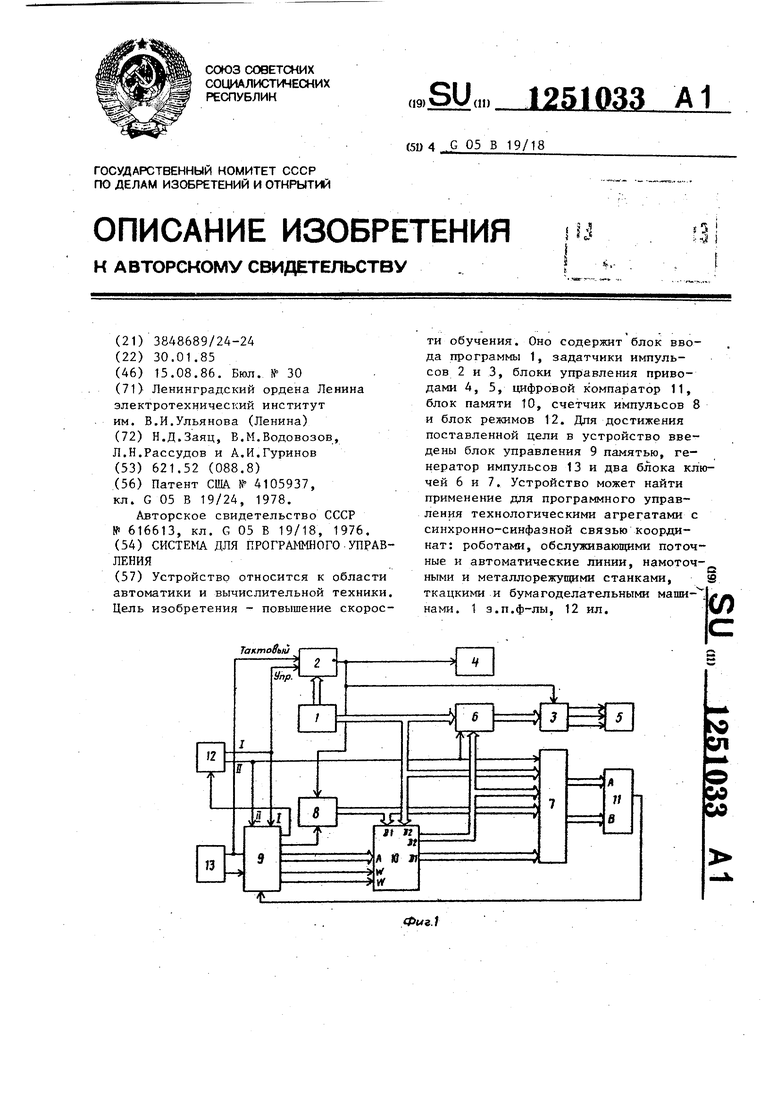

На фиг.1 изображена функциональная схема устройства; на фиг.2 - функциональная схема блока управления памятью; на фиг.З - принципиальная схема задатчика импульсов ведущего привода; на фиг.4 - принципиальная схема задатчика импульсов ведомого привода; на фиг.З принципиальная схема блока режимов; на -фиг.6 - принципиальная схема второго блока ключей; на фиг.7 - принципиальная схема первого блока ключей; .на фиг.8 - принципиальная схема блока памяти; на фиг.9 - временная диаграмма работы устройства; на фиг.10- временная диаграмма работы блока управления памятью; на фиг.11 - пример дешифратора; на фиг.12 - схема синхронизации.

Система программного управления (фиг, содержит блок 1 ввода программы задатчики импульсов ведущего привода 2 и импульсов ведомого привода 3, блок 4 управления ведущим приводом, блок 5 управления ведомым приводом, второй блок 6 ключей, первый блок 7 ключей, счетчик 8 импульсов, блок 9 управления памятью, блок 10 памяти, цифровой компаратор 11, блок 12 режимов, генератор 13 тактовых импульсов.

Блок 9 управления памятью содержит элемент НЕ 14, первый 15 и второй 16 формирователи импульсов,счетчик 17 кадров, регистр 18, компаратор 19, первый злемент И 20, дешифратор 21, делитель 22 частоты, второй элемент И 23, первый элемент ИЛИ 24, первую 25 и вторую 26 схемы синхронизации, второй элемент ИЛИ 27, третий 7.8 и четвертый 29 элементы И.

12510332

Задатчик 2 импульсов ведущего привода содержит инвертор 30, счетчик 31 импульсов, а задатчик 3 импульсов ведомого привода - инверто- 5 ры 32 и 33 и счетчик 34 импульсов. Блок 12 режимов содержит RS-триггер 35, элемент И 36, резисторы 37-39, диод 40, конденсатор 41.

Блок 6 ключей состоит из элемен- 10 тов 2-2И-ИЛИ-НЕ 42-46, элементов НЕ 47-52, а блок ключей 7 - из элементов 2-2И-ИЛИ-НЕ 53-62, элементов НЕ 63-73, элементов И 74-79

Дешифратор 21 (фиг.11) состоит 15 из элемента И 80, элементов НЕ 81-85, элемента 2И-ИЛИ-НЕ 86.

Схема 25 (26) синхронизации со- держит два RS-триггера 87 и 88, элемент И 89 и элемент НЕ 90. ZO Блок 10 памяти содержит преобразователи 91-94 кода, элементы-НЕ 95-109.

Устройство работает в одном из трех режимов. В режиме Запись про- 25 граммы в блоке 1C памяти формируется программа обработки изделия, а в режиме Воспроизведение сформиро- ваннйя программа отрабатывается на станке. В третьем режиме Очистка памяти обнуляется содержимое всех ячеек памяти.

Для очистки блока 10 памяти необходимо без пуска системы перевести ее в режим записи, для чего необходимо зафиксировать кнопку Запись в блоке 12 режимов в нажатом положении. При этом на втором выходе блока 12 режимов устанавливается сигнал 1.

30

35

40

45

50

55

на первом - также 1

От генератора 13 тактовых импульсов на второй и первый входа блока 9 управления памятью поступают две синхронизированные между собой последовательности импульсов, их частоты определяются соотношением fj 15f , а длительность импульсов по обоим входам одинакова. И& названных двух последовательностей в блоке 9 управления памятью формируется 5 тактовых последовательностей: ТИ1, ТИ2, ТИЗ, ТИ4, ТИ5, необходимых для синхронизации всех управляющих сигналов блока 9. Частота всех импульсных последовательностей одинакова и равна fjy, ,2... f , длительность импульса f, 1/f J . Импульс первой тактовой последовательности ТИ1 появляется через t 2/f2 после импульки блока 10 памяти не уска системы перевест аписи, для чего необх ровать кнопку Запись ежимов в нажатом поло том на втором выходе имов устанавливается

на первом - также 1

От генератора 13 тактовых импульсов на второй и первый входа блока 9 управления памятью поступают две синхронизированные между собой последовательности импульсов, их частоты определяются соотношением fj 15f , а длительность импульсов по обоим входам одинакова. И& названных двух последовательностей в блоке 9 управления памятью формируется 5 тактовых последовательностей: ТИ1, ТИ2, ТИЗ, ТИ4, ТИ5, необходимых для синхронизации всех управляющих сигналов блока 9. Частота всех импульсных последовательностей одинакова и равна fjy, ,2... f , длительность импульса f, 1/f J . Импульс первой тактовой последовательности ТИ1 появляется через t 2/f2 после импуль3

са частотой последовательности f, Импульсы всех остальных последовательностей сдвинуты друг относительно друга на t 2/f . Первая тактовая последовательность ТИ1 используется дпя синхронизации входных асинхронных управляющих команд, по- ступаюпщх на первый, второй и пятьй входы, блока 9. Вторая последовательность ТИ2 используется также для синхронизации и для формирования синала записи по четвертому выходу блока 9 управления памятью, С помощью третьей последовательности ТИЗ формируется сигнал обнуления счетчика 8 и смены номера кадра в блоке 9, по импульсу четвертой последовательности ТИ4 формируется сигнал записи номера импульса в память (сигнал 1.на третьем выходе блока 9). По пятому такту (ТИЗ) схемы синхронизации в блоке 9 возвращаются в исходное состояние.

Для очистки блока 10 памяти кнопка Запись блока 12 режимов фиксируется в нажатом положении. При этом на выходах блока 12 устанавливается сигнал 1. Блок 9 управления памятью постоянно с частотой fj формирует управляющие сигналы последовательно на четвертом, втором и третьих выходах, код счетчика 17 кадров (адрес ячеек памяти) изменяется на 1 в каждый период частоты f,. Если код коэффициента деления на вторых выходах блока ввода программ равен нулю, то блок 10 памяти будет полностью очищен, что дает возможность в случае необходимости Написать в него любой другой начальный код. Процесс обнуления происходит до пуска системы (фиг. О,

При пуске в режиме Запись программы кнопка Запись в блоке 12 режимов остается в нажатом состоянии. Нажимается кнопка Пуск в блоке 12 режимов, и на первом выходе его появляется сигнал О, разрешая работу задатчика 2 импульсов ведущего привода. На втором выходе блока 9 управления памятью будет сформирован управляющий сигнал обнуления счетчика 8 импульсов, при этом счетчик 17 кадров в блоке 9 будет также обнулен (см. диаграмму на фиг.11).

Первым задатчиком блока 1 ввода программы оператор заносит в задат510334

чик 2 импульсов ведущего привода коэффициент деления, отличный от нуля, и с задатчика 2 на блок управления ведущим приводом начинает поступать 5 импульсная последовательность заданной частоты, приводя в движение ведущий привод.

Вторым задатчиком блока 1 ввода программы оператор через второй 10 блок 6 ключей заносит в задатчик 3 импульсов ведомого привода коэффициент деления, отличный от нуля, и . с задатчика 2 на блок 5 управления

ведомым приводом начинает поступать 15 импульсная последовательность заданной частоты,.приводя в движение ведомый привод.

Эта же импульсная последовательность заполняет счетчик 8 импульсов.

Стремясь удержать рабочий орган на записываемой траектории, предварительно нанесенной на изделие,оператор изменяет коэффициент деления частоты в задатчике 3 ведомого привода с помощью второго задатчика блока 1 ввода программы. Как/только оператор изменит код коэффициента деления дпя ведомого .привода, цифровой компаратор 11 зафиксирует отличие кода, занесенного в память 10,( от поступившего с блока 1, и сформирует на своем выходе сигнал О. Появление О на пятом входе блока 9 управления памятью приводит к выра- ботке на четвертом выходе блока 9 управления памятью сигнала разрешения записи в блок 10 памяти номера импульса в счетчике 8 импульсов, при котором изменяется коэффициент деления . После этого увеличивается на единицу адрес сигналов по адресному входу блока 10 памяти, сигналом 1 на втором выходе блока 9 управления памятью обнуляется сче1-чик 8 импульсов и вновь формируется сигнал разрешения записи в блок 10 памяти (на этот раз на третьем выходе блока 9 управления памятью) и в блок 10 памяти заносится новый код коэффициента деления. При каждом последующем лзме- нении коэффициента деления на рторых выходах блока 1 ввода программы в текущем кадре фиксируется номер импульса со счетчика 8 импульсов, при котором произошло изменение, а затем в ячейку блока 10 памяти с адресом, на единицу большим предыдущего, записывается код коэффициента деления с блока 1 .

Код последнего кадра запоминается Р блоке 9 управления памятью в момент смены режима (при переключении клави ши Воспр./запись в положение Вое- произведение).

При переходе в режим воспроизведения на первом выходе блока 9 управления памятью вырабатывается сигнал l который устанавливает на первом вы- ходе блока 12 режимов сигнал 1 и задатчик 2 импульсов ведущего привода прекращает работу. На вход блока 3 блок 6 ключей передает коэффициент деления из блока 10 памяти, Влок 7 ключей разрешает сравнение текущего кода номера импульса со счетчика 8 импульсов и кода номера импульса из блока 10 памяти, при котором бьт сформирован очередной кадр программы

Для запуска системы в режиме Воспроизведение нажимается кнопка Пуск на блоке 12 режимов. При этом разрешается работа задатчика 2 импульсов ведущего привода, обнуляет- ся счетчик кадров блока 9 управления памятью и на втором выходе его формируется сигнал 1, обнуляющий счетчик 8 импульсов. Первым задатчиком блока 1 ввода программы оператор за- носит в задатчик 2 импульсов ведущего привода коэффициент деления, отличный от нуля (или сохраняет прежний коэффициент, бывший при записи), и с задатчика 2, на блок управления . ведущим приводом начинает поступать импульсная последовательность заданной частоты, приводя в движение ведущий привод.

Эта импульсная последовательность заполняет счетчик 8,

Влок 7 ключей передает теперь на входы цифрового компаратора 11 для сравнения коды текущего номера импульса со счетчика 8 и номера им- пульса, при котором происходит схема кадра из блока 10 памяти. В момент совпадения этих кодов на выходе цифрового компаратора 11 появляется сигнал 1, и в блоке 9 управления памятью на единицу увеличивается номер кадра (адреса), По новому адресу из блока 10 памяти извлекается новый коэффициент деления для блока б ключей, задавая новую скорость движения ведомого привода.

По завершении обработки последнег кадра, номер которого хранится в

блоке 9, блок 9 управления памятью формирует сигнал 1 на первом выходе, который приводит к останову ведущего привода (фиг.11),

Так как программа сохраняется в блоке, устройство обеспечивает многократное ее выполнение.

Ведомых координат может быть несколько. Для этого необходимо соответствующим образом увеличить объем памяти, для казкдого ведомого привода необходимо иметь свой блок 6, 3, 5, 7 и 11, Выходы всех схем цифровых компараторов должны быть объединены схемой ИЛИ, Блок 1 ввода программ должен иметь возможность задавать код деления для каждого ведомого привода. Остальные блоки системы остаются без изменения.

Рассмотрим более подробно работу системы программного управления.

Блок 1 ввода программ может быть реализован различными средствами (на фиг,2 представлен один из возможных вариантов реализации блока), Для задания коэффициентов деления здесь использованы кодовые преобразователи десятичного кода в двоичный. Для простоты изложения все схемы разработаны применительно к системе с одним ведуншм и одним ведомым приводами,

Задатчик 2 импульсов ведущего привода (фиг.З) и задатчик 3 импульсов ведомого привода (на фиг,4) построены на базе стандартных делителей частоты 31 и 34 с переменным коэффициентом деления. Значение коэффициента деления для блока 2 поступает с первых выходов блока 1, Разрешение на работу задатчика 2 импульсов, поступает на управляющий вход с первого выхода блока 12 режимов. Пока этот сигнал равен 1 на выходе задатчика 2 и-мпульсов будет нуль, ведущий и ведомый приводы неподвижны. Импульсы на С-вход блока 40 поступают с первого выхода генератора 13 импульсов. Частота с выхода блока 2 поступает на вход блока управления ведущим приводом и .на тактовый вход блока 3 одновременно с коэффициентом деления на вторы выходах блока 1, определяя скорость ведомого привода. Блоки 4 и 5 управления приводами стандартные, например типа БУ-2-64.

При наличии на управляющем входе блока 6 ключей (фиг.6) 1 (режим записи) на выходы блока и с них на информационные входы задатчика 3 импульсов ведомого привода поступает код коэффициента деления с блока 1 ввода программ.

При появлении на управляющем входе О (режим воспроизведения) на выходы проходит код крэффициента деления с блока 10 памяти.

Аналогично построен блок 7 кпю чей (фиг.7), В режиме записи на управляющем входе с блока 12 режимов устанавлива ется 1, поэтому на пер- вые и вторые выходы поступают для сравнения в цифровом компараторе 11 коды коэффициентов деления с блока 1 и блока 10 памятиi При изображении схем системы условно принято, что код коэффициента деления не будет превышать 4-х двоичных разрядов, а разрядность счетчика 8 не будет выше 8 двоичных разрядов, поэтому для пропуска через блок 78-разрядного кода номера импульса помимо схем 2-2И-ИЛИ-НЕ использованы элементы И.

В режиме воспроизведения на управляющем входе блока 7 будет О, что позволит пройти для сравнения в цифровом компараторе 11 кодам текущего номера импульса и номера импульса из блока 10 памяти, при котором произошла смена кадра.

Блок режимов представлен на фиг.5 В исходном состоянии после включения питания с помощью элемента И 36 на инверсном выходе Е8-триг1;ера 35 будет установлена 1, что позволит обнулить блок 2- по управляющему вхо- ду и подготовить к работе блок 9. Сигнал на втором выходе блока 12 режимов непосредственно зависит от положения клавиши Воспр./запись. Если она зафиксирована в нижнем по- ложении, что соответствует режиму записи, то на втором выходе будет 1 Пуск системы обеспечивается нажатием клавиши Пуск, при этом появляется О на S-входе RS-триггера 35, и на первом выходе блока 12 устанавливается О, разрешая работу блока 2. Остановка наступает либо по окончании режима записи (клавишу Воспр,/запись необходимо зафикси- ровать в верхнем положении), либо в режиме воспроизведения, так как в том и другом случае на входе с блока 9 появляется сигнал окончания пр граммы (переход из О в 1), уста навливается на первом выходе блока режимов сигнал 1,

Повторный пуск обеспечивается нажатием на клавишу Пуск. Функциональная схема блока 9 управления памятью приведена на фиг.2, а на фиг, показана временная диаграмма работы составных частей блока 9, Перед на- чалом записи программы с помощью блока 12 на первом выходе блока управления памятью будет установлена 1,-на втором входе - также 1, На пятом входе сигнал может быть любым в зависимости от значений кодов с вторых выходов блока 1 (фиг,1) и блока 10 памяти. Счетчик 17 кадров (фиг.2) может находиться в произвольном состоянии. Для очистки памяти надо, не запуская системы, установить код коэффициента деления на вторых выходах блока 1 равным нулю, тогда на первом (31) выходе дешифратора 21 (фиг,2) установится 1, На выходе второй схемы 26 синхронизации в каждом периоде частоты сигнал 1 появляется по импульсу тактовой последовательности ТИ2, поступающему с выхода 34 делителя частоты 22, что позволяет этому же импульсу последовательности ТИ2 пройти через четвертый ключ 39 на IV выход блока 9 управления и далее на вход записи блока 10 памяти, где записывается код номера импульса со счетчика 8 на фиг,1, В первый момент после включения питания он может оказаться нулевым, но после первого же цикла записи счетчик будет обнулен и до пуска системы его состояние не изменится. Таким образом, та часть памяти, в которую записывается номер импульса, будет очищена

Сигнал 1 с выхода схемы 26 (фиг,2), пройдя через второй элемент ИЛИ 27 на вход второго элемента И 23 разрешает пройти импульсу тактовой последовательности ТИЗ на счетный вход счетчика 17 кадров, тем саг-1ым изменяя его код на 1, и через пер- вый элемент ИЛИ 24 - на второй выход блока 9 и далее на вход сброса счетчика 8, обнуляя его. Импульс тактовой последовательности ТИ4, пройдя через третий элемент, И 28 на третий выход блока 9, обнуляет ячей-

9125

у памяти, адрес которой определен четчиком 17 кадров.

Импульс последовательности ТИ5 возвращает вторую схему 26 синхронизации в исходное состояние (О на выходе), то же самое будет сделано со схемой 25 в режиме Воспроизведение (см, диаграмму на фиг.10),

Рассмотренный процесс обнуления памяти происходит в каждом периоде частоты fJ , поступающей на третий вход блока 9, до пуска системы.

При пуске системы в режиме записи на первом входе блока 9 появляется О, При этом второй формирователь 16 импульсов формирует импульс, который обнуляет счетчик 17 кадров и через схему 24 - счетчик 8 (фиг,1).

Над диаграмме (фиг.10) рассмотрен частный случай появления двух им- пульсов подряд в течение периода час- тоты fj , что не является сбоем, поскольку импульс на вход записи счетчика 8 (фиг.1) может придти не раньше первого после пуска импульса тактовой частоты с первого выхода генератора 13 тактовых импульсов.

Начинается процесс записи программы. При изменении кода на вторых выходах блока 1 цифровой компаратор 1 1 устанавливает отличие кодов из блока 1 и из блока 10 памяти, на пятом входе блока 9 появится О, дешифратор 21 (фиг.9) на первом выходе 31 формирует 1. Сигнал 1 после синхронизации во второй схеме 26 производит, как показано на диаграмме (фиг.12), вначале запись в ячейку памяти с адресом 00-00 номера импульса со счетчика 8, при котором изменяется код коэффициента деления, затем изменяется на единицу код адреса ячейки (номер кадра) и обнуляет счетчик 8. В следукщем такте записывается код коэффициента деления.

Повторное изменение коэффициента деления приводит сначала к записи Номера импульса, при котором произошло изменение, в ячейку памяти с адресом 00-01, затем к смене адреса и записи нового коэффициента деления.

По окончании программы клавишу Еоспр./Запись необходимо возвратить в верхнее положение. При этом на втором входе блока 9 появляется О, первьй формирователь 15 (фиг.2) формирует импульс, который записывает в регистр 18 номер пос

3, 0

леднего кадра программы. По окончании записи на выходе регистра 18 оказывается тот же код, что и на выходе счетчика 17, что выявляется цифровым

компаратором 19. На его выходе () появляется сигнал 1, которьш через первый ключ 20 поступает на первый выход блока 9 и далее на вход блока 12 режимов.. Происходит остановка

системы.

При повторном пуске уже в режиме воспроизведения ведомый привод работает от программы. Счетчик 17 кадров и счетчик 8 (фиг.1) обнуляется при пуске импульсом, сформированньм вторым формирователем 16 (фиг.2). На входы цифрового компаратора 11 (фиг.1) при этом поступают код номера импульсов со счетчика 8 и код, записан-, ный в блоке 9 памяти в ячейке с нулевым адресом. Когда поступает равенство кодов, на выходе компаратора 11 появляется .1, на втором выходе 32 дешифратора 21 (фиг.2) формируется сигнал 1, который после синхронизации в схеме 25 разрешает прохождение импульса тактовой последовательности ТИЗ через второй ключ 23. Данный импульс увеличивает на 1 номер кадра в счетчике 17 и, пройдя через первый элемент .ИЛИ 24, обнуляет счетчик 8. Коэффициент деления из блока 10 памяти через первый блок 6 поступает на входы задатчика 3 импульсов ведомого привода, устанавливая ведомому приводу необходимую скорость. По окончании первого кадра компаратор 11 вновь выявляет равенство кодов импульсов и увеличивает номер кадра на единицу и т.д.

По окончании программы компаратор 11 (фиг.1) выявляется номер им- пульса, при котором коэффициент деления на вторых выходах блока 1 был ус- становлен равным нулю, и формирует

на своем выходе сигнал 1, счетчик 17 кадров (фиг.9) устанавливает на своих выходах код последнего кадра.

на входах А и В компаратора 19 коды ргГвны, и на его выходе появляется 1, сбрасывая по С-выходу триггер 35 (фиг.5) в исходное состояние. Система остановлена. Блоки 2 и 8 обнулены. Счетчик 17 кадров (фиг.9) также обнулен импульсом тактовой последовательности ТИЗ.

11

Формула изобретени

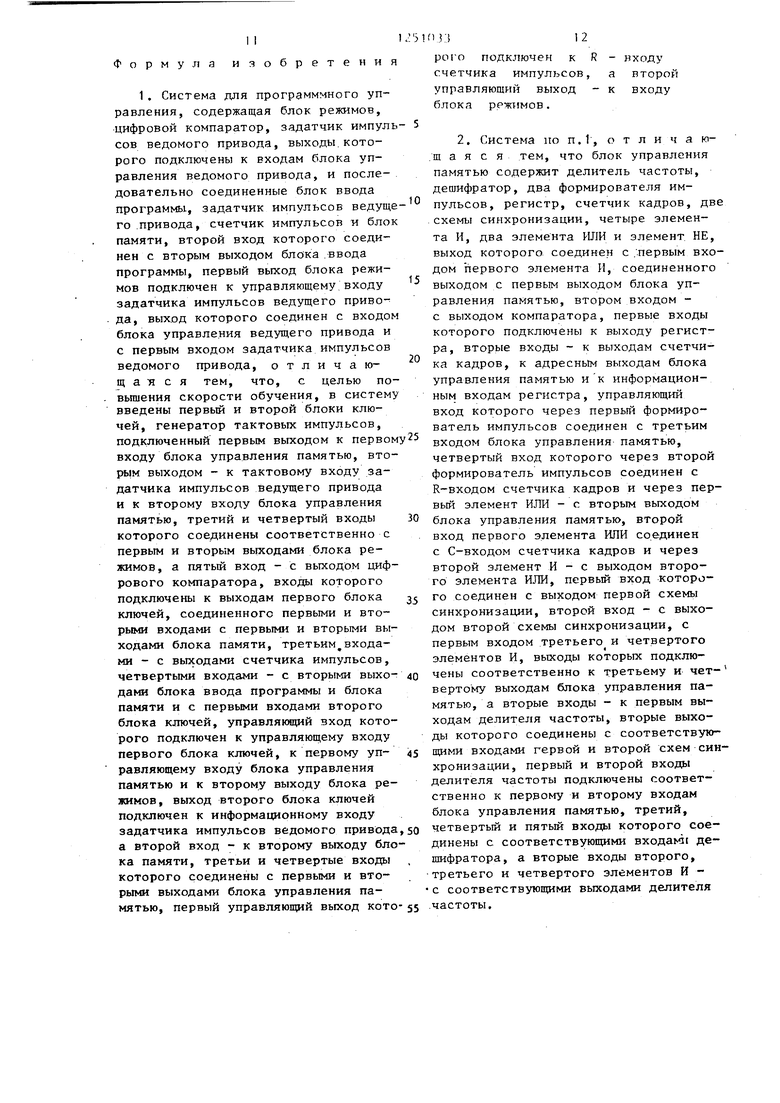

1. Система для программмного управления, содержащая блок режимов, цифровой компаратор, задатчик импул сов ведомого привода, выходы.которого подключены к входам блока управления ведомого привода, и последовательно соединенные блок ввода программы, задатчик импульсов ведущ го .привода, счетчик импульсов и бло памяти, второй вход которого соединен с вторым выходом блока .ввода программы, первый выход блока режимов подключен к управляющему входу задатчика импульсов ведущего приво- да, выход которого соединен с входо блока управле.ния ведущего привода и с первым входом задатчика импульсов ведомого привода, отличающаяся тем, что, с целью по вьпцения скорости обучения, в систем введены первый и второй блоки ключей, генератор тактовых импульсов, подключенный первым выходом к перво входу блока управления памятью, вторым выходом - к тактовому входу задатчика импульсов ведущего привода и к второму входу блока управления памятью, третий и четвертый входы которого соединены соответственно с первым и вторым вьпсодами блока режимов, а пятый вход - с выходом цифрового компаратора, входы которого подключены к выходам первого блока ключей, соединенного первыми и вторыми входами с первыми и вторыми выходами блока памяти, третьим входами - с выходами счетчика импульсов, четвертыми входами - с вторыми выхо- дани блока ввода программы и блока памяти и с первьми входами второго блока ключей, управляквций вход которого подключен к управляющему входу первого блока ключей, к первому уп- равляющему входу блока управления памятью и к второму выходу блока режимов, выход второго блока ключей подключен к информационному входу задатчика импульсов ведомого привода а второй вход - к второму выходу блока памяти, третьи и четвертые входы которого соединены с первыми и вторыми выходами блока управления памятью, первый управляющий выход кото

10

15

20

I. J

5 зо 35 40 45 so 55

ifij.

рого подключен к R - входу счетчика импульсов, а второй управляющий выход - к входу блока режимов.

2. Система по п.1, о т л и ч а ю- щ а я с я тем, что блок управления памятью содержит делитель частоты, дешифратор, два формирователя импульсов, регистр, счетчик кадров, две схемы синхронизации, четыре элемента И, два элемента ИЛИ и элемент НЕ, выход которого соединен с.первым входом первого элемента И, соединенного выходом с nepBbiM выходом блока управления памятью, втором входом - с выходом компаратора, первые входы которого подключены к выходу регистра, вторые входы - к выходам счетчика кадров, к адресным выходам блока управления памятью и к информационным входам регистра, управляющий вход которого через первьй формирователь импульсов соединен с третьим входом блока управления памятью, четвертый вход которого через второй формирователь импульсов соединен с R-входом счетчика кадров и через первый элемент ИЛИ - с вторым выходом блока управления памятью, второй вход первого элемента ИЛИ соединен с С-входом счетчика кадров и через второй элемент И - с выходом второго элемента ИЛИ, первый вход которого соединен с выходом первой схемы синхронизации, второй вход - с выходом второй схемы синхронизации, с первым входом третьего и четвертого элементов И, выходы которых подключены соответственно к третьему и чет- вертому выходам блока управления памятью, а вторые входы - к первым выходам делителя частоты, вторые выходы которого соединены с соответствующими входами гервой и второй схем синхронизации, первый и второй входы делителя частоты подключены соответственно к первому и второму входам блока управления памятью, третий, четвертый и пятый входы которого соединены с соответствующими входам дешифратора, а вторые входы второго, третьего и четвертого элементов И - с соответствующими выходами делителя .частоты.

1б,0д У

Uwffft - Т Вход °,

Wl J3

Ifblfffg

фаг. 5

(pui.S

фиг. 7

ч Ча

a

iTTm

««V4

Ы

t; t3 g S

саж r

г

vsit

S2

G

fells te

i

} «SI

Ь Ь q

e

юкга -NT

irm

1

3

I

V

v

«

p

k

4

fe

fe

Ovucmffoffyc/r

flffftjtmu JBx I1

ffS6fif. ij

ILL

УЩ H

I fl

/tofffH ffyc/f

jff i/C6f &bcfy 0e/yfe f/fu

TJ

titfl

Iffofffl. ftoc/ie H./arffp

Редактор Е.Коте

Составитель И,Швец Техред Н.Бонкапо

Заказ 4409/43 Тираж 836Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие,,г.Ужгород, ул. Проектная, 4

Q}U2.ff

(UZ.iZ

Корректор Е.Рошко

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство компенсации сигнала царапин кинопленки | 1988 |

|

SU1536521A2 |

| Функциональный интерполятор | 1986 |

|

SU1383301A1 |

| Устройство прерывистой радиосвязи | 1989 |

|

SU1748263A1 |

| Устройство для опроса информационных каналов | 1982 |

|

SU1062677A1 |

| Устройство для программного управления | 1985 |

|

SU1327059A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ НАГРУЖЕНИЕМ ПРИ ПРОГРАММНЫХ ИСПЫТАНИЯХ МЕХАНИЧЕСКИХ КОНСТРУКЦИЙ НА УСТАЛОСТНУЮ ПРОЧНОСТЬ | 2007 |

|

RU2365963C2 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЯ | 1992 |

|

RU2045781C1 |

| Программное задающее устройство | 1981 |

|

SU991376A1 |

| Устройство для кинематического дробления стружки на токарных станках с числовым программным управлением | 1981 |

|

SU1004974A1 |

| Функциональный интерполятор | 1985 |

|

SU1272311A1 |

Устройство относится к области автоматики и вычислительной техники. Цель изобретения - повышение скорости обучения. Оно содержит блок ввода программы 1, задатчики импульсов 2 и 3, блоки управления приводами 4, 5, цифровой компаратор 11, блок памяти 10, счетчик импульсов 8 и блок режимов 12. Для достижения поставленной цели в устройство введены блок управления 9 памятью, генератор импульсов 13 и два блока ключей 6 и 7, Устройство может найти применение для программного управления технологическими агрегатами с синхронно-синфазной связью координат: роботами, обслуживающими поточные и автоматические линии, намоточными и металлорежупщми станками, Э ткацкими и бумагоделательными маши- , нами. 1 э.п.ф-лы, 12 ил. СО

| Патент США № 4105937, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для позиционного программного управления | 1976 |

|

SU616613A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1986-08-15—Публикация

1985-01-30—Подача