Изобретение относится к радиотехнике и может быть использовано в радиосистемах передачи дискретной информации, а также в совмещенных измерительно-информационных системах, использующих фазоманипулированные псевдослучайные радиосигналы.

Цель изобретения - сокращение времени приема фазоманипулированных псевдослучайных сигналов.

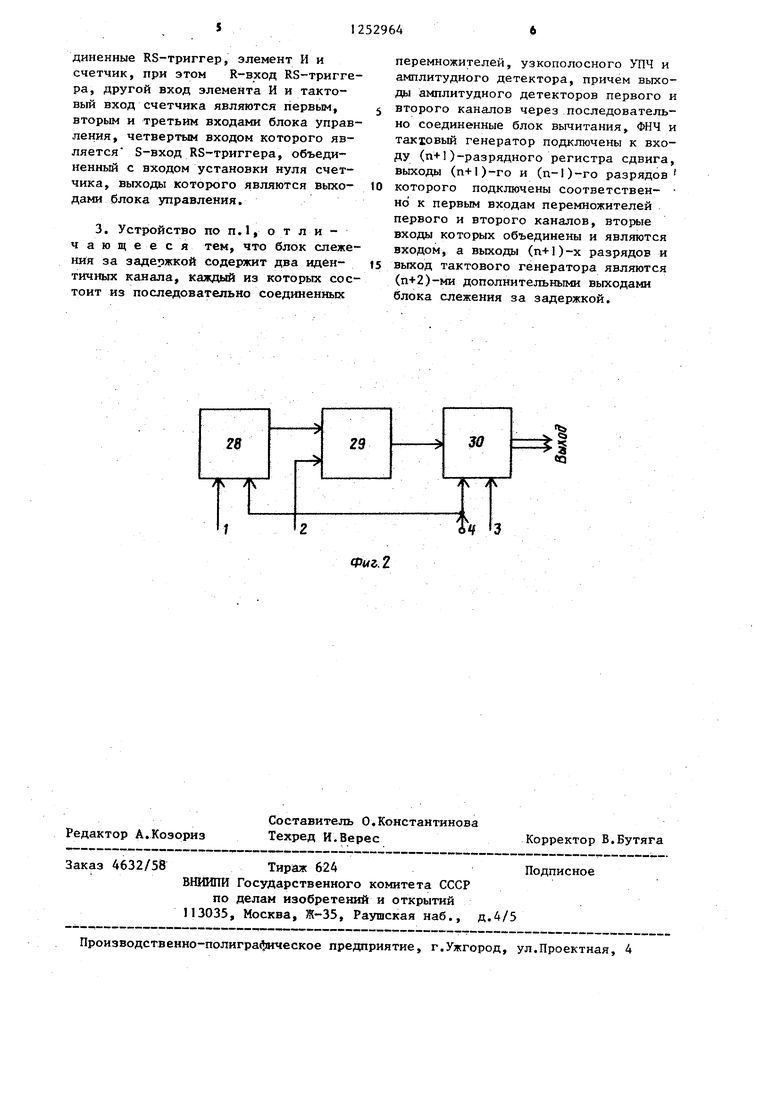

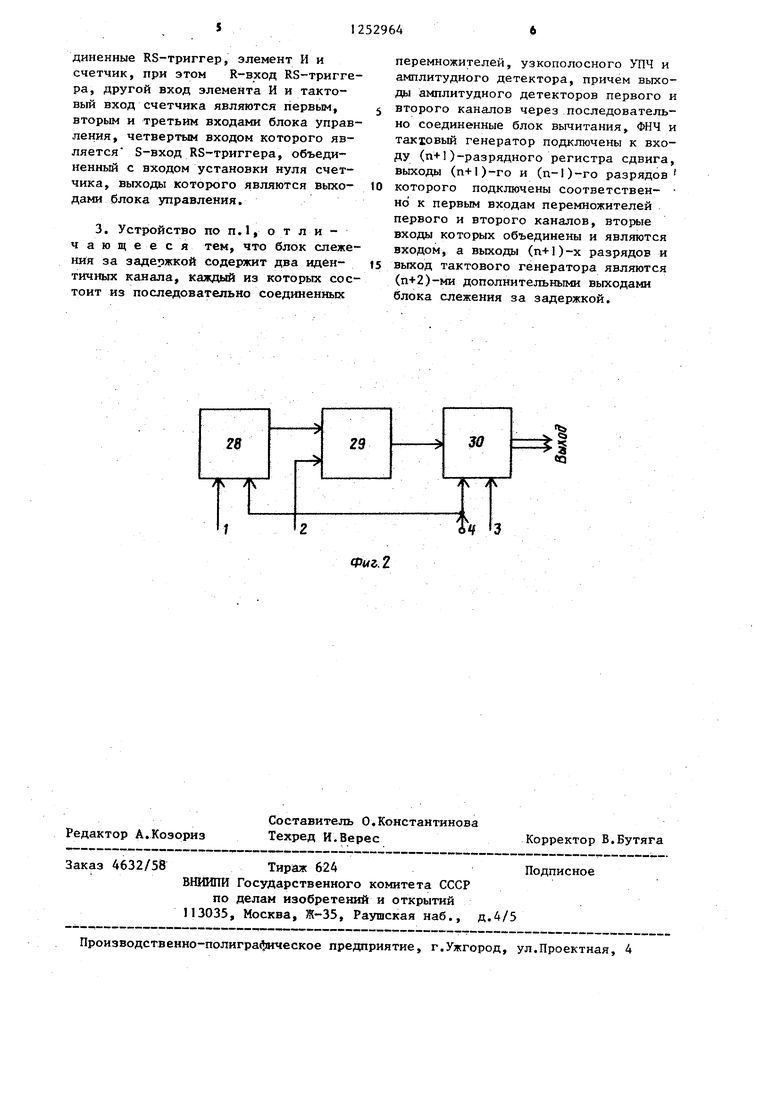

На фиг. 1 приведена структурно- электрическая схема устройства дпя корреляционного приема фазоманипули- рованных псевдослучайных сигналов J на 4мг« 2 - структурно-электрическая схема блока управления.

Устройство для корреляционного приема фазоманипулированных псевдослучайных сигналов содержит смеситель 1, широкополосный усилитель 2 промежуточной частоты (иШ1Ч), фазовый демодулятор 3, узкополосный усилитель 4 промежуточной частоты (УПЧ), фазовый детектор 5, опорный гетеродин 6, фильтр 7 нижних частот (ФНЧ), управлякяций элемент 8, управляемый генератор 9,сумматор IО, цифроанало- говый преобразователь (ЦАП) 11, амплитудный детектор 12, ключ 13, компаратор 14, блок 15 управления, депшф- ратор 16, Блок 17 слежения за задержкой содержит регистр 18 сдвига, тактовый генератор 19, первый 20 и второй 21 перемножители, узкополосные УПЧ 22 и 23, амплитудные детекторы 24 и 25, блок 26 вычитания, фильтр 27 нижних частот (ФНЧ), Блок 15 управле- 1ШЯ состоит из RS-триггера 28, элемента И 29 и счетчика 30.

Устройство для корреляционного приема фазоманипулированных псевдослучайных сигналов работает следую- образом.

Перед началом работы на четвертый вход блока }5 с пульта управления системы поступает импульс (для этого оператор нажимает кнопку на пульте), устанавливающий RS-триггер 28 блока 15 в состояние 1 и обнуляющий счет10

15

входного сигнала на промежуточную частоту в смесителе 1, далее через ШУПЧ 2 сигнал поступает на входы первого 20 и второго 21 перемножителей, на другие входы которых с выходов (п+1)-го и (п-1)-го разрядов регистра 18 подаются модулирующие псевдослучайные последовательности,сдвинутые один относительно другого на 2 to , где to - длительность одного элемента псевдослучайной последовательности. Если одна из опорных псевдослучайных последовательностей совпадает по задержке с входным сигналом в большей степени, чем другая, то в со- ответствукяцем перемножителе 20 или 21 произойдет более полное восстановление несущей входного сигнала, а на выходе соответствующего амплитудного

20 детектора 24 или 25 появится напряжение, превышакмцее напряжение на выходе другого канала. Разность этих напряжений с выхода блока 26 через ФНЧ 27 поступает на вход тактового

25 генератора 19 и осуществляет подстройку его частоты. После установления синхронизма по задержке с выхода разряда регистра 18 синхронная опорная псевдослучайная последовательность поступает на вход фазового демодулятора 3, на другой вход которого поступает входной фазоманипули- рованный сигнал с выхода ЩУПЧ 2. В фазовом демодуляторе 3 происходит

35 сжатие входного сигнала по спектру, и восстановленная несущая с выхода фазового демодулятора 3 через узкополосный УПЧ 4 поступает на вход амплитудного детектора 25, с выхода

40 которого сигнал через ключ 13, открываемый импульсами, поступающими с выхода дешифратора 16 в моменты окончания формируемой на выходе п-го разряда регистра 18 сдвига опорной псев45 дослучайной последовательности, подается на вход компаратора 14. Выход компаратора 14 подключен к первому входу блока 15. В режиме захвата по частоте каждый раз в момент оконча30

чйк 30. На управлякяций вход компара- 50 ния очередной опорной псевдослучай- тора 14 подается постоянное порого- ной последовательности выходное напряжение амплитудного детектора 25 сравнивается с пороговым уровнем компаратора 14. Если имеется частотная нала на выходе амхг титудного детекто- 55 расстройка, сигнал на выходе компара- ра 25 в режиме синхронизма в моменты, тора 14 отсутствует, RS-триггер 28

блока 15 находится в состоянии и импульсы с выхода дешифратора 16,

вое напряжение, величина которого определяется Допустимой вероятностью ложной синхронизации и уровнем сигкогда открывается ключ 13, На входе устройства осуществляется перенос

5

входного сигнала на промежуточную частоту в смесителе 1, далее через ШУПЧ 2 сигнал поступает на входы первого 20 и второго 21 перемножителей, на другие входы которых с выходов (п+1)-го и (п-1)-го разрядов регистра 18 подаются модулирующие псевдослучайные последовательности,сдвинутые один относительно другого на 2 to , где to - длительность одного элемента псевдослучайной последовательности. Если одна из опорных псевдослучайных последовательностей совпадает по задержке с входным сигналом в большей степени, чем другая, то в со- ответствукяцем перемножителе 20 или 21 произойдет более полное восстановление несущей входного сигнала, а на выходе соответствующего амплитудного

0 детектора 24 или 25 появится напряжение, превышакмцее напряжение на выходе другого канала. Разность этих напряжений с выхода блока 26 через ФНЧ 27 поступает на вход тактового

5 генератора 19 и осуществляет подстройку его частоты. После установления синхронизма по задержке с выхода разряда регистра 18 синхронная опорная псевдослучайная последовательность поступает на вход фазового демодулятора 3, на другой вход которого поступает входной фазоманипули- рованный сигнал с выхода ЩУПЧ 2. В фазовом демодуляторе 3 происходит

5 сжатие входного сигнала по спектру, и восстановленная несущая с выхода фазового демодулятора 3 через узкополосный УПЧ 4 поступает на вход амплитудного детектора 25, с выхода

0 которого сигнал через ключ 13, открываемый импульсами, поступающими с выхода дешифратора 16 в моменты окончания формируемой на выходе п-го разряда регистра 18 сдвига опорной псев5 дослучайной последовательности, подается на вход компаратора 14. Выход компаратора 14 подключен к первому входу блока 15. В режиме захвата по частоте каждый раз в момент оконча0

поступающие на второй вход блока 15, которым является второй вход элемента И 29 блока 15, проходят через элемент И 29 на счетный вход счетчика 30 блока 15, так как на первый вход элемента И 29 подана логическая 1 с выхода RS-триггера 28 блока 15 К старших разрядов счетчика 30 являются выходом блока 15 и подключены к входу ЦАП 11. Выходное напряжение ЦАП 11 через сумматор 10. на другом входе которого до момента захвата по частоте управляющее напряжение отсутствует, поступает на управляющий элемент 8 и устанавливает значение частоты управляемого генератора 9,со ответствукнцее определенному частотному интервалу полосы захвата.Частота управляемого генератора 9 остается неизменной в течение времени, от- веденного на захват частоты сигнала в каждом частотном интервале и определяемого числом поступивших с выхо да дешифратора 16 импульсов. При изменении содержимого, младшего из К задействованных разрядов счетчика 30 меняется управляющее напряжение на выходе ЦАП 11 и управляемый генератор 9 скачком переключается на новую частоту, соответствукицую соседнему частотному интервалу полосы захвата, и так до тех пор, пока в одном из частотных интервалов произойдет зах- частоты. В этот момент выходной сигнал амплитудного детектора 25, поступающий через ключ 13 на компаратор 14, превышает пороговый уровень. На первый вход блока 15 поступает импульс, переключающий RS-триггер 28 блока 15 в состояние О, при этом элемент И 29 блокируется, а содержимое счетчика 30 и выходное напряжение ЦАП И фиксируется. Управляющее напряжение подается на вход управляющего элемента 8 с выхода сумматора 10 и представляет собой сумму постоянной составляющей, которая поступает на первый вход сумматора 10 с выхода ЦАП 1I, и переменной составляющей, которая поступает на второй вход сумматора 10 с выхода №4 7. В режиме синхронизма: формируемая на выходе п-го разряда регистра 18 псев дослучайная последовательность н когерентный сигнал на выходе управляе- мого генератора 9 могут быть использованы для корреляционного приема информации. Задержки псевдослучайной последовательности, снимаемой с п-го разряда регистра 18, относительно излучаемой передатчиком может быть использована для измерения расстояния до объекта управления, а частота сигнала с выхода управляемого генератора 9 - для измерения скорости объекта.

Формула изобретения

1. Устройство для корреляционного приема фазоманипулированных псевдослучайных сигналов, содержащее последовательно соединенные смеситель, широкополосный усилитель промежуточной частоты (ШУПЧ) фазовый демодулятор, узкополосный усилитель промежуточной частоты (УПЧ), фазовый детектор и фильтр нижних частот (ФНЧ), а также управляющий элемент, выход которого через управляемый генератор подключен к первому входу смесителя, опорный гетеродин, выход которого подключен к другому входу фазового детектора, и блок слежения за задержкой, к входу которого подключен выход ШУПЧ, а выход блока слежения за задержкой подключен к другому входу фазового демодулятора, причем второй вход смесителя является входом, а выходы управляемого генератора и блока слежения за задержкой - соответственно выходами устройства, отличающееся тем, что, с целью сокращения времени приема фазоманипулировантлх псевдослучайных сигналов, введены дешифратор и последовательно соединенные амплитудный детектор, ключ, компаратор, блок управления, цифроаналоговый преобразователь (ЦАП) и сумматор, при этом (п+1) дополнительных выходов блока слежения за задержкой через дешифратор подключенны к объединенным второму входу ключа и второму входу блока управления, к третьему входу которого подключен (п+2)-й дополнительный выход блока слежения за задержкой, а четвертый вход блока управления является входом сигнала установки нуля, выход узкополосного УПЧ подключен к входу амшитудного детектора, а выход ФНЧ через сумматор - к Bxojuy управляккцего элемента.

2. Устройство по п.1, о т л и - чающееся тем, что блок управления содержит последовательно соединенные RS-триггер, элемент И и счетчик, при этом R-вход КЗ-триггера, другой вход элемента И и тактовый вход счетчика являются первым, вторым и третьим входами блока управления, четвертым входом которого является S-вход RS-триггера, объединенный с входом установки нуля счетчика, выходы которого являются выходами блока управления.

3. Устройство по П.1, от ли - чающееся тем, что блок слеже ния за задержкой содержит два идентичных канала, каждый из которых сое тоит из последовательно соединенньрс

Редактор А.Коэориз

Составитель О.Константинова Техред И.Верес

Заказ 4632/58Тираж 624

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

перемножителей, узкополосного Я1Ч и амплитудного детектора, причем выхода амплитудного детекторов первого и второго каналов через последовательно соединенные блок вычитания , ФНЧ и такювый генератор подключены к входу (п+1)-разрядного регистра сдвига, выходы (п+1)-го и (n-I)-ro разрядов которого подключены соответствен- но к первым входам перемножителей первого и второго каналов, вторые входы которых объединены и являются входом, а выходы (п+1)-х разрядов и выход тактового генератора являются (п+2)-ми дополнительными выходами блока слежения за задержкой.

§ I

Корректор В.Бутяга

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Следящий фильтр фазоманипулированного псевдослучайного сигнала | 1986 |

|

SU1394411A1 |

| Следящий фильтр фазоманипулированного псевдослучайного сигнала | 1982 |

|

SU1072252A1 |

| РАДИОЛИНИЯ С АМПЛИТУДНО-ФАЗОМАНИПУЛИРОВАННЫМИ ШУМОПОДОБНЫМИ СИГНАЛАМИ | 1996 |

|

RU2101871C1 |

| Устройство синхронизации широкополосных псевдослучайных сигналов | 1985 |

|

SU1415445A1 |

| ИЗМЕРИТЕЛЬ ФАЗ ОСЦИЛЛОГРАФИЧЕСКИЙ | 2005 |

|

RU2314543C2 |

| ЦИФРОВОЙ МОДЕМ КОМАНДНОЙ РАДИОЛИНИИ ЦМ КРЛ | 2013 |

|

RU2548173C2 |

| ПОМЕХОЗАЩИЩЕННАЯ СИСТЕМА СВЯЗИ | 2004 |

|

RU2285344C2 |

| Следящий фильтр для некогерентной обработки сигнала с подавленной несущей фаза которого манипулирована по закону бинарной псевдослучайной последовательности | 1967 |

|

SU710008A1 |

| СИСТЕМА РАДИОСВЯЗИ | 1992 |

|

RU2085038C1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2006 |

|

RU2316905C1 |

Изобретение относится к радиотехнике и может использоваться в системах передачи дискретной информации. Цель изобретения - сокращение времени приема фазоманипулированных псевдослучайных сигналов. Устройство содержит смеситель 1, широкополос- шлй усилитель 2 промежуточной частоты, фазовый демодулятор 3, узкополосный усилитель 4 промежуточной частоты, фазовый детектор 5, опорный гетеродин 6, фильтр 7 нижних часют, управляющий элемент 8, управляемый генератор 9, сумматор 10, ЦАП 11, амплитудный детектор 12, ключ 13,компаратор 4, блок 15 управления, дешифратор 16, блок 17 слежения за задержкой. Дается выполнение блока управления и блока слежения за задержкой. Цель изобретения достигается за счет введения дешифратора 16, амплитудного детектора 12, ключа 13, компаратора.14, блока 15 управления, ЦАП 11 и сумматора 10. 2 з.п.ф-лы. 2 иЛ, о (Л Ч5

| Спилкер Дж | |||

| Цифровая спутниковая связь | |||

| Перев | |||

| с англ,/Под ред | |||

| В.В.Маркова | |||

| М.: Связь, 1979 с.592 | |||

| Следящий фильтр для некогерентной обработки сигнала с подавленной несущей фаза которого манипулирована по закону бинарной псевдослучайной последовательности | 1967 |

|

SU710008A1 |

Авторы

Даты

1986-08-23—Публикация

1984-11-15—Подача