Предлагаемое изобретение относится к области радиотехники и может быть использовано для передачи дискретной информации в условиях радиоэлектронного противодействия (РЭП) и большого числа непреднамеренных узкополосных помех.

Известно, например (Борисов В.И. и др. Помехозащищенность систем радиосвязи с расширением спектра сигналов методом псевдослучайной перестройки рабочей частоты. - М.: Радио и связь, 2000 г.), что для затруднения постановки прицельных по частоте и времени помех средствами РЭП противника применяются сигналы с псевдослучайной перестройкой рабочей частоты (ППРЧ). При медленной ППРЧ на одной частотной позиции передается один или несколько информационных символов. Однако если эта позиция поражена узкополосной помехой, правильная демодуляция информационных символов будет невозможна.

При быстрой ППРЧ, когда один информационный символ делится на временные отрезки и передается на разных частотах, происходит значительное расширение спектра сигнала на каждой частотной позиции, что повышает вероятность поражения узкополосной помехой. Пусть длительность информационного символа равна 100 мксек, тогда ширина спектра сигнала (по первым нулям) составит 20 КГц, что сравнимо с шириной спектра одной узкополосной помехи.

Если разделить информационный символ на 10 временных отрезков, то ширина спектра при передаче каждого из них составит 200 КГц. При такой полосе велика вероятность попадания в нее хотя бы одной узкополосной помехи на любой частотной позиции. Кроме того, при демодуляции сигнала на каждой частотной позиции в 10 раз снижается отношение сигнал/шум.

Известны системы, в которых используются когерентные частотно-манипулированные сигналы (КЧМнС или ДЧМ-сигналы), предусматривающие когерентное накопление временных отрезков сигнала с разных частотных позиций. В этом случае из-за резкого расширения общей полосы частот при передаче одного информационного символа когерентное накопление временных отрезков сигнала может оказаться невозможным.

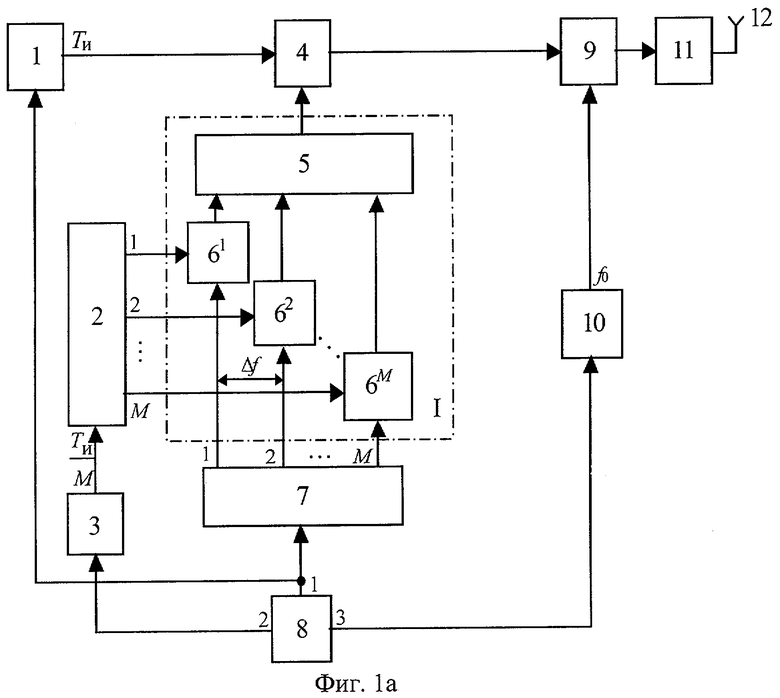

Наиболее близкой к предлагаемой системе можно считать "Адаптивную систему связи с повышенной помехозащищенностью" по патенту РФ №2226037, 7 Н 04 В 15/00, 25.07.2002, функциональная схема передатчика которой для случая когерентных частотно-манипулированных сигналов с учетом схемы, представленной в книге (Помехозащищенность радиосистем со сложными сигналами. /Под ред. Г.И.Тузова. - М.: Радио и связь, 1985, рис.2.6, стр.35), приведена на фиг.1а, а функциональная схема приемника - на фиг.1б, где обозначено:

Фиг.1а:

I - блок коммутации;

1 - источник информации;

2 - формирователь импульсов управления;

3 - генератор кода;

4 - блок модуляции;

5 - сумматор;

61, 62,...6м - ключи;

7 - генератор сетки частот (ГСЧ);

8 - блок опорных частот (БОЧ);

9 - преобразователь частоты;

10 - синтезатор несущей частоты;

11 - усилитель мощности;

12 - передающая антенна.

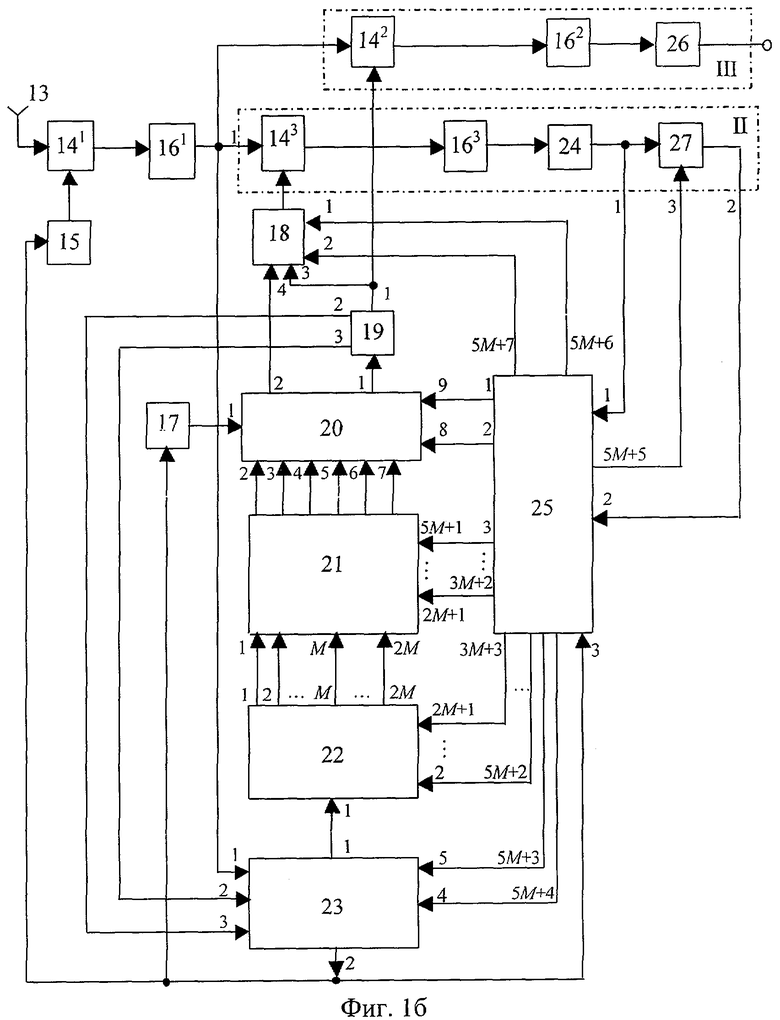

Фиг.1б:

II - блок поиска узкополосных помех;

III - информационный канал;

13 - приемная антенна;

141, 142, 143 - смесители;

15 - синтезатор частот;

161, 162, 163 - усилители промежуточной частоты (УПЧ);

17 - опорный генератор;

18 - коммутатор;

19 - блок задержек;

20 - блок формирования опорных сигналов (БФОС);

21 - блок режекции и коммутации (БРиК);

22 - генератор сетки частот (ГСЧ);

23 - блок синхронизации;

24 - амплитудный детектор;

25 - блок управления;

26 - квадратурный демодулятор;

27 - пороговое устройство.

Помехозащищенная система связи-прототип состоит из передатчика и приемника. Передатчик-прототип (фиг.1а) содержит последовательно соединенные источник информации 1, блок модуляции 4, преобразователь частоты 9 и усилитель мощности 11, выход которого соединен с передающей антенной 12. Первый выход блока опорных частот (БОЧ) 8 соединен с входом источника информации 1 и с входом генератора сетки частот (ГСЧ) 7, М выходов которого соединены с соответствующими М сигнальными входами блока коммутации I, являющимися сигнальными входами соответствующих ключей 61, 62,...6м, выходы которых соединены с соответствующими входами сумматора 5, выход которого является выходом блока коммутации I и соединен со вторым входом блока модуляции 4. Второй выход БОЧ 8 через генератор кода 3 соединен с входом формирователя импульсов управления 2, М выходов которого соединены с соответствующими М управляющими входами блока коммутации I, являющимися управляющими входами соответствующих ключей 61, 62,...6м. Третий выход БОЧ 8 через синтезатор несущей частоты 10 соединен со вторым входом преобразователя частоты 9.

Приемник-прототип (фиг.1б) содержит приемную антенну 13, соединенную с первым входом первого смесителя 141, выход которого через последовательно соединенные первый усилитель промежуточной частоты (УПЧ) 161, третий смеситель 143, третий УПЧ 163, амплитудный детектор 24 и пороговое устройство 27 соединен со вторым входом блока управления 25, первый вход которого соединен с выходом амплитудного детектора 24, при этом блоки 143, 163, 24 и 27 образуют блок поиска узкополосных помех II. Выход первого УПЧ 161 соединен также с входом информационного канала III, состоящего из последовательно соединенных второго смесителя 142, второго УПЧ 162 и квадратурного демодулятора 26, выход которого является выходом приемника, и с первым входом блока синхронизации 23, второй выход которого соединен с третьим входом блока управления 25, через синтезатор частот 15 - со вторым входом первого смесителя 141, а через опорный генератор 17 - с первым входом блока формирования опорных сигналов (БФОС) 20, первый выход которого соединен с входом блока задержек 19. Второй и третий входы блока синхронизации 23 соединены соответственно с третьим и вторым выходами блока задержек 19, первый выход которого соединен со вторым входом второго смесителя 142 и с третьим входом коммутатора 18, выход которого соединен со вторым входом третьего смесителя 143. Первый и второй входы коммутатора 18 соединены соответственно с (5М+6) и (5М+7) выходами блока управления 25, (5М+5) выход которого соединен со вторым входом порогового устройства 27. Первый и второй выходы блока управления 25 соединены соответственно с девятым и восьмым входами БФОС 20, 3...(3М+2) выходы блока управления 25 соединены соответственно с (5М+1)...(2М+1) входами блока режекции и коммутации БРиК 21. (3М+3)...(5М+2) выходы блока управления 25 соединены соответственно с (2М+1)...2 входами ГСЧ 22, выходы (5М+3) и (5М+4) блока управления 25 соединены соответственно с пятым и четвертым входами блока синхронизации 23, первый выход которого соединен с соответствующим входом ГСЧ 22, 2М выходов которого соединены с соответствующими 2М входами БРиК 21, шесть выходов которого соединены соответственно со второго по седьмой входами БФОС 20, второй выход которого соединен с четвертым входом коммутатора 18.

Работа передатчика-прототипа (фиг.1а) происходит следующим образом.

Один информационный символ с выхода источника информации 1 разбивается на М временных отрезков длительностью  , каждый из которых передается на одной из М частот. Первоначальное формирование частотно-временных элементов КЧМнС осуществляется блоком коммутации I по сигналам управления с блока 2 из сетки частот, вырабатываемых ГСЧ 7. При этом на сумматор 5 блока коммутации I поступает отрезок синусоидального колебания с выхода одного из ключей 61,...6м. Генератор кода 3 задает значение частоты на каждом временном отрезке

, каждый из которых передается на одной из М частот. Первоначальное формирование частотно-временных элементов КЧМнС осуществляется блоком коммутации I по сигналам управления с блока 2 из сетки частот, вырабатываемых ГСЧ 7. При этом на сумматор 5 блока коммутации I поступает отрезок синусоидального колебания с выхода одного из ключей 61,...6м. Генератор кода 3 задает значение частоты на каждом временном отрезке  . Все М временных отрезков М сигнала переносят одну и ту же информацию, которая накладывается в блоке модуляции 4. В преобразователе 9 происходит перенос сформированного сигнала в область рабочих частот, задаваемую синтезатором несущей частоты 10. Преобразователь частот 9 может быть как однополосным, так и двухполосным. Его выходной сигнал усиливается в блоке 11 и излучается передающей антенной 12 в эфир.

. Все М временных отрезков М сигнала переносят одну и ту же информацию, которая накладывается в блоке модуляции 4. В преобразователе 9 происходит перенос сформированного сигнала в область рабочих частот, задаваемую синтезатором несущей частоты 10. Преобразователь частот 9 может быть как однополосным, так и двухполосным. Его выходной сигнал усиливается в блоке 11 и излучается передающей антенной 12 в эфир.

Как показано в книге (Помехозащищенность радиосистем со сложными сигналами. /Под ред. Г.И.Тузова. - М.: Радио и связь, 1985, стр. 35), чтобы получить фазу выходного сигнала без скачков в моменты переключении, необходимо формировать сетку частот от той же опорной частоты, которая синхронизирует генератор кода 3. Обозначим эту частоту как fоп. Тогда должны выполняться следующие соотношения:

fоп=mfоп,

Δf=lfоп,

где k, l, m, n - целые числа;

f0 - значение несущей частоты;

Δf - расстояние между соседними частотами;

Ти - длительность информационного символа.

Эти соотношения задаются блоком опорных частот 8, который выполняет функции синхронизатора.

Работа приемника-прототипа (фиг.1б) заключается в следующем.

КЧМнС принимается приемной антенной 13 и с помощью блоков 141, 15, 161 переносится на первую промежуточную частоту, на которой осуществляется его обработка. Свертка по спектру происходит в смесителе 142, на второй вход которого подается опорный КЧМнС, синхронизированный с входным КЧМнС, в результате чего устраняются скачки частоты и на вход УПЧ 162 с полосой ˜ поступает радиоимпульс длительностью Ти. После фильтрации и усиления в УПЧ 16 он подается в квадратурный демодулятор 26 (выполненный, например, в виде относительного фазового), на выходе которого выделяется информационный сигнал. Опорный сигнал формируется из опорной частоты генератора 17 и последовательности радиоимпульсов длительностью

поступает радиоимпульс длительностью Ти. После фильтрации и усиления в УПЧ 16 он подается в квадратурный демодулятор 26 (выполненный, например, в виде относительного фазового), на выходе которого выделяется информационный сигнал. Опорный сигнал формируется из опорной частоты генератора 17 и последовательности радиоимпульсов длительностью  , формируемых в БФОС 20 из сетки частот, состоящей из М частот, генерируемых ГСЧ 22.

, формируемых в БФОС 20 из сетки частот, состоящей из М частот, генерируемых ГСЧ 22.

Для исключения частотных составляющих КЧМнС, пораженных узкополосными помехами, используется режекция соответствующих частот в опорных КЧМнС, которая осуществляется в БРиК 21. Сложность такого подавления узкополосных помех в случае двухполосного сигнала заключается в независимом исключении частотных составляющих опорного сигнала в нижней и верхней боковых полосах его спектра. Функцию разделения полос выполняет блок формирования опорных сигналов 20. Так как разделение полос осуществляется фазовым способом, используются пары квадратурных составляющих с выхода ГСЧ 22.

Поиск частотных составляющих КЧМнС, пораженных узкополосными помехами, осуществляется блоком поиска узкополосных помех II, состоящим из блоков 143, 163, 24 и 27. Для этого на смеситель 143 через коммутатор 18 последовательно подаются все частотные составляющие опорного КЧМнС со второго выхода БФОС 20. В результате через УПЧ 163 последовательно проходят все частотные составляющие входного сигнала, на основе оценок амплитуд которых с выхода (5М+5) блока управления 25 формируется пороговый уровень, который подается на пороговое устройство 27. Если уровень какой-либо частотной составляющей превышает пороговый, устройство 27 вырабатывает сигнал, по которому блок управления 25 запрещает прохождение соответствующей частотной составляющей опорного сигнала по первому выходу БФОС 20, чем достигается режекция узкополосных помех.

В режиме приема информации поиск частотных составляющих сигнала, пораженных узкополосными помехами, производится периодически. Режиму приема информации предшествует режим синхронизации по задержке, который включает режим поиска и режим слежения. В начале работы после поиска узкополосных помех та же схема производит поиск сигнала по задержке. Для этого опорный сигнал с первого выхода БФОС 20 через блок задержек 19 и коммутатор 18 подается на смеситель 143. Блок управления 25 через блок синхронизации 23 изменяет временное положение импульсов опорного сигнала и по сигналу с выхода амплитудного детектора 24 фиксирует положение максимума, после чего поиск по задержке прекращается, и коммутатор 18 опять пропускает на выход сигнал со второго выхода БФОС 20. Слежение за задержкой осуществляет блок синхронизации 23, причем схема слежения аналогична типовой схеме слежения за задержкой сложных фазоманипулированных сигналов с опережающим и отстающим опорными сигналами.

Опорные сигналы с необходимыми задержками формируются блоком 19 (для информационного канала III - по первому выходу, а для блока синхронизации 23 - по второму и третьему выходам). При временном рассогласовании временной дискриминатор, входящий в состав блока 23, добавляет или исключает импульс в импульсной последовательности, на основе которой работает ГСЧ 22.

Таким образом, приемник-прототип осуществляет когерентное накопление частотно-временных элементов КЧМнС с режекцией элементов, пораженных узкополосными помехами.

Однако система-прототип имеет недостаток, который заключается в значительном расширении (пропорционально М) спектра сигнала на каждой частотной позиции и увеличении общей полосы. В результате повышается вероятность поражения узкополосными помехами значительного числа частотных позиций сигнала и затрудняется когерентное накопление в широкой полосе частот.

Устранение этих недостатков достигается введением дополнительной быстрой перестройки рабочей частоты.

При этом каждый информационный символ исходной длительности последовательно передается на каждой частоте из сетки частот быстрой перестройки. Сохранение исходной ширины спектра сигнала на каждой частотной позиции достигается объединением информационных символов в блоки с одновременным увеличением их длительности. Сохранение скорости передачи достигается параллельной передачей информационных символов блока на всех частотах сетки частот быстрой перестройки. В результате исключения частотных позиций, пораженных узкополоснымн помехами, теряется лишь часть информационного символа, а не весь символ, как в системе-прототипе. Потери компенсируются за счет когерентного накопления частей информационного символа с разных частотных позиций.

Для этого в помехозащищенную систему связи, состоящую из передатчика и приемника, причем передатчик содержит источник информации, блок модуляции, преобразователь частоты, выход которого через усилитель мощности соединен с передающей антенной, а второй вход соединен с выходом синтезатора несущей частоты, блок коммутации, генератор сетки частот (ГСЧ), блок опорных частот, первый выход которого соединен с первым входом ГСЧ и с входом источника информации, а второй выход соединен с входом генератора кода, приемник содержит приемную антенну, соединенную с сигнальным входом первого смесителя, опорный вход которого соединен с выходом синтезатора частот, а выход соединен с входом первого усилителя промежуточной частоты (УПЧ), выход которого соединен с сигнальными входами блока поиска узкополосных помех, первого информационного канала, состоящего из последовательно соединенных соответствующих смесителя, УПЧ и квадратурного демодулятора, и первого блока синхронизации, первый выход которого соединен с входом ГСЧ, М пар квадратурных выходов которого соединены с соответствующими 2М сигнальными входами блока режекции и коммутации, опорный генератор, выход которого соединен с опорным входом блока формирования опорных сигналов (БФОС), блок управления, первый и второй входы которого соединены с соответствующими выходами блока поиска узкополосных помех, третий вход которого соединен со вторым выходом блока управления, третий вход которого соединен со вторым выходом первого блока синхронизации, СОГЛАСНО ИЗОБРЕТЕНИЮ в передатчик введен преобразователь информационных символов, первый вход которого соединен с выходом источника информации, второй вход является входом добавочного символа, служащего пилот-сигналом, а М выходов соединены с соответствующими М информационными входами блока модуляции, М опорных входов которого соединены с М соответствующими выходами ГСЧ, второй вход которого соединен с четвертым выходом блока опорных частот, третий выход которого соединен с третьим входом преобразователя информационных символов и со вторым входом формирователя импульсов управления, первый вход которого соединен с четвертым входом преобразователя информационных символов и с первым выходом блока опорных частот, М2 выходов блока модуляции соединены с соответствующими М2 сигнальными входами блока коммутации, М2 управляющих входов которого соединены с соответствующими М2 выходами формирователя импульсов управления, причем выход блока коммутации соединен с первым входом преобразователя частоты, а выход генератора кода соединен с входом синтезатора несущей частоты, в приемник введены (М-2) информационных канала, идентичных первому, два квадратурных пилот-канала, каждый из которых состоит из соответствующих последовательно соединенных смесителя и УПЧ, преобразователь информационных символов, фазовращатель на 90° и второй блок синхронизации, первый выход которого соединен с входом синтезатора частот, а второй выход соединен с четвертым входом блока управления, пятый вход которого соединен с первым выходом первого блока синхронизации, вторым входом блока поиска узкополосных помех и (2М-1)-м входом преобразователя информационных символов, выход которого является выходом приемника, а (2М-2) остальных входов соединены соответственно с (М-1) парами выходов соответствующих квадратурных демодуляторов (М-1) информационных каналов, вторые входы всех квадратурных демодуляторов объединены и соединены с выходом УПЧ синфазного пилот-канала, третьи входы всех квадратурных демодуляторов объединены и соединены с выходом УПЧ квадратурного пилот-канала, четвертые входы всех квадратурных демодуляторов объединены и соединены с третьим выходом первого блока синхронизации, сигнальные входы смесителей обоих пилот-каналов и смесителей всех введенных (М-2) информационных каналов объединены и соединены с выходом первого УПЧ, опорный вход смесителя квадратурного пилот-канала через фазовращатель на 90° соединен с опорным входом смесителя синфазного пилот-канала, с первым выходом БФОС и со вторым входом первого блока синхронизации, М следующих входов [с третьего по (М+2)-й] которого соединены с соответствующими М выходами [с (4М+3)-го по (5М+3)-й] блока режекции и коммутации, остальные (4М+2) выходов [с первого по (4М+2)-й] которого соединены с соответствующими входами БФОС, (4М+3)-й вход которого соединен с первым выходом блока управления, (М-1) выходов БФОС (со второго по М-й) соединены с опорными входами соответствующих смесителей информационных каналов, а (М+1)-й выход соединен с четвертым входом блока поиска узкополосных помех, сигнальный вход второго блока синхронизации соединен с выходом первого УПЧ, М следующих входов [со второго по (М+1)-й] соединены с соответствующими синфазными выходами ГСЧ, а (М+2)-й вход соединен с третьим выходом блока управления, четвертый и пятый выходы которого соединены соответственно с (М+4)-м и (М+3)-м входами первого блока синхронизации, а следующие (М2+4М) выходов соединены шиной с соответствующими управляющими входами блока режекции и коммутации.

Графические материалы, представленные в заявке:

Фиг.1 - Система связи-прототип:

Фиг.1а - передатчик;

Фиг.1б - приемник.

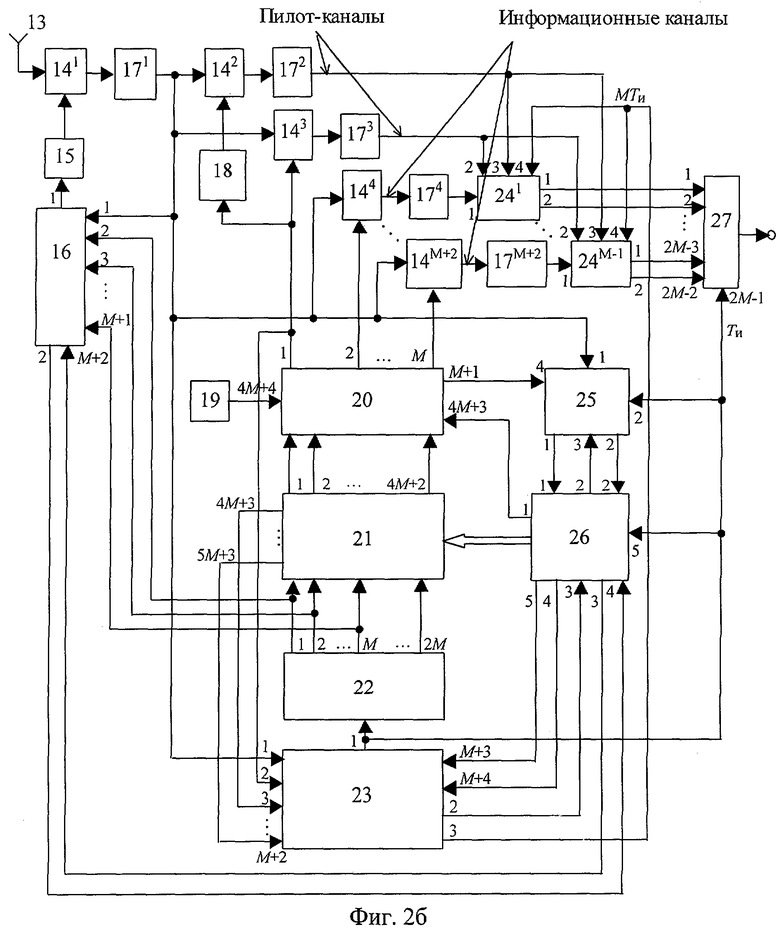

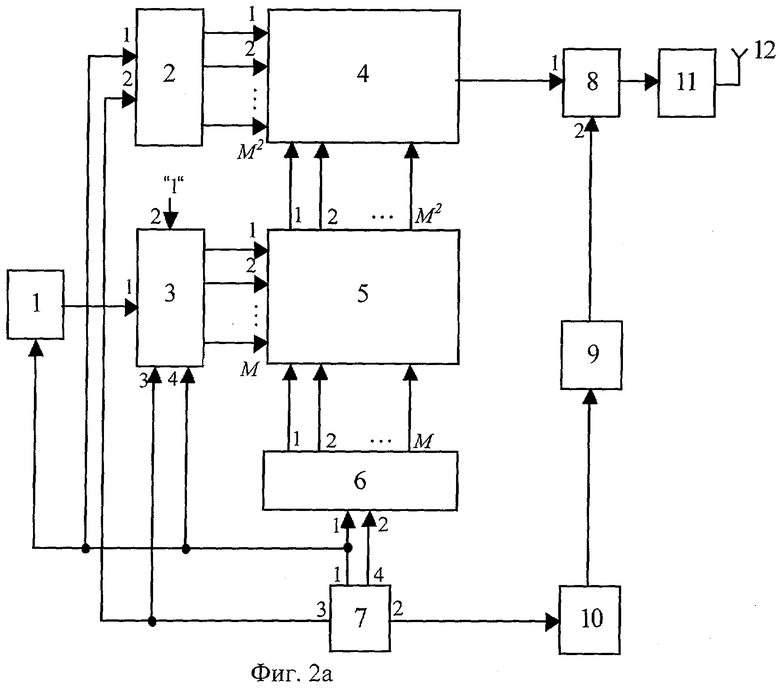

Фиг.2 - Предлагаемая помехозащищенная система связи:

Фиг.2а - передатчик;

Фиг.2б - приемник.

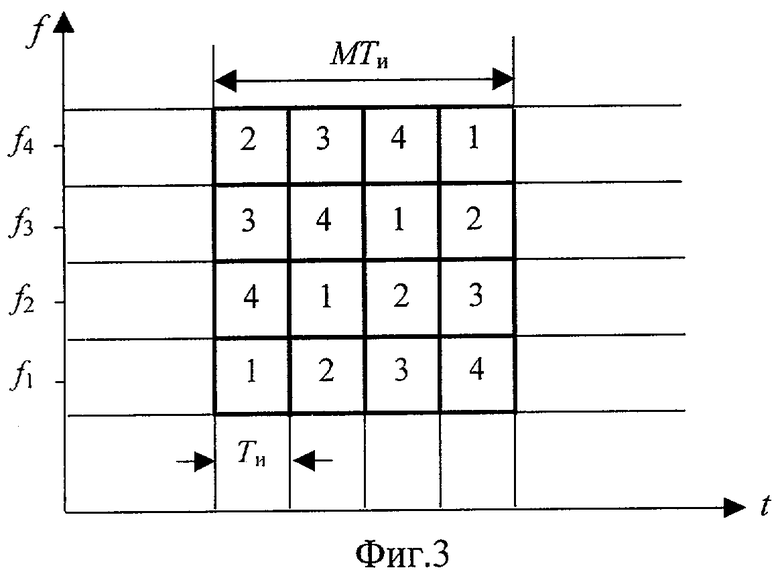

Фиг.3 - Схема преобразования информационных символов.

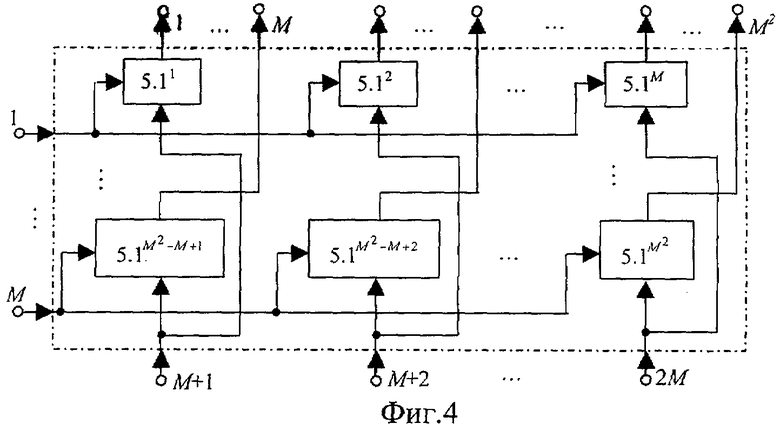

Фиг.4 - Функциональная схема блока модуляции.

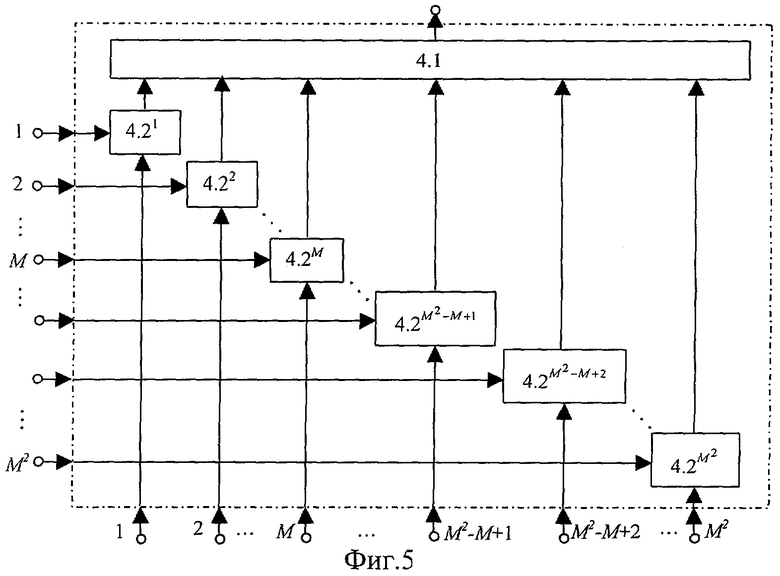

Фиг.5 - Функциональная схема блока коммутации.

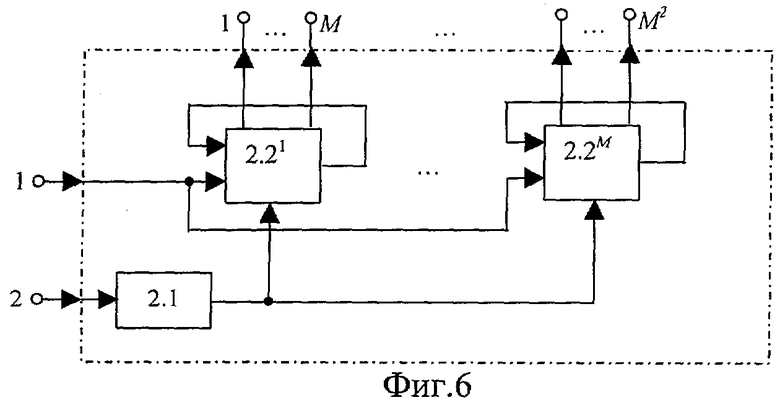

Фиг.6 - Функциональная схема формирователя импульсов управления.

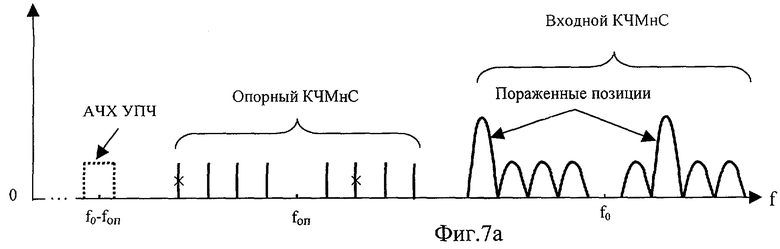

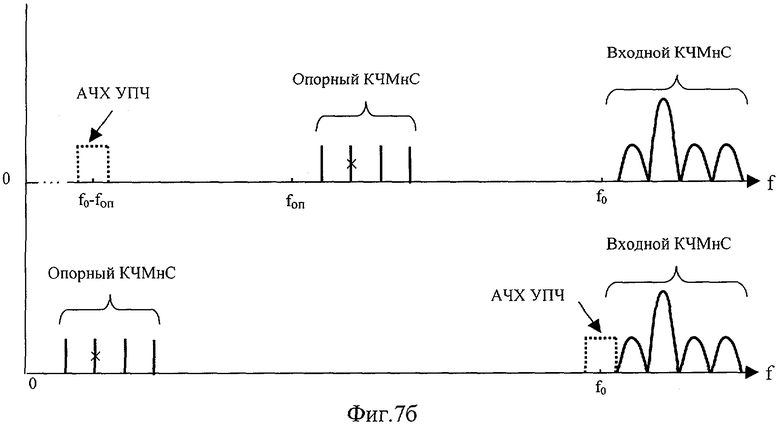

Фиг.7 - Способы режекции узкополосных помех при приеме однополосных и двухполосных КЧМнС.

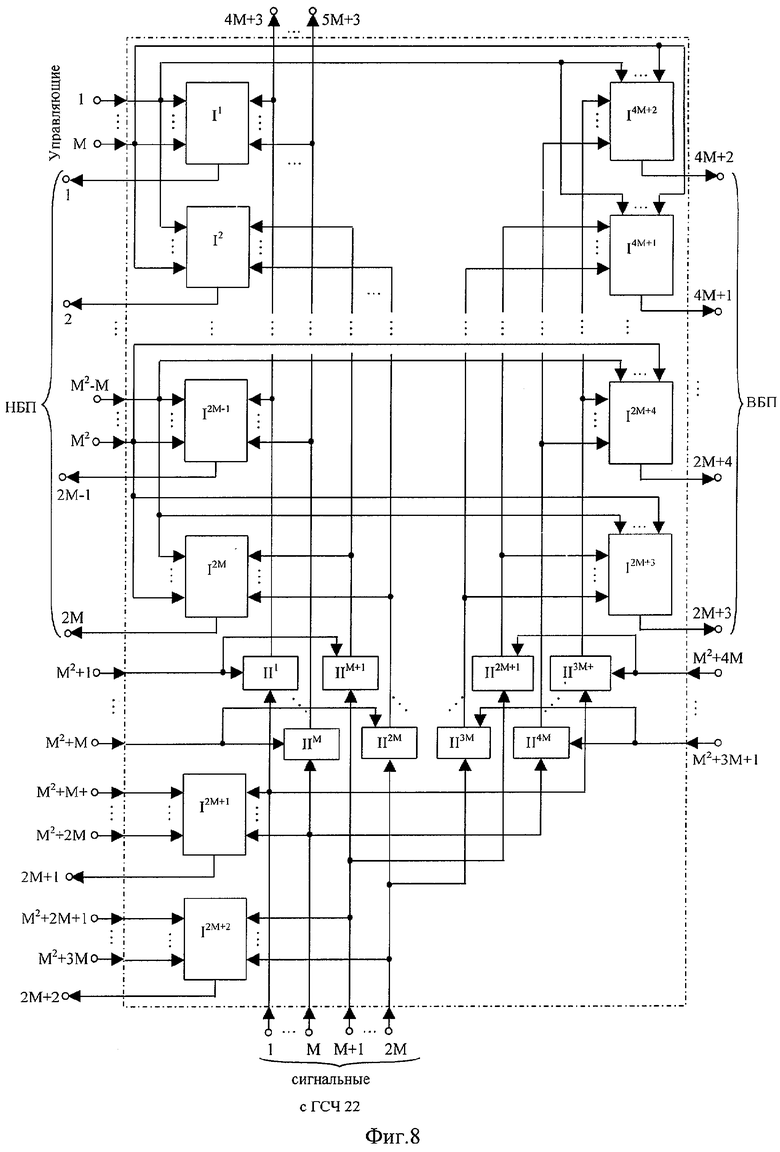

Фиг.8 - Функциональная схема блока режекции и коммутации.

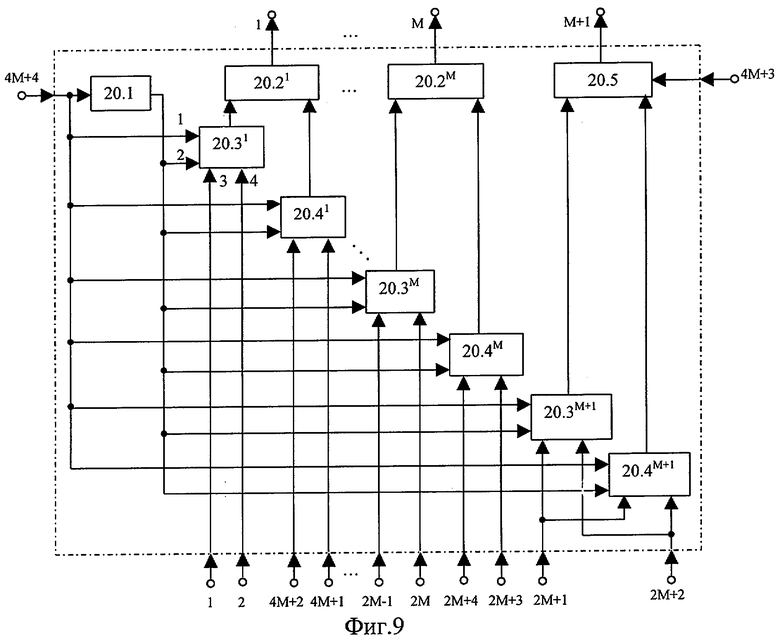

Фиг.9 - Функциональная схема блока формирования опорных сигналов.

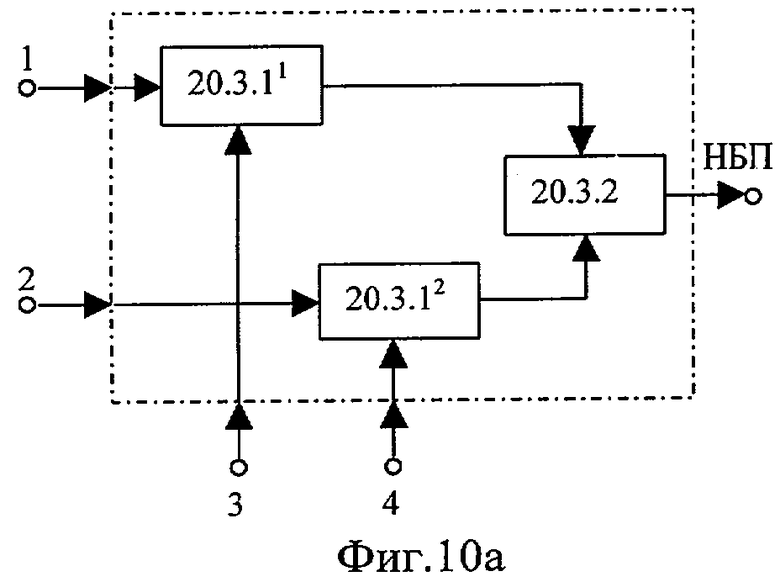

Фиг.10 - Функциональные схемы преобразователей нижней и верхней боковых полос.

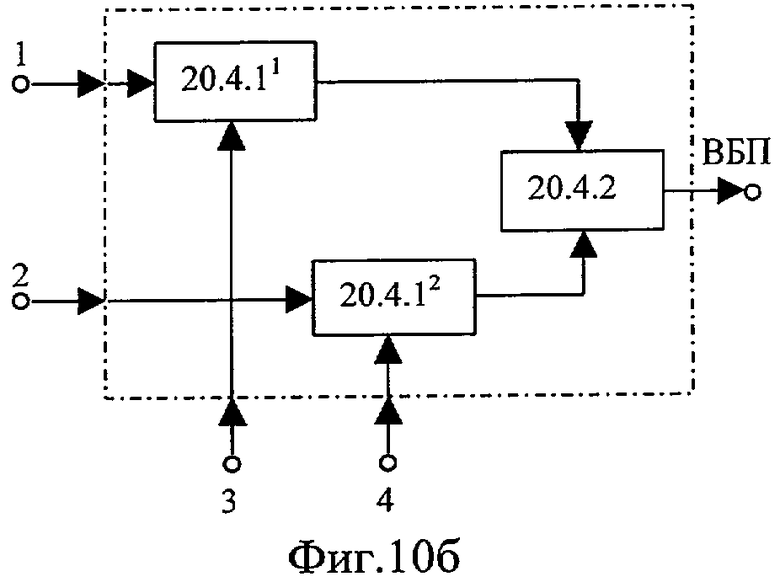

Фиг.11 - Функциональная схема блока поиска узкополосных помех.

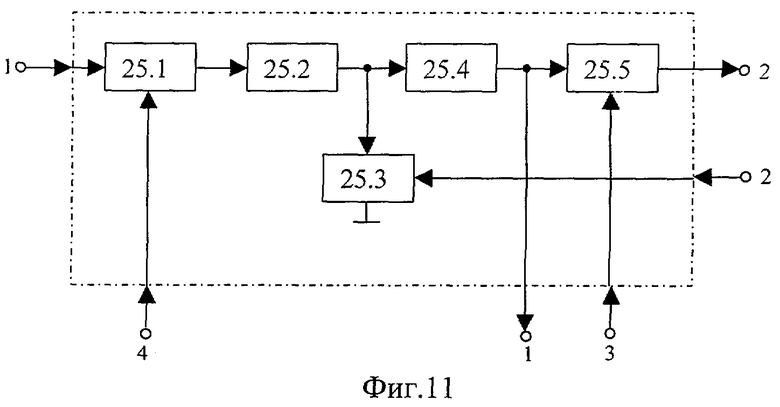

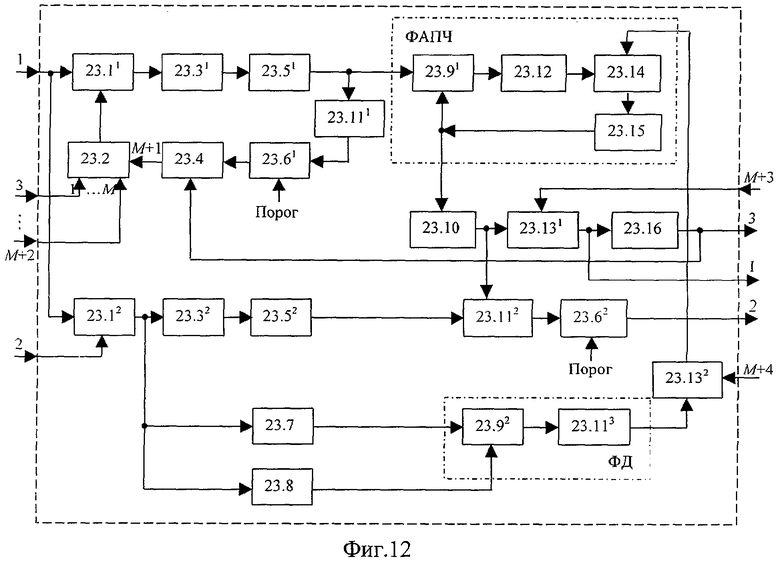

Фиг.12 - Функциональная схема первого блока синхронизации.

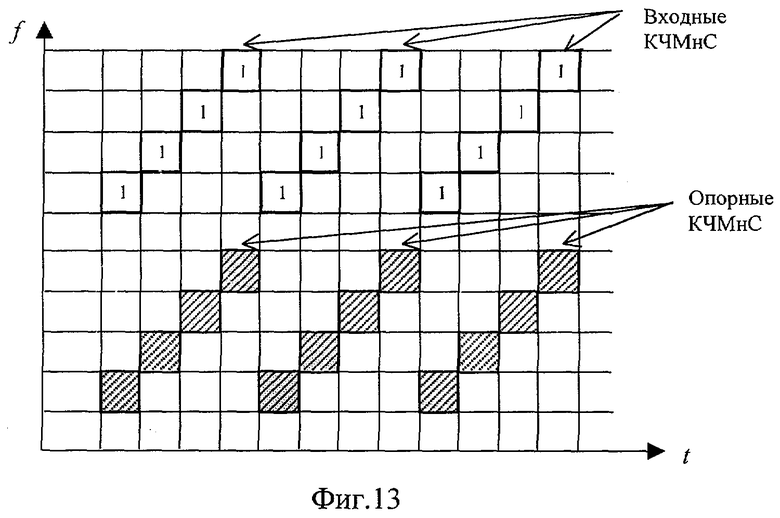

Фиг.13 - Частотно-временные позиции входных и опорных сигналов.

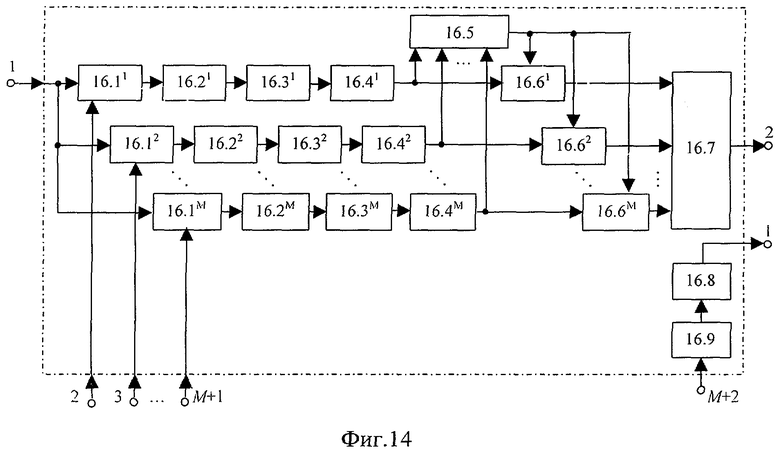

Фиг.14 - Функциональная схема второго блока синхронизации.

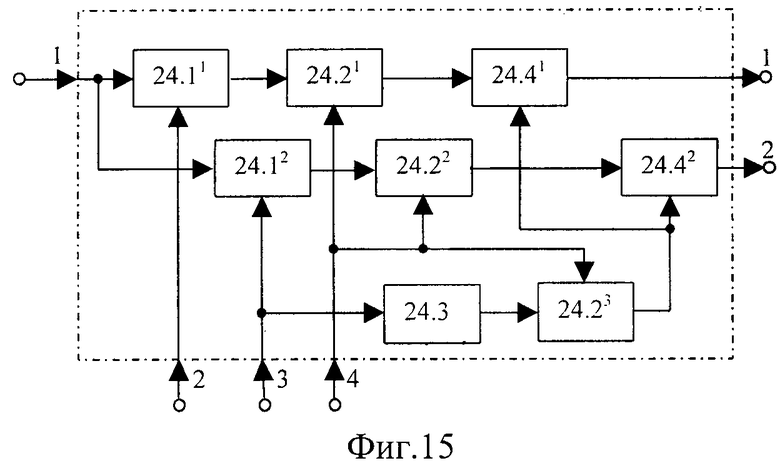

Фиг.15 - Функциональная схема квадратурного демодулятора.

Функциональная схема предлагаемой помехозащищенной системы связи представлена на фиг.2, где обозначено:

Фиг.2а - передатчик:

1 - источник информации;

2 - формирователь импульсов управления;

3 - преобразователь информационных символов;

4 - блок коммутации;

5 - блок модуляции;

6 - генератор сетки частот (ГСЧ);

7 - блок опорных частот (БОЧ);

8 - преобразователь частоты;

9 - синтезатор несущей частоты;

10 - генератор кода;

11 - усилитель мощности;

12 - передающая антенна.

Фиг.2б - приемник:

13 - приемная антенна;

141,...14М+2 - смесители;

15 - синтезатор частот;

16 - второй блок синхронизации;

171,...17М+2 - усилители промежуточной частоты (УПЧ);

18 - фазовращатель на 90°;

19 - опорный генератор;

20 - блок формирования опорных сигналов (БФОС);

21 - блок режекции и коммутации (БРиК);

22 - генератор сетки частот (ГСЧ);

23 - первый блок синхронизации;

241,...24М+1 - квадратурные демодуляторы;

25 - блок поиска узкополосных помех;

26 - блок управления;

27 - преобразователь информационных символов.

Предлагаемая помехозащищенная система связи состоит из передатчика и приемника. Передатчик (фиг.2а) содержит источник информации 1, выход которого соединен с первым (информационным) входом преобразователя информационных символов 3, второй вход которого является входом добавочного символа, служащего пилот-сигналом. М выходов блока 3 соединены с соответствующими М информационными входами блока модуляции 5, М опорных входов которого соединены с соответствующими М выходами ГСЧ 6, первый и второй входы которого соединены соответственно с первым и четвертым выходами блока опорных частот (БОЧ) 7. Первый выход БОЧ 7 соединен также с входом источника информации 1, с четвертым входом преобразователя информационных символов 3 и с первым входом формирователя импульсов управления 2, М2 выходов которого соединены с соответствующими М2 управляющими входами блока коммутации 4, М2 сигнальных входов которого соединены с соответствующими М2 выходами блока модуляции 5, причем выход блока коммутации 4 через последовательно соединенные преобразователь частоты 8 и усилитель мощности 11 соединен с передающей антенной 12. Второй выход БОЧ 7 через последовательно соединенные генератор кода 10 и синтезатор несущей частоты 9 соединен со вторым входом преобразователя частоты 8. Третий выход БОЧ 7 соединен с третьим входом преобразователя информационных символов 3 и со вторым входом формирователя импульсов управления 2.

Приемник (фиг.26) содержит приемную антенну 13, соединенную через первый смеситель 141 с первым усилителем промежуточной частоты (УПЧ) 171, выход которого соединен с сигнальным входом квадратурного пилот-канала, состоящего из последовательно соединенных второго смесителя 142 и второго УПЧ 172, и с сигнальным входом синфазного пилот-канала, состоящего из последовательно соединенных третьего смесителя 143 и третьего УПЧ 173. Выход первого УПЧ 171 соединен также с сигнальными входами (М-1) информационных каналов, каждый из которых состоит из последовательно соединенных соответствующих смесителя 144...14М+2, УПЧ 174...17М+2 и квадратурного демодулятора 241...24М+1, сигнальными (первыми) входами первого (23), второго (16) блоков синхронизации, и блока поиска узкополосных помех 25, второй вход которого соединен с (2М-1)-м входом преобразователя информационных символов 27, пятым входом блока управления 26, с синхронизирующим входом ГСЧ 22 и с первым выходом первого блока синхронизации 23. Выход УПЧ 17 квадратурного пилот-канала соединен с третьими входами демодуляторов 241...24М-1, а выход УПЧ 173 синфазного пилот-канала соединен со вторыми входами квадратурных демодуляторов 241...24M-1, (М-1) пар выходов которых соединены с соответствующими (2М-2) входами преобразователя информационных символов 27, выход которого является выходом приемника. Выход опорного генератора 19 соединен с опорным входом БФОС 20, первый выход которого соединен со вторыми (опорными) входами первого блока синхронизации 23, смесителя синфазного канала 143 и через фазовращатель на 90° с опорным входом смесителя квадратурного канала 142. (М-1) выходов БФОС 20 (со второго по М-й) соединены соответственно с опорными входами смесителей (М-1) информационных каналов 144...14М+2, а (МН)-й выход БФОС 20 соединен с четвертым входом блока поиска узкополосных помех 25, первый и второй выходы которого соединены с соответствующими входами блока управления 26. 2М выходов ГСЧ 22, из которых первые М выходов являются синфазными, а вторые М - квадратурными, соединены с соответствующими сигнальными входами БРиК 21, причем М синфазных выходов соединены с соответствующими М входами (со второго по (МН)-й) второго блока синхронизации 16, управляющий выход которого через синтезатор частот 15 соединен с опорным входом первого смесителя 141. Второй выход второго блока синхронизации 16 соединен с четвертым входом блока управления 26, третий выход которого соединен с (М+2)-м входом блока синхронизации 16. (4М+2) выхода БРиК 21 соединены с соответствующими входами БФОС 20, а остальные М выходов [с (4М+3)-го по (5М+3)-й] - соответственно с [третьим...(М+2)-м] входами первого блока синхронизации 23, второй выход которого соединен с третьим входом блока управления 26, а третий выход - с четвертыми входами квадратурных демодуляторов 241...24M-1. Первый выход блока управления 26 соединен с (4М+3)-м входом БФОС 20, второй выход - с третьим входом блока поиска узкополосных помех 25, четвертый и пятый выходы - с (М+4)-м и (М+3)-м входами первого блока синхронизации 23 соответственно, следующие (M2+4M) выходов соединены условной шиной с соответствующими управляющими входами БРиК 21.

Работа предлагаемой помехозащищенной системы связи происходит следующим образом.

В передатчике (фиг.2а) в общем случае двоичные информационные символы с выхода источника информации 1 объединяются в группы, образуя недвоичные информационные символы длительностью Ти. (М-1) этих информационных символов в преобразователе 3 формируются в блок параллельных во времени символов длительностью МТи. К этому блоку по второму входу преобразователя 3 добавляется еще один символ, всегда равный, например, "1", который служит пилот-сигналом. Каждый из М полученных расширенных символов делится на М временных отрезков, каждый из которых передается на своей частоте, например, так, как показано на фиг.3 для М=4, где цифрами 1, 2, 3, 4 обозначены номера расширенных информационных символов.

Ширина спектра сигнала на каждой частотной позиции (по первым нулям) равна  , т.е. расширения спектра не происходит.

, т.е. расширения спектра не происходит.

Каждый из М информационных символов в блоке модуляции 5 модулирует все М синусоидальных колебаний с выходов ГСЧ 6. Из этих М2 модулированных колебаний блок коммутации 4 в каждый из М временных интервалов длительностью Ти выбирает М заданных колебаний. Например, на фиг.3 в первый временной интервал первый символ излучается на частоте f1, четвертый символ - на частоте f2, третий - на частоте f3, второй - на частоте f4.

Формирователь импульсов 2 вырабатывает импульсы управления блоком коммутации 4. Групповой сигнал с выхода блока 4 переносится в область рабочих частот в преобразователе частоты 8, усиливается в блоке 11 и излучается передающей антенной 12 в эфир. Преобразователь частоты 8 может быть как двухполосным, так и однополосным. Несущая частота вырабатывается синтезатором несущей частоты 9, который управляется генератором кода 10. Генератор кода 10 вырабатывает числовую последовательность, которая определяет значения частот при ППРЧ. Таким образом, в эфир излучается сигнал, который можно назвать КЧМнС с медленной ППРЧ.

Блок опорных частот 7 задает основную тактовую частоту fи= (по выходу 1), тактовую частоту расширенных информационных символов

(по выходу 1), тактовую частоту расширенных информационных символов  (по выходу 3), а также частоту перестройки синтезатора

(по выходу 3), а также частоту перестройки синтезатора  где N - целое число (по выходу 2). ГСЧ 6 должен вырабатывать колебания с частотами, кратными некоторой опорной частоте fоп (выход 4 блока 7). В результате все формируемые радиоимпульсы на выходе блока коммутации 4 имеют несущие колебания, синхронные с колебанием тактовой частоты fи=

где N - целое число (по выходу 2). ГСЧ 6 должен вырабатывать колебания с частотами, кратными некоторой опорной частоте fоп (выход 4 блока 7). В результате все формируемые радиоимпульсы на выходе блока коммутации 4 имеют несущие колебания, синхронные с колебанием тактовой частоты fи= .

.

Преобразователь информационных символов 3 представляет собой блок памяти, в которую последовательно записываются двоичные или недвоичные информационные символы с выхода источника информации 1, а затем параллельно считываются на выходы 1, 2,...М.

Функциональная схема блока модуляции 5 представлена на фиг.4, где блоки 5.11,...5.1М2 - модуляторы.

Первый вход блока модуляции 5 соединен с информационными входами модуляторов 5.11,...5.1М, опорные входы которых соединены с соответствующими М входами блока 5 [с (М+1)-го по 2М-й и со опорными входами соответствующих модуляторов 5.1м2-м+1...5.1М2, информационные входы которых соединены с М-м входом блока модуляции 5. Выходы 5.11...5.1М2 модуляторов являются соответствующими 1...М2 выходами блока модуляции 5.

Как было сказано выше, каждый из М информационных символов, хранящихся в преобразователе информационных символов 3 (фиг.2а), модулирует все М синусоидальных колебаний с выходов ГСЧ 6.

На фиг.4 эти синусоидальные колебания поступают на входы (М+1), (М+2),...2М, а с каждого входа - на опорные входы М соответствующих модуляторов 5.1 (расположенных на фиг.4 по вертикали).

Информационные символы поступают на входы 1, 2,...М, а с каждого входа - на информационные входы М соответствующих модуляторов 1 (расположенных на фиг.4 по горизонтали).

В модуляторах 5.1 осуществляется изменение одного или нескольких параметров синусоидальных колебаний под воздействием информационных сигналов.

Модуляторы в общем случае могут быть амплитудно-фазовыми, в простейшем случае представлять собой перемножители (инверторы знака).

Функциональная схема блока коммутации 4 показана на фиг.5, где обозначено:

4.1 - сумматор;

4.21, 4.22,...4.2м2 - ключи.

Блок коммутации 4 (фиг.2а) содержит ключи 4.21, 4.22,...4.2М2, первые входы которых являются соответствующими управляющими М2 входами блока коммутации 4, а вторые входы являются соответствующими сигнальными М2 входами блока 4, при этом выходы ключей 4.21, 4.22,...4.2м2 соединены с соответствующими входами сумматора 4.1, выход которого является выходом блока коммутации 4.

Под действием управляющих сигналов с выходов формирователя импульсов управления 2 (фиг.2а) отпирается М заданных ключей 4.2, сигналы с выходов которых суммируются в блоке 4.1.

Функциональная схема формирователя импульсов управления 2 изображена на фиг.6, где обозначено:

2.1 - формирователь импульса записи;

2.21,...2.2М - М-разрядные регистры сдвига с обратной связью.

Первый вход формирователя импульсов управления 2 (фиг.2а) соединен с первыми входами М-разрядных регистров сдвига 2.21,...2.2М, вторые входы которых через формирователь импульса записи 2.1 соединены со вторым входом блока 2. Каждый регистр сдвига М-разрядный, следовательно, блок 2 имеет М2 выходов.

Работу блока 2 можно пояснить с помощью фиг.3, из которой следует, что i-й информационный символ излучается последовательно на всех М частотах, причем начальная частота для каждого символа своя. Согласно этому импульсы управления для каждого информационного символа вырабатываются М-разрядным регистром сдвига с обратной связью 2.2. Начальное состояние регистра, которое определяет начальную частоту, задается номером триггера, который переводится в единичное состояние импульсом записи, вырабатываемым формирователем 2.1. Затем под действием тактовых импульсов этот единичный импульс последовательно проходит через все триггеры регистра сдвига, являясь импульсом управления для блока коммутации 4.

Генератор сетки частот 6 может быть выполнен на основе делителей частоты, как описано в книге (Аппаратура передачи дискретной информации МС-5. /Под ред. А.М.Заездного и Ю.Б.Окунева. - М.: Связь, 1970, стр.32-36).

Остальные блоки на фиг.2а являются типовыми блоками радиопередатчиков.

Приемник на фиг.2б работает следующим образом.

Сигнал КЧМн с медленной ППРЧ с выхода приемной антенны 13 поступает на вход смесителя 141, в котором происходит снятие медленной ППРЧ. Для этого на второй вход смесителя 141 с выхода синтезатора частот 15 подается опорный сигнал с аналогично перестраиваемой несущей частотой. В результате на выходе УПЧ 171 на промежуточной частоте выделяется сигнал с оставшейся быстрой КЧМн. Синхронизация медленных скачков частоты осуществляется вторым блоком синхронизации 16, который сначала фиксирует попадание КЧМнС в полосу первого УПЧ 171, а затем совмещает моменты скачков частоты во входном и опорном сигналах.

Снятие быстрых скачков частоты (с интервалом Ти) происходит в смесителях 142, 143,...14M+2, на вторые входы которых подаются соответствующие опорные сигналы. Опорные колебания для квадратурных демодуляторов 24 формируются из входного пилот-сигнала, выделяемого в смесителях 142, 143. Поворот фазы колебания на 90° в квадратурном канале (элементы 142, 172) относительно фазы в синфазном канале (элементы 143, 173) осуществляется за счет фазовращателя 18. УПЧ 172 и 173, ввиду периодичности пилот-сигналов, могут иметь полосу пропускания меньше, чем  .

.

Остальные (М-1) каналов, содержащих элементы 144, 174, 241...14М+2, 17М+2, 24М-1, являются информационными. На их выходах выделяется (М-1) переданных расширенных информационных символов, поэтому полосы пропускания УПЧ 174,...17M+2 имеют величину порядка  . В квадратурных демодуляторах 241,...24М-1 выделяются проекции векторов соответствующих информационных сигналов на векторы опорных сигналов, по которым вычисляются переданные информационные символы. В преобразователе 27 (М-1) параллельных информационных символов длительностью МТи преобразуются в исходную последовательность двоичных или недвоичных символов длительностью Tи (аналогичную последовательности на выходе источника информации 1 на фиг.2а).

. В квадратурных демодуляторах 241,...24М-1 выделяются проекции векторов соответствующих информационных сигналов на векторы опорных сигналов, по которым вычисляются переданные информационные символы. В преобразователе 27 (М-1) параллельных информационных символов длительностью МТи преобразуются в исходную последовательность двоичных или недвоичных символов длительностью Tи (аналогичную последовательности на выходе источника информации 1 на фиг.2а).

Борьба с узкополосными помехами в предлагаемом приемнике осуществляется так же, как и в приемнике-прототипе, т.е. методом режекции соответствующих частотных составляющих в опорных сигналах смесителей 142, 143,...14M+2. Возможные способы режекции узкополосных помех при приеме двухполосных КЧМнС приведены на фиг.7а, а однополосных - на фиг.7б.

Структура блока поиска узкополосных помех 25 на фиг.2б аналогична структуре блока II на фиг.1б. Блок 25 выдает в блок управления 26 информацию о пораженных частотных позициях, а блок 26 выдает в БРиК 21 команды на режекцию соответствующих частотных составляющих в опорных сигналах.

Синхронизация опорных КЧМнС, формируемых в блоках 20 и 21, осуществляется первым блоком синхронизации 23, который сначала осуществляет грубый поиск КЧМнС по задержке и грубую синхронизацию тактов, а затем переходит к более точному слежению за задержкой и тактовой частотой. БФОС 20 и БРиК 21, как и в приемнике-прототипе, служат для осуществления раздельной режекции пораженных частотных позиций в верхней и нижней боковых полосах опорных сигналов при приеме двухполосных КЧМнС. Разделение полос осуществляется фазокомпенсационным (квадратурным) способом, для чего требуется, чтобы ГСЧ 22 выдавал пары квадратурных частотных составляющих. На фиг.2б первые М выходов ГСЧ 22 соответствуют синфазным составляющим, а вторые М выходов - квадратурным. Эти составляющие поступают соответственно на 2М сигнальных входов БРиК 21, функциональная схема которого приведена на фиг.8, где обозначено:

I1,...I4М+2 - коммутаторы;

II1,...II4M - ключи.

1...М управляющие входы блока режекции и коммутации 21 соединены с соответствующими М входами каждого из коммутаторов I1, I2, I4M+2, 14M+1, выходы которых являются первым, вторым, (4М+2)-м, (4М+1)-м выходами БРиК 21 соответственно. Входы (М2-М)...М2 БРиК 21 соединены с соответствующими управляющими М входами коммутаторов I2M-1, I2M, I2M+4, I2M+3, выходы которых являются (2М-1)-м, 2М-м, (2М+4)-м, (2М+3)-м выходами БРиК 21 соответственно. Входы (M2+M+1)...(M2+2M) блока 21 соединены с соответствующими управляющими М входами коммутатора I2M+1 выход которого является (2М+1)-м выходом БРиК 21. Входы (M2+2M+1)...(M2+3M) блока 21 соединены с соответствующими управляющими М входами коммутатора I2M+2, выход которого является (2М+2)-м выходом БРиК 21. Первые М сигнальных входов БРиК 21 (с ГСЧ 22) соединены соответственно с сигнальными М входами коммутатора I2M+1 и через соответствующие ключи II1...IIм с соответствующими (4М+3)...(5М+3) выходами блока 21, а также с соответствующими сигнальными М входами М нечетных коммутаторов I1...I2M-1, вырабатывающих КЧМнС для приема нижней боковой полосы (НБП), а через ключи II3M+1...II4M - с соответствующими сигнальными М входами М четных коммутаторов I4M+2...I2М+4, вырабатывающих КЧМнС для приема верхней боковой полосы (ВБП). Вторые М сигнальных входов БРиК 21 [с (М+1)-го по 2М-й] соединены соответственно с сигнальными М входами коммутатора I2М+2 и через соответствующие ключи IIм+1...II2M с соответствующими сигнальными М входами М четных коммутаторов I2...I2M, вырабатывающих КЧМнС для приема НБП, а через ключи II2M+1...II3M - с соответствующими сигнальными М входами М нечетных коммутаторов I4M+1...I2M+3, вырабатывающих КЧМнС для приема ВБП. Входы (M2+1)...(M2+М) блока 21 соединены с управляющими входами соответствующих 2М ключей II1, IIM+1...IIM, II2M, а входы (M2+3M+1)...(M2+4M) блока 21 соединены с управляющими входами соответствующих 2М ключей II4M, II3M...II3M+1, II2M+1. Управляющие входы БРиК 21 [1...М; (M2-M)...M2; (M2+1)...(M2+M); (M2+M+1)...(M2+2M); (M2+2M+1)...(M2+3М); (M2+3M+1)...(M2+4M)] соединены с соответствующими выходами блока управления 26 условной шиной (фиг.2б).

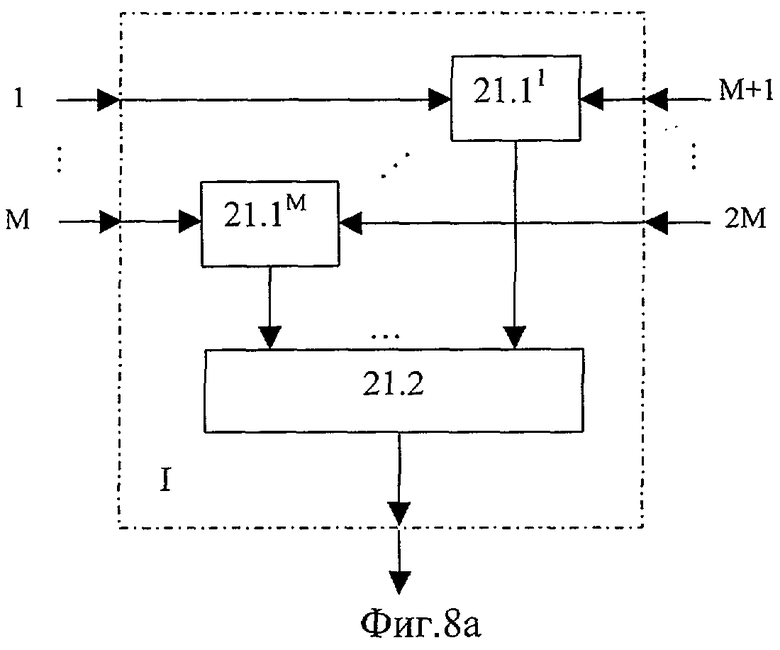

Функциональная схема коммутатора I, в свою очередь, показана на фиг.8а, где введены следующие обозначения:

21.11,...21.1М - ключи;

21.2 - сумматор.

Управляющие М входов коммутатора I соединены с первыми входами соответствующих ключей 21.11,...21.1М, сигнальные входы которых соединены с остальными (М+1)...2M входами коммутатора I соответственно, при этом выходы ключей 21.11,...21.1М соединены с соответствующими М входами сумматора 21.2, выход которого является выходом коммутатора I.

Коммутаторы I служат для формирования соответствующих синфазных и квадратурных опорных КЧМнС из непрерывных синусоидальных колебаний с выходов ГСЧ 22. Ключи 21.1 управляются командами с блока 26, поступающими на фиг.2б по условно обозначенной шине [входы на фиг.8 (M2-M)...M2, (M2+M+1)...(M2+2M), (M2+2M+1)...(M2+3M]. На фиг.8 2М левых верхних коммутаторов вырабатывают исходные опорные КЧМнС для приема НБП входного двухполосного КЧМнС (выходы 1,...,2М), а 2М правых коммутаторов [(2М+3)...(4М+2)] вырабатывают исходные опорные КЧМнС для приема ВБП [выходы (2М+3),...(4М+2)]. Два левых нижних на фиг.8 коммутатора [(2М+1)-й и (2М+2)-й] формируют исходные квадратурные КЧМнС [выходы (2М+1) и (2М+2)], на основе которых БФОС 20 вырабатывает однополосные опорные КЧМнС для поиска пораженных частотных позиций в нижней и верхней боковых полосах входного двухполосного КЧМнС. Эти сигналы последовательно поступают на четвертый вход блока поиска узкополосных помех 25 (фиг.2б). Блок 25 по второму выходу выдает в блок управления 26 информацию о пораженных частотах, на основе которой блок 26 вырабатывает команды на запирание соответствующих ключей II1,...II2M и II2M+1,...II4M [входы (M2+1)...(M2+M), (M2+3M+1)...(M2+4M) на фиг.8, входящие в шину], осуществляющих режекцию в нижней и верхней боковых полосах опорных КЧМнС.

Таким образом, БРиК 21 вырабатывает исходные КЧМнС с режектированными пораженными частотами, на основе которых БФОС 20 формирует необходимые опорные КЧМнС.

Функциональная схема БФОС 20 приведена на фиг.9, где обозначено

20.1 - фазовращатель на 90°;

20.21,...20.2М - сумматоры;

20.31,...20.3М+1 - преобразователи НБП;

20.41,...20.4М+1 - преобразователи ВБП;

20.5 - переключатель.

Вход (4М+4) блока формирования опорных сигналов 20 соединен с входом фазовращателя на 90° 20.1 и с первыми входами преобразователей НБП 20.31,...20.3M+1 и ВБП 20.41,...20.4М+1, вторые входы которых соединены между собой и с выходом фазовращателя на 90° 20.1, третьи и четвертые входы преобразователей НБП 20.31,...20.3M являются [первым, вторым...(2М-1), 2М-м] входами БФОС 20 соответственно, а третьи и четвертые входы преобразователей ВБП 20.41,...20.4М являются [(4М+2), (4М+1)...(2М+4), (2М+3)] входами БФОС 20 соответственно, кроме того, третьи входы блоков 20.3М+1 и 20.4M+1 соединены между собой и являются (2М+1)-м входом БФОС 20, а четвертые входы блоков 20.3М+1 и 20.4М+1 соединены между собой и являются (2М+2)-м входом БФОС 20. Выходы каждой пары преобразователей НБП и ВБП 20.31, 20.41...20.3М, 20.4М соединены с первым и вторым входами соответствующих сумматоров 20.21...20.2М, выходы которых являются 1...М-ми выходами БФОС 20. Выходы преобразователей НБП 20.3М+1 и ВБП 204.М+1 соединены соответственно с первым и вторым входами переключателя 20.5, третий вход которого является (4М+3)-м входом блока 20, а выход переключателя 20,5 является (М+1)-м выходом БФОС 20.

На преобразователь НБП 20.31,...20.3М+1 и соответствующий ему преобразователь ВБП 20.41,...20.4М+1 с выходов соответственно 1,...2М и (2М+3),...(4М+2) БРиК 21 поступают низкочастотные исходные КЧМнС, в общем случае с разными режектированными частотами. Опорный генератор 19 (фиг.2б) вырабатывает некоторую промежуточную частоту, поступающую на вход (4М+4) БФОС 20, которая служит для формирования двухполосных опорных сигналов.

На выходах преобразователей НБП 20.3 и ВБП 20.4 формируются соответственно нижние и верхние полосы опорных КЧМнС, которые объединяются в сумматорах 20.21,...20.2М.

Формирование полос опорного сигнала для блока поиска узкополосных помех 25 (фиг.2б) происходит в преобразователях 20.3М+1 и 20.4M+1, на которые поступают низкочастотные исходные КЧМнС с выходов (2М+1) и (2М+2) БРИК 21. Сигналы с выходов преобразователей 20.3М+1 и 20.4М+1 последовательно через переключатель 20.5 подаются по выходу (М+1) блока 20 на опорный (четвертый) вход блока 25. Переключатель 20.5 по входу (4М+3) управляется сигналом с первого выхода блока управления 26.

Функциональные схемы преобразователей НБП 20.3 и ВБП 20.4 представлены на фиг.10а и 10б соответственно, где обозначено:

20.3.11, 20.3.12, 20.4.11, 20.4.12 - перемножители;

20.3.2 - сумматор;

20.4.2 - блок вычитания.

Первые входы перемножителей 20.3.11 и 20.3.12 соединены соответственно с первым и вторым входами преобразователя НБП 20.3, а вторые их входы - соответственно с третьим и четвертым входами преобразователя НБП 20.3, выходы перемножителей 20.3.11 и 20.3.12 соединены с входами сумматора 20.3.2, выход которого является выходом блока 20.3. В схеме преобразователя ВБП 20.4 все функциональные связи аналогичны, только вместо сумматора 20.3.2 используется блок вычитания 20.4.2.

Работа этих схем основана на простых тригонометрических соотношениях:

cos(α+β)=cosαcosβ-sinαsinβ,

cos(α-β)=cosαcosβ+sinαsinβ,

где cos(α+β) означает сигнал ВБП,

a cos(α-β) - сигнал НБП.

Необходимо подчеркнуть, что при приеме однополосного КЧМнС блоки 20 и 21 (фиг.2б) существенно упрощаются.

Функциональная схема блока поиска узкополосных помех 25 показана на фиг.11, где обозначено:

25.1 - смеситель;

25.2 - усилитель промежуточной частоты (УПЧ);

25.3 - ключ;

25.4 - амплитудный детектор;

25.5 - пороговый блок.

Блок поиска узкополосных помех 25 представляет собой последовательно соединенные смеситель 25.1, УПЧ 25.2, амплитудный детектор 25.4, пороговый блок 25.5, выход которого является вторым выходом блока поиска узкополосных помех 25. Первый и второй входы смесителя 25.1 являются соответственно первым и четвертым входами блока 25, третий вход которого является вторым входом порогового блока 25.5. Выход УПЧ 25.2 соединен также с первым входом ключа 25.3, второй вход которого является соответствующим входом блока 25, кроме того, выход амплитудного детектора 25.4 соединен с первым выходом блока 25.

Работа блока поиска узкополосных помех 25 происходит следующим образом.

На четвертый вход блока 25 (второй вход смесителя 25.1) с (М+1)-го выхода БФОС 20 (фиг.2б) подается опорный сигнал, который представляет последовательность радиоимпульсов длительностью Ти с разными несущими частотами. В результате просматриваются все частотные позиции входного КЧМнС. Полоса УПЧ 25.2 выбирается порядка  , что достаточно для радиоимпульса длительностью Tи. Значение его амплитуды с выхода детектора 25.4 передается по первому выходу в блок управления 26 (фиг.2б) для вычисления величины порога. После анализа амплитуды радиоимпульса с одной частотной позиции фильтр УПЧ 25.2 обнуляется ключом 25.3, управляемым сигналом, поступающим на второй вход, после чего начинается анализ другой частотной позиции. Значения амплитуд на каждой частотной позиции сравниваются в пороговом блоке 25.5 с величиной порога, который вычисляется в блоке 26 и подается на второй вход блока 25.5 (третий вход блока 25). При превышении порога по второму выходу блока 25 вырабатывается сигнал, по которому блок управления 26 выдает команду в БРиК 21 на режекцию соответствующей частоты.

, что достаточно для радиоимпульса длительностью Tи. Значение его амплитуды с выхода детектора 25.4 передается по первому выходу в блок управления 26 (фиг.2б) для вычисления величины порога. После анализа амплитуды радиоимпульса с одной частотной позиции фильтр УПЧ 25.2 обнуляется ключом 25.3, управляемым сигналом, поступающим на второй вход, после чего начинается анализ другой частотной позиции. Значения амплитуд на каждой частотной позиции сравниваются в пороговом блоке 25.5 с величиной порога, который вычисляется в блоке 26 и подается на второй вход блока 25.5 (третий вход блока 25). При превышении порога по второму выходу блока 25 вырабатывается сигнал, по которому блок управления 26 выдает команду в БРиК 21 на режекцию соответствующей частоты.

Функциональная схема первого блока синхронизации 23 показана на фиг.12, где обозначено:

23.11, 23.12 - смесители;

23.2 - коммутатор;

23.31, 23.32 - усилители промежуточной частоты;

23.4 - формирователь импульсов коммутации;

23.51, 23.52 - амплитудные детекторы;

23.61, 23.62 - пороговые устройства;

23.7 - блок задержки на время Tи;

23.8 - фазовращатель на 90°;

23.91, 23.92 - перемножители;

23.10 - формирователь тактовых импульсов;

23.111,...23.113 - интеграторы;

23.12 - фильтр петли;

23.131, 23.132 - ключи;

23.14 - сумматор:

23.15 - управляемый генератор тактовых импульсов;

23.16 - делитель частоты.

Первый вход первого блока синхронизации 23 соединен с первыми входами первого 23.11 и второго 23.12 смесителей, причем второй вход второго смесителя 23.12 является вторым входом блока 23, а выход первого смесителя 23.11 через последовательно соединенные первый УПЧ 23.31 и первый амплитудный детектор 23.51 соединен с входом первого интегратора 23.111 и с первым входом первого перемножителя 23.91, являющегося первым входом системы ФАПЧ, состоящей из последовательно соединенных первого перемножителя 23.91, фильтра петли 23.12, сумматора 23.14 и управляемого генератора тактовых импульсов 23.15, выход которого соединен со вторым входом перемножителя 23.91 и с входом формирователя тактовых импульсов 23.10, выход которого соединен с первым входом первого ключа 23.131 и через последовательно соединенные вторые интегратор 23.112 и пороговое устройство 23.62 со вторым выходом блока 23, при этом второй вход блока 23.62 является входом порога. Выход второго смесителя 23.12 через последовательно соединенные второй УПЧ 23.32 и второй амплитудный детектор 23.52 соединен со вторым входом второго интегратора 23.112, через блок задержки 23.7 - с первым входом второго перемножителя 23.92, а через фазовращатель на 90° - со вторым входом перемножителя 23.92, выход которого через третий интегратор 23.113 соединен с первым входом второго ключа 23.132, второй вход которого является (М+4)-м входом блока синхронизации 23, а выход соединен со вторым входом сумматора 23.14. Выход первого интегратора 23.111 через последовательно соединенные первое пороговое устройство 23.61 и формирователь импульсов коммутации 23.4 соединен с (М+1)-м входом коммутатора 23.2, выход которого соединен со вторым входом первого смесителя 23.11, причем остальные М входов коммутатора 23.2 (с первого по m-й) соединены с третьим... (М+2)-м входами блока 23 соответственно. (М+3)-й вход первого блока синхронизации 23 является вторым входом первого ключа 23.131, выход которого соединен с первым выходом блока 23 и через делитель частоты 23.16 - с третьим выходом блока 23, при этом выход делителя частоты 23.16 соединен также со вторым входом формирователя импульсов коммутации 23.4, а второй вход первого порогового устройства 23.61 является входом порога.

Установление синхронизации начинается после режекции частотных составляющих, пораженных узкополосными помехами. При этом на смеситель 23.11 через коммутатор 23.2 поступает неманипулированное колебание с одной из непораженных опорных частот, поступающих на входы 3,...М+2. Колебания непораженных опорных частот можно взять в случае приема однополосного КЧМнС непосредственно с выходов ключей II1,...IIM на фиг.8, как это показано на фиг.2б. В общем случае эти колебания, перенесенные в область опорной частоты, генерируемой блоком 19, можно сформировать в БФОС 20. На второй вход смесителя 23.12 поступает опорный сигнал с первого выхода БФОС 20.

В результате на выход УПЧ 23.31 проходит сигнал, соответствующий одной из частотных позиций входного КЧМнС, например, частоте f1 на фиг.3. В этом случае он будет манипулирован по амплитуде и фазе информационными символами с номерами 1, 2, 3, 4. Провалы огибающей, возникающие при прохождении сигнала через фильтр в УПЧ 23.31, соответствуют моментам смены информационных символов, задаваемых тактовыми импульсами. Огибающая выделяется амплитудным детектором 23.51 и фильтруется схемой ФАПЧ, которая включает элементы 23.91, 23.12, 23.14, 23.15. Тактовые импульсы с частотой fи с выхода системы ФАПЧ формируются блоком 23.10 и служат для сброса интегратора 23.112 и для формирования импульсов с частотой  делителем частоты 23.16, следовательно, блок синхронизации 23 по выходу 1 выдает импульсы с частотой

делителем частоты 23.16, следовательно, блок синхронизации 23 по выходу 1 выдает импульсы с частотой  а по выходу 3 - с частотой

а по выходу 3 - с частотой  . Сигнал с выхода амплитудного детектора 23.51 интегрируется в блоке 23.111 и поступает на пороговое устройство 23.61, где сравнивается с порогом. Превышение порога означает, что с выхода коммутатора 23.2 поступает непораженное (нережектированное) опорное колебание. При этом состояние коммутатора 23.2 не меняется. Если порог не превышен, формирователь 23.4 изменяет состояние коммутатора 23.2, соединяя с выходом другой вход.

. Сигнал с выхода амплитудного детектора 23.51 интегрируется в блоке 23.111 и поступает на пороговое устройство 23.61, где сравнивается с порогом. Превышение порога означает, что с выхода коммутатора 23.2 поступает непораженное (нережектированное) опорное колебание. При этом состояние коммутатора 23.2 не меняется. Если порог не превышен, формирователь 23.4 изменяет состояние коммутатора 23.2, соединяя с выходом другой вход.

В принципе схема тактовой синхронизации, основанная на фильтрации огибающей, является типовой для ФМн сигналов.

После установления грубой тактовой синхронизации схема на фиг.12 переходит к поиску сигнала (в данном случае пилот-сигнала) по задержке. Для этого по команде с блока управления 26 (фиг.26), поступающей на (М+3)-й вход блока 23, ключ 23.131 исключает по одному тактовому импульсу на интервале МТи до тех пор, пока последовательность частотно-временных элементов опорного сигнала не совпадет с последовательностью частотно-временных элементов входного КЧМнС (фиг.13). При совпадении элементов на входе УПЧ 23.32 во временной области появится последовательность радиоимпульсов длительностью Ти, которая в случае идеальной тактовой синхронизации превращается в синусоидальное колебание. Полоса УПЧ 23.32 выбирается порядка  , т.е. образующиеся радиоимпульсы проходят через блок 23.32, практически не перекрываясь. Эти импульсы детектируются в амплитудном детекторе 23.52 и после интегрирования в блоке 23.112 поступают в пороговое устройство 23.62. В блоке 23.62 при совпадении элементов входного и опорного КЧМнС во временной области будет наблюдаться превышение порога на каждом тактовом интервале Ти (за исключением пораженных). Информация о превышении порога с выхода блока 23.62 (со второго выхода блока 23) поступает на третий вход блока управления 26 (фиг.2б), который по четвертому выходу принимает решение о прекращении поиска по задержке и переходу к точной тактовой синхронизации путем отпирания ключа 23.13. Так как тактовыми импульсами синхронизируются все колебания, вырабатываемые ГСЧ 6 (фиг.2а) и ГСЧ 22 (фиг.26) при точной тактовой синхронизации последовательность радиоимпульсов (пилот-сигнала) с выхода смесителя 23.12 превращается в синусоидальное колебание, т.к. соседние импульсы (длительностью Ти) приобретают одинаковые начальные фазы. В результате прохождения этого сигнала через блок задержки 23.7 и фазовращатель на 90° 23.8 на входах перемножителя 23,92 действуют два синусоидальных колебания, сдвинутых на 90°. Перемножитель 23.92 и интегратор 23.113 образуют фазовый детектор. При отклонении тактовых импульсов от идеального положения между соседними радиоимпульсами возникает разность фаз Δϕ и на выходе блока 23.113 появляется напряжение рассогласования, пропорциональное sinΔϕ, которое через ключ 23.132 поступает на сумматор 23.14 и дополнительно подстраивает петлю ФАПЧ.

, т.е. образующиеся радиоимпульсы проходят через блок 23.32, практически не перекрываясь. Эти импульсы детектируются в амплитудном детекторе 23.52 и после интегрирования в блоке 23.112 поступают в пороговое устройство 23.62. В блоке 23.62 при совпадении элементов входного и опорного КЧМнС во временной области будет наблюдаться превышение порога на каждом тактовом интервале Ти (за исключением пораженных). Информация о превышении порога с выхода блока 23.62 (со второго выхода блока 23) поступает на третий вход блока управления 26 (фиг.2б), который по четвертому выходу принимает решение о прекращении поиска по задержке и переходу к точной тактовой синхронизации путем отпирания ключа 23.13. Так как тактовыми импульсами синхронизируются все колебания, вырабатываемые ГСЧ 6 (фиг.2а) и ГСЧ 22 (фиг.26) при точной тактовой синхронизации последовательность радиоимпульсов (пилот-сигнала) с выхода смесителя 23.12 превращается в синусоидальное колебание, т.к. соседние импульсы (длительностью Ти) приобретают одинаковые начальные фазы. В результате прохождения этого сигнала через блок задержки 23.7 и фазовращатель на 90° 23.8 на входах перемножителя 23,92 действуют два синусоидальных колебания, сдвинутых на 90°. Перемножитель 23.92 и интегратор 23.113 образуют фазовый детектор. При отклонении тактовых импульсов от идеального положения между соседними радиоимпульсами возникает разность фаз Δϕ и на выходе блока 23.113 появляется напряжение рассогласования, пропорциональное sinΔϕ, которое через ключ 23.132 поступает на сумматор 23.14 и дополнительно подстраивает петлю ФАПЧ.

Таким образом обеспечивается возможность когерентного сложения частотных позиций КЧМнС.

Второй блок синхронизации 16 (фиг.2б) может быть выполнен по функциональной схеме, приведенной на фиг.14, где обозначено:

16.11,16.12,...16.1М - смесители;

16.21,16.22,...16.2М - усилители промежуточной частоты (УПЧ);

16.31, 16.32,...16.3М - амплитудные детекторы;

16.41, 16.42,...16.4М - интеграторы;

16.5 - блок вычисления порога;

16.61,16.62,...16.6М - пороговые блоки;

16.7 - блок обнаружения сигнала (БОС);

16.8 - блок управления синтезатором частот;

16.9 - генератор кода.

Второй блок синхронизации 16 (фиг.2б) содержит М каналов обнаружения, каждый из которых состоит из соответствующих последовательно соединенных смесителя 16.1, УПЧ 16.2, амплитудного детектора 16.3 и интегратора 16.4, причем первые входы смесителей 16.11,16.12,...16.1М объединены и соединены с первым (сигнальным) входом блока 16. Второй вход каждого из смесителей 16.11,16.12,...16.1М соединен с соответствующим (со второго по (М+1)-й) входом блока 16. Выход каждого из интеграторов 16.41, 16.42,...16.4М соединен с первым входом соответствующего порогового блока 16.61,16.62,...16.6M и через блок вычисления порога 16.5 с его вторым входом. Выход каждого порогового блока 16.6 соединен с соответствующим входом блока обнаружения сигнала 16.7, выход которого является вторым выходом блока синхронизации 16. Вход (М+2) блока 16 через последовательно соединенные генератор кода 16.9 и блок управления синтезатором частот 16.8 соединен с первым выходом блока 16.

Работу второго блока синхронизации 16 можно представить следующим образом.

В начальный момент времени генератор кода 16.9 находится в состоянии, соответствующем некоторой частотной позиции. Когда входной сигнал с ППРЧ достигает этой позиции, напряжения на выходах каналов обнаружения, состоящих из смесителей 16.1, УПЧ 16.2, амплитудных детекторов 16.3 и интеграторов 16.4, превышают величину порога во всех пороговых блоках 16.6. На основе мажоритарного правила блок 16.7 принимает решение об обнаружении сигнала и передает его по выходу 2 в блок управления 26 (фиг.2б), который после пропадания сигнала начинает управлять работой генератора кода 16.9 по входу (М+2). Блок 16.5 на основе анализа сигнала на несовпадающих частотных позициях вычисляет величину порога. Блок 16.8 непосредственно управляет синтезатором частот 15 (фиг.2б).

Функциональная схема квадратурного демодулятора 24 (фиг.2б) приведена на фиг.15, где обозначено:

24.11,24.12 - перемножители;

24.21, 24.22, 24.23 - интеграторы;

24.3 - амплитудный детектор;

24.41, 24.42 - блоки нормировки.

Квадратурный демодулятор 24 (фиг.2б) содержит две параллельные цепочки, каждая из которых состоит из последовательно соединенных соответствующих перемножителя 24.1, интегратора 24.2 и блока нормировки 24.4. Первые входы перемножителей 24.11, 24.12 объединены и соединены с первым входом блока 24, выходы первого и второго блоков нормировки 24.41, 24.42 соответственно являются первым и вторым выходами квадратурного демодулятора 24, второй вход которого является вторым входом первого перемножителя 24.11, а третий вход соединен со вторым входом второго перемножителя 24.12 и через последовательно соединенные амплитудный детектор 24.3 и третий интегратор 24.23co вторыми входами блоков нормировки 24.41, 24.42. Четвертый вход квадратурного демодулятора 24 соединен со вторыми входами интеграторов 24.21, 24.22, 24.23.

Работа квадратурного демодулятора 24 происходит следующим образом.

На выходах интеграторов 24.21 и 24.22 формируются проекции вектора информационного сигнала на координатные оси, задаваемые пилот-сигналом. Для демодуляции АФМ сигналов используется нормировка амплитуд проекций путем деления на амплитуду пилот-сигнала, которая формируется блоками 24.3 и 24.23. Блок 27 (фиг.2б) по значениям проекций вычисляет значения расширенных информационных символов (для случая, представленного на фиг.3, с номерами 2, 3 и 4) и записывает их в память, откуда они последовательно считываются со скоростью  .

.

Блок управления 26 (фиг.2б) может быть выполнен на основе микропроцессора с соответствующим программным обеспечением, например, TMS 320 Схх, Motorola 56xxx, Intel и др.

Остальные блоки на фиг.2б являются типовыми и не нуждаются в раскрытии.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПАРАЛЛЕЛЬНЫЙ КОРОТКОВОЛНОВЫЙ МОДЕМ | 2004 |

|

RU2286648C2 |

| НЕЛИНЕЙНЫЙ РАДАР ДЛЯ ДИСТАНЦИОННОГО МОНИТОРИНГА ПРОДУКТОПРОВОДОВ | 2007 |

|

RU2343499C1 |

| УСТРОЙСТВО ВЫСОКОСКОРОСТНОГО РАДИОПРИЕМА БЛОКА ЧИСЕЛ | 2010 |

|

RU2419967C1 |

| Способ передачи информации с использованием модуляции частотным сдвигом при наличии помех с неравномерной спектральной плотностью | 2022 |

|

RU2799089C1 |

| УСТРОЙСТВО И СПОСОБ КОМПЕНСАЦИИ УЗКОПОЛОСНЫХ ПОМЕХ В ЦИФРОВЫХ РАДИОСИСТЕМАХ ПЕРЕДАЧИ ИНФОРМАЦИИ | 2013 |

|

RU2552850C2 |

| УСТРОЙСТВО СЕЛЕКЦИИ ДВИЖУЩИХСЯ ЦЕЛЕЙ ДЛЯ РЕЖИМА ПЕРЕСТРОЙКИ ЧАСТОТЫ ОТ ИМПУЛЬСА К ИМПУЛЬСУ | 2014 |

|

RU2541504C1 |

| КОГЕРЕНТНАЯ РАДИОЛИНИЯ | 2005 |

|

RU2286026C1 |

| СПОСОБ КОМПЕНСАЦИИ ВНУТРИКАНАЛЬНЫХ АДДИТИВНЫХ РАДИОПОМЕХ В ПРИЕМНИКАХ АМПЛИТУДНО-МОДУЛИРОВАННЫХ, ЧАСТОТНО- И ФАЗОМАНИПУЛИРОВАННЫХ РАДИОСИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1996 |

|

RU2100903C1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ СТРУКТУРНЫХ ПОМЕХ | 2010 |

|

RU2450445C2 |

| УСТРОЙСТВО КОМПЕНСАЦИИ СТРУКТУРНЫХ ПОМЕХ | 2013 |

|

RU2534221C1 |

Изобретение относится к радиотехнике и может быть использовано для передачи дискретной информации в условиях радиоэлектронного противодействия. Технический результат заключается в повышении помехозащищенности системы связи с медленной псевдослучайной перестройкой рабочей частоты. Для этого вводят дополнительно быструю перестройку рабочей частоты. При этом каждый информационный символ исходной длительности последовательно передается на каждой частоте из сетки частот быстрой перестройки рабочей частоты. Сохранение исходной ширины спектра сигнала на каждой частотной позиции достигается объединением информационных символов в блоки с одновременным увеличением их длительности. Сохранение скорости передачи достигается параллельной передачей информационных символов блока на всех частотах сетки частот быстрой перестройки. В результате исключения частотных позиций, пораженных узкополосными помехами, теряется лишь часть информационного символа. Потери компенсируются за счет когерентного накопления частей информационного символа с разных частотных позиций. 15 ил.

Помехозащищенная система связи, состоящая из передатчика и приемника, причем передатчик содержит источник информации, блок модуляции, преобразователь частоты, выход которого через усилитель мощности соединен с передающей антенной, а второй вход соединен с выходом синтезатора несущей частоты, блок коммутации, генератор сетки частот (ГСЧ), блок опорных частот, первый выход которого соединен с первым входом ГСЧ и с входом источника информации, а второй выход соединен с входом генератора кода, приемник содержит приемную антенну, соединенную с сигнальным входом первого смесителя, опорный вход которого соединен с выходом синтезатора частот, а выход соединен с входом первого усилителя промежуточной частоты (УПЧ), выход которого соединен с сигнальными входами блока поиска узкополосных помех, первого информационного канала, состоящего из последовательно соединенных соответствующих смесителя, УПЧ и квадратурного демодулятора, и первого блока синхронизации, первый выход которого соединен с входом ГСЧ, М пар квадратурных выходов которого соединены с соответствующими 2М сигнальными входами блока режекции и коммутации, опорный генератор, выход которого соединен с опорным входом блока формирования опорных сигналов (БФОС), блок управления, первый и второй входы которого соединены с соответствующими выходами блока поиска узкополосных помех, третий вход которого соединен со вторым выходом блока управления, третий вход которого соединен со вторым выходом первого блока синхронизации, отличающаяся тем, что в передатчик введен преобразователь информационных символов, первый вход которого соединен с выходом источника информации, второй вход является входом добавочного символа, служащего пилот-сигналом, а М выходов соединены с соответствующими М информационными входами блока модуляции, М опорных входов которого соединены с М соответствующими выходами ГСЧ, второй вход которого соединен с четвертым выходом блока опорных частот, третий выход которого соединен с третьим входом преобразователя информационных символов и со вторым входом формирователя импульсов управления, первый вход которого соединен с четвертым входом преобразователя информационных символов и с первым выходом блока опорных частот, М2 выходов блока модуляции соединены с соответствующими М2 сигнальными входами блока коммутации, М2 управляющих входов которого соединены с соответствующими М2 выходами формирователя импульсов управления, причем выход блока коммутации соединен с первым входом преобразователя частоты, а выход генератора кода соединен с входом синтезатора несущей частоты, в приемник введены (М-2) информационных канала, идентичных первому, два квадратурных пилот-канала, каждый из которых состоит из соответствующих последовательно соединенных смесителя и УПЧ, преобразователь информационных символов, фазовращатель на 90° и второй блок синхронизации, первый выход которого соединен с входом синтезатора частот, а второй выход соединен с четвертым входом блока управления, пятый вход которого соединен с первым выходом первого блока синхронизации, вторым входом блока поиска узкополосных помех и (2М-1)-м входом преобразователя информационных символов, выход которого является выходом приемника, а (2М-2) остальных входов соединены соответственно с (М-1) парами выходов соответствующих квадратурных демодуляторов (М-1) информационных каналов, вторые входы всех квадратурных демодуляторов объединены и соединены с выходом УПЧ синфазного пилот-канала, третьи входы всех квадратурных демодуляторов объединены и соединены с выходом УПЧ квадратурного пилот-канала, четвертые входы всех квадратурных демодуляторов объединены и соединены с третьим выходом первого блока синхронизации, сигнальные входы смесителей обоих пилот-каналов и смесителей всех введенных (М-2) информационных каналов объединены и соединены с выходом первого УПЧ, опорный вход смесителя квадратурного пилот-канала через фазовращатель на 90° соединен с опорным входом смесителя синфазного пилот-канала, с первым выходом БФОС и со вторым входом первого блока синхронизации, М следующих входов [с третьего по (М+2)-й] которого соединены с соответствующими М выходами [с (4М+3)-го по (5М+3)-й] блока режекции и коммутации, остальные (4М+2) выходов [с первого по (4М+2)-й] которого соединены с соответствующими входами БФОС, (4М+3)-й вход которого соединен с первым выходом блока управления, (М-1) выходов БФОС (со второго по М-й) соединены с опорными входами соответствующих смесителей информационных каналов, а (М+1)-й выход соединен с четвертым входом блока поиска узкополосных помех, сигнальный вход второго блока синхронизации соединен с выходом первого УПЧ, М следующих входов [со второго по (М+1)-й] соединены с соответствующими синфазными выходами ГСЧ, а (М+2)-й вход соединен с третьим выходом блока управления, четвертый и пятый выходы которого соединены соответственно с (М+4)-м и (М+3)-м входами первого блока синхронизации, а следующие (М2+4М) выходов соединены шиной с соответствующими управляющими входами блока режекции и коммутации.

| АДАПТИВНАЯ СИСТЕМА СВЯЗИ С ПОВЫШЕННОЙ ПОМЕХОЗАЩИЩЕННОСТЬЮ | 2002 |

|

RU2226037C1 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ В РАДИОЛИНИИ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧИХ ЧАСТОТ И УСТРОЙСТВО ЕГО РЕАЛИЗУЮЩЕЕ | 1994 |

|

RU2099886C1 |

| US 4653068, 24.03.1987 | |||

| ЕР 00/27152 В1, 22.04.1981 | |||

| JP 10079690 А, 24.03.1998 | |||

| ВАРАКИН Л.Е., Системы связи с шумоподобными сигналами | |||

| - М.: Радио и связь, 1985, с.19, рис.1.11 | |||

| Помехозащищенность радиосистем со сложными сигналами | |||

| Под ред | |||

| ТУЗОВА Г.И | |||

| - М.: Радио и связь, 1985. | |||

Авторы

Даты

2006-10-10—Публикация

2004-10-14—Подача