иен, как показано на фиг.2. Он служит д риминатора задержки, а также масшта

| название | год | авторы | номер документа |

|---|---|---|---|

| Следящий фильтр фазоманипулированного псевдослучайного сигнала | 1982 |

|

SU1072252A1 |

| УСТРОЙСТВО ПОДАВЛЕНИЯ УЗКОПОЛОСНЫХ ПОМЕХ | 2004 |

|

RU2259011C1 |

| Устройство для поиска шумоподобного сигнала | 1984 |

|

SU1277415A1 |

| УСТРОЙСТВО ДЛЯ ВЫДЕЛЕНИЯ ШУМОПОДОБНОГО СИГНАЛА | 1980 |

|

SU1840562A1 |

| ИЗМЕРИТЕЛЬ ФАЗ ОСЦИЛЛОГРАФИЧЕСКИЙ | 2005 |

|

RU2314543C2 |

| УСТРОЙСТВО КВАДРАТУРНОГО ПРИЕМА ЧАСТОТНО-МАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2010 |

|

RU2425457C1 |

| ПОМЕХОЗАЩИЩЕННАЯ СИСТЕМА СВЯЗИ | 2004 |

|

RU2285344C2 |

| Устройство синхронизации широкополосных псевдослучайных сигналов | 1985 |

|

SU1415445A1 |

| Устройство для корреляционного приема фазоманипулированных псевдослучайных сигналов | 1984 |

|

SU1252964A1 |

| Система синхронизации пространственно разнесенных часов | 1985 |

|

SU1299335A1 |

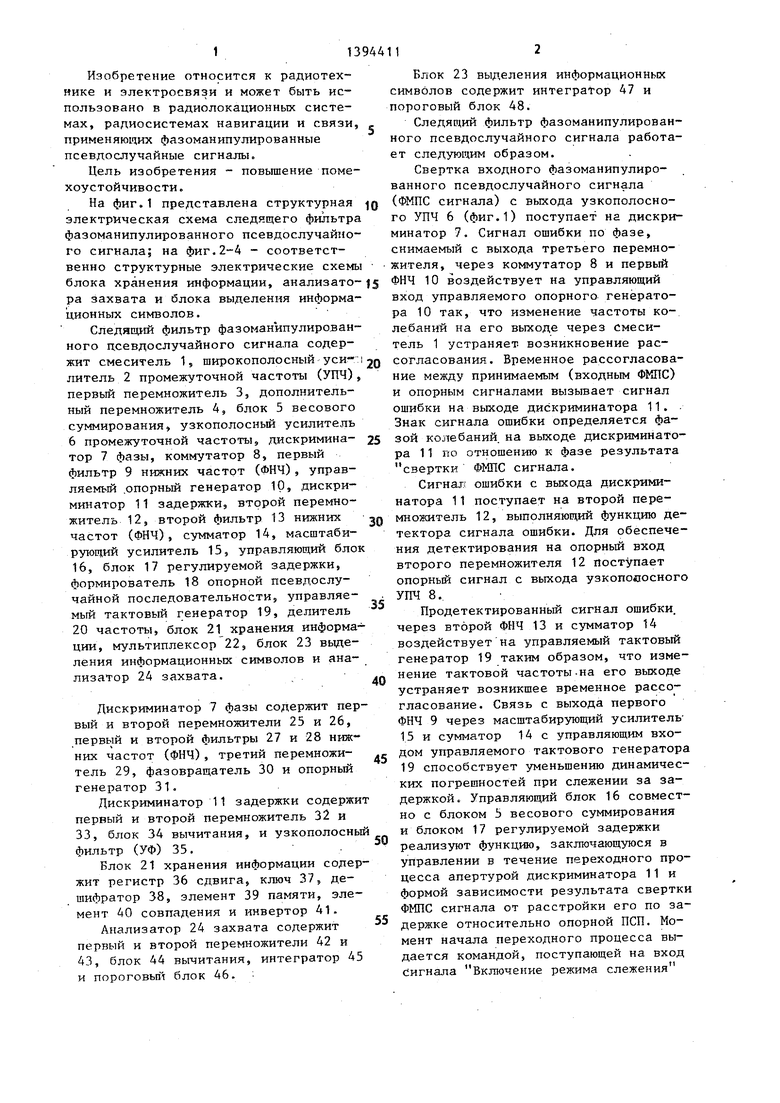

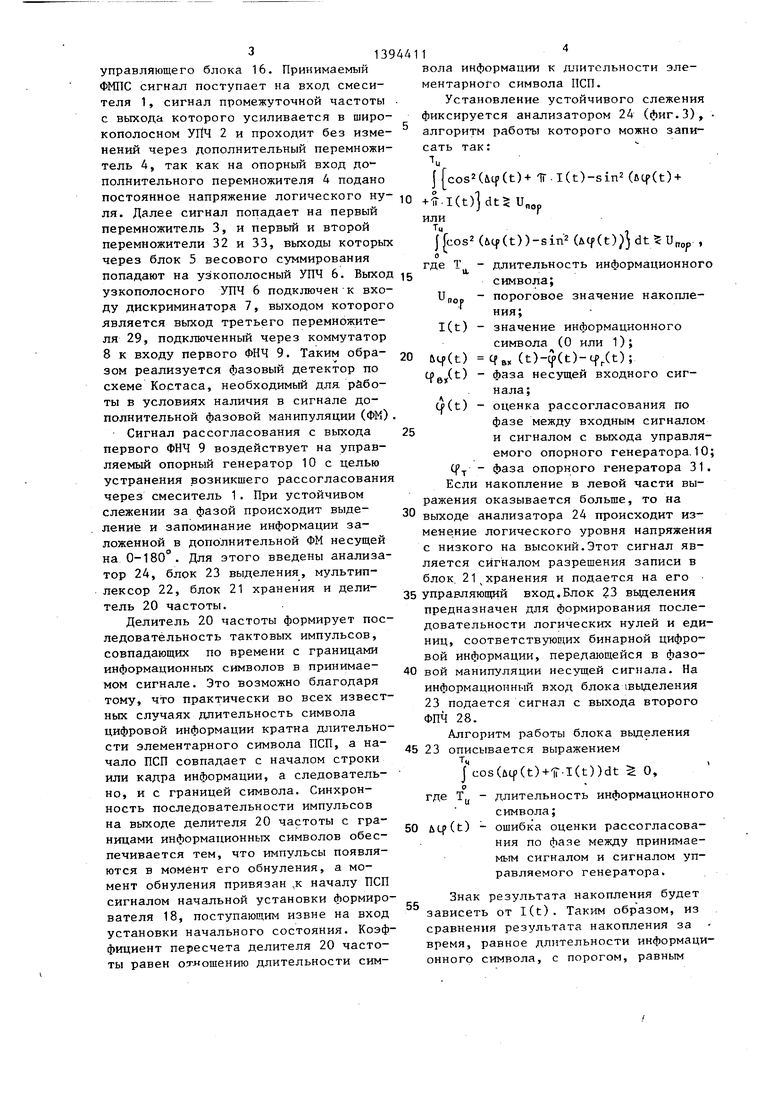

Изобретение относится к радиотехнике и электросвязи. Цель изобретения - повышение помехоустойчивости. В режеме слежения сигнал поступает на смеситель 1, широкополосный УПЧ 2 и проходит без изменений через дополнительный перемножитель (П) 4, на опорный вход к-рого подано постоянное напряжение логич.нуля. Далее сигнал попадает на П 3 и на П 32 и 33., через блок 5 весового суммирования на узкополосный УПЧ 6. Выход УПЧ 6 подключен к входу дискриминатора 7, выходом к-рого является выход П 29, подключенный через коммутатор 8 к входу фильтра 9 нижних частот. Т.обр. реализуется фазовый детектор по схеме Костаса, необходимый для работы в условиях наличия в сигнале дополнительной фазовой манипуляции. Сигнал с фильтра 9 воздействует на управляемый опорный г-р 10 с целью устране- ния рассогласования через смеситель 1. При устойчивом слежении за фазой происходит выделение и запоминание информации, заложенной в дополнительной фазоманипулированной несущей на 0-180 . Для этого введены анализатор 24, блок 23 выделения, мультиплексор 22, блок 21 хранения и делитель 20 частоты. 3 з.п. ф-лы, 4 ил. с (Я с

для запоминания последовательности символов, поступающих с блока 23 выделения, кадровой синхронизации и последующей циклической синхронной

выдачи информации на опорный вход ющий блок, первый, второй и третий полиительного перемноз сителя 4.

Цифровой сигнал на выходе блока 21 хранения, тактируемый импульсами, поступающими с делителя 20 частоты, точно воспроизводит информацию пере- 20 дающуюся в ФМПС сигнале, и совпадает с ней по времени. Дополнительньй перемнояитель 4, на опорный вход которого поступает этот сицнал, начинавьгходы которого подсоединены соотве ственно к первому и второму управля щим входам блока весового суммирова ния и управляющему входу блока регу лируемой задержки, дополнительный в ход формирователя опорной псевдослу чайной последовательности подсоедин к первому входу первого перемножите ля, второй вход которого подключен

ет работать как демодулятор, что при- 25 информационному входу дискриминатора

водит к полному восстановлению несущей входного сигнала после демодуляции ПСП в первых и втором перемножителях 3, 38 и 33. Это позволяет ис пользовать для фазового детектирования линейный фазовый детектор, роль которого может выполнить одно плечо фазового детектора, состоящее из первого перемножителя 25, фазовращателя 30, опорного генератора 31 и первого ФНЧ 27. Высокий уровень, поступающий со второго выхода блока 21 хранения на управляющий вход коммутатора 8., обеспечивает подключение выходы первого ФНЧ 27 через коммутатор 8 на вход первого ФНЧ 9.

При необходимости обновить информацию в регистре 36 извне подается кратковременный импульс на вход.инвертора 44.

Формула изобретения

бирующий усилитель, вход и выход которого подключены соответственно к выходу первого.фильтра нижних частот и второму входу сумматора, и управляющий блок, первый, второй и третий

вьгходы которого подсоединены соответственно к первому и второму управляющим входам блока весового суммирования и управляющему входу блока регулируемой задержки, дополнительный выход формирователя опорной псевдослучайной последовательности подсоединен к первому входу первого перемножите- ля, второй вход которого подключен к

0

5

0

5

0

5

задержки, вторые выходы iy)Toporo подсоединены к соответствующим информационным 15ходам блока весового суммирования, причем вход смесителя является входом с ледящего фильтра, а дискриминатор фазы содержит первый и второй перемножители, выходы которых подсоединены соответственно через первый и второй фильтры нижних частот к входам третьего перемножителя, первый вход первого перемножителя через фазовращатель объединен с первым входом второго перемножителя и подключен к выходу опорного генератора, объединенные вторые входы первого и второго перемножителей и выходы первого фильтра нижних частот, третьего перемножителя и второго фильтра ниж-- них частот являются соответственно входом и первым, вторым и третьим выходами дискриминатора фазы, дискриминатор задержки содержит последовательно соединенные первый перемножитель, блок вычитания и узкополосный фильтр, а также второй перемножитель, выход которого подключен к второму входу блока вычитания, первые и объединенные вторые входы первого и второго перемножителей являются соответственно опорными и информационным входами дискриминатора задержки, выход узкополосного фильтра и вькоды первого и второго перемножителей являются соответственно первым и вторы

10

15

713944

ми выходами дискриминатора задержки, отличающийся тем, что, с целью повышения помехоустойчивости, введены последовательно соединенные блок выделения информационных симво- лов, мультиплексор, блок хранения информации и дополнительный перемножитель, вход и выход которого подключены соответственно к выходу широкополосного усилителя промежуточной частоты и входу первого перемножителя, последовательно соединенные делитель частоты и анализатор захвата, выход которого подсоединен к управляющему входу блока хранения информации, а также коммутатор, первый и второй ин- формационные входы которого подключены соответственно к первому и второму выходам дискриминатора фазы, при этом 2п первый и третий выходы дискриминатора фазы подсоединены соответственно к первому информационному входу анализатора захвата и объединенным второму информационному входу анализатора 25 захвата и входу блока выделения информационных символов, тактовый вход которого объединен с тактовым входом блока хранения информации и подключен к выходу делителя частоты, установоч- , ный и счетный входы которого подключены соответственно к установочному входу формирователя опорной псевдослучайной последовательности и выходу управляемого тактового генератора, первый и второй выходы блока хранения информации подсоединены соответственно к информационному входу мультиплексора и объединенным управляющим входам мультиплексора и коммутатора, выход i oToporo подключен к входу первого фильтра нижних частот, вькод узкополосного усилителя промежуточной частоты подсоединен к второму входу второго перемножителя, а дополнительный выход управляющего блока подсоединен ко второму управляющему входу блока регулируемой задержки, причем установочный вход делителя частоты и вход сигнала смены информации блока хранения информации являются соответ- . ственно входом установки начального

40

45

0

5

44

п 5 .

0

5

118

состояния и входом сигнала смены информации следящего фильтра,

и тактовый входы регистра сдвига, второй вход элемента совпадения, вход инвертора, выходы ключа и элемента памяти являются соответственно информационным, тактовым и управляющим входами, входом сигнала смены информации и первым и вторым выходами блока хранения информации.

а также второй перемножитель, выход которого подсоединен к второмт входу блока вычитания, причем объединенные входь первого перемножителя, объединены входы второго перемножителя, вход Сброс интегратора и выход порогового блока являются соответственно первым и вторым информационным и тактовым входами и выходом анализатора захвата.

и выход порогового блока являются соответственно информационным и тактовым входами и выходом блока выделения информационных символов.

Ф1Л.2

Фи.З

| Следящий фильтр для некогерентной обработки сигнала с подавленной несущей фаза которого манипулирована по закону бинарной псевдослучайной последовательности | 1967 |

|

SU710008A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Следящий фильтр фазоманипулированного псевдослучайного сигнала | 1982 |

|

SU1072252A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

| СЛЕДЯЩИЙ ФИЛЬТР ФАЗОМАНИПУ- ЛИРОВАННОГО ПСЕВДОСЛУЧАЙНОГО СИГНАЛА | |||

Авторы

Даты

1988-05-07—Публикация

1986-02-25—Подача