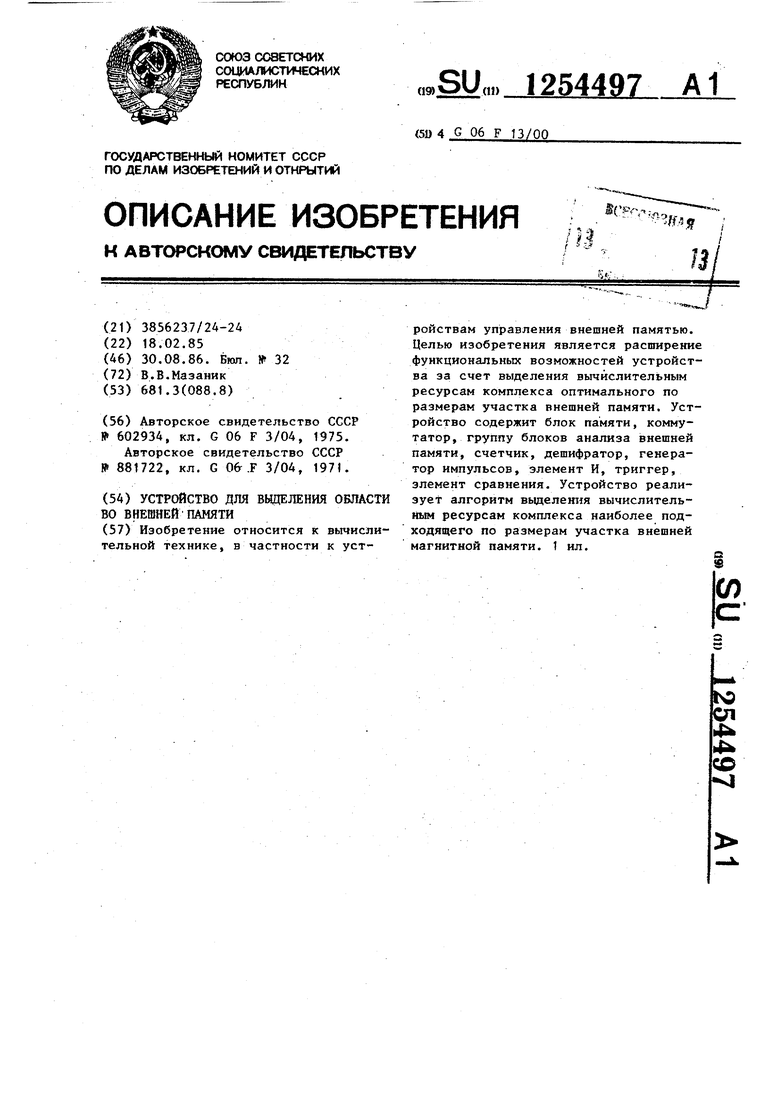

Изобретение относится к вычислительной технике, в частности, к устройствам управления внешней памятью.

Цель изобретения - расширение фуш циональных возможностей устройства за счет выделения вычислительным ресурсам комплекса оптимального размера участка внешней памяти.

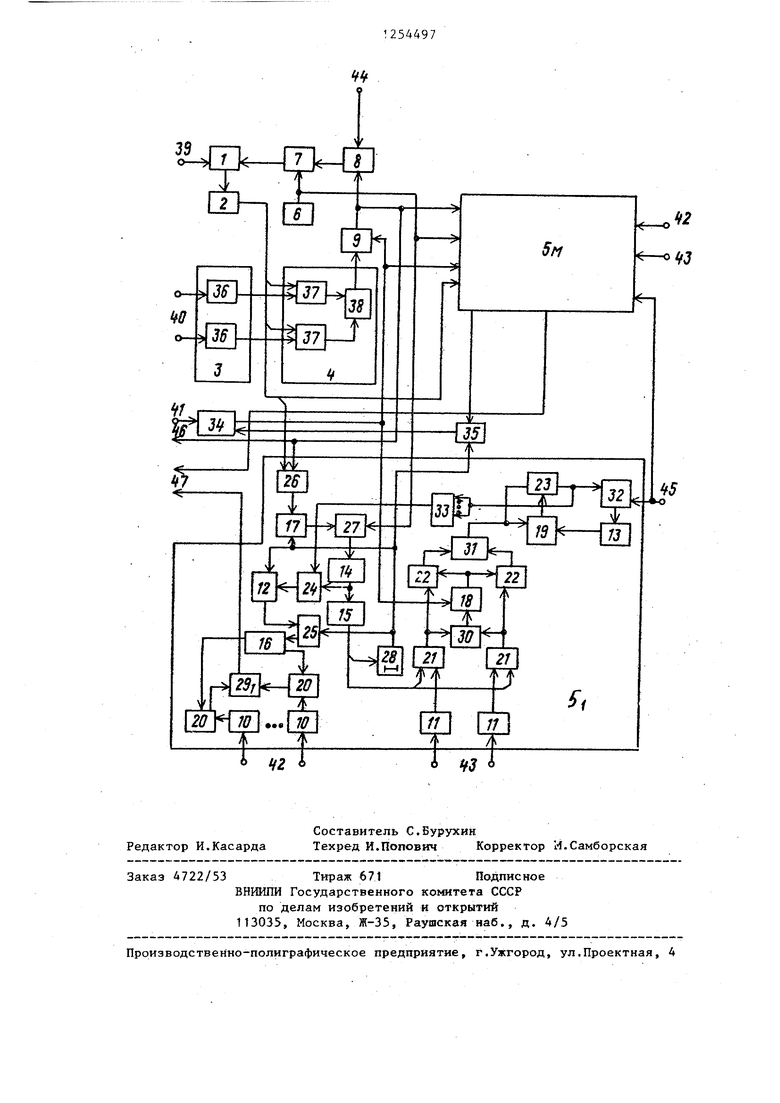

На чертеже представлена структурная схема устройства.

Устройство содержит счетчик 1, дешифратор 2, блок 3 памяти, коммутатор 4, группу 5. блоков анализа внешней памяти,генератор 6 импульсов, элемент 7 И, триггер 8, элемент 9 сравнения,,причем каждый блок анализа внешней памяти содержит первую и вторую группы регистров 10 и 11, первый, второй регистры 12 и 13, счетчик 14, первый и второй дешифраторы 15 и .16, триггер 17, Первый, второй элементы 18 и 19 сравнения, первую, вторую, третью группы блоков элементов И 20-22, первую, вторую.

третью группы элементов И 23-25, пер- 25 рованное время, равное максимальному

вый и второй элементы И 26 и 27, элементы 28 задержки, первую, вторую, третью и четвертую группы элементов ИЛИ 29-32, элемент ИЛИ 33, регистр 34, элемент 35 ИЛИ, блок 36 регистров, группу 37 блоков элементов И, блок 38 элементов РШИ, установочный вход 39 устройства, Jxoд 40 размера максимального свободного уча- йтка памяти устройства, вход 41 задания размера требуемого памяти устройства, группу входов 42 начального адреса, группу входов 43 размера свободного участка памяти, запускающий вход 44 устройства, вход 43 общей емкости памяти, выход 46 сигнализации готовности устройства, группу выходов 47 начального адреса устройства.

Устройство работает следующим образом.

По входу 41 в регистр 34 заносится код размера требуемого куска памяти на магнитном барабане (МБ). В счетчике 1 хранится код номера МБ/К, на котором вьщелена память для предшествующего запроса. По входу 44 триггер 8 устанавливается в единичное состояние и содержимое счетчика 1 увеличивается на 1: STJ : К+1. В регистрах 36 блока 3 памяти хранятся коды размеров максималь- ных свободных кусков памяти на Т, М (М - количество МБ). Содержимое

К+1-ГО регистра 36 через коммутатор 4 подключается к первому входу элемента 9 сравнения, на второй вход которого подается содержимое регист- ра 34. Если код размера максимального свободного куска памяти на К+1-м МБ превышает или равен требуемому, то на выходе элемента 9 сравнения появляется единичный сигнал, который обнуляет триггер 8, поступает на выход 46 устройства и запускает К+1-й блок 5 анализа внешней памяти на магнитном барабане.

В противном случае (т.е. на К+1-м МБ свободного куска памяти требуемого размера нет) содержимое счетчика 1 увеличивается на единицу и производится анализ К- -2-го МБ. Такой поиск повторяется по круговому алгоритму до тех пор, пока не будет найден МБ, на котором есть кусок свободной памяти требуемого размера (если такого вообще нет на данный момент времени, то операционная система через фикси

времени работы устройства, опрашивает выход 46 устройства и выдает отказ заказчику).

При запуске К+1-го (т.е. первого МБ, удовлетворяющего запросу) сигнал

с выхода элемента 9 сравнения через элемент 36 И устанавливает триггер 17 в единичное состояние. По К+1-му входу 45 устройства в регистр 13 заносится код емкости МБ. Триггер 17 разрешает прохождение импульсов с генератора 6 на счетный вход счетчика 14. В результате производится последовательный анализ содержимого регистров 11, в которые по входам 43 устройства заносятся коды размеров свободных кусков памяти МБ. Содержимое i-ru регистра 11 поступает на первый вход элемента 18 сравнения, на второй вход которого поступает содержимое регистра 34 (код размера требуемого куска памяти). Если размер i-ro свободного куска памяти K-tl-ro МБ в i-M регистре 11 равен или превышает требуемы 4 в регистре 34, то на выходе элемента 18 сравнения появляется единичный сигнал, который разрешает поступление содержимого i-ro регистра 11 на первый вход элемента 19 сравнения, на второй вход которого подается содержимое регистра 13.

Как только будет найден первый i-й свободный кусок памяти из i-ro

регистра It, .удовлетворяющий требуемому запросу из регистра 34, на выхо Де элемента 19 сравнения появляется единичный сигнал, показывающий, что содержимое i-ro регистра 11 меньше, чем содержимое регистра 13, поскольку первоначально в регистре 13 записан максимально возможный код - код емкости МБ, При этом сигнал на выходе элемента ИЛИ 33 разрешает запись кода из счетчика 14 в регистр 12; содержимое i-ro регистра 11 записывается в регистр 13.

Затем, начиная с i-«-1-ro куска свободной памяти производится поиск так го 1-го () куска свободной памяти который удовлетворяет требуемому запросу и имеет размер, меньший чем i-ro. Тогда код размера t-ro куска памяти записывается в регистр 13, а в регистр 12 записывается код t из счетчика 14.

.Процесс продолжается до тех пор, пока не будут просмотрены все свободные куски памяти на К+1-м МБ. При вы п олнении указанного условия в регистре 12 хранится код L куска памяти, наиболее подходящего к требуемому запросу. При этом на п-м (прследнем) выходе дешис)ратора 15 появляется еди ничньш сигнал, который через элемент 28 задержки разрептает подачу ко ,да Ь Из регистра 12 на вход дешифратора 16. Тогда разрешается прохождение кода начального адреса Ь-го свободного куска памяти из L-ro регист- ра 10 на выход 47 устройства.

Сигнал с выхода элемента 28 задержки обнуляет триггер 17, регистры 12 и 34. На этом работа устройст- ва заканчивается.

Формула изобретения Устройство для вьделения области

во внешней , содержащее счетчик, дешифратор, блок памяти, элемент И, коммутатор и элемент сравнения, причем установочный вход устройства подключен к установочному входу счетчика, выход которого соединен с входом дешифратора, выход элемента И подключен к счетному входу счетчика, вход задания размера максимального свободного участка внешней памяти устройства соединен с информа- ционным входом блока памяти, выход которого подключен к информационному входу коммутатора, выход которого

соединен с первым входом элемента сравнения, выход дешифратора подключен к управляющему входу коммутатора, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет выделения вычислительным ресурсом комплекса оптимального размера учаска внешней памяти, в него введены генератор импульсов, триггер, регистр, элемент ИЛИ и группа блоков анализа внешней памяти, каждый из которых содержит первую и вторую группы регистров, первый второй регистры, счетчик, первый, второй дешифраторы, триггер, первый, второй элементы сравнения, первую, вторую, третью группы блоков элементов И, первый, второй элементы И, элемент задержки, первую, вторую, третью и четвертую группы элементов ИЛИ, элемент ИЛИ, причем запускающий вход устройства подсоединен к единичному входу триггера, выход которого подключен к первому входу элемента И, второй вход которого подключен к выходу генератора импульсов, вход задания размера требуемой памяти устройства подсоединен к информационному входу регистра, выход которого соединен с вторым входом элемента сравнения и с первым входом первого элемента сравнения каждого блока анализа внешней памяти, выход элемента срав нения подсоединен к нулевому входу триггера, к выходу сигнализации готовности устройства и к первому входу первого элемента И каждого блока анализа внешней памяти, выход генератора импульсов подключен к первому входу второго элемента И каждого блока анализа внешней памяти, К-й выход (, М) дешифратора подключен к второму входу первого элемента И К-го блока анализа внешней Памяти, вход обнуления регистра соединен с выходом элемента ИЛИ, К-й вход которого соединен с выходом элемента задержки К-го блока анализа внешней памяти, в каждом блоке анализа внешней памяти выход первого элемента И соединен с единичным входом триггера, выход которого соединен с вторым входом второго элемента И, выход которого подключен к сче-р Ному входу счетчика, информационный выход i-ro (, n) регистра первой группы соединен с первыми входами элементов И 1-го блока первой группы, информационный выход j-ro (, n) регистра второй группы соединен с первыми вхоами элементов И j-ro блока второй группы, i-й выход первого дешифратора соединен с вторыми входами элемен- тов И i-rc блока первой группы, п-й выход первого дешифратора соединен с входом элемента задержки, выходы элементов И i-ro блока первой группы соединены с i-ми входами элемен тов ИЛИ первой группы, j-й (j 1-, n) выход второго дешифратора соединен с вторыми входами элементов И j-ro блока второй группы,выходы которых соединены с i-ми входами элементов ИЛИ второй группы, выхода которых подсоединены к второму входу первого элемента сравнения, выходы элементов И j-блока второй группы соединены с первыми входами элементов И третьей группы, выход перво- го элемента сравнения соединен с вторыми входами блоков элементов И третьей группы, выходы элементов И j-ro блока третьей группы соединены с j-ми входами элементов ШМ третьей группы, выходы которых соединены с первыми входами элементов И первой группы и с первым входом второго элемента сравнения, выход которого соединен с вторыми входами элементов И первой группы, выходы которых соединены с первыми входами элементов ШШ четвертц#4 группы и с входами элемента ИЛИ, выход которого сое12

-- 1254497б

динен с первыми входами элементов И второй группы, вторые входы которых соединены с информационным выходом счетчика и с входом первого дешифратора, выход элемента задержки соединен с нулевым входом тригге

ра, с входом обнуления первого регистра и с первыми входами элементов И третьей группы, вторые входы и выходы которых соединены соответственно с выходом первого регистра и с входом второго Дешифратора, выходы элементов И первой группы соединены С информационным входом первого Тре- гистра, выходы элементов ИЛИ четвертой группы соединены с информационным входом второго регистра, выход которого соединен с вторым входом второго элемента сравнения, К-й вход начального адреса группы подсоединен к информационным входам регистров первой группы К-го блока анализа внешней памяти, К-й вход размера свободного участка памяти подсоединен к информационному входу регистров второй группы К-го блока анализа внешней памяти, вход общей емкости устройства соединен с вторыми входами элементов ИЛИ четвертой группы каждого блока анализа внешней памяти, выходы элементов ИЛИ первой группы К-го блока анализа внешней памяти соединены с К-ми выходами начального адреса группы устройства.

Редактор И.Касарда

Составитель С.Бурухин

Техред И.Попович Корректор Н.Самборская

Заказ 4722/53 Тираж 671Подписное

ВНШШИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

« 4 J

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1984 |

|

SU1259241A1 |

| Устройство для поиска информации в памяти | 1985 |

|

SU1352494A1 |

| Устройство управления распределением оперативной памяти | 1985 |

|

SU1298754A1 |

| Устройство для управления распределенной вычислительной системой | 1982 |

|

SU1136159A1 |

| Устройство для сопряжения ЦВМ с внешними устройствами | 1989 |

|

SU1784840A1 |

| Устройство для распределения заданий процессорам | 1985 |

|

SU1291983A1 |

| Устройство для тестового контроля цифровых узлов | 1987 |

|

SU1425682A1 |

| Устройство для обмена информации | 1979 |

|

SU962909A2 |

| Устройство для поиска данных | 1990 |

|

SU1795447A1 |

| Устройство для обслуживания запросов | 1987 |

|

SU1437864A1 |

Изобретение относится к вычислительной технике, в частности к устройствам управления внешней памятью. Целью изобретения является расширение функциональных возможностей устройства за счет выделения вычислительным ресурсам комплекса оптимального по размерам участка внешней памяти. Устройство содержит блок памяти, коммутатор, группу блоков анализа внешней памяти, счетчик, дешифратор, генератор импульсов, элемент И, триггер, злемент сравнения. Устройство реализует алгоритм вьщеления вычислительным ресурсам комплекса наиболее подходящего по размерам участка внешней магнитной памяти. 1 ил. (Л С

| Устройство сопряжения | 1976 |

|

SU602934A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения | 1979 |

|

SU881722A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-08-30—Публикация

1985-02-18—Подача