Изобретение отнЬсится к вычислительной технике и может быть исполь- .зовано при вводе информации.

Цель изобретения - повьшение быстродействия устройства,

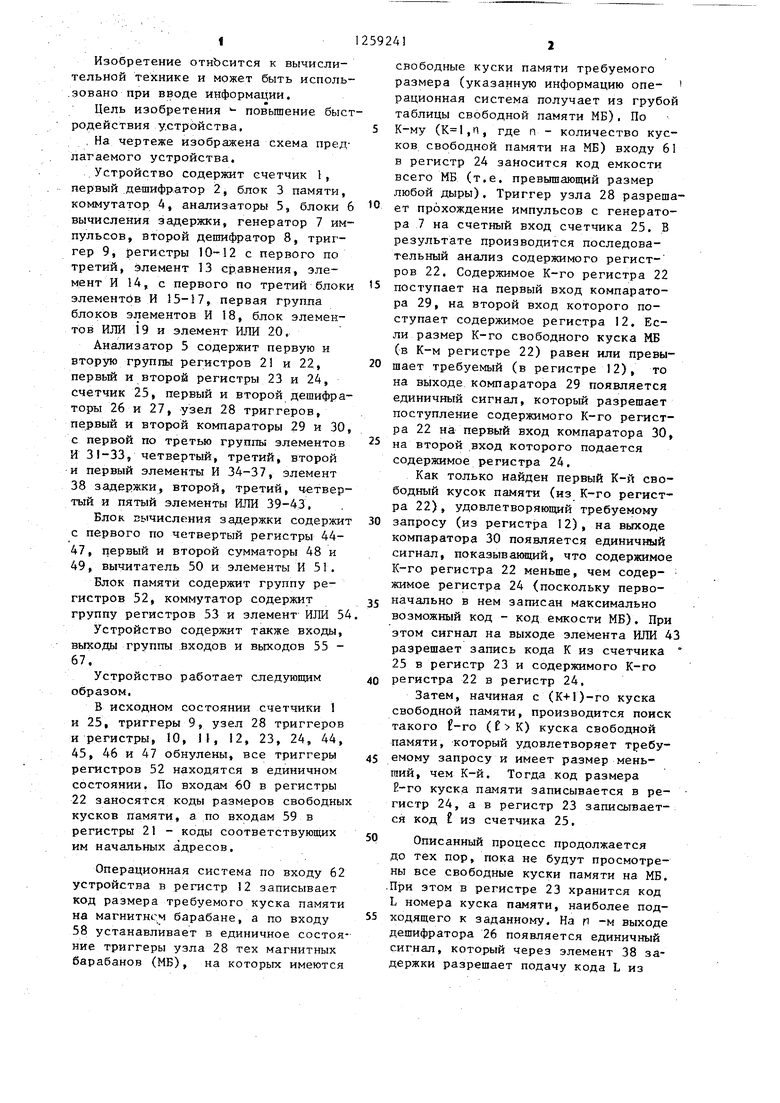

, На чертеже изображена схема предлагаемого устройства.

Устройство содержит счетчик 1, первый дешифратор 2, блок 3 памяти, коммутатор 4, анализаторы 5, блоки 6 вычисления задержки, генератор 7 импульсов, второй дешифратор 8, триггер 9, регистры 10-12 с первого по третий, элемент 13 ср.авнения, элемент И 14, с первого по третий блоки элементов И 55-17, первая группа блоков элементов И 18, блок элементов ИЛИ i9 и элемент ИЛИ 20.

Анализатор 5 содержит первую и вторую группы регистров 2 и 22, первый и второй регистры 23 и 24, счетчик 25, первый и второй дешифраторы 26 и 27, узел 28 триггеров, первый и второй компараторы 29 и 30, с первой по третью группы элементов И 31-33, четвертый, третий, второй и первый элементы И 34-37, элемент 38 задержки, второй, третий, четвертый и пятый элементы ИЛИ 39-43,

Блок вычисления задержки содержит с первого по четвертый регистры 44- 47, первый и второй сумматоры 48 и 49, вычитатель 50 и элементы И 51. Блок памяти содержит группу регистров 52, коммутатор содержит группу регистров 53 и элемент ИЛИ 54

Устройство содержит также входы, выходы группы входов и выходов 55 - 67,

Устройство работает следующим образом,

В исходном состоянии счетчики 1 и 25, триггеры 9, узел 28 триггеров и регистры, 10, 11, 12, 23, 24, 44, 45, 46 и 47 обнулены, все триггеры регистров 52 находятся в единичном состоянии. По входам -60 в регистры 22 заносятся коды размеров свободны кусков памяти, а по входам 59 в регистры 21 - коды соответствующих им начальных адресов.

Операционная система по входу 62 устройства в регистр 12 записывает код размера требуемого куска памяти на магнитнсм барабане, а по входу 58 устанавливает в единичное состояние триггеры узла 28 тех магнитных барабанов (МБ), на которых имеются

5

свободные куски памяти требуемого размера (указанную информацию one- рационная система получает из грубой таблицы свободной памяти МБ), По К-му (,п, где п - количество кусков свободной памяти на МБ) входу 61 в регистр 24 заносится код емкости всего МБ (т.е. превышающий размер любой дыры). Триггер узла 28 разрешает прохождение импульсов с генератора 7 на счетный вход счетчика 25. В результате производится последовательный анализ содержимого регист- ров 22, Содержимое К-го регистра 22 поступает на первый вход компаратора 29, на второй вход которого поступает содержимое регистра 12, Если размер К-го свободного куска МБ (в К-м регистре 22) равен или превы- 0 шает требуемый (в регистре 12), то на выходе компаратора 29 появляется единичный сигнал, который разрешает поступление содержимого К-го регистра 22 на первый вход компаратора 30, на второй вход которого подается содержимое регистра 24.

Как только найден первый K-fi свободный кусок памяти (из К-го регистра 22), удовлетворяющий требуемому запросу (из регистра 12), на выходе компаратора 30 появляется единичный сигнал, показывающий, что содержимое К-го регистра 22 меньше, чем содер- жимое регистра 24 (поскольку первоначально в нем записан максимально возможный код - код емкости МБ). При этом сигнал на выходе элемента ИЛИ 43 разрешает запись кода К из счетчика ° 25 в регистр 23 и содержимого К-го регистра 22 в регистр 24,

Затем, начиная с (K-t-l)-ro куска свободной памяти, производится поиск такого -го (f К) куска свободной памяти, который удовлетворяет требуемому запросу и имеет размер меньший, чем К-й. Тогда код размера Е-го куска памяти записывается в регистр 24, а в регистр 23 записывается код из счетчика 25,

5

0

5

0

5

Описанный процесс продолжается до тех пор, пока не будут просмотрены все свободные куски памяти на МБ. .При этом в регистре 23 хранится код L номера куска памяти, наиболее подходящего к заданному. На п -м выходе дешифратора 26 появляется единичный сигнал, который через элемент 38 задержки разрешает подачу кода L из

регистра 23 на вход дешифратора 27. Тогда разрешается запись кода начального адреса L-ro свободного куска памяти из L-ro регистра 21 в регистр 47 соответствующего блока 6 вычисления задержки. Сигнал с выхода элемента 38 задержки обнуляет триггер узла 28, счетчик 25, регистры 23 и 24 и поступает на выход 67 устройства. Данный сигнал указывает на то, что с i-M МБ найден наиболее подходящий кусок памяти, а его начальный адрес А,, в. качестве результата работы i-ro анализатора 5 памяти на МБ выдается на регистр 47 i-ro блока 6 вычисления задержки.

Операционная система записывает в i-й блок 6 вычисления задержки соответственно по входу 55 в регистр 4 код адреса текущего Ак состояния магнитных головок, по входу 56 в регистр 45 код числа AOI слов, запланированных для записи при вращении МБ от A-ti до А Hi , по входу 57 в регистр 46 код количества слов , которые проходят под магнитными головками при холостом вращении МБ За время записи Ani . Тогда на выходе вы читателя 50 появляется код задержки

М

(АНР ) (ATI +А Ai ) , равный

коду числа слов, которые проходят под магнитными головками МБ при его вращении от An до Ац/ при заданных А( и AJ,; . Таким образом, i-м блоком 6 вычисления задержки экстраполируется относительное время задержки на вращение МБ от адреса AT; до АН с учетом запланированных на зтом промежутке записей (чтений) с i-ro МБ, Код Ajuaj записывается в i-й регистр 52 группы.

Одновременно с запис: ю информации в регистры 44 - 46 по входу 64 устройства триггер 9 устанавливается в единичное состояние, и разрешается прохождение импульсов с генератора 7 на счетный вход счетчика 1. В результате производится последовательный анализ содержимого регистров 52 группы для определения номера МБ, обеспечивающего минимальную задержку записи i arg min lAjoaj . Содержимое i-ro регистра 52 группы поступает на первый вход злемента 13 сравнения, на второй вход которого подается содержимое регистра 10 (куда первоначально по входу 63 уст5 О S

20 5

0

5

0

5 0 5

ройства записывается код - все единицы) .

Как только будет анализироваться i-й регистр- 52 группы с содержимым, отличным от.кода все единицы I ... I , на выходе элемента ИЛИ 20 разрешается запись кода i из счетчика 1 в регистр 11.

Затем начиная с (i+l)-ro МБ производится поиск такого j-ro (j i) МБ, для которого Ajo, Тогда A|i)jy записывается в регистр 10, а в регистр 11 - код j из счет.}1ика 1.

Описанный процесс продолжается до тек пор, пока не будут проанализированы все МБ. При зтом в регистре П хранится код номера МБ, обеспечивающего минимальную задержку начала записи. На (М+1)-м выходе дешифратора 2 появляется сигнал, который разрешает подачу кода 1 из регистра 11 на вход дешифратора 8. При зтс j разрешается выдача на выход 65 устройства кода АН, начального адреса свободного куска памяти на i -м (выбранном) МБ. Этот код сопровождается сигналом на выходе 66 устройства, свидетельствующем об успешном окончании устройства. Этот сигнал.

i также обнуляет счетчик 1, триггер 9, регистры 10 - 12 и 44 - 47, все триггеры регистров 52 группы устанавливает в единичное состояние. На этом работа устройства заканчивается. Таким образом, устройство выделяет начальный адрес наиболее подходящего куска свободной памяти на магнитном барабане, обеспечивающем минималь ную задержку начала записи информации.

В связи с тем, что изобретение сокращает среднее время для вьщеления внешней памяти Т, проведем сравнительный анализ по указанному критерию

Т Ти

где Т.

Tjurf

время поиска наиболее подходящего куска свободной памяти на i-м МБ; время поиска МБ, обеспечивающего минимальную задержку начала записи.

Для предлагаемого устройства (работа анализатора 5) Т„ nt, гдеп - количество свободных кусков МБ; Г - период повторения импульсов с генератора 7, МГ.

Для известного устройства „

/р , Mt,p, где tc 3 3r/4/ - ремя выполнения операций сравнения. Относительный выигрьпп при исполь- овании изобретения составит Т 3 раза.

Таким образом, использование изобретения в вычислительных комплексах позволит сократить время для поиска области памяти в 3 раза,,Это, в свою очередь, приводит к сокращению системных потерь на управление файлами и повышению производительности вычислительных комплексов в целом.

Формула изобретения

1, Устройство для ввода информации, содержащее генератор импульсов, первый дешифратор, счетчик, коммутатор, первую группу блоков элементов И и блок памяти, выходы которого подключены к информационным входам коммутатора, управляющие входы которого соединены с выходами первого дешифратора, выходы счетчика подключены к входам первого дешифратора, выходы . первой группы блоков элементов И являются группой информационных выходов устройства, отличаю ще еся тем, что, с целью повышения быстродействия устройства, в него введены анализаторы, блоки вычисления задержки, второй дешифратор, триггер, три регистра, элемент сравнения, элемент ИЛИ, три блока элементов И, элемент ИЛИ, блок элементов ИЖ, первый установочный вход триггера является первым управляющим входом устройства, выход соединен с первым входом элемента И, второй вход которого объединен с тактовыми входами анализаторов и подключен к выходу генератора импульсов, а выход - к счетному входу счетчика, выход коммутатора соединен с первьм входом элемента сравнения и с первым входом первого блока элементов И, второй вход которого подключен к выходу элемента сравнения, второй вход которого подключен к выходу первого регистра, стробирующий вход которого соединен с выходом блока элементов ИЛИ, одни входы которого являются первой группой управляющих входов устройства, а другие объединены с входами элемента ИЛИ и подключены к выходам первого блока элементов И, .выход элемента ИЛИ соединен с первым

125924 6

входом второго блока элементов И,

5

0

5

0

5

0

5

0

5

второй вход которого подключен к од- ному из выходов счетчика, выходы первого дешифратора соеди 1ены с первым входом третьего блока элементов И, с вторым установочным входом триггера с установочным входом счетчика, со стробируюш 1ми входами первого, второго и третьего регистров, управляющими входами блока памяти, с первыми управляющими входами блоков вычисления задержки, один выход дешифратора явля.ется первым управляющим выходом устройства, выходы второго блока элементов И подключены к информационным входам второго регистра, выходы которого соединены с другими входами третьего блока элементов И, выходы которого подключены к входам второго дешифратора, выходь ко.торого соединены с первыми входами первой группы блоков элементов И, вторые входы которых подюшчены к первым информационным выходам блоков вычисления задержки, вторые информационные выходы которых подключены к информационным входам блока памяти, входы третьего регистра являются информационными входами первой группы устройства, а выходы подключены к информационным входам первой группы анализаторов,, вторые и третьи группы информационных входов анализаторов являются второй и третьей группой информационных входов устройства, первые и вторые управляющие входы анализаторов - второй и третьей группами управляющих входов устройства, первые выходы анализаторов являются группой управлякнцих выходов устройства, первые и вторые выходы анализаторов подключены к вторым и третьим управлякнцим входам блоков вычисления и задержки, информационные , входы группы которых являются информационными входами устройства четвертой группы.

2. Устройство ПОП.1, отличающееся тем, что блок вычисления за,держки содержит четыре регистра, два сумматора, вычитатель, элементы И, информационные входы регистров с первого по четвертый .являются информационными входами группы и третьим управляющим входом блока, стробирующие входы - первым Зтгтравляющим входом блока, а выходы соответственно подключены к первым и вторым входам первого и второго cy tMaTopa, выходы которых соединены с входами вычитателя, выходы которого соединены с одними входами элементов И, выходы которых и выходы четвертого регистра являются вто- рым и первым информационными выхода- Ми блока, а другие входы элементов И являются вторым управляющим входом блока.

3. Устройство по п. 1, о т л и - чающееся тем, что анализатор содержит две группь регистров, два регистра, счетчик, два дешифратора, узел триггеров, два компаратора, три группы элементов И, четыре элемен- та И, элемент задержки, пять элементов ИЛИ, входы первой групгал первого компаратора и входы регистров первой и второй групп являются с первой по третью группами информационных входов анализатора, первые установочные входы узла триггеров и первый вход первого элемента ИЛИ являхзтся первым и вторым управляющими входами .анализатора , первый вход первого элемента И является тактовыми входом анализатора, выход элемента задержки и выход второго элемента ИЛИ являются первым и вторым выходами анализатора, выходы регистров первой группы подключены к одним входам элементов И первой группы, выходы которых подключены к входам второго элемента ИЛИ, выходы первого дещифрато- ра соединены с входами элемента за-, держки и с одними входами элементов И второй группы, выхода элемента задержки подключены к первому входу второго элемента И и к управляющему входу первого регистра, выходы кото- рого соединены с вторь1М входом вторюСоставитель И. Алексеев Редактор О, Юрковецкая Техред Л.Сердюкова Корректор В, Бутяга

Заказ 5121/45Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская иаб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4го элемента И, а информационный вход с выходом третьего элемента И, одни входы которого объединены с входами первого дешифратора и соединены с выходами счетчика, другие объединены с информационными входами второго регистра и подключены к выходу второго элемента ИЛИ, выход узла триггеров соединен с первым входом первого элемента И, выход которого под- ключен к счетному -входу счетчика, установочный вход которого, объединенный с установочным входом узла триггеров, подключен к выходу элемента задержки, выходы второго дешифратора соединены с другими входами элементов И первой группы, входы - с выходом второго элемента И, другие входа элементов И второй группы подключешл к выходам регистров второй группы, выходы - к одним входам элементов И третьей группы и входам третьего элемента ШШ, выхода которого соединены с рторой группой входов пер- |Вого компаратора, выход которого подключен к другим входам элементов И третьей группы, выходы KOTOI«IIX соединеш) с входаю четвертого элемента ИШ, нлход которого подключен к первому входу второго компаратора и к первому входу четвертого элемента И, второй вход которого подключен к выходу кo шapaтopa, а выход соединен с входами пятого апемен- та ШШ и с вторым входом первого элемента ИЛИ, выход которого подключен к угфавляющему входу второго регистра, выход которого соединен с вторым входом второго компаратора, а установочный вход второго регистра соединен с выходом элемента задержки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выделения области во внешней памяти | 1985 |

|

SU1254497A1 |

| Сигнатурный анализатор | 1987 |

|

SU1499349A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Устройство для селекции признаков подвижных объектов | 1989 |

|

SU1691860A1 |

| Процессор для идентификации и адресования событий | 1983 |

|

SU1188748A1 |

| Устройство для определения координат точечных световых объектов | 1988 |

|

SU1589300A1 |

| Устройство для распределения ресурсов памяти в вычислительном комплексе | 1985 |

|

SU1288705A1 |

| Устройство для исследования модели транспортной системы | 1984 |

|

SU1256038A2 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| Устройство для контроля и идентификации пользователя | 1991 |

|

SU1833902A1 |

Изобретение относится к области вычислительной техники и может быть использовано при вводе информации. Цель изобретения - повьппение быстродействия .устройства достигается путем введения в устройство, содержащее счетчик , первый дешифратор 2, блок 3 памяти, коммутатор 4, генератор 7 импульсов и первую группу блоков элементов И 18, анализаторов 5, блоков 6 вычисления задержки, второго дешифратора 8, триггера 9, трех . регистров 10-12, элемента 13 сравнения, элемента И 14, трех блоков элементов И, блока элементов ИЛИ 19, элемента ИЛИ 20 с их связями эа счет сокращения поиска свободной области памяти. 2 з.п. ф-лы, 1 ил. (Л С ьэ ел со to 4;:

| Патент США № 3662378, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Контрольный висячий замок в разъемном футляре | 1922 |

|

SU1972A1 |

| Устройство для ввода информации | 1981 |

|

SU993234A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-23—Публикация

1984-04-01—Подача