t

Изобретение относится к вычислительной технике, в частности к устройствам управления памятью,

Цель изобретения - расширение функционсшьных возмолшостей устройства за счет выделения первой требуемого размера свободной области оперативной памяти.

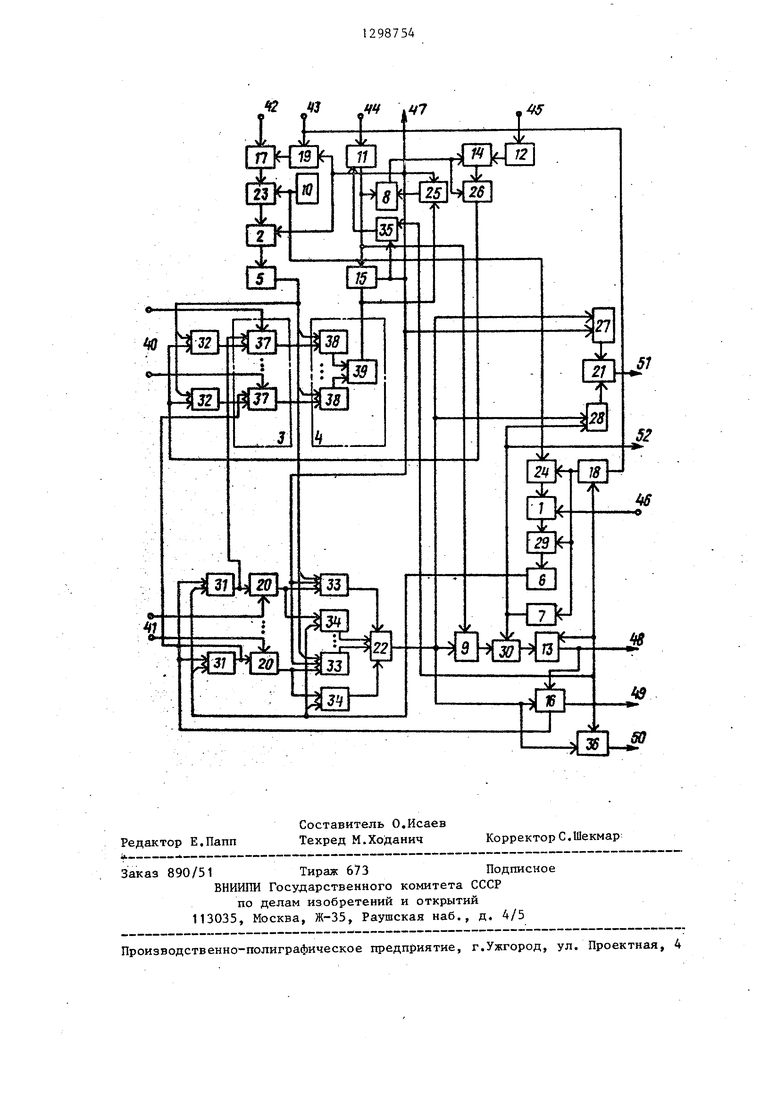

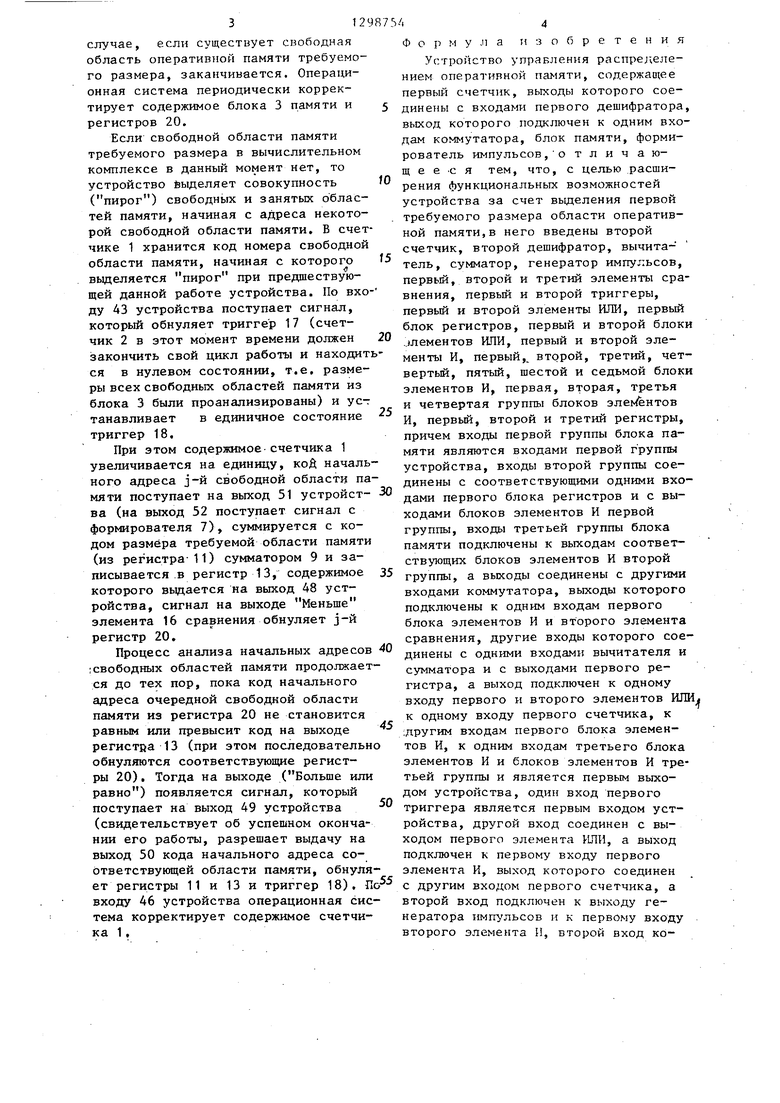

На чертеже представлена схема устройства управления распределением оперативной памяти,

Устройство содержит второй и первый счетчики 1 и 2, блок 3 памяти, коммутатор 4, первый и второй дешифраторы 5 и 6, формирователь 7 импульсов, вычитатель

сумматор

генератор 10 импульсов, первый, второй и третий регистры 11-13, первый, второй и третий элементы - ( сравнения, первый и второй триггеры 17

и 18, первый элемент ИЛИ 19, первый блок регистров 20, первый и второй блоки ИЛИ 21 и 22 элементов, первый и второй элементы И 23 и 24, первый, второй, третий, четвертый, пятый и шестой блоки 25-30 элементов И, первую, вторую, третью и четвертую группы блоков 31-34 элементов PI, второй элемент ИЛИ 35, седьмой блок 36 элементов И, второй блок регистров 37, пятую группу блоков 38 элементов И, третий блок 39 элементов ИЛИ, входы кодов размеров 40 и начальных адресов 41 свободных областей оперативной памяти, установочный вход 42, вход 43 сброса, входы кода требуемого 44 и минимального 45 размера оперативной памяти, входы 46 коррекции, выход 47 сигнала успешного окончания поиска свободной области оперативной памяти, выходы 48 кода начального адреса свободной области памяти после обслуживания запроса на выделение требуемой области, выход 49 сигнала выделения совокупности свободных областей оперативной памяти, выходы кодов начального адреса запрошенной об;лас- ти 50 и выделенной совокупности областей 51 оперативной памяти.

Устройство работает следующим образом.

Оно обеспечивает выделение первой подходящей свободной области оперативной памяти для запроса требуемого размера. Если такой области в данный момент нет, то устройство вьзделяет совокупность (пирог) свободных и

fO

f5

2987542

занятых областей памяти, начиная с адреса некоторой свободной области,

В исходном состояния триггеры 17 и 18, регистры 11 и 13, счетчик 2 5 обнулены, в регистрах 20 хранятся коды начальных адресов свободных кусков оперативной памяти, в регистрах 37 - коды соответствующих им размеров, в регистр 12 хранится код минимальной области .свободной памяти (если остаток свободной оперативной памяти равен или меньше его, то он принимает значение,равное нулю),

Первоначально триггер 17 устанавливается в единичное состояние сигналом по входу 42 устройства, по входу 44 в регистр 11 заносится код размера оперативной памяти, требуемый для выполнения программы в те- кущий момент времени.

При этом ш пульсы с генератора 10 поступают на счётный вход счетчика 2 и разрешается последовательный анализ свободных областей оперативной памяти: код размера i-й (i 1,п) области памяти через коммутатор 4 поступает на второй вход элемента 15 сравнения,на первый вход которого поступает код из регистра 11. Если код размера i-й области памяти превьшает или равен требуемог Еу (из регистра 11), то на выходе элемента 15 сравнения появляется единичный сигнал, обнуля25

30

.ет триггер 17,, регистр 11 и счетчик 2, 35 поступает на выход 47 устройства - (свидетельствует об успешном окончании его работы), разрешает выдачу на выход 50 устройства кода начального адреса i-й выделенной области 40 свободной памяти из i-ro регистра 20 и поступление на вход з еньшаемого вычитателя 8 кода размера i-й вьще- ленной области памяти.

г Вычитатель 8 вычитает из кода i-й выделенной области памяти код требуемой области памяти (из регистра 11), разность поступаем на второй вход элемента 14 сравнения, на первый вход

еп которого поступает код из регистра 12, Если код разности из вычитателя 8 превьш ает или равен коду из регистра 12, то на выходе элемента 14 сравнения появляется сигнал, который разcf решает запись кода разности из вычи- тателя 8 в i-й регистр 37, Если на выходе элемента 14 сравнения сигнал отсутствует, то i-й регистр 37 обнуляется. На этом работа устройства в

3129

случае, если существует свободная область оперативной памяти требуемого размера, заканчивается. Операционная система периодически корректирует содержимое блока 3 памяти и регистров 20.

Если свободной области памяти требуемого размера в вычислительном комплексе в данный момент нет, то устройство выделяет совокупность (пирог) свободных и занятых областей памяти, начиная с адреса некоторой свободной области памяти. В счетчике 1 хранится код номера свободной области памяти, начиная с которого выделяется пирог при предшествующей данной работе устройства. По входу 43 устройства поступает сигнал, который обнуляет триггер 17 (счетчик 2 в этот момент времени должен :закончить свой цикл работы и находиться в нулевом состоянии, т.е. размеры всех свободных областей памяти из блока 3 были проанализированы) и ус-г танавливает в единичное состояние триггер 18,

При этом содержимое счетчика 1 увеличивается на единицу, кой начального адреса j-й свободной области памяти поступает на выход 51 устройст- ва (на выход 52 поступает сигнал с формирователя 7), суммируется с кодом размера требуемой области памяти (из регистра- 11) сумматором 9 и записывается .в регистр 13, содержимое которого выдается на выход 48 устройства, сигнал на выходе Меньше элемента 16 сравнения обнуляет j-й регистр 20.

Процесс анализа начальных адресов ; свободных областей памяти продолжается до тех пор, пока код начального адреса очередной свободной области памяти из регистра 20 не становится равным или превысит код на выходе регистра 13 (при этом последовательно обнуляются соответствую1цие регистры 20), Тогда на выходе (Больше или равно) появляется сигнал, который поступает на выход 49 устройства (свидетельствует об успешном окончании его работы, разрешает выдачу на выход 50 кода начального адреса со- ответствунлцей области памяти, обнуляет регистры 11 и 13 и триггер 18). По входу 46 устройства операционная система корректирует содержимое счетчика 1 .

5

7

5

О 5 0 05

3/.4

Формула изобретения

Устройство управления распределением оперативной памяти, содержап;ее первый счетчик, выходы которого соединены с входами первого дешифратора, выход которого подключен к одним входам коммутатора, блок памяти, формирователь импульсов, О т л и ч а ю- щ е е .с я тем, что, с целью расширения функциональных возможностей устройства за счет выделения первой требуемого размера области оперативной памяти,в него введены второй счетчик, второй дешифратор, вычита- тель, сумматор, генератор импу.чьсов, первый, второй и третий элементы сравнения, первый и второй триггеры, первый и второй элементы ИЛИ, первый блок регистров, первый и второй блоки ..шементов ИЛИ, первый и второй элементы И, первый,, второй, третий, чет- вертьй, пятый, шестой и седьмой блоки элементов И, первая, вторая, третья и четвертая группы блоков элеь ентов И, первьш, второй и третий регистры, причем входы первой группы блока памяти являются входами первой группы устройства, входы второй группы соединены с соответствующими одними входами первого блока регистров и с выходами блоков элементов И первой группы, входь третьей группы блока памяти подключены к выходам соответствующих блоков элементов И второй группы, а выходы соединены с другими входами коммутатора, выходы которого подключены к одним входам первого блока элементов И и второго элемента сравнения, другие входы которого соединены с одними входами вычитателя и сумматора и с выходами первого регистра, а выход подключен к одному входу первого и второго элементов ИЛИ к одному входу первого счетчика, к ;другим входам первого блока элементов И, к одним входам третьего блока элементов И и блоков элементов И третьей группы и является первым выходом устройства, один вход первого триггера является первым входом устройства, другой вход соединен с выходом первого элемента ВДИ, а выход подключен к первому входу первого элемента И, выход которого соединен с другим входом первого счетчика, а второй вход подключен к выходу генератора импульсов и к первому входу . второго элемента И, второй вход которого соединен с теля импульсов, с

входом формнрова- одними входами пятого блтка элементов И и с выходом второго триггера, один вход которого подключен к другому входу первого элемента ИЛИ и является вторым входом устройства, а другой вход соединен с другим входом второго элемента ИЛИ, с одним входом третьего регистра, с одними входами седьмого блока элементов И, выходом третьего элемента сравнения и является вторым вькодом -устройства, один вход второго счетчика подключен к выходу второго элемента И, другой вход является третьим входом устройства, а выходы соединены с другими входами пятого блока элементов И, выходы которого подключены к входам второго

соединены с другими входами третьего регистра, одни входы блоков элементов И второй группы подключены к дру гим входам соответствующих блоков и

5 третьей группы и к выходам первого дешифратора, а другие входы подключены к выходам второго блока элементов И, одни входы которого соединены с одними входами первого элемента

Ю сравнения и с выходами вычитателя, а другие входы подключены к выходам первого элемента сравнения, другие входы которого соединены с выходами второго регистра, другие входы вы15 читателя подключены к выходам первого блока элементов И, входы первой и второй группы первого блока элемен тов ИЛИ соединены соответственно с выходами третьего и четвертого блодешифратора, выходы которого соедине- 20 ков элементов И, а выходы являются ны с одними входами блоков элемен- выходами третьей группы устройства.

тов И четвертой и первой групп, другие входы последних подключены к выходу третьего элемента сравнения, одни входы которого соединены с выхода ми третьего регистра и являются выходами первой группы устройства, а другие входы подключены к другим входам третьего, четвертого и седьмого блоков элементов И, к выходам второго блока элементов ИЛИ и к другим входам сумматора, выходы которого соединены с одними входами шестого блока элементов И, другие входы ко-

торого подключены к одним входам чет- 35 гистра и выходы седьмого блока элё- вертого блока элементов И, выходу ментов И являются соответственно формирователя импульсов и является входами четвертой группы и выходами

третьим выходом устройства, а выходы

соединены с другими входами третьего регистра, одни входы блоков элементов И второй группы подключены к другим входам соответствующих блоков и

третьей группы и к выходам первого дешифратора, а другие входы подключены к выходам второго блока элементов И, одни входы которого соединены с одними входами первого элемента

сравнения и с выходами вычитателя, а другие входы подключены к выходам первого элемента сравнения, другие входы которого соединены с выходами второго регистра, другие входы вычитателя подключены к выходам первого блока элементов И, входы первой и второй группы первого блока элементов ИЛИ соединены соответственно с выходами третьего и четвертого бло

третьи входы блоков элементов И третьей группы подключены к другим входам блоков элементов И четвертой группы 25 и к выходам первого блока регистров, другие входы которого являются входами второй группы устройства, входы второго блока элементов ИЛИ соединены с вь ходами блоков элементов И тре- 30 тьей и четвертой групп, выход второго элемента ИЛИ подключен к одному входу первого регистра, другие входы которого являются входами третьей группы устройства, входы второго ревторой группы устройства.

ffr

51

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поиска координат точки экстремума функции двух переменных | 1981 |

|

SU966703A1 |

| Устройство для ввода информации | 1984 |

|

SU1259241A1 |

| Устройство для оценки степени оптимальности размещения в многопроцессорных кубических циклических системах при направленной передаче информации | 2017 |

|

RU2727555C2 |

| Устройство для реализации безызбыточного алгоритма быстрого преобразования Фурье | 1981 |

|

SU1056206A1 |

| Дифференцирующе-сглаживающее устройство | 1975 |

|

SU610115A1 |

| УСТРОЙСТВО АНАЛИЗА ПЕРЕКРЫТИЙ КАНАЛОВ ПРИ РАЗМЕЩЕНИИ ПАРАЛЛЕЛЬНЫХ ПОДПРОГРАММ В МНОГОПРОЦЕССОРНЫХ СИСТЕМАХ | 2011 |

|

RU2460126C1 |

| Анализатор спектров | 1982 |

|

SU1023341A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ И КОРРЕКЦИИ АНОМАЛЬНЫХ ЦИФРОВЫХ ОШИБОК ПРИ ПЕРЕДАЧЕ РЕЧИ МЕТОДОМ ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИИ | 1999 |

|

RU2159470C1 |

| Устройство для спектрального анализа с постоянным относительным разрешением | 1982 |

|

SU1109760A1 |

| Система сбора и обработки информации | 1983 |

|

SU1108432A1 |

Изобретение относится к вычислительной технике, в частности к устройствам управления памятью. Целью изобретения является расширение функциональных возможностей устройства за -счет выделения первой требуемого размера свободной области оперативной памяти. Устройство содержит первый и второй счетчики, блок памяти, коммутатор, первый и второй дешифраторы, сумматор, вычислитель, генератор импульсов, первый, второй и третий регистры, элементы ИЛИ, элементы И, блоки элементов И, группы блоков элементов И, блок регистров, блоки элементов ИЛИ. Использование изобретения позволяет сократить время выделения оперативной памяти по сравнению с программной реализацией соответствующего процесса. 1 ил.

Редактор E.Папп

Составитель О.Исаев Техред М.Ходанич

Заказ 890/51 Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035 Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4

Корректор С.Шекмар

Авторы

Даты

1987-03-23—Публикация

1985-03-12—Подача