(54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения абонентов с каналами связи | 1985 |

|

SU1262510A1 |

| Устройство для сопряжения | 1983 |

|

SU1104498A1 |

| Устройство для сопряжения | 1990 |

|

SU1835546A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1984 |

|

SU1200271A1 |

| Устройство для сопряжения | 1985 |

|

SU1259275A1 |

| Устройство для сопряжения источника и приемника информации | 1984 |

|

SU1166125A1 |

| Устройство для ввода информации | 1988 |

|

SU1536368A1 |

| Устройство для сопряжения | 1977 |

|

SU746488A1 |

| Устройство для сопряжения источника и приемника информации | 1985 |

|

SU1309032A1 |

| Устройство для сопряжения двух асинхронных магистралей | 1986 |

|

SU1403083A1 |

Г

Изобретение относится к автоматике и вычислительной технике и может быть использовано для сопряжения двух разноскоростных устройств обработки данных.

Известны устройства для; сопряжения, содержащие буферную память на регистрах, входной и выходной коммутаторы, распределители ввода и выводы информации, регистр меток, сумматор, две схемы сравнения, два регистра констант и узел управления til .

Недостатком этих устройств является их сложность и большие аппаратурные затраты.

Наиболее близким к изобретению по сущности технического решения является устройство для сопряжения, содержащее буферную память, информационные входы которой являются информационнымы входами устройства, управляющий вход через элемент за1держки записи подключен к управляющему входу записи устройства, первому входу

триггера, входу счетчика записи и первому счетному входу реверсивного счетчика, второй счетный вход-которого соединен со входом счетчика считывания, управляющим входом считывания, вторым входом триггера и через элемент задержки считывания с управлякицим входом выходного коммутатора, выходы которого являются информационными выходами устройства, а

10 входы - соединены с информационными выходами буферной памяти, адресный вход которой подключен к выходу адресного коммутатора, первый и второй входы которого соединены соот15ветственно с выходами счетчика записи и счетчика считывания, управляющие входы - с соответствующими выходами триггера, а вход блокировки.с выходом дешифратора нуля, входом

20 подключенного к выходу реверсивного счетчика C2j.

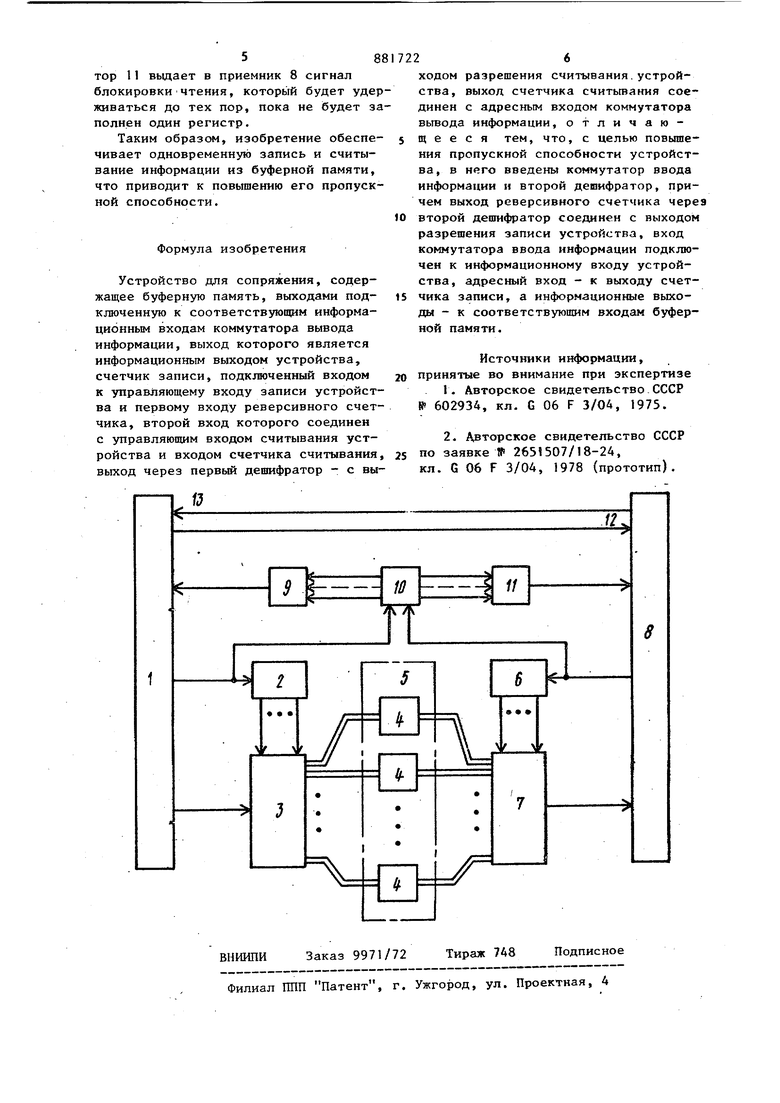

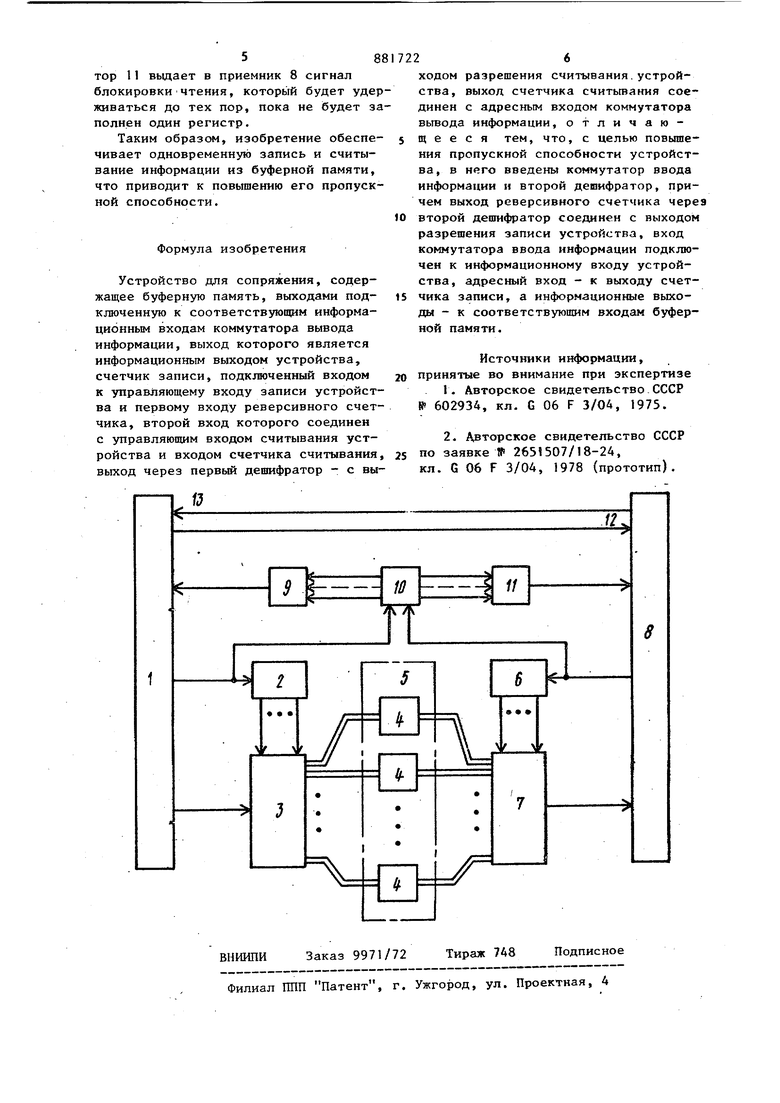

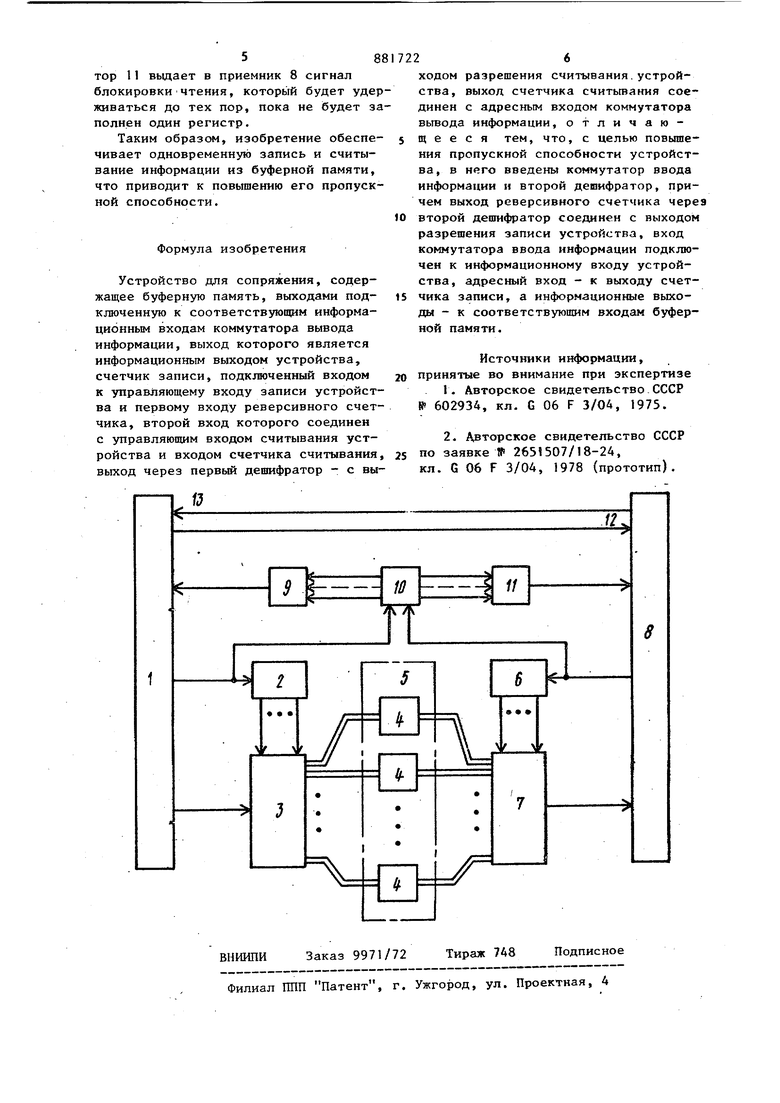

Недостаток данного устройства состоит в низкой пропускной способное3ти, что обусловлено невозможноетьк одновременной эапиёи и считывания буферной памяти. Цель изобретения - повышение пропускной способности устройства. Поставленна-я цель достигается тем что в устройство, содержащее буферную память, выходами подключенную к соотв-етствугощим информационным входам коммутатора вывода информации, выход которого является информационным выходом устройства, счетчик записи, подключенный входом к управляющему входу записи устройства и первому входу реверсивного счетчика второйВХОД которого, соединен с управляющим входом считывания устройства и входом счетчика считывания, а выход через первый дешифратор г с вы ходом разрешения считывания устройства, выход счетчика считывания соединен с адресным входом коммутатора вывода информации, введены коммутато ввода информации и второй дешифратор причем выход реверсивного счетчика через второй дешифратор соединен с выходом разрешения записи устройства, вход коммутатора ввода информации подключен к информационному вход устройства, адресный вход - к выходу счетчика записи, а информационные выходы - к соответствующим входам бу ферной памяти, На чертеже представлена блок-схема устройства. Устройство содержит источник 1 информации, счётчик 2 записи, коммутатор 3 ввода информации, регистры 4 буферной памяти 5, счетчик 6 считывания , коммутатор 7 вывода информации, приемник 8 информации, второй дешифратор 9, реверсивный счетчик 10, первый дешифратор 11, вход 12 пр емника 8, вход 13 источника . Устройство работает следугошлм об разом. Перед процессом передачи последовательности дискретных сигналов источник 1 посылает сигнал Запрос на прием на вход 12 приемника 8. При.11 емник 8 на данный сигнал выдает на вход 13 источника 1 сигнал Готов к приему. После этого источник 1 генерирует последовательность кодов которые поступают на вход коммутато ра 3, Одновременно каждый сигнал по следовательности сопровождает синхроимпульс, который jiocTynaeT на счетчик 2, выдающий адреса для подк 2 чения входа коммутатора 3 к соответствующему регистру А буферной памяти 5. Одновременно эти синхроимпульсы поступают на вход -И реверсивного счетчика. fO. Емкость реверсивного счетчика 10 соответствует количеству регистров 4 буферной памяти 5. Реверсивный счетчик 10 имеет параллельные выходы (от каждого разряда), которые подключены к соответствующим входам дешифраторов 9 и 11. Одновременно с записью первого сигна,па последовательности, т.е. с появлением первого синхроимпульса, «а выходе дешифратора I1 формируется сигнал Информация записывается в буферную память, который разрешает считывание информации приемнику 8. С появлением на управляющем входе записи импульсов считывания счетчик вьщает адрес на коммутатор 7, который подключает выход соответствующего регистра А на вход приемника 8 дискретных сигналов синхронно с импульсами считывания. Счетчик 6 совместно с коммутатором 7 работает таким образом, что считывание сигналов происходит аналогично их порядку записи. Одновременно импульсы поступают на вход -1 |зеверсивного счетчика 10, так что каждый из этих импульсов уменьшает содержимое реверсивного счетчика на один импульс. Таким образом, в процессе записи и считывания в реверсивном счетчике 10 хранится количество импульсов, равное количеству регистров А памяти 5, в которых хранится еще несчитанная информация. Так как запись и считывание происходит с различной скоростью, то Может оказаться, что в буферной памяти 5 не останется свободного регистра для записи последующего кода. Этот момент определяется дешифратором 9, который вырабатывает сигнал блокировки записи, который поступает на соответствующий вход источника 1 и запрещает вьщачу кодов на вход коммутатора 3 и соответствующих синхроимпульсов записи. После освобождения хотя бы одого регистра А дешифратор 9 снимает сигнал блокировки, и запись будет продолжена в свободные регистры, т.е. в регистры, информация в которых была прочитана. Если считывание будет происходить быстрее записи, то при нулевом состоянии реверсивного счетчика 10 дешифра58тор 11 выдает в приемник 8 сигнал блокировкичтения, который будет удер живаться до тех пор, пока не будет за полнен один регистр. Таким образом, изобретение обеспечивает одновременнук) запись и считывание информации из буферной памяти, что приводит к повышению его пропускной способности. Формула изобретения Устройство для сопряжения, содержащее буферную память, выходами подключенную к соответствующим информационным входам коммутатора вывода информации, выход которого является информационным выходом устройства, счетчик записи, подключенный входом к управляющему входу записи устройства и первому входу реверсивного счетчика, второй вход которого соединен с управляюпдам входом считывания устройства и входом счетчика считывания выход через первый дешифратор - с вы6ходом разрешения считывания.устройства, выход счетчика считывания соединен с адресным входом коммутатора вьгеода информации, отличающ е е с я тем, что, с целью повьппения пропускной способности устройства, в него введены коммутатор ввода информации и второй дешифратор, причем выход реверсивного счетчика череэ второй дешифратор соединен с выходом разрешения записи устройства, вход коммутатора ввода информации подключен к информационному входу устройства, адресный вход - к выходу счетчика записи, а информационные выходы - к соответствующим входам буферной памяти. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство.СССР № 602934, кл. G 06 F 3/04, 1975. 2.Авторское свидетельство СССР по заявке № 2651507/18-24, кл. G 06 F 3/04, 1978 (прототип).

Авторы

Даты

1981-11-15—Публикация

1979-01-19—Подача