Изобретение относится к измерительной технике и. может быть использовано в различных областях радиоэлектроники для регулировки фазы сигналов .5

Цель изобретения - повышение точ- ности установки фазы сигнала в широком диапазоне.

На чертеже приведена схема предлагаемого устройства.10

Цифровой фазорегулятор содержит блок 1 опорных частот, п смесителей 2.2-2,п, п формирователей 3.1-З.п, триггерных делителей 4.1-4.П частоты, фильтры 5 и 6, блок 7 установ- 15 ки делителей частоты, состоящий из инверторов 8.1-8.k, первой группы 9,I-9.k элементов 2 И-НЕ и второй группы lO.l-1-O.k элементов 2 И-НЕ.

Выходы блока 1 опорных частот 20 соединены с гетеродинными входами смесителей 2,1, 2.2,...,2.п, выход каждого из которых через формирователи 3.1, 3.2,...,3п подключен к входу соответствующего триггера триггер- 25 ного делителя 4.1, 4.4,..., 4.п частоты, выход каждого из триггерных делителей 4.1, 4.2,..., 4.(п-) частоты подключен к входу смесителя 2,2, 2.3,..., 2.П соответственно, один из 30 вькодо блока 1 опорных частот и выход триггерного делителя 4.п частоты соединены соответственно с первым и вторым фильтрами 5 и 6. Триггерные делители 4 частоты выполнены на D- триггерах, количество которых определяется выбранным коэффициентом деления каждого из делителей. R- и S- входы каждого из D-триггеров триггерных делителей частоты подключены к выходам блока 7 установки делителей частоты. Выходы элементов 2 И-НЕ первой и второй групп 9 и 10 являются выходами блока 7 установки делителей частоты. Устройство работает следующим образом.

35

40

55

45

от

Сигнал частотой f, , когерентный с опорной частотой f , поступает на смеситель 2.1, на гетеро дин ный вход которого поступает сигнал f блока 1 опорных частот. Значение гетеродинного Сигнала выбирается такой величины, чтобы на выходе смесителя 2.1 выделялся сигнал с частотой где 1, - коэффициент деления первого делителя 4.1. Гармонический сигнал с выхода смесителя 2,1 поступает на вход формирователя 3.1, в кото- |ром он преобразуется в последовательность прямоугольных импульсов той же частоты, и далее на вход .делителя 4.1 частоты. Последний представляет собой двоичный счетчик, коэффициент деления его Е 2 где т - число разрядов делителя частоты. На выходе делителя 4.1 частоты образуется сигнал, фаза которого по отношению к фазе входного сигнала изменяется на величину

U) -t IJ1

uV -la-- J - N,

(

Зел,

где У - начальная фаза;

Ч - фазовый сдвиг, создаваемый в смесителе 2.1; f - фазовый сдвиг, создаваемый делителем 4.1,

ц

Ч:И1

Ч

noct

ч

2ТГЫЧ

Зел-,

-.

PQKC

1

Ч-макс т, 0,1,2... 1,

,

N где

- двоичный код; - разрядный код, который при- нимает значения 0,1,2,..., 2 - 1.

Фазовый сдвиг, создаваемый делителем 4.1, изменяется в соответст202530

35

50

вии с кодом N

Ч

в моменты времени.

40

определяемые час тотой иI fflyльcнoй последовательности t.T.e. производятся установка каждоЬо из разрядов де- .гштеля 4.1 частоты в О и 1 и таким образом запись числа N,. в счетчик, а фаза вьгходного сигнала с делителя. 4.1 сдвигается на величину У. Делитель 4.1 частоты управляет блоком 7 установки делителей частоты. При поступлении О в первом разряде кода N на первый вход элемента 9.1 2И-НЕ nocTjTiaeT проинвертирован- -1ый через инвертор 8.1 сигнал, а на входе элемента 10.1 2И-НЕ действует прямой сигнал. По импульсу установки делителя . на выходах элементов 9.1 и 10.1 устанавливаются .состояния 1 и О, которые соответствуют 1 первого разряда делителя 4,1. При поступлении 1 в коде первого разряда N на выходах элементов 9.1 и 10.1 устанавливается состояние, соответствующее 1 пер- 55 вого разряда делителя 4.1. Аналогично происходит работа по всем остальным разрядам блока 7 установки делителей частоты.

45

После делителя 4.1 частоты сигнал проходит через последовательно соединенные смеситель 2,2, формирователь 3.2 и делитель 4.2 частоты, в которых частота повышается до величины fg1 (где fj - коэффициент де ления второго делителя частоты в смесителе 2.2), затем формируется последовательность прямоугольных им пульсов в формирователе 3.2 и произ водится установка фазы в делителе 4.2 частоты. Установка фазы во втором делителе 4.2 частоты производит ся также, как и в делителе 4.1, отличие может заключаться только в коэффициенте деления второго делите ля 4.2 частоты. Управление вторым делителем 4.2 частоты производится от блока 7 установки делителей час тоты по тому же принципу, что и управление первым делителем 4,1. Аналогично производится преобразование сигнала и установка фазового сдвиd4 4 + h nocTb,

7TT( n,

пределах от

до

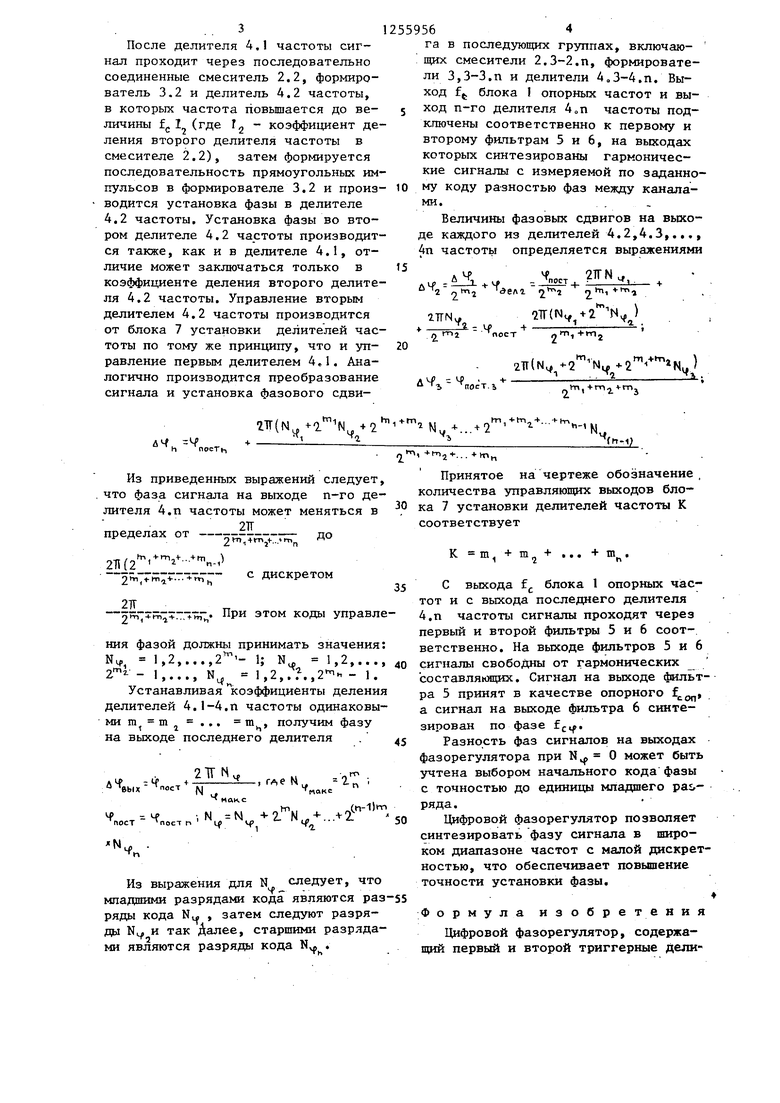

Из приведенных выражений следует, что фаза сигнала на выходе п-го делителя 4.П частоты может меняться в

2ТГ

,

2Т1( дискретом

2

-2 К7-г;,---рц-. При этом коды управления фазой должны принимать значения: N, 1,2,..., 1; N 1,2,..., 2 - 1,..., N 1,2,.., - 1.

Устанавливая коэффициенты деления делителей 4.1-4.П частоты одинаковыми т m

m , получим фазу

на выходе последнего делителя 2irN

д 10

вЫХ пост |у|

:,глеМ -г

пакс

.

-.N.rj -г-N -..л пост г IfIf

N.

Из выражения для N следует, что младшими разрядами кода являются разряды кода NI , затем следуют разряды N и так Далее, старшими разрядами являются разряды кода N .

2559564

га в последующих группах, включаю- щих смесители 2.3-2.П, формирователи 3,3-З.п и делители 4„3-4.п. Выход fj, блока I опорных частот и вы- 5 ход п-го делителя 4„п частоты под- кгпочены соответственно к первому и второму фштьтрам 5 и 6, на выходах которых синтезированы гармонические сигналы с измеряемой по заданно10 му коду разностью фаз между каналами.

Величины фазовых сдвигов на выходе каждого из делителей 4.2,4.3,..., 4п частоты определяется выражениями

ITTNv

nocT

2TrN

йелг , « Ti, 21T(N, +

.

jITI, -t-nij

21T(N .) 1 - . ,

4n,+nn,

-m.

...+ 2 - - N

4fT-i)

0, +(2-1-... +1т(„ - .

Принятое на чертеже обозначение, количества управляюпщх выходов бло- 30 ка 7 установки делителей частоты К соответствует

К

т, + т +

+ т

С выхода f блока 1 опорных частот и с выхода последнего делителя 4.П частоты сигналы проходят через первый и второй фильтры 5 и 6 соответственно. На выходе фильтров 5 и 6

сигналы свободны от гармонических

составляющих. Сигнал на выходе фильтра 5 принят в качестве опорного fj.o а сигнал на выходе фильтра 6 синтезирован по фазе ffip.

Разность фаз сигналов на выходах фазорегулятора при N, О может быть учтена выбором начального кода фазы с точностью до единицы младшего раь- ряда.

Цифровой фазорегулятор позволяет синтезировать фазу сигнала в широком диапазоне частот с малой дискретностью, что обеспечивает повьвпение точности установки фазы.

Формула изобретения

Цифровой фазорегулятор, содержащий первый и второй триггерные дели1255956

тели частоты, первый формирователь, первый и второй фильтры„ о т л и - ч а.ю щ и и с я тем, что, с целью повьшения точности установки фазы сигнала независимо от его частоты, он снабжен блоком опорных частот,, п смесителями, (п-2) триггерныии делителями частоты ,(п-) формирователями и блоком установки делителей частоты, состоящим из k инверторов .и двух групп по k элементов 2Й-НЕ в каждой, где k - разрядность кода установки фазы, при этом выход первого смесителя через последовательно соединенные первый формирователь, первьш триггерный делитель частоты, второй смеситель, второй формирователь , второй триггерный делитель частоты и далее .в той же последовательности до п-го триггерного делителя частоты соединен с входом второго iJftmbTpa, гетеродиннь е входы каждого из п смесителей подсоединены соответственно к одному Из и ( с первоРедактор О.Бугир

Составитель А.Старостина Техред М.Ходаннч

Заказ 4818/45 Тираж 728

ВНШШИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

го по п-й) выходам блока опорных час-ь тот, (п+1)-й выход которого соеди- ; ней с входом первого фильтра, уста- HOBO4Hbie R-входы каждого триггера триггерных делителей частоты соединены поразрядно с выходами соответствующих элементов 2И-НЕ первой блока установки делителей частоты, первые входы которых через

инвертор этого блока соединены с соответствующими разрядными клеммами установки фазового сдвига, а установочные S-входы каждого триггера триггерных делителей частоты соединены

поразрядно с выходами соответствую- щш элементов 2И-НЕ второй группы блока установки делителей частоты, первые входы которых также соединены с соответствующими разрядными

клеммами установки фазового сдвига, при этом вторые входы элементов 2И-НЕ первой и второй групп блока установки делителей частоты объединенны и. соединены с клеммой тактового сигнала.

Корректор М.Самборская Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| СТАНЦИЯ ПРИЦЕЛЬНЫХ ПОМЕХ РАДИОЛИНИЯМ УПРАВЛЕНИЯ ВЗРЫВНЫМИ УСТРОЙСТВАМИ | 2005 |

|

RU2292059C1 |

| СИСТЕМА ПЕРЕДАЧИ ДАННЫХ С МНОЖЕСТВЕННЫМ ДОСТУПОМ И ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ | 2003 |

|

RU2240653C1 |

| Формирователь сложного сигнала с частотной и частотно-фазовой манипуляцией | 1982 |

|

SU1136323A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ ПОСЛЕДОВАТЕЛЬНОГО ОБЗОРА ПО ДАЛЬНОСТИ С ПЕРЕСТРОЙКОЙ ПО ЛИНЕЙНОМУ ЗАКОНУ ДЛИТЕЛЬНОСТИ ЗОНДИРУЮЩИХ ФАЗОМАНИПУЛИРОВАННЫХ РАДИОИМПУЛЬСОВ | 2009 |

|

RU2405170C1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ С ЗОНДИРОВАНИЕМ ПРОСТРАНСТВА ФАЗОМАНИПУЛИРОВАННЫМИ СИГНАЛАМИ С ПЕРЕСТРОЙКОЙ ДЛИТЕЛЬНОСТИ ПАРЦИАЛЬНЫХ РАДИОИМПУЛЬСОВ ПО ЛИНЕЙНОМУ ЗАКОНУ | 2009 |

|

RU2405169C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| ПРОТИВОУГОННОЕ УСТРОЙСТВО ДЛЯ ТРАНСПОРТНОГО СРЕДСТВА | 1991 |

|

RU2006394C1 |

| ШИРОКОПОЛОСНЫЙ СИНТЕЗАТОР ЧАСТОТ | 2011 |

|

RU2450418C1 |

| Синтезатор частот | 1988 |

|

SU1656680A1 |

| СПОСОБ ОБНАРУЖЕНИЯ ДЕФЕКТОВ В ТРУБОПРОВОДАХ, ПРЕИМУЩЕСТВЕННО КОРРОЗИОННЫХ ДЕФЕКТОВ В ТРУБОПРОВОДАХ ВОДОСНАБЖЕНИЯ | 2002 |

|

RU2229708C2 |

Изобретение относится к измерительной технике. Может быть использовано в различных областях радиоэлектроники для регулировки фазы сигналов. Целью изобретения является повышение точности установки фазы сигнала в широком диапазоне. В устройство, содержащее два триггерных делителя частоты 4.п-1, 4.п, формирователь З.п, фильтры 5,6, для достижения цели дополнительно введены блок 1 опорных частот, п смесителей 2.2-2.п, (п-2) триггерных делителей частоты 4.1-4.П - 2,(п-1) формирователей 3.1-З.П-1, блок 7 установки делителей частоты, состоящих из инверторов 8.1-8.k, -групп 9.1-9.k и 10.1-10.k элементов 2И-НЕ. Разность фаз сигналов на выходах фазорегулятора может быть учтена выбором начального кода фазы с точностью до единицы младшего разряда, Устройство позволяет синтезировать фазу сигнала в широком диапазоне частот с малой дискретностью, что обеспечивает повышение точности установки фазы. 1 ил. -§ (Л

| Устройство дискретного изменения разности фаз сигналов | 1973 |

|

SU464863A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Дискретное фазозадающее устройство | 1980 |

|

SU911366A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-09-07—Публикация

1985-03-18—Подача