Изобретение относится к способам и устройствам для передачи и приема сигналов, имеющих заданные спектры и границы времени действия. В части передачи сигнала изобретение относится к способам и устройствам преобразования сигналов, представляемых непрерывными функциями, или дискретными последовательностями импульсов, или последовательностями двоичных чисел, в последовательности волновых пакетов (ВП), формируемых в средах без дисперсии, т.е. с линейной зависимостью фазы от частоты, дополнительно кодированными посредством изменяемых параметров группами импульсов (группами двоичных чисел). В части приема сигнала изобретение относится к способам и устройствам фильтрации принимаемых сигналов волновыми пакетами (ВП) и декодирования отфильтрованных сигналов для получения исходных непрерывных функций, или дискретных последовательностей импульсов, или последовательностей двоичных чисел.

Сигналы типа волновых пакетов (ВП) с конечной шириной спектра, определяемой граничными точками, задают действиями образующих их полей на датчик, например на приемную антенну, усилитель и т.п. В радиотехнике и электротехнике действие элементарного ВП формируют в виде реакций идеальных фильтров на сигнал дельта импульса, у которых полоса пропускания равна спектральной ширине ВП. Термин «действие волнового пакета» (ДВП) применяется при описании формы сигналов посредством синтеза и понимается как элемент, оказывающий воздействие, т.е. при построении модуляторов, а термин «импульсная реакция идеального фильтра» (ИР ИФ) используется для описания выделения сигналов в виде реакции на оказанное воздействие, т.е. при построении фильтров. Понятие элемент в применении к ВП базируется на том, что, будучи единожды созданы устройством (передатчиком), они существуют независимо и существуют до тех пор, пока не окажут воздействие на приемный элемент, произведя своим воздействием работу. Таким образом, в данной заявке ДВП -это реально существующий объект, а ИР ИФ - это виртуальное образование, возникающее при построении фильтров.

Подобные ВП со спектром от 0 до ω, действия которых эквивалентны импульсным реакциям (ИР) идеальных однокомпонентных фильтров (ИОФ) с шириной полосы ω, определяются как

F(t)=sin(ω·t)/(ω·t), где ω - угловая частота.

Они широко описаны в литературе по математике, физике, электротехнике, радиотехнике и т.д. Формирование ДВП осуществляют из значений F(t), взятых в точках дискретизации. Но из-за медленного их затухания во времени относительно периода частоты ω, и в связи с этим большого количества точек дискретизации, реализация вышеуказанных действий ВП затруднительна.

Известны способ и устройство по патенту US 4558454, кл. Н 04 L 25/24, 10.12.1985, в которых цифровыми методами осуществляется формирование сигнала представляющего собой две последовательные по времени и противоположные по знаку дублетные импульсные реакции ИФ. Дублетная импульсная реакция ИФ обеспечивает существенно более быстрое затухание значений токов или напряжений во времени, чем в случае ИР ИФ. Ограниченность действия таких ВП во времени позволяет осуществлять сопряжение цифровых информационных потоков с каналами среды переноса. Недостатком является отсутствие вторичных методов кодирования, формирование только одного канала передачи, который начинается с нулевой частоты, хотя сама нулевая частота отсутствует, и все-таки большое время затухания токов или напряжений во времени. Данный способ не позволяет формировать ВП с широкими спектрами из-за трудностей с цифровой обработкой больших объемов информации, вызванных временем существования данных ВП, что ограничивает его информационную емкость. Данный способ формирования не позволяет также формировать ВП с высокочастотными спектрами, так как предложенный цифровой модулятор обладает тем же недостатком. И, наконец, пропускная способность канала, сформированного этим способом, ограничена шириной формируемого ВП, так как данный ВП имеет бинарный характер без группового кодирования, а удвоение спектра, вызванное его цифровым переносом, ничем не скомпенсировано.

Известны способ и устройство по патенту RU 2160509, кл. Н 04 L 27/34, 10.12.2000, в которых предложено использовать для формирования сигнала методы дискретизации спектров определенной формы. Спектр сигнала данного патента эквивалентен спектру сигнала предложенного в предыдущем патенте, а значит данный сигнал, несмотря на оригинальный способ формирования, также представим в виде дублетных импульсных реакций (ДИР) ИФ. При этом для повышения скорости передачи информации, используются вариации величины задержки относительно друг друга ИР ИФ внутри ДИР ИФ между ее парафазными амплитудами. Недостатки данного способа, эквивалентные недостаткам описанного выше решения, обусловлены длительным временем затухания во времени ДИР ИФ. Другим недостатком данного и предыдущего способов является форма спектра используемого ими сигнала, которая не позволяет с помощью его спектра выделять спектры произвольной формы и ширины без искажений выделяемого сигнала.

Техническим результатом, на достижение которого направлено изобретение, является создание взаимно обратимого способа прямого и обратного преобразований непрерывных сигналов и цифровых информационных потоков в волновые носители этих потоков, а также устройства для реализации этого способа. Создание взаимно обратимого способа преобразования непрерывных сигналов достигают путем отказа от модуляции несущей, заменяя его кодированием (модуляцией) волновых пакетов. В данном случае нагрузка носителя информацией не сопровождается трансформацией исходного спектра носителя, поэтому термин кодирование волновых носителей или создание волновых пакетов вполне соответствует способу изобретения. Техническая реализация прямого преобразования (кодирование волновых носителей) позволяет расширить и унифицировать возможности сопряжения произвольно задаваемых временными (импульсными) или частотными (спектральными) параметрами потоков информации с дискретными по частоте каналами передачи. При этом частотная ширина каждого канала определена периодом следования посылок информации или шириной спектра непрерывного сигнала, а его расположение произвольно на оси частот. Совокупность таких каналов составляет множество (диапазон) каналов передачи, осуществляющих коммутацию информационных потоков между передающей и приемной частями. Техническая реализация обратного преобразования - фильтрация радио- или видеосигналов волновыми носителями - расширяет и повышает избирательность выделения частотных каналов путем построения управляемых фильтров на основе процедуры свертки ВП с сигналом. Следствием такого единообразия является улучшение физических, экономических и надежностных характеристик в сравнении с выполняющими аналогичные функции известными устройствами.

Указанный технический результат достигается тем, что в способе генерации, передачи, приема и селекции сигналов с ограниченным спектром

упорядочивают поток информации произвольного формата в поток двоично-дискретных символов оптимального формата для передачи и приема формата;

преобразовывают путем управления генерацией перемножаемых базовых волновых пакетов (ВП) каждый двоично-дискретный символ потока в действие волнового пакета (ДВП), образующего частотный канал заданного диапазона передачи, и, имеющего ограниченный во времени интервал действия на датчики поля образующего ДВП;

преобразовывают поток двоично-дискретных символов в поток действий волновых пакетов (ПДВП) путем суммирования на интервале времени действия одного ДВП частей всех одновременно присутствующих, предыдущих и последующих получаемых в ответ на символы потока данных, синтезируемых ДВП, интервалы, следования которых в потоке определяют параметры базовых ВП, входящих в виде мультипликативных компонент в состав каналообразующих ДВП;

передают сформированный суммарный сигнал в среду распространения;

принимают суперпозицию сигналов, одновременно присутствующих в среде распространения;

ограничивают спектр принятого сигнала заданным диапазоном;

квантуют принятый ограниченный по спектру сигнал с частотой выборки, определяемой шириной спектра выделяемого сигнала;

в ответ на каждую выборку уровня принимаемого сигнала путем управления генерацией перемножаемых импульсных реакций (ИР) базовых однокомпонентных идеальных фильтров (ОИФ) синтезируют импульсные реакции (ИР) многокомпонентного идеального фильтра (МИФ), с прямо пропорциональной значению выборки амплитудой ИР, с интервалом времени действия ИР, ограниченным во времени, и с полосой пропускания МИФ, равной сумме спектров базовых однокомпонентных ИР;

выделяют сигнал в заданном частотном канале путем суммирования на интервале времени действия одной ИР МИФ частей всех одновременно присутствующих, предыдущих и последующих, синтезируемых ИР получаемых в ответ на выборки уровней квантованного сигнала, интервалы следования которых определяют параметры базовых ИР, входящих в виде мультипликативных компонент в состав образующих МИФ ИР;

дешифрируют выделенный сигнал в поток двоично-дискретных символов передаваемого формата для последующего преобразования в исходный поток двоичной информации.

Указанный технический результат достигается тем, что в способе генерации сигналов для передачи с ограниченным спектром

упорядочивают поток информации произвольного формата в поток двоично-дискретных символов оптимального формата для передачи и приема формата;

преобразовывают путем управления генерацией перемножаемых базовых волновых пакетов (ВП) каждый двоично-дискретный символ потока в амплитуду действия волнового пакета (ДВП), образующего частотный канал заданного диапазона передачи и имеющего ограниченный во времени интервал действия на датчики поля образующего ДВП;

преобразовывают поток двоично-дискретных символов в поток действий волновых пакетов (ПДВП) путем суммирования на интервале времени действия одного ДВП частей всех одновременно присутствующих, предыдущих и последующих, получаемых в ответ на символы потока данных, синтезируемых ДВП, интервалы следования которых в потоке определяют параметры самого широкого базового ВП, входящего в виде мультипликативной компоненты в состав каналообразующих ДВП;

передают сформированный суммарный сигнал в среду распространения.

Указанный технический результат достигается также тем, что в вышеуказанном способе

управлением генерацией ограниченного во времени действия волнового пакета (ВП) осуществляют формирование амплитуды действия каналообразующего волнового пакета пропорциональной значению каждого четного символа упомянутого потока, формируя, таким образом, четный сигнал для передача-управлением генерацией ограниченного во времени действия волнового пакета (ВП) осуществляют формирование амплитуды действия каналообразующего волнового пакета, пропорциональной значению каждого нечетного символа упомянутого потока, формируя, таким образом, нечетный сигнал для передачи;

при этом суммирование всех сформированных сигналов осуществляют таким образом, что интервал времени между амплитудами смежных ДВП двух разных сигналов равен интервалу следования символов потока.

Указанный технический результат достигается тем, что в способе генерации сигналов для передачи с ограниченным спектром

упорядочивают поток информации произвольного формата в поток двоично-дискретных символов оптимального формата для передачи и приема формата;

преобразовывают путем управления генерацией перемножаемых базовых волновых пакетов (ВП) каждый двоично-дискретный символ потока в ширину спектра одного из его базовых ВП, при этом ширина спектра остальных его базовых ВП соответствует значениям предыдущих и последующих символов укладываемых на интервале времени действия волнового пакета (ДВП), образующего частотный канал заданного диапазона передачи;

преобразовывают поток двоично-дискретных символов в поток действий волновых пакетов (ПДВП) путем суммирования на интервале времени действия одного ДВП частей всех одновременно присутствующих, предыдущих и последующих, получаемых в ответ на символы потока данных, синтезируемых ДВП, интервалы следования которых в потоке пропорциональны размерам спектров базовых ВП, входящих в виде мультипликативной компонент в состав каналообразующих ДВП;

передают сформированный суммарный сигнал в среду распространения.

Указанный технический результат достигается тем, что в способе генерации сигналов для передачи с ограниченным спектром

упорядочивают поток информации произвольного формата в поток двоично-дискретных символов оптимального формата для передачи и приема формата;

преобразовывают путем управления генерацией перемножаемых базовых волновых пакетов (ВП) каждый двоично-дискретный символ потока во временной сдвиг спектра одного из его базовых ВП относительно некоторой точки времени, при этом временные сдвиги спектров остальных его базовых ВП соответствуют значениям предыдущих и последующих символов, укладываемых на ограниченном интервале времени действия волнового пакета (ДВП), образующего частотный канал заданного диапазона передачи;

преобразовывают поток двоично-дискретных символов в поток действий волновых пакетов (ПДВП) путем суммирования на интервале времени действия одного ДВП частей всех одновременно присутствующих, предыдущих и последующих, получаемых в ответ на символы потока данных, синтезируемых ДВП, интервалы следования которых в потоке пропорциональны фазам спектров базовых ВП, входящих в виде мультипликативной компонент в состав каналообразующих ДВП;

передают сформированный суммарный сигнал в среду распространения.

Указанный технический результат достигается тем, что в способе генерации сигналов для передачи с ограниченным спектром

упорядочивают поток информации произвольного формата в поток двоично-дискретных символов оптимального формата для передачи и приема формата;

преобразовывают путем управления генерацией перемножаемых базовых волновых пакетов (ВП) каждый двоично-дискретный символ потока в местоположение на оси частот спектров базовых ВП действия волнового пакета (ДВП), образующего частотный канал заданного диапазона передачи и имеющего ограниченный во времени интервал действия на датчики поля образующего ДВП;

преобразовывают поток двоично-дискретных символов в поток действий волновых пакетов (ПДВП) путем суммирования на интервале времени действия одного ДВП частей всех одновременно присутствующих, предыдущих и последующих, получаемых в ответ на символы потока данных, синтезируемых ДВП, интервалы, следования которых в потоке определяют параметры самого широкого ВП, входящего в виде мультипликативной компоненты в состав каналообразующих ДВП;

передают сформированный суммарный сигнал в среду распространения.

Указанный технический результат достигается тем, что в способе генерации сигналов для передачи с ограниченным спектром

упорядочивают поток информации произвольного формата в поток двоично-дискретных символов оптимального формата для передачи и приема формата;

преобразовывают путем управления генерацией перемножаемых базовых волновых пакетов (ВП) каждый двоично-дискретный символ потока в фазу частоты местоположения на оси частот спектров базовых ВП действия волнового пакета (ДВП), образующего частотный канал заданного диапазона передачи и имеющего ограниченный во времени интервал действия на датчики поля образующего ДВП;

преобразовывают поток двоично-дискретных символов в поток действий волновых пакетов (ПДВП) путем суммирования на интервале времени действия одного ДВП частей всех одновременно присутствующих, предыдущих и последующих, получаемых в ответ на символы потока данных, синтезируемых ДВП, а интервалы, следования которых в потоке определяют параметры самого широкого ВП, входящего в виде мультипликативной компоненты в состав каналообразующих ДВП;

передают сформированный суммарный сигнал в среду распространения.

Указанный технический результат достигается тем, что в способе приема и селекции радиосигналов с ограниченным спектром

принимают суперпозицию радиосигналов, одновременно присутствующих в среде распространения;

транслируют на нулевую частоту спектр принятой суперпозиции радиосигналов с помощью двух одинаковых по частоте и ортогональных по фазе гармоник, для получения двух ортогональных проекций видеосигнала;

осуществляют фильтрацию проекций видеосигнала фильтрами нижних частот, полоса пропускания которых превышает ширину выделяемого спектра в несколько раз для минимизации искажений амплитудно-частотной и фазочастотной характеристик спектра выделяемого сигнала;

квантуют отфильтрованные проекции видеосигнала с частотой выборки, определяемой шириной спектра выделяемого сигнала;

формируют абсолютные значения уровней напряжений или токов реконструируемого видеосигнала из выборок двух ортогональных проекций путем вычисления по теореме Пифагора;

формируют знаки вычисленных значений уровней напряжений или токов реконструируемого видеосигнала путем подстановки знака выборки одной из упомянутых ортогональных проекций видеосигнала, который инвертируют с частотой в два раза превышающей частоту расхождения частот генераторов приемника и передатчика;

формируют значения уровней напряжений или токов реконструируемого видеосигнала, содержащих выделяемый спектр, путем наложения на реконструированные абсолютные значения реконструированных знаков;

в ответ на каждое значение уровня реконструированного видеосигнала путем управления генерацией перемножаемых импульсных реакций (ИР) базовых однокомпонентных идеальных фильтров (ОИФ) синтезируют импульсные реакции (ИР) многокомпонентного идеального фильтра (МИФ), с прямо пропорциональной значению выборки амплитудой ИР, с интервалом времени действия ИР ограниченным во времени, и, с полосой пропускания МИФ равной сумме спектров базовых однокомпонентных ИР;

выделяют значения полезного сигнала в заданном частотном канале путем суммирования на интервале времени действия одной ИР МИФ частей всех одновременно присутствующих, предыдущих и последующих, синтезируемых ИР получаемых в ответ на каждое значение уровня реконструированного видеосигнала, интервалы, следования которых определяют параметры базовых ИР, входящих в виде мультипликативных компонент в состав образующих МИФ ИР;

дешифрируют выделенный сигнал в поток двоично-дискретных символов передаваемого формата для последующего преобразования в исходный поток двоичной информации.

Указанный технический результат

достигается тем, что в способе приема и селекции радиосигналов с ограниченным спектром

принимают суперпозицию радиосигналов, одновременно присутствующих в среде распространения;

транслируют на нулевую частоту спектр принятой суперпозиции радиосигналов с помощью двух одинаковых по частоте и ортогональных по фазе гармоник, для получения двух ортогональных проекций видеосигнала;

осуществляют фильтрацию проекций видеосигнала фильтрами нижних частот, полоса пропускания которых превышает ширину выделяемого спектра в несколько раз для минимизации искажений амплитудно-частотной и фазочастотной характеристик спектра выделяемого сигнала;

квантуют отфильтрованные проекции видеосигнала с частотой выборки, определяемой шириной спектра выделяемого сигнала;

в ответ на каждую выборку уровня отдельно опорной и отдельно ортогональной проекций реконструируемого видеосигнала путем управления генерацией перемножаемых импульсных реакций (ИР) базовых однокомпонентных идеальных фильтров (ОИФ) синтезируют ограниченные во времени импульсные реакции (ИР) многокомпонентного идеального фильтра (МИФ), с прямо пропорциональной значению выборки амплитудой ИР, с полосой пропускания МИФ равной сумме спектров базовых одно компонентных ИР;

выделяют значения отдельно опорной и отдельно ортогональной проекций полезного сигнала в заданном частотном канале, формируя амплитудно-варьируемый временной поток ИР МИФ, путем суммирования на интервале времени действия одиночной ИР всех одновременно присутствующих синтезированных ИР, интервалы следования которых определяют параметры базовых ИР, входящих в виде мультипликативных компонент в состав одиночных ИР МИФ;

подстраивают генератор частоты переноса приемника импульсами изменения величины отношения опорной и ортогональной проекций полезного сигнала, добиваясь вырождения одной проекции;

дешифрируют оставшийся сигнал в поток двоично-дискретных символов передаваемого формата для последующего преобразования в исходный поток двоичной информации.

Математические выражения имеющих возможность технической реализации действий ВП должны подчиняться требованию затухания во времени этих действий в выделенной точке пространства и требованию конечности значений параметров полей, образующих эти действия в выделенной точке пространства в произвольный момент времени. Математические выражения действий ВП, удовлетворяющих этим требованиям и составляющих формализованною сторону метода изобретения, состоят из полиномов от функций, отнесенных к полиномам от времени. Представление этих полиномов в виде произведения их корней дает произведение простых функциональных дробей, где числитель - линейная функция линейного аргумента, а знаменатель - просто линейная функция. Каждая функциональная дробь является действием некоторого ВП. Такие ВП называются базовыми ВП, или БВП. Само же математическое выражение произведения функциональных дробей называется многокомпонентным мультиплексным преобразованием (ММП), а физический объект, получаемый путем технической реализации ММП произведением волновых пакетов (ПВП). Среди всех возможных простых функциональных дробей существуют простые взаимно упорядоченные дроби, где их полюсы (они же корни полинома знаменателя в выражении ММП) должны быть скомпенсированы нулями ВП (они же корни функционального полинома числителя в выражении ММП) в центральных точках компонент ММП. Центральные точки сигналов, формируемых посредством ПВП, есть точки осевой симметрии. Математически центральные точки описывают нулевым отсчетом времени, которое является собственным действием некоторого собственного же БВП. Центральные точки компонент собственных БВП некоторого произведения ВП не обязательно совпадают с собственным временем произведения ВП. Центральная точка самого широкого в спектральном отношении собственного БВП является центральной точкой ДВП (ЦТ ДВП). Интервал времени между ЦТ ДВП и собственной центральной точкой какого-нибудь собственного БВП данного ДВП называется фазовым числом компоненты ДВП (ФЧК ДВП). Значение поля в ЦТ ДВП максимально. Самой общей формулировкой данного условия является совпадение корней полинома знаменателя с полиномом, который получают из аргументов функционального полинома числителя. Другим условием реализации конструктивных ДВП является наличие нулей, не скомпенсированных полюсами. Кроме базовых ВП, представленных конечными спектральными интервалами, в составе сомножителей БПВ возможно присутствие гармонической функции, которая представляет частотную точку, в окрестностях которой расположено ПВП. Формируемые посредством таких ПВП действия ВП имеют конечные интервалы времени существования. Интервалы времени существования определяют из условия того, что локально максимальные значения полей, образующих ДВП (как и все другие значения ДВП), затухают на этих интервалах от амплитуды в центральной точке ДВП до практически минимально приемлемых значений на концах этих интервалов. Физически данные интервалы времени определены временем действия (ВД) ВП на приемный датчик или преобразователь. Порядок минимальных значений ДВП в начале и конце ВД определен погрешностью реализации произведения ВП в создаваемом им действии ВП, исходя из чувствительности приемопередающего тракта. Наличие ЦТ и нулей ДВП позволяет формировать из них непрерывные потоки (цепи), в которых ЦТ текущего ДВП встраиваются в нули тех ДВП потока, ВД которых пересекается с ВД текущего ДВП. Длина ВД ВП определена степенью затухания ПВП, которая равна степени полинома от времени знаменателя. Данное изобретение предлагает варианты построения не только классических, но и самых произвольных модуляторов, демодуляторов и фильтров единым способом путем реализации произведения ВП (ПВП), являющегося общим описанием процедуры кодирования произвольной информацией функции нескольких базовых волновых пакетов.

Базовые ВП, действия которых определены выше, имеют спектр, ограниченный конечным интервалом частот с определенной формой, заранее выбранной по тем или иным свойствам разработчиком сигнала. Базовыми они называются потому, что их спектры являются примитивами (для конкретных исходных данных) и их задают одним параметром, например шириной с нормированной на единицу амплитудой и нулевой фазой. При этом форма спектра всех БВП будет одинакова. Иными словами БВП это неразборные элементы построения волновых носителей. Различные произведения ВП в виде соответствующих математических выражений дробей функциональных полиномов произвольного вида отображают информацию, представленную числами (или выборками чисел), в непрерывные функции. Спектры Фурье этих функций, являясь сверткой спектров всех входящих в модулируемый волновой пакет базовых ВП, имеют конечные интервалы частот, определяющих параметры реальных волновых посылок. Сами ПВП, являющиеся интегралами Фурье определенных конечных частотных интервалов, описывают действия полей, образующих ВП (ДВП), на приемный датчик или преобразователь, например на антенну, входной усилитель кабельного приемника и т.п. ВП - это конечные волновые объекты, поток которых однозначно отображает поток передаваемой информации путем реализации их ДВП. Спектральные параметры потока ВП и временные параметры потока информации при выборе БВП определенного типа близки к условиям оптимальности (предельная теорема Шеннона). Данное утверждение может быть доказано строго при соответствующем выборе БВП и применении методов сходимости последовательностей.

Любое действие ВП, описываемое конкретным ПВП, представляет число (цифровой сигнал). Совокупность действий ВП, представляющих конкретный набор чисел на интервале времени, равном длительности времени действия (ВД) отдельного ВП, выполняет функцию модулятора, формирующего сигналы волн связи. При этом числа, являющиеся исходным элементом модуляции, получают в виде двоичных кодов или оцифровкой непрерывного сигнала. В последнем случае непрерывный сигнал имеет спектр Фурье, который может быть либо полностью передан модуляторами данного типа, если он имеет границы, либо может быть передана часть его спектра, вырезанная модуляторами, имеющими плоские спектральные формы БВП. Процедура вырезания части спектра фактически является фильтрацией, а сами модуляторы являются составными частями фильтрующих преобразователей или просто фильтров. В последнем случае ДВП, с помощью которых производится построение фильтрующего модулятора, фактически являются импульсными реакциями многокомпонентных идеальных фильтров (ИР МИФ), полоса пропускания которых равна ширине спектра модулируемых ВП.

Соответствующий изобретению способ передачи непрерывных сигналов осуществляет модуляцию перемножением выборок значений исходного непрерывного сигнала с выборками нормированного на единицу ВП, построенного как ПВП. Полученный результат фильтруют от высших гармоник, получая непрерывный ДВП, который несет порцию информации об исходном непрерывном сигнале. Интервалы выборок задают исходя из временной структуры ДВП, топологию которого определяет множество окрестностей, представленных интервалами времени, задаваемыми, в силу мультипликативности ПВП, нулевыми значениями функций, входящих в состав компонент произведения ВП. Компоненты ПВП выбирают из множества базовых ВП.

Соответствующий изобретению способ передачи дискретной информации заключается в том, что в ответ на числа, полученные в виде двоичных кодов (цифровых символов), формирователь ВП путем перемножения БВП, вычисляя значения и формируя поле ДВП, создает ДВП, занимающее заданный частотный интервал, при этом поток и композиция ДВП являются значениями и полем модулированного видеосигнала или значениями и полем модулированного радиосигнала. Значения чисел формирователь ВП кодирует амплитудами ДВП, либо топологией ДВП, либо местоположением ВП на оси частот, т.е. частотой переноса.

Фильтрация сигнала отличается от формирования сигнала интегрированием процедуры модуляции на интервале ВД, где применение теоремы, проистекающей из теоремы Котельникова, позволяет заменить интеграл конечной суммой, учитывая конечность ВД, в результате чего все аналоговые устройства заменяют цифровыми. Интегрирование заменяют суммированием выборок на интервале ВД. Процедуру выборок осуществляют с частотой, в два раза превышающей максимальную частоту обрабатываемого спектра, которая в любом случае больше ширины рабочего канала. Способ фильтрации сигнала, соответствующий изобретению, заключается в том, что в ответ на числа, полученные оцифровкой непрерывного сигнала, фильтр на основе формирователя ВП путем перемножения БВП создает ДВП, поток которых является потоком значений модулированного видеосигнала либо потоком значений модулированного радиосигнала. Полученные потоки значений видеосигнала или радиосигнала цифроаналоговым преобразованием и фильтрацией преобразуют в поток ДВП, который в свою очередь передают в среду переноса, если формирователь ВП выполнял функцию модулятора, либо дешифрируют, если формирователь ВП выполнял функцию фильтра.

Спектры ВП, формируемые способом, соответствующим изобретению, являются интегралами произведений ВП. Получают их в предположении независимости времени от переменной интегрирования - частоты. Спектры таких ВП состоят из наложений спектров базовых ВП. Частотный спектр каждого из базовых ВП состоит из гиперболически зависящих от времени функций, задаваемых на определенных отрезках оси частот. Формирование ВП осуществляют посредством ДВП путем вычисления произведений нормированных компонент, составляющих ПВП. Число компонент в ПВП равно двоичному логарифму от общего числа базовых спектров в спектре ВП. Для определенного типа БВП верхний предел частоты следования нулей функций числителя, входящих в состав компонент ПВП, равен половине ширины спектра максимального базового ВП.

Множество всех возможных ВП, получаемых таким способом, имеет бесконечную мощность, определяемую произведением размеров всех компонент ПВП, размеры каждой из которых (ширина спектра базовых ВП) равны мощности, определяемой множеством вещественных неотрицательных чисел, из которых состоит ось частот.

Порождаемые произведениями БВП действия ВП, как и спектры их ВП, непрерывны и локальны, т.е. ограничены сверху и снизу во времени и по частоте. Границы существования ДВП определяют интервалы времени, на которых значения напряженности поля ДВП отличны от нуля с определенной погрешностью, а границы спектра ВП определяют интервалы частот, на которых значения частот спектра просто отличны от нуля. Таким образом, каждый формируемый ВП генерирует и частотный канал распространения, определяемый шириной и положением его спектра.

Любая периодическая функция удовлетворяет двум условиям технической реализации ДВП, приведенным выше, и может быть функцией числителя какого-либо БВП. Функцию знаменателя может исполнять произвольная алгебраическая функция первой степени. Так как любая периодическая функция раскладывается в тригонометрический ряд, то математическое выражение спектра синтезируемого ВП данного типа, явно зависящее от времени, получают с помощью тригонометрических преобразований формулы ПВП и ее дифференцирования. При этом сначала путем тригонометрических преобразований переводят произведения в суммы и разности синусов и косинусов, отнесенных ко времени, в степени, которая не меньше числа компонент, являющихся базовыми ВП, а затем дифференцируют и получают выражение синтезированного волнового пакета в виде сумм функций амплитуд на частотных интервалах. В таком представлении функции амплитуд спектра синтезируемого ВП имеют явную зависимость от времени, являющегося независимым параметром. Число этих интервалов равно двум в степени, равной числу компонент ПВП. Таким образом, сигнал, формируемый способом, соответствующим изобретению, представляет собой сумму спектров базовых волновых пакетов, затухающих во времени относительно собственной точки отсчета времени действия ВП, в которой это действие принимает свое амплитудное значение. Собственная точка отсчета времени ДВП является центральной точкой действия волнового пакета (ЦТ ДВП). Данная логическая цепь поясняет характер формируемого заявленным способом сигнала, поясняет термин «волновой пакет» и позволяет вычислять границы сигнала (интервалы затухания) и границы рабочих участков его частотного спектра. Рабочий участок спектра синтезированного ВП выбирают таким образом, что он почти целиком определен амплитудной зависимостью спектра одного из базовых ВП.

Форма спектра ВП, не зависящего явно от времени, может быть вычислена через спектры компонент, входящих в состав произведения ВП сверткой спектров всех его БВП.

Математические преобразования, проведенные для определенного класса БВП, не приводимые здесь, позволяют сделать вывод, что форма спектра в общем случае состоит из участков, каждый из которых описывается алгебраической кривой. Наивысший порядок алгебраической кривой на единицу меньше числа сомножителей в ПВП. Т.е. для определенного класса БВП, спектр ВП образован участками кривых, степень которых на единицу меньше порядка времени затухания действия этого ВП. Из этих участков практический интерес представляют два. Первый - рабочая часть спектра, т.е. участок с априорной зависимостью амплитуды частот спектра ВП, и второй - это весь спектр частот или ширина спектра ВП. Зависимости, выражающие границы этих участков, получают непосредственным интегрированием ПВП.

Границы в общем виде могут быть вычислены следующим образом.

Формула для ПВП содержит N сомножителей, которые являются базовыми ВП. Ширина спектра основного (первого) ВП обозначается как

В-Н=Δ,

где В - верхняя граница спектра,

Н - нижняя граница спектра.

Ширина остальных БВП - как

Δ/N(i),

где N(i) - вещественное неотрицательное число,

i - целое положительное число от 2 до N; N(1)=2.

Число 2, с которого начинают процесс формирования ПВП, учитывает факт удвоения спектра за счет отрицательных частот спектра. Спектр ПВП формируют последовательно в порядке нарастания параметра N, используя при этом процедуру свертки спектров. Начало границы затухания спектра двухкомпонентного ПВП равны:

Δ·[1/N(1)-1/N(2)] - для положительных частот спектра ПВП;

Δ·[-1/N(1)+1/N(2)] - для отрицательных частот спектра ПВП.

Границы всего спектра равны:

Δ·[1/N(1)+1/N(2)] - для положительных частот спектра ПВП;

Δ·[-1/N(1)-1/N(2)] - для положительных частот спектра ПВП.

Осуществляя последовательное построение (математическую индукцию), получают начало спада амплитуды спектра N-компонентного ПВП в следующем виде:

Δ·[1/N(1)-Σi(1/N(i))] - для положительных частот спектра ПВП;

Δ·[-1/N(1)+Σi(1/N(i))] - для отрицательных частот спектра ПВП.

Границы всего N-компонентного спектра ПВП равны:

Δ·[1/N(1)+Σi(1/N(i))] - для положительных частот спектра ПВП;

Δ·[-1/N(1)-Σi(1/N(i))] - для отрицательных частот спектра ПВП.

Тело N-компонентного спектра ПВП, расположенного в границах

от 0 до Δ·[1/N(1)+Σi(1/N(i))] - для положительных частот спектра ПВП и

от 0 до -Δ·[1/N(1)+Σi(1/N (i))] - для отрицательных частот спектра ПВП.

При N→∞ спектр ПВП имеет распределение амплитуд равное произведению бесконечного числа бесконечно малых спектров, каждый из которых пропорционален спектру основного БВП, а коэффициенты пропорциональности представляют собой произвольную вещественную функцию. Функции, рассматриваемые в изобретении, есть конечные дискретные функции, для которых коэффициенты пропорциональности равны N(i). Числа N(i) далее называются волновыми числами компонент (ВЧК) ПВП.

Границы интервала времени ДВП определены зависимостью

˜1/[(t+αi)n·Πi(Δ/(N(i)],

так как на интервале времени t=Х·N1)/Δ, отсчитываемом от момента времени t=0, то есть относительно ЦТ, ДВП затухает в Xn·ΠI[N(1)/N(i)] раз. Здесь Πi[(Δ/(N(i)] - нормирующий множитель, αi - ФЧК соответствующего базового волнового пакета. Выражение для S=-Хmax и S=+Хmax, то есть для первого и последнего номера, определяет погрешность преобразования функции Fn или, что равнозначно, погрешность формирования ВП. Число S равно половине времени существования полей, образующих ДВП, в выделенной точке пространства, а полное время существования ДВП в выделенной точке пространства равно 2*S, которое ранее было определено как интервал ВД ДВП. Далее везде, где это не приводит к путанице слова "в выделенной точке пространства" опускаются. Произведение Πi осуществляется по i от 1 до n, причем N(1)=2. Условия, накладываемое на ВП границами существования во времени, приводят к трансформации конечного спектра в бесконечный спектр путем "растягивания" фронтов спектрального импульса, спадающих тем не менее в степени, не меньшей степени затухания ДВП во времени. Последнее утверждение верно в силу симметричности прямого и обратного Фурье преобразований и подтверждается расчетами, выполненными на соответствующих математических моделях.

Представление формы сигнала - ДВП.

Формула ПВП математически описывает ДВП, короткие ВД которых образуют путем одновременного действия всех входящих в него базовых ВП, где ширину спектра каждого базового ВП выбирают, оптимизируя отношение ширины спектра ВП к ВД ДВП.

Ширину спектра ВП выбирают исходя из ширины спектра исходного непрерывного сигнала, либо ширины спектра полезного сигнала в исходном непрерывном сигнале, либо частоты следования исходных информационных посылок.

Модуляцию ДВП осуществляют по любому масштабирующему параметру формулы ПВП (не затрагивающему его вида), как-то амплитуда рабочего участка спектра (амплитуда того базового ВП, тело которого определяет этот участок), частоты компонент базовых ВП, фазы компонент базовых ВП и отдельно частота и фаза компоненты ПВП, определяющей место на оси частот. Для сравнения скажем, что классические способы модуляции основаны на управлении исходным сигналом одного из трех параметров несущей частоты. А именно амплитудой несущей частоты, фазой несущей частоты или значением несущей частоты. Причем исходный сигнал должен иметь спектр, расположенный в определенных границах.

Дуальная интерпретация формы сигнала.

Формула ПВП математически описывает быстро затухающие во времени ИР многокомпонентных фильтров (МФ), порядок затухания которых образуют путем одновременного действия всех входящих в него полос базовых фильтров (БФ), где полосу пропускания каждого БФ выбирают, оптимизируя отношение ширины полосы МФ к длине его ИР.

Способы получения сигналов с ограниченным спектром из самых различных исходных сигналов в современной радиотехнике разнообразны и многочисленны. Но все они основаны на едином принципе обработки непрерывного исходного сигнала радиочастотными или статистическими фильтрами. Даже если исходная информация образует дискретный поток, он преобразуется в непрерывный сигнал сначала статистической обработкой, а затем фильтрацией - сначала фильтрами Гаусса, а затем реальными фильтрами. Такая сложная конструкция вызвана тем, что прямая фильтрация дискретного потока информации, имеющего бесконечный спектр, реальными фильтрами с гиперболическими частотными характеристиками вызывает эрозию многократно фильтруемого сигнала, так как спектр сигнала, получаемого фильтрацией реальным фильтром числового потока, не ограничивается полосой пропускания последнего. Многократные фильтрации каждый раз отсекают от спектра сигнала какую-то часть, что и вызывает искажение сигнала, выражающееся в расползании интервалов времени. Итоговая картина усугубляется нелинейностью фазовых характеристик в полосе пропускания реальных гиперболических фильтров. Фильтры Гаусса ограничивают спектры сигналов практически в границах их полосы и фронтов. Фильтрация таких сигналов реальными гиперболическими фильтрами, полоса пропускания которых целиком покрывает спектр фильтра Гаусса, не приводит к искажениям сигнала, связанным с потерей части его спектра. Общим существенным недостатком таких сигналов являются низкие динамические характеристики фронтов нарастания и спада значений. Данный недостаток и вызвал появление различных методов статистической обработки призванных повысить классическое отношение сигнал/шум. Последние можно разделить по методам формирования, например статистический метод сглаживания смены фазы квадратурной амплитудной модуляции и методы шифрации/дешифрации сигнала, реализуемые различными статистическими алгоритмами.

В приведенных выше известных решениях осуществляется преобразование информационных посылок в непрерывный сигнал путем суперпозиции сигналов, являющихся импульсными реакциями (ИР) некоторых БФ, полосы пропускания которых соответствуют спектрам сигналов. Так в патенте US 4558454 сигнал получают суперпозицией двух БВП, имеющих постоянную амплитуду спектра на отрезке, прилегающем к нулю, с полярными и постоянными амплитудами, которые задержаны относительно друг друга на величину равную TL=2/В-Н. В патенте RU 2160509 сигнал БВП получают методом интегрирования спектров с гармонической зависимостью на выбранном отрезке. Дуальная интерпретация данного сигнала эквивалентна суперпозиции двух базовых ВП, имеющих постоянную амплитуду спектра, произвольно расположенного на оси частот, с полярными и равными между собой амплитудами, которые задержаны относительно друг друга на величину, кратную TL=2/В-Н, и амплитуды которых дискретно изменяют, кодируя входную информацию. Площади спектров таких сигналов в относительных единицах равны 2/π от площади спектра единичного базового ВП, который представляет собой ВП Котельникова. Базовый ВП Котельникова как известно имеет форму квадрата единичной длины (так называемый шумоподобный спектр). Последнее из приведенных выше известных решений практически реализует потенциальные возможности используемого сигнала, состоящего из суперпозиции действий двух ВП Котельникова. Таким образом теоретический предел таких сигналов ограничен величиной в 2/π от аналогичного предела шумоподобных сигналов. Кроме того, в патенте RU 2160509 указан метод приближения величины 2/π к единице путем предварительного кодирования исходной информации на заранее выбранном интервале, т.е. предварительной обработке информации по определенному алгоритму, предлагаемые к патентованию данной заявкой, формируют методами, которые не предусматривают способов неконтролируемого отсекания спектра гиперболическими фильтрами или слабо контролируемого отсекания энергетики спектра статистической обработкой сигнала. Сигналы, реализуемые способами, соответствующими настоящему изобретению, для дискретных посылок информации допускают спектры, формы которых весьма разнообразны, среди которых есть формы эквивалентные криволинейным трапециям (боковые стороны алгебраические кривые).

Для определенного типа БВП отношение площади части трапеции, занимаемой плоской частью, к площади, занимаемой ее границами, в общем случае может быть представлено формулой вида

2/(ΣiN(i) -1),

где N(i) - площади спектров базовых ВП в произведении ПВП, причем суммирование производится по i от 2 до N.

Из приведенной формулы отношения площадей спектров следует, что сигналы, создаваемые предлагаемым способом, могут иметь различные границы предельной загруженности. Их наибольшей верхней границей является величина, следующая из теоремы Котельникова. Ее можно определить как границу информационной емкости сигнала, на который наложен шум по Котельникову. Граница по Котельникову состоит из двух сомножителей, первый из которых - частота следования посылок информации, равная удвоенной ширине спектра сигнала ≈N(1), а второй - емкость каждой посылки, отсчитываемой в единицах, равных уровню шума.

В отличие от предела по Шеннону, в пределе по Котельникову сигналы представлены максимально возможными амплитудами. Далее, в трактовке по Котельникову понятие вероятности отсутствует вообще. То есть сам сигнал при выполнении условий второго сомножителя (естественно и первого) полностью однозначен.

Далее, степень затухания ДВП во времени в предлагаемом способе значительно выше аналогичного параметра для приведенных выше известных способов, что выражается в уменьшении объема аппаратуры, требуемой для их реализации и/или увеличения ширины спектра формируемого сигнала.

И, наконец, форма спектра в приведенных выше способах не обеспечивает построения фильтров типа нижних частот (НЧ) или промежуточных частот (ПЧ) на основе их ИР-ДВП (см. ниже).

Преимущества реализации сигналов на основе ДВП.

1. В силу того, что спектр ВП имеет границу, все стандартные виды модуляций и их варианты, примененные к ВП, не приводят к дополнительному увеличению ширины спектра ВП сверх обычно задаваемой этими видами модуляции и не требуют фильтров, ограничивающих спектр сигнала. Например, амплитудная модуляция увеличивает ширину спектра ВП вдвое и не более того.

2. Сами стандартные модуляции получают перемножением ВП, которые создают соответствующие этим модуляциям кодирования ДВП дискретной информации. Данный вывод есть следствие приближения формы спектра ВП, порождаемых ПВП, к форме ВП Котельникова - прямоугольнику.

3. Подобие форм спектров ВП формам временных импульсов, например электромагнитных, порождает соответствующие импульсным модуляциям кодирования параметрами спектрального представления. При этом амплитуды импульсов соответствуют амплитудам спектров, а интервал следования импульсов расщепляется на собственно интервал следования посылок информации и интервал смещения спектров, являющийся элементом кодирования информации. Ниже такие представления рассматриваются как пакетные кодирования. Поле этих кодирований задает форма спектра ВП, определяемая топологией ДВП, задаваемой в свою очередь нулевыми значениями компонент, порождающих их базовых ВП. Данное поле кодирования фактом расщепления интервалов следования ДВП разделено на два элемента, один из которых отклонения ЦТ БВП от ЦТ основного БВП - отображения интервалов следования во временное смещение спектров БВП относительно основного БВП, а другой ширина спектра ВП каждой отдельной посылки ВП - отображения интервала следования в ширину спектра ВП. Таким образом, подобие форм порождает вид модуляции, имеющий две степени свободы, т.е. два независимых параметра кодирования.

4. Полное поле кодирования имеет пять степеней свободы, а именно амплитуду, ширину спектра ДВП, отклонения ЦТ БВП от ЦТ основного БВП, частоту и фазу трансляционной (т.е. определяющей место на оси частот) компоненты ДВП. Таким образом, общее число различных видов кодирования числа параметрами ДВП составляет 25=32. Особо нужно подчеркнуть, что все типы кодирования - модуляций имеют конечные спектры. Конечный спектр имеют и две трансляционные модуляции, соответствующие классическим частотной модуляции и фазовой модуляции, что объясняется видом модулирующего воздействия, которое в данном случае не гармоническое, а дискретное. То есть дискретное действие преобразуется в дискретный спектр. Это же относится и к непрерывному модулирующему воздействию с ограниченным спектром.

5. Полное поле кодирования представляется обобщенным алгоритмом, который наполняет соответствующую ему формулу ПВП конкретными действиями, реализуя соответствующий конкретный вариант осуществления заявленного способа.

6. Непременным условием простой реализации синтезируемого произведения ВП является наличие нулей функции ПВП, которые не скомпенсированы полюсами ПВП. Период следования нулей, если таковой существует, далее обозначен TL/2. Значения поля ДВП, реализованного по такой формуле ПВП, имеют абсолютный максимум в центральной точке (ЦТ) и по меньшей мере 2·S локальных максимумов, расположенных между смежными нулями ДВП, которые затухают от ЦТ к периферии по гиперболическому закону степени N. Каждое вновь синтезируемое ДВП встраивают в поток ДВП таким образом, что его ЦТ приходится на один из нулей всех, как уже существующих, так и вновь порождаемых ДВП. Такие точки синтезируемого потока ДВП содержат суперпозицию 2·S нулей и одной амплитуды ЦТ. Интервал 2·S имеет длительность, равную времени действия (ВД) произвольного ДВП в единицах TL. Вне этого интервала поле единичного действия ВП затухает пропорционально числу SΣm(i), где m(i) - степень зависимости от времени i-го БВП.

Варианты осуществления способа передачи-приема сигналов с использованием ПВП.

Прямое преобразование.

По каждому символу информации - числу, вычисляя параметры произведением выбранных базовых ВП, создают волновые носители - действие волновых пакетов (ДВП), поток которых однозначно представляет соответствующий ему поток символов информации.

Поток информации в общем случае может быть представлен потоком двоичных чисел, амплитуда (значение) и интервал следования которых, в совокупности, отражают мощность потока информации. Таким образом, любой информационный поток передается совокупностью двух своих параметров. В заявленном изобретении предлагается пять независимых вариантов реализации любых информационных потоков.

Амплитудный вариант модулирования ВП

Каждый символ информации - число модулирует каналообразующий ВП, полученный перемножением определенных базовых ВП, путем перемножения числа и соответствующего каналообразующему волновому пакету действия с суммированием со всеми одновременно присутствующими на интервале его ВД предыдущими и последующими ДВП, порождаемыми символами входного потока информации.

В данном варианте интервалы следования ДВП постоянны и согласно теореме Котельникова превышают величину, обратную ширине спектра нормированного на единицу амплитуды ВП, порождающего поток ДВП. Информация кодируется амплитудами ДВП.

Фазовый вариант модулирования ВП

Пакет смежных символов информации - пакет чисел модулирует каналообразующий ВП, полученный перемножением выбранных базовых ВП, путем подбора распределения смещения базовых ВП каналообразующего волнового пакета, соответствующего ДВП, с суммированием со всеми одновременно присутствующими на интервале его ВД предыдущими и последующими ДВП, порождаемыми символами входного потока информации.

В данном варианте амплитуды всех ДВП, входящих в поток ДВП, постоянны. Информация кодируется интервалами следования ДВП. Необходимым условием реализации подобных вариантов является наличие в каждом ДВП следа от интервалов постановки амплитуд других ДВП. След соседних действий ВП проявляется нулевыми значениями данного действия ВП. Эти нулевые значения формируют путем манипуляций со смещением ЦТ компонент ДВП, которые составляют данное произведение ВП.

Частотный вариант модулирования ВП.

Пакет смежных символов информации - пакет чисел модулирует каналообразующий ВП, полученный перемножением выбранных базовых ВП, путем подбора ширины базовых ВП каналообразующего волнового пакета, соответствующего ДВП, суммированием со всеми одновременно присутствующими на интервале его ВД предыдущими и последующими ДВП, порождаемыми символами входного потока информации.

След соседних ДВП в этом варианте реализуют путем манипуляций с частотами компонент ДВП, которые определяются размерами (шириной) спектров соответствующей группы БВП данного волнового пакета.

Вариант модулирования фазы частоты трансляции (переноса) ВП.

Каждый символ информации - число модулирует каналообразующий ВП, полученный перемножением выбранных базовых ВП, путем подбора фазы частоты трансляции (переноса) каналообразующего волнового пакета, соответствующего ДВП, суммированием со всеми одновременно присутствующими на интервале его ВД предыдущими и последующими ДВП, порождаемыми символами входного потока информации.

Данный вариант является прямым аналогом классической фазовой модуляции. Отличие состоит в том, что спектр такого сигнала не является гребенчатым и по форме соответствует амплитудной модуляции. Амплитуды и интервалы следования ДВП постоянны. Информация кодируется пропорциональным изменением фазы трансляционной (несущей) компоненты ДВП, то есть компоненты, задаваемой гармоникой.

Вариант модулирования частоты трансляции (переноса) ВП.

Каждый символ информации - число модулирует каналообразующий ВП, полученный перемножением выбранных базовых ВП, путем подбора частоты трансляции (переноса) каналообразующего волнового пакета, соответствующего ДВП, суммированием со всеми одновременно присутствующими на интервале его ВД предыдущими и последующими ДВП, порождаемыми символами входного потока информации.

Данный вариант является прямым аналогом классической частотной модуляции. Отличие состоит в том, что спектр такого сигнала не является гребенчатым и по форме соответствует амплитудной модуляции. Амплитуды и интервалы следования ДВП постоянны. Информация кодируется пропорциональным изменением частоты несущей компоненты ДВП, то есть компоненты, задаваемой гармоникой.

Выделение спектра частот

Выделение спектра частот из существующего непрерывного сигнала - фильтрация, отличается от вышеприведенного алгоритма кодирования ВП (модуляции ДВП) оцифровкой непрерывного сигнала, то есть вычислением элементов цифрового потока данных, по которым реконструируют сигнал передатчика.

Элементы цифрового потока данных вычисляются на основе теоремы о свертке, при этом одним из свертываемых сигналов является входной непрерывный сигнал, а другим сигналом - импульсная реакция многокомпонентного фильтра (ИР МФ), который представляет собой ДВП, получаемый перемножением заранее выбранных базовых ВП. Интеграл свертки заменяют суммой и осуществляют суммирование значений подынтегрального выражения в точках дискретизации.

Такая замена в спектральном представлении приводит к замене произведения спектра исходного непрерывного сигнала и ВП на сумму бесконечного числа спектров, являющихся произведениями исходного непрерывного сигнала, и МИФ (ВП), сдвинутых относительно друг друга на частоту дискретизации, т.е. сумму транслированных спектров. Поэтому частота дискретизации исходного непрерывного сигнала, а вместе с ним и ИР МИФ (ДВП), выбирается из условия неналожения смежных сдвинутых относительно друг друга произведений спектра исходного непрерывного сигнала и ВП. Для получения непрерывного сигнала достаточно пропустить уровни вычисленных значений через реальный фильтр. Операция фильтрации реальным фильтром предполагает пограничные зоны пустых частотных интервалов, а это означает, что частота дискретизации должна превышать максимальную частоту спектра исходного непрерывного сигнала более чем в два раза. Данная величина рассчитывается в основном из условия неискажения фазово-частотной характеристики (ФЧХ) спектра, т.к. реальные многозвенные фильтры при достаточно хороших эквипотенциальных амплитудно-частотных характеристиках (АЧХ) имеют удовлетворительную линейность ФЧХ на участке менее 0.5 полосы пропускания фильтров. Таким образом, фильтрации реальным фильтром предполагает пограничные зоны пустых частотных интервалов, превышающие по величине сам спектр сигнала, а это означает, что частота дискретизации должна превышать максимальную частоту спектра исходного непрерывного сигнала более чем в четыре раза. Выбор частоты дискретизации зависит от типа реального фильтра, который собирается применить разработчик, так увеличение частоты дискретизации приводит к ослаблению требований, предъявляемых к постоянству уровня АЧХ и постоянства угла наклона ФЧХ. Требования, предъявляемые к такому фильтру, минимальны, поскольку рабочий участок, определяемый постоянством коэффициента передачи и линейностью фазы, много меньше полосы пропускания, а спад полосы пропускания может быть протяженным. С другой стороны максимум частоты дискретизации ограничен быстродействием элементной базы.

Формирование значений выделяемого сигнала

Выделяемый сигнал получают путем фильтрации уровней напряжения или тока, которые формируют сверткой выборок значений входного сигнала и значений импульсной реакции идеального многокомпонентного фильтра (ИР МИФ), состоящего из перемножаемых компонент, являющихся импульсными реакциями многокомпонентных фильтров нижних/промежуточных частот.

Импульсные реакции многокомпонентных идеальных фильтров промежуточных частот отличаются от импульсных реакций многокомпонентных идеальных фильтров нижних частот трансляционной компонентой, представляющей собой гармонику частоты переноса.

Поэтапное описание способа выделения сигнала выглядит следующим образом.

1) Измеряют диапазон значений исходного непрерывного сигнала в единицах шага квантования.

2) Вычисляют для всех возможных ИР МИФ (ДВП), с амплитудами, взятыми из области квантования диапазона исходного непрерывного сигнала, значения, число которых для каждого ИР МИФ (ДВП) равно 2·S·TL/Td, где Td - частота дискретизации, TL/2 - период следования нулей ИР МИФ (ДВП), и запоминают их в библиотеке потенциальных ИР МИФ (ДВП). Согласно сказанному выше FL=2·π/TL - это величина большая, чем ширина полосы пропускания основного базового ИФ (ширина спектра основного БВП).

3) Измеряют аналого-цифровым преобразователем значения исходного непрерывного сигнала с частотой следования измерений 1/Td, превышающей не менее чем в два раза максимальную частоту спектра исходного непрерывного сигнала.

4) Формируют квадратную матрицу значений активных ИР МИФ (ДВП), состоящую из тех ИР МИФ (ДВП), амплитуды которых совпадают с числами измерений, а порядок поступления, которых определяет порядок расположения столбцов матрицы активных ИР МИФ (ДВП). Число столбцов равно длине интервала ВД в единицах Td. Иными словами каждая ИР МИФ (ДВП) представлена вектором в дискретном пространстве 2·S·Tb/Td измерений.

5) Вычисляют значение отфильтрованного сигнала суммированием значений, расположенных на диагонали матрицы активных ИР МИФ (ДВП). Получаемое таким образом значение является следом (Shpure) матрицы активных ИР МИФ (ДВП). Более подробно указанная процедура выглядит следующим образом. Квадратную матрицу активных ИР МИФ (ДВП) формируют путем сдвига всех столбцов, состоящих из векторов ИР МИФ (ДВП), влево на одну позицию. В результате самый старый вектор-столбец ИР МИФ (ДВП) (соответствующий наиболее старому значению исходного непрерывного сигнала) исчезает, его место занимает следующий по порядку (времени измерения) вектор-столбец и т.д. Освободившееся первое место занимает вектор-столбец, соответствующий вновь измеренному значению.

6) Вычисленные значения цифроаналоговым преобразователем преобразуют в уровни напряжений или токов и фильтруют фильтром нижних частот с характеристиками, аналогичными предварительному фильтру.

Описанный способ реализует как фильтры НЧ, так и фильтры ПЧ. Формула ПВП фильтров ПЧ отличается наличием трансляционной компоненты.

Таким образом, для того чтобы вырезать из спектра принимаемого сигнала полезную часть и при этом не получить наложения из смежного транслированного произведения, необходимо осуществлять дискретизацию с частотой, не допускающей наложения генерируемых процессом дискретизации спектров. Далее если известно, что полезная часть спектрально обособлена, т.е. имеет приграничные зоны пустых частотных интервалов, длина которых не менее длины границы ИР МИФ (ДВП), то реконструкцию значений достаточно производить ИР МИФ (ДВП) с полосой пропускания (телом спектра ДВП), равной ширине спектра любого ДВП, излучаемого передатчиком. Последнее из вышеприведенных условий означает наличие зазора между каналами передачи, длина которых не менее длины границы ИР МИФ (ДВП), т.е. длины нарастания и затухания полосы пропускания.

Вычисляемые по такой процедуре значения будут тем меньше отличаться от значений получаемых при дискретизации исходного сигнала, поступающего к передатчику (если исходный сигнал был непрерывным), чем выше частота дискретизации. Причем в данном случае дискретизацией, накладывающей указанные условия, является дискретизация ВД ИР МИФ (ВД ДВП), в то время как интервал дискретизации фильтруемого сигнала определен шириной полосы пропускания ИР МИФ (ДВП) и соответствующим условием теоремы, подобной теореме Котельникова. Интервал дискретизации влияет лишь на амплитуду выделяемого сигнала. Тем самым применение реального фильтра ставится в зависимость от быстродействия цифровой элементной базы, а это приводит к отказу от последнего 6-го пункта способа фильтрации.

Следствием приведенного выше алгоритма является распространение взаимно однозначного соответствия между числовым потоком определенной частоты и шириной спектра непрерывного сигнала, полученного Котельниковым. Учитывая, что указанное соответствие фактически есть соответствие между плоской частью спектра ВП, полученного ПВП, и числовым потоком, коэффициент полезного действия преобразований осуществляемых ПВП определенного вида (КПД ПВП) равен отношению ширины плоской части спектра ВП к сумме длин его верхней и нижней пограничных областей. Так КПД однокомпонентного ВП Котельникова (БВП) равен единице.

С другой стороны данный результат должен согласоваться с теоремой Шеннона о ширине спектра. Действительно, рассматривая параметры кодирования, фигурирующие в формирователях непрерывных сигналов (способ построения которых изложен ниже в пяти разделах) в качестве носителей бит входной информации, беря шаг квантования не меньше уровня шумов в тракте передачи-приема формируемого непрерывного сигнала, беря плотность носителей бит входной информации в виде двоичного логарифма от диапазона квантования формируемого непрерывного сигнала, можно заключить, что скорость передачи информации, достигаемая устройством, реализованным предлагаемым способом, приближается к произведению ширины спектра формируемого непрерывного сигнала, и двоичного логарифма от отношения диапазона кодирования к шуму в тракте передачи-приема.

Следует заметить, что в отличие от теоремы Шеннона в отношении под знаком логарифма присутствуют не энергии, а потенциалы. Но и рассматриваемый спектр фактически меньше в два раза и равен В. Его удвоение при умножении на частоту переноса компенсируется введением дополнительного канала. Механизм, осуществляющий введение дополнительного канала и сама процедура введения рассматривается в амплитудном варианте способа изобретения. Полученный результат, учитывая то, что участки спектров ДВП, ограниченные плоской частью, шуму подобны, прекрасно согласуются с выводами той же теоремы Шеннона.

Амплитудный вариант осуществления способа, соответствующего изобретению.

Амплитудный вариант, способ формирования которого приводится в изобретении, заключается в том, что:

поток чисел преобразуют в поток амплитудно-модулированных ДВП перемножением базовых ВП, спектры, фазы спектров, частота местоположения и фаза частоты местоположения которых фиксированы, а амплитуды ДВП пропорциональны числам потока.

Вычисление по формуле ПВП в точках дискретизации значения полей напряжений или токов ДВП, число которых равно диапазону изменяемого параметра амплитуды Y(m), осуществляют либо в реальном времени и запоминают в блоках памяти, либо в отложенном времени и также запоминают в блоках памяти. Таким образом, в обоих случаях блоки памяти являются источниками потенциальных ДВП - возможных реакций на все возможные числа источника данных. Последнее, а именно согласование произвольного диапазона входных чисел, зависящего в общем случае от количества разрядов интерфейса связи, осуществляют отдельными преобразователями форматов представления чисел.

Амплитудный модулятор ДВП, создающий поток электромагнитных волн, подобен устройству гортани человека, создающей поток акустических волн. Для процесса передачи информации ДВП является неразборным образованием или квантом энергии, пропорциональной переносимой информации.

В качестве источника данных может выступать любой цифровой массив, полученный либо оцифровкой непрерывного сигнала, либо являющийся изначально цифровым массивом, предназначенным к передаче. Поэтому множество значений, способ формирования которых описан в данном разделе, являются значениями ДВП при построении амплитудного модулятора ВП или множеством значений ИР многокомпонентных идеальных фильтров при построении фильтра.

Для произвольных БВП формула амплитудной модуляции ВП выглядит следующим образом

Fn=Y(m)·Fnn·cos (ψДВП·t),

где Y(m) - изменяемый параметр амплитуды,

Fnn - ядро ММП (ПВП),

cos(ΨДВП·t) - трансляционная компонента ПВП.

Основной характеристикой таких ПВП является наличие периодически повторяющихся нулей функции Fnn, которые не скомпенсированы ее полюсами. Центральные точки (ЦТ) компонент функции Fnn совпадают между собой и ЦТ ДВП, то есть все фазовые числа компонент (ФЧК) равны 0. Волновые числа компонент (ВЧК) в общем случае различны и постоянны для всех Fnn.

Суперпозиция сигналов Fn - это сигнал, который традиционно получают балансной амплитудной модуляцией частоты Ψдвп, с модулирующим сигналом Fnn, являющимся ядром ПВП, также представляющим некоторое ДВП с переменной амплитудной.

Элементы множества потенциальных ДВП - множества действий в ответ на все возможные числа источника данных различающиеся амплитудами Y(m), составляют те ДВП, ВЧК которых намного превышают ВЧК наивысшей по частоте компоненты N(i)≫N(1)=2.

При этом условии спектральная ширина ВП приблизительно равна (В-Н)=Δ.

Множество потенциальных действий ВП можно трансформировать путем формирования одиночных ДВП со знаковыми вариациями амплитуды Y следующим образом. Числа источника данных преобразуют в N-компонентные ДВП, ставя в соответствие числу m источника данных амплитудное значение ДВП Y(m) из диапазона

+Ymax-0 ИЛИ 0-(-Ymax)

с шагом квантования, превышающим уровень шумов тракта на начальном или конечном интервалах 2/TL ДВП.

В результате каждый элемент сформированного таким образом полного множества значений потенциальных ДВП соответствует одному и только одному числу источника данных. Иными словами, вычисляют значения ДВП в точках дискретизации посредством многокомпонентного мультиплексного преобразования (ММП), выраженного функцией Fnn с амплитудой Y(m). Кодируют группы бит - двоичных импульсов источника данных N-компонентными действиями ВП, ставя в соответствие числу m источника данных, выражающему группу, амплитудное значение ДВП Y(m) из диапазона +Y(max) -Y(max) с шагом квантования, превышающим максимальный суммарный уровень внешних шумов и шумов квантования на начальном или конечном интервалах 2/TL ВД ДВП. Диапазон Y(m) равен целому кратному диапазона чисел источника данных с шагом квантования не меньшим

ϑ>ϑs=1/[(S·2/Δ)n·Π(Δ/N(i)]

ϑ>ϑs=1/[(S·2)n·Π(1/N(i))]

ϑ>ϑs=1/[(S·2/(B-H))n·Π((B-H)/(N(i))]

ϑ>ϑs=1/[(S·2)n·Π(1/N(i))]

данного ММП. Здесь ϑs собственный шум формирования, вызываемый ограничением времени существования ДВП, а S·2 - длина ВД ДВП. Формируемые последовательно во времени слова источника данных принимают и преобразуют в посылки - числа Y (m), которые развертывают в наборы значений ДВП, которые сплетают в поток значений ДВП, который преобразуют цифроаналоговым преобразованием в квантованный по уровням напряжений или токов поток действий волновых пакетов (ПДВП), фильтрацией которого получают итоговый непрерывный сигнал. То есть получают поток ДВП, предназначенный для передачи через среду переноса к приемной стороне или для переноса на другую частотную точку, либо получают отфильтрованный входной сигнал приемника с шириной полосы, равной ВП и полностью повторенной частью спектра, которая ограничена плоской частью ВП.

Вычисления границ ПДВП приведены выше в описании общей части способа, соответствующего изобретению.

Выбор конкретного многокомпонентного мультипликативного преобразования ММП (математической формулы ПВП) и частоты дискретизации его значений в данном варианте осуществляют подбором наборов ВЧК (N(i)) путем оптимизации ВЧК, исходя из быстродействия элементов устройства, реализующего способ, ширины выделенных каналов передачи, ширины частотного диапазона каналов, получая в качестве конечного результата удельную (на единицу ширины полосы) и полную скорости передачи.

Дешифрация сигналов составляющих полного потока ДВП приемной стороной основана на определении ЦТ отдельных ДВП, составляющих этот ПДВП.

Следует отметить, что создаваемый передающей стороной полный поток ВП имеет замкнутый спектр и соответствует сигналу, спектр которого заключен в определенных границах и может быть перенесен в любую доступную точку радиодиапазона одним из стандартных методов модуляции, являющейся внешней модуляцией по отношению к ММП. При этом спектр радиосигнала, получаемого внешней модуляцией, может формироваться из различных сигналов, где поток действий ВП расположен либо в верхней области всего радиосигнала, либо в нижней области, свободную же часть области могут занять служебные сигналы (СС).

Сборку последовательности ДВП в поток ДВП (ПДВП), соответствующий последовательности чисел источника данных, осуществляют суммированием всех существующих на текущий момент времени дискретизации значений различных ДВП таким образом, что наивысшие по частоте гармоники -1/TL, входящие в состав соответствующей компоненты каждого ПВП и его ДВП, расположены либо синфазно, либо противофазно. Пополняют сборку ПДВП до полного ПДВП синхросигналом, либо суммируя с ним значения гармоники синхросигнала, не принадлежащей спектру ПДВП, либо регулярно пропуская ввод значений чисел источника данных.

Синхронизация позитивом (посредством дополнительно использованной гармоники) имеет частотный спектр, который отстоит на некоторый интервал от спектра ДВП. Синхронизацию позитивом встраивают в ПДВП путем суммирования значений ДВП с заранее вычисленными значениями гармоники синхросигнала. В результате полный спектр передаваемого сигнала шире спектра отдельного ДВП на величину, равную интервалам распознавания синхросигнала, расположенным симметрично вокруг синхросигнала. Суммарная ширина интервалов распознавания зависит главным образом от избирательности устройства распознавания (узкополосного фильтра синхросигнала) и ВД ДВП, от которого зависит шум за пределами спектра ДВП.

Синхронизацию негативом осуществляют пропуском постановки информации в регулярно повторяемых моментах времени. Спектр синхронизации негативом фактически отсутствует. Поэтому полный спектр (границы спектра) не превышает спектра отдельно взятого ДВП. Расплатой за такой вид синхронизации является понижение скорости передачи информации. Математически это выглядит следующим образом. Выразим условие периодически повторяющихся нулей через одну из периодических функций например косинус. Тогда ввод в формируемую последовательность действий ВП новых действий ВП и уход предшествующих действий ВП, прекративших свое существование, производят в моменты времени, в которых соблюдается равенство

Cos[(Δ/2)t)=0,

то есть с удвоенной частой Δ=2/TL, в которой некоторые регулярно повторяющиеся точки ti, соответствующие равенству

cos[(Δ/2)·ti]=0

не занимаются и используются приемной стороной для синхронизации негативом. При этом интервалы времени Tv между такими событиями определены заранее и переданы приемной стороне на предварительных этапах (либо при изготовлении, либо при установке и т.д., либо на начальной фазе или любой другой фазе сеанса связи) на частоте, равной Δ/2=1/TL, используя оставшиеся точки линейной частоты 2/TL для синхронизации.

Таким образом, в точках, повторяющихся с периодом, равным TL/2, являющихся ЦТ некоторого ДВП, полный поток ДВП принимает значения Y(m), равные значениям соответствующих действий ВП. А при синхронизации негативом входного сигнала, принимает нулевые значения, которые соответствуют нулям фазы синхрочастоты 1/Tv. Величина 1/Tv, отнесенная к скорости передачи, и есть коэффициент понижения скорости передачи. Например, для частоты постановки данных 2/TL этот коэффициент равен TL/(2·Tv).

Варианты оценки ПДВП приемной частью основаны именно на этих свойствах регулярности ядра Fnn.

Следствием из теоремы подобной теореме Котельникова и трансформированной под ПВП является то, что для восстановления исходного непрерывного сигнала формирование синхросигналов необязательно. Поэтому при передаче непрерывных сигналов аппаратура синхронизации отсутствует, а сам поток информации в канале передачи не разбавлен служебной информацией. Что касается передачи числовых последовательностей, то в этом случае восстановить исходную последовательность на приемном конце без синхронизации можно. Но при этом вычислительные мощности, потребные для такого процесса, осуществляемого в реальном времени, существенно превысят сложность аппаратуры, потребной для синхронизации по одному из приведенных выше алгоритмов. Данное утверждение основано, но том факте, что процедура прямого вычисления будет рекурсивной, содержащей 2·S членов, где 2·S длина ВД ДВП в единицах TL.

Способ компенсации понижения скорости передачи информации, происходящего из-за удвоения ширины спектра сигнала вследствие переноса спектра в радиодиапазоне.

Описанная выше процедура формирования ПДВП на частотах переноса, равных целым кратным величины 2/TL, то есть для ММП равных

Fn=Fn n·ехр(j·ΨДВП·t),

где ΨДВП=(2/TL)·n при целых n≥1,

в силу наличия нулевых значений, задаваемых решениями уравнения

ехр(j·ΨДВП·t)=0,

позволяет создать фазово-смещенный поток ДВП, задержанный во времени относительно вышеописанного потока ДВП и идентичный ему. Фазово-смещенный поток ДВП формируют следующим образом. Разбивают последовательность чисел источника данных на две последовательности четных и нечетных по порядку следования чисел источника данных. Формируют два потока значений ДВП - четный и нечетный, состоящих из ДВП, являющихся реакциями на четные и нечетные числа, соответственно, по порядку их следования в последовательности чисел источника данных. Формируют полный поток ДВП (ПДВП) суммированием значений потока четных ДВП со значениями потока нечетных ДВП, центральные точки которых сдвинуты относительно ЦТ потока четных ДВП на время, которое кратно периоду частоты Δ.

Данная процедура пополнения ПДВП фактически является дополнением ПДВП до полного потока ДВП, так как мощность такого потока может быть приближена к максимальному сколь угодно близко, как по частоте постановки данных, так и по шуму.

Выражение в явном виде сдвига подобного канала равно

cos[ΨДВП·t+ϕ]=0,

где ϕ=π/2+2·π·r - фаза компоненты переноса МПП,

ΨДВП=n·Δ - частота трансляционной компоненты (переноса),

Δ=2·2·π/TL,

t - время,

n>r, где r - целое число.

Из приведенного уравнения следует, что при целых n и r больше 0 эффект максимален. Дешифрацию фазово-смещенных потоков ДВП осуществляют переносом радиосигнала на частоту В-Н=Δ, так как получаемый сигнал является ядром того ММП (ПВП), спектр которого ровно в два раза превышает спектр ядра исходного ММП. Отсюда следует, что оптимальным значением является r=n-1.

Частота постановки ДВП в суммарном потоке равна

2·Δ=4·2·π/TL

Скорость передачи информации в суммарном потоке ДВП приближена к величине [ln(Ymax)]·4/TL, которая, учитывая, что при волновых числах компонент, не равных первой компоненте, много больших двойки, так что величина 2·Δ=4·2·π/TL приблизительно равна удвоенной ширине спектра ВП, приближена к теоретическому пределу скорости передачи данных для соответствующих аналоговых каналов.

Получение полного потока ВП для канала среды переноса осуществляют фильтрацией фильтром нижних частот или полосовым фильтром полного потока уровней поля ДВП путем выделения нужного спектра ПДВП из формируемого цифроаналоговым преобразованием набора транслированных спектров ПДВП, порожденных дискретизацией ДВП. При этом перенос спектра несущей частотой возможно осуществить аналоговыми модуляторами, что соответствует ПВП, в котором умножение на трансляционную компоненту осуществляют аналоговыми методами. Результатом операций переноса спектра, как использующих механизм выделения трансляционных составляющих, так и использующих механизм аналоговых переносчиков спектров, является удвоение спектральной ширины ВП. Но, первое, так как ВП по условиям формирования отстоит от точки нулевой частоты на величину Н или n/Td - Н (где 1/Td - частота дискретизации ДВП), то одна из его боковых полос легко локализуется соответствующим фильтром промежуточной частоты. И, второе, вышеописанный механизм повышения плотности информации полностью переносится на аналоговые переносчики спектров. При этом первый канал переносят синусом, а второй канал переносят косинусом частоты ΨДВП. Формирование значений ПДВП второго канала смещено относительно формирования значений первого канала на фазу, равную ϕ=π/2+2·π·r частоты переноса. Сборку каналов осуществляют объединением их на единой нагрузке.

Формирование фазово-смещенных потоков ДВП для частот ΨДВП, много больших Δ, осуществляют раздельно, вплоть до их передачи усилителю мощности. Объединение фазово-смещенных потоков ДВП осуществляют путем суперпозиции четного и нечетного радиосигналов таким образом, что задержка между ЦТ ДВП двух радиосигналов равна половине интервала времени постановки информации в любом радиосигнале.

Дешифрация полного потока действий ВП приемной стороной основана на определении ЦТ составляющих его действий ВП.

Процедура выделения ЦТ имеет варианты, обусловленные вариантами формирования ПДВП. Это, при синхронизации позитивом, определение ЦТ с помощью одной из частот сопровождения (ЧС) - кратной 2/TL. Либо при синхронизации негативом используют регулярность структуры ДВП. Дешифрацию уровней значений полей в ЦТ полного потока ДВП, в двоичные числа Y(m), равные двоичным числам источника данных передатчика, осуществляют определением ЦТ с нулевыми значениями, которые были заложены в качестве частоты синхронизации в полный поток ДВП на этапе его формирования.

Формирование местоположения сигнала.

Актуальность преобразования спектра ДВП внешними по отношению к основному ПВП трансляторами вызвана тем фактом, что частота ΨДВП полностью вычисленного ДВП ограничена быстродействием элементов реального устройства, осуществляющих суммирование. Так для амплитудного варианта модулирования двухкомпонентного ВП с погрешностью формирования -70 дБ, то есть с диапазоном Y(m) не менее 12 двоичных разрядов, без учета шумов, привносимых элементами формирования и средой переноса, время существования равно 20 единиц TL. Поэтому при периоде дискретизации Tk=10-6 сек, при использовании накапливающего сумматора такт суммирования должен быть не больше Td=5·10-8.

При использовании параллельного сумматора это время увеличится, по меньшей мере, в 20 раз, т.е. Td=Tk.

Вследствие этого создание устройств на сигнальных процессорах с ΨДВП>5 МГц затруднительно. Но специальный многопроцессорный (с соответствующим количеством арифметико-логических преобразователей) вариант, смещает границу ΨДВП до 30 МГц при соблюдении перечисленных выше условий.

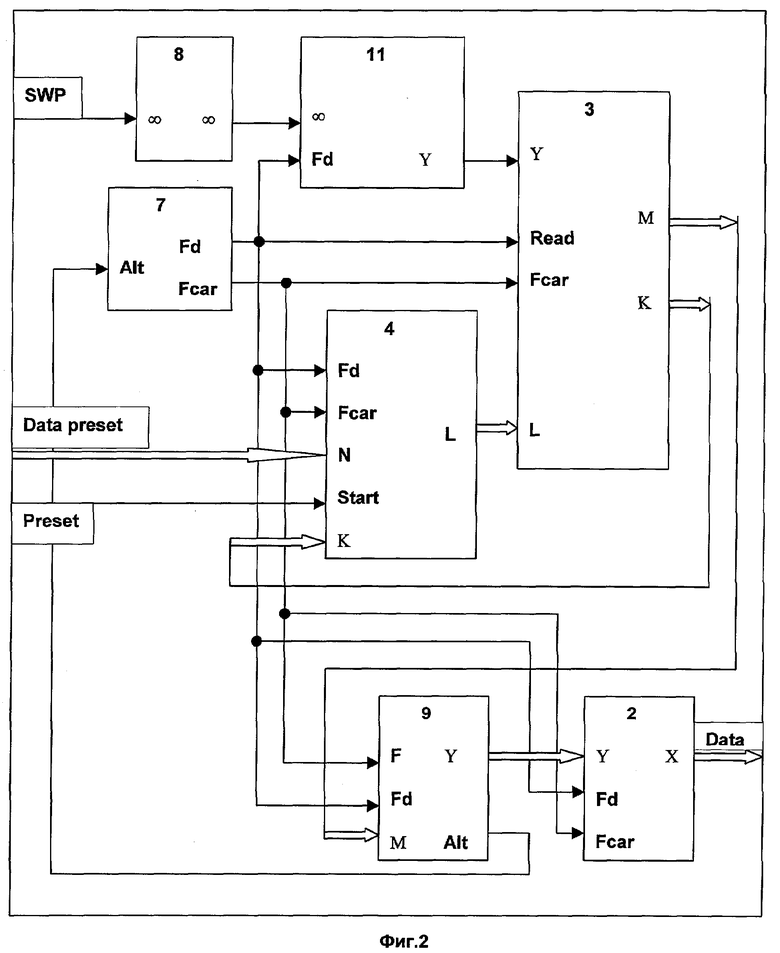

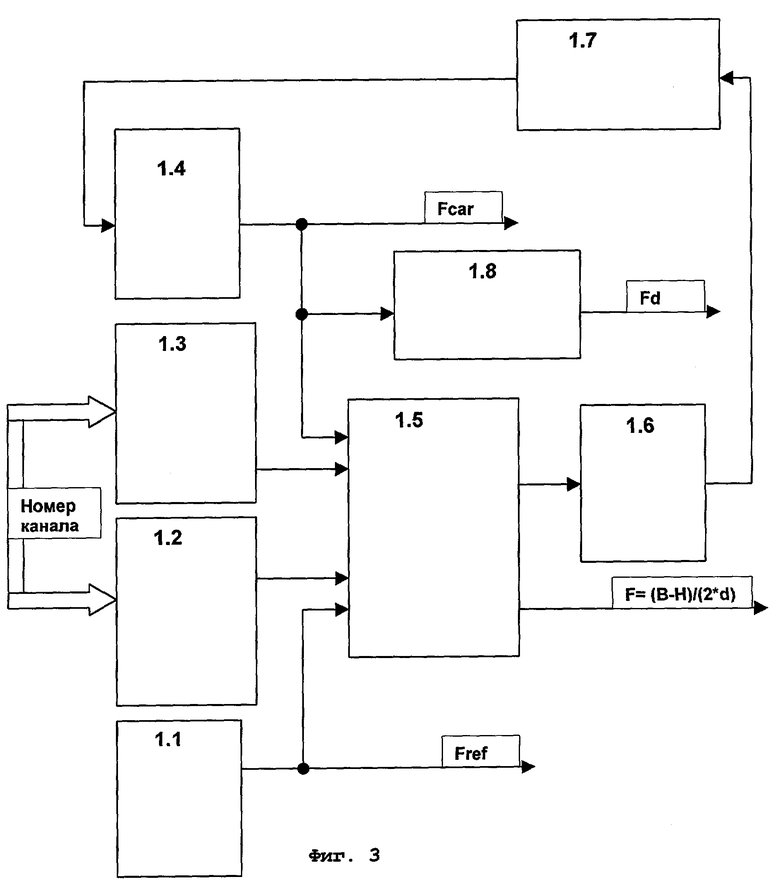

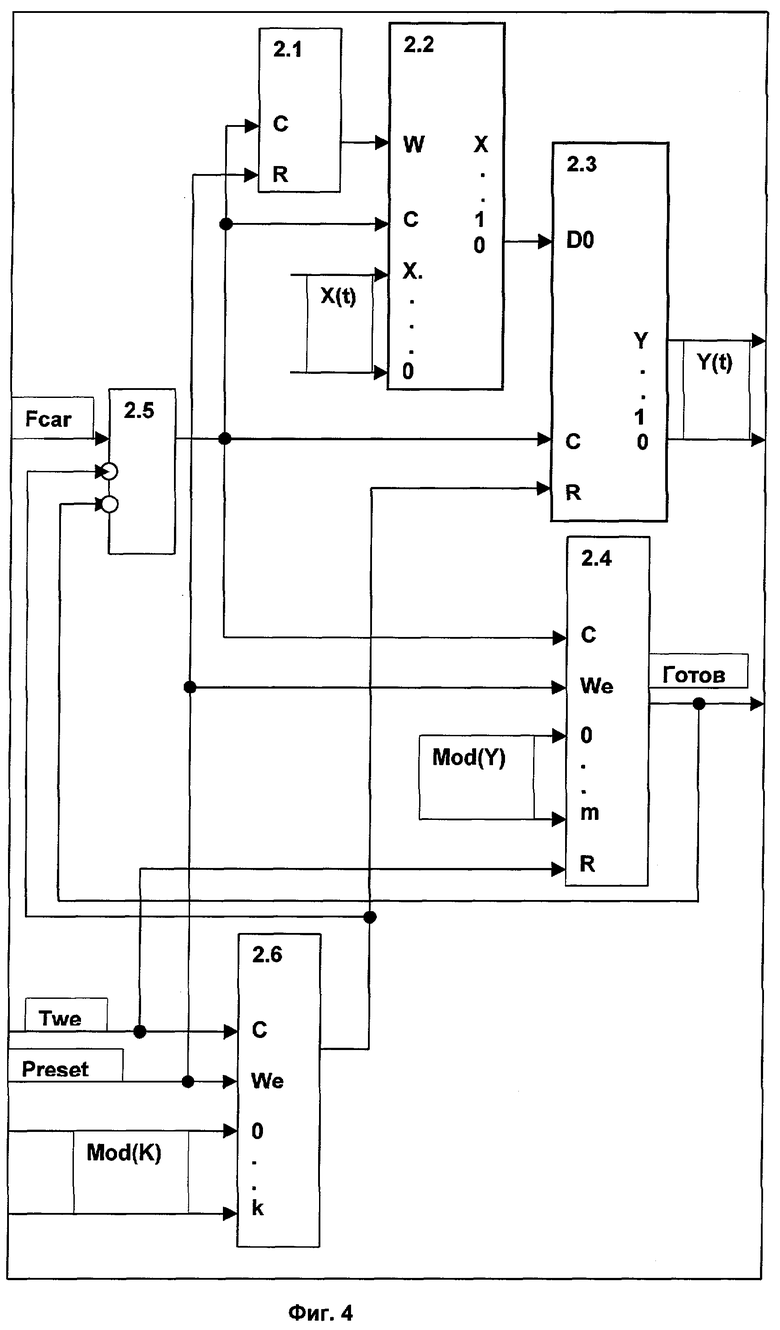

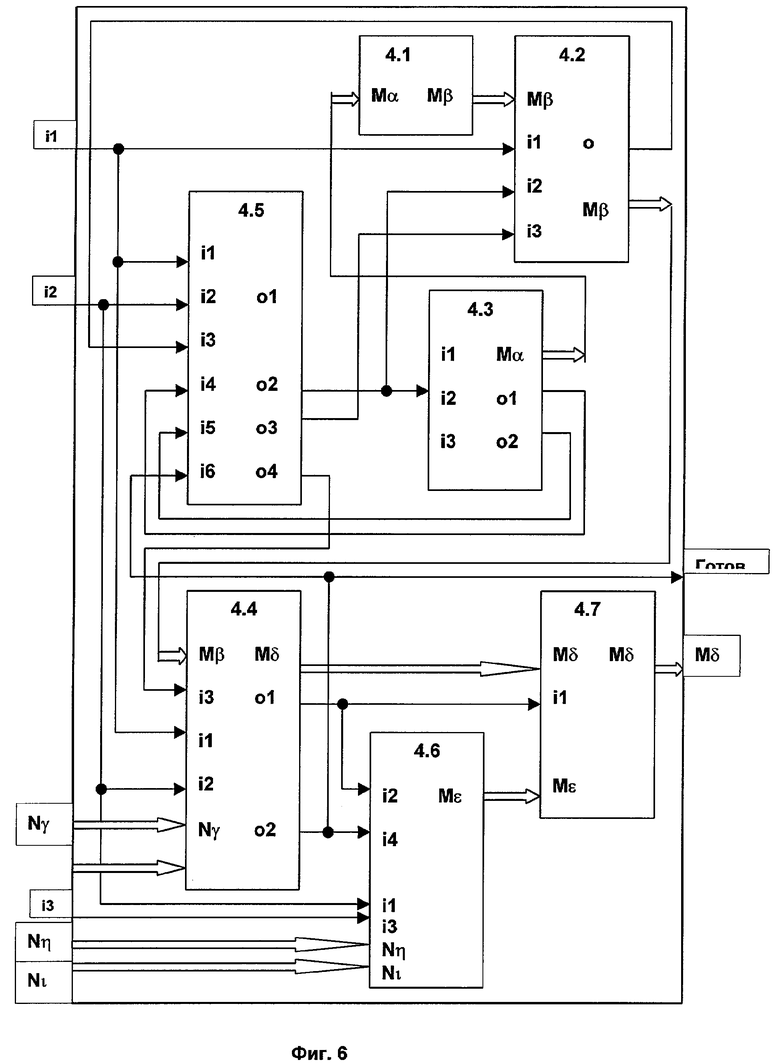

И, наконец, укороченный сигнал, формируемый без использования сумматора методом частотной (широтной) или фазовой модуляций волновых пакетов, смещает границу ΨДВП выше 500 МГц при соблюдении перечисленных выше условий. В этом случае время расходуется только на считывание и преобразование уровня цифроаналоговым преобразователем, поэтому указанная выше цифра в действительности должна быть меньше быстродействия цифроаналогового преобразователя, по меньшей мере, в два раза.