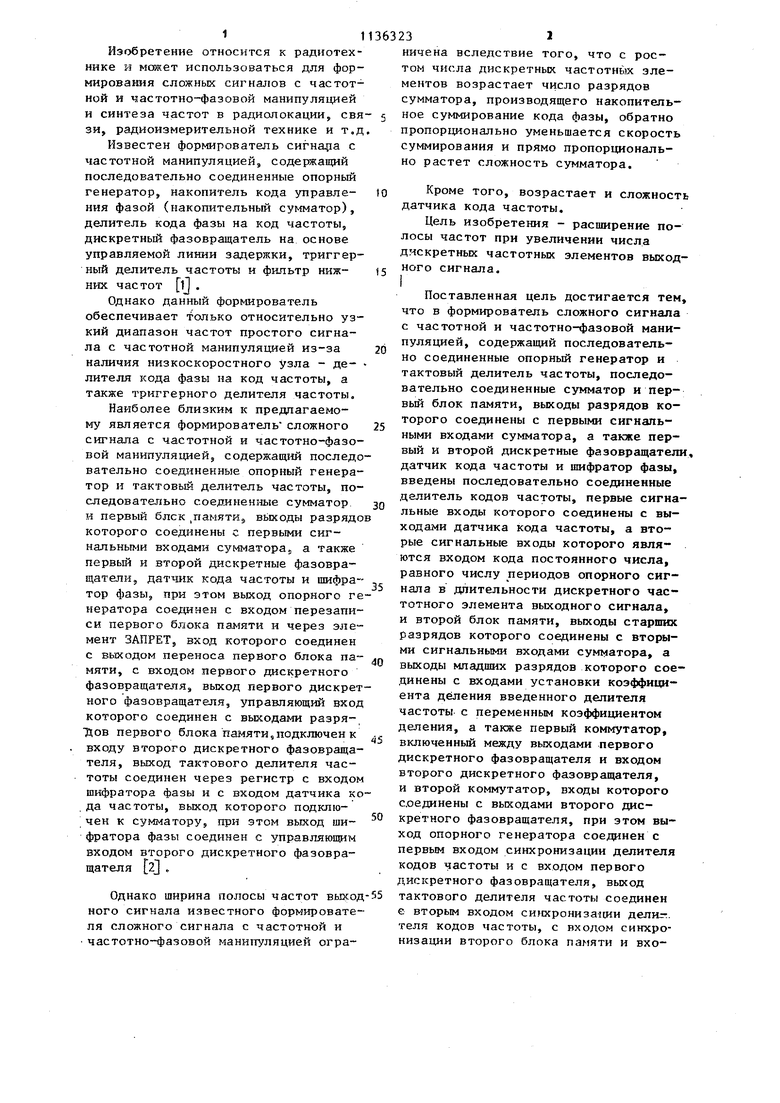

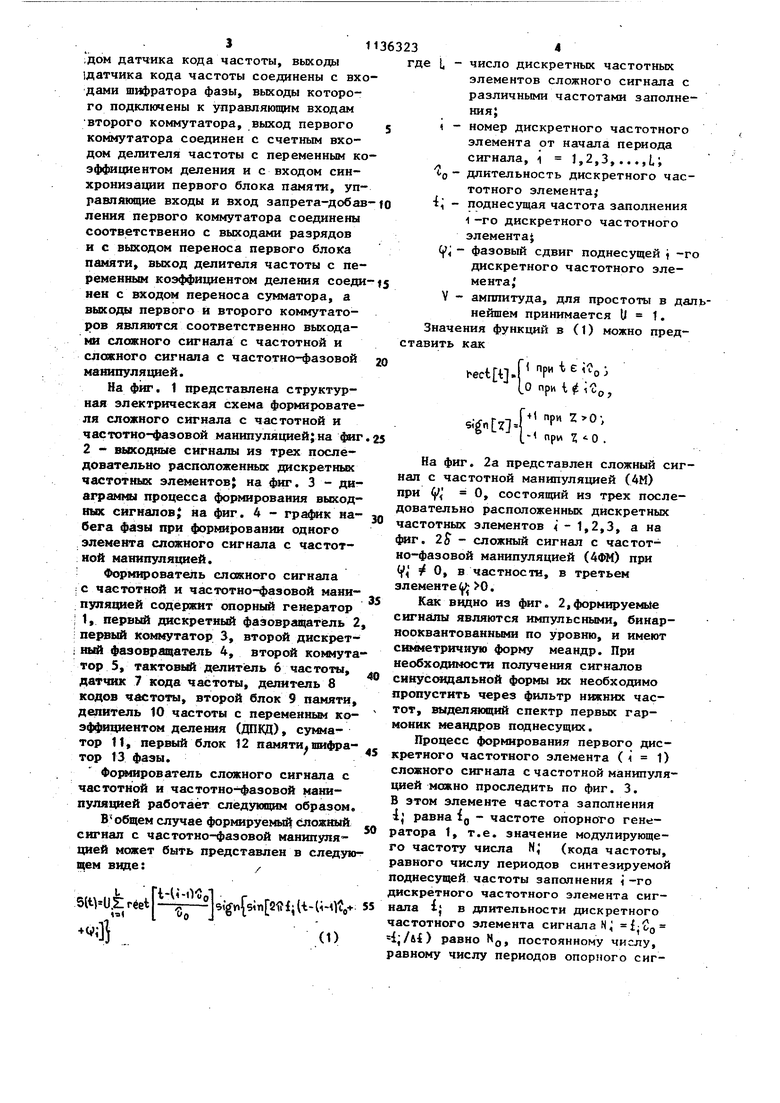

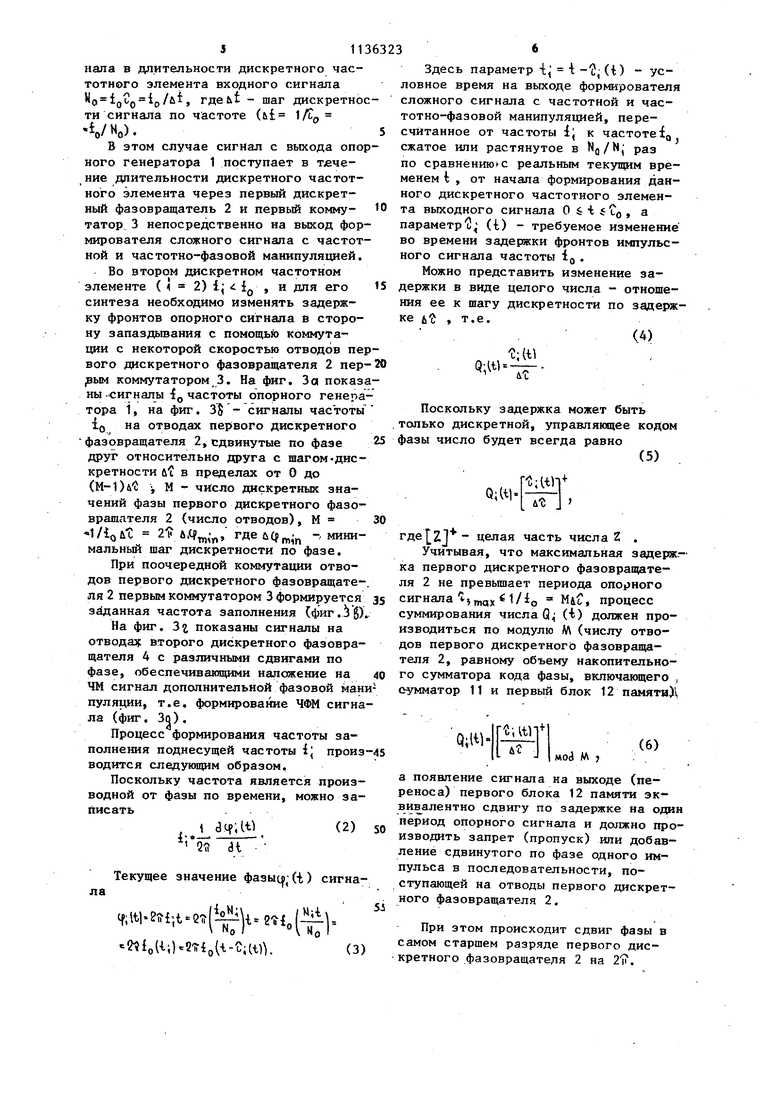

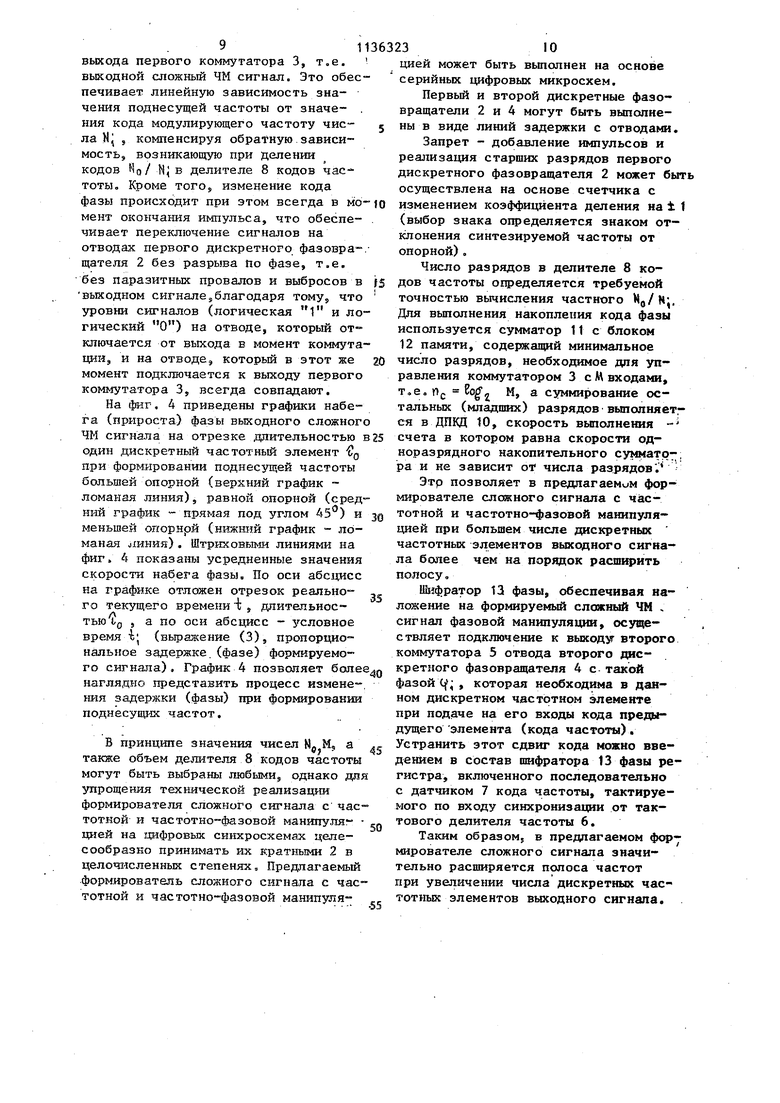

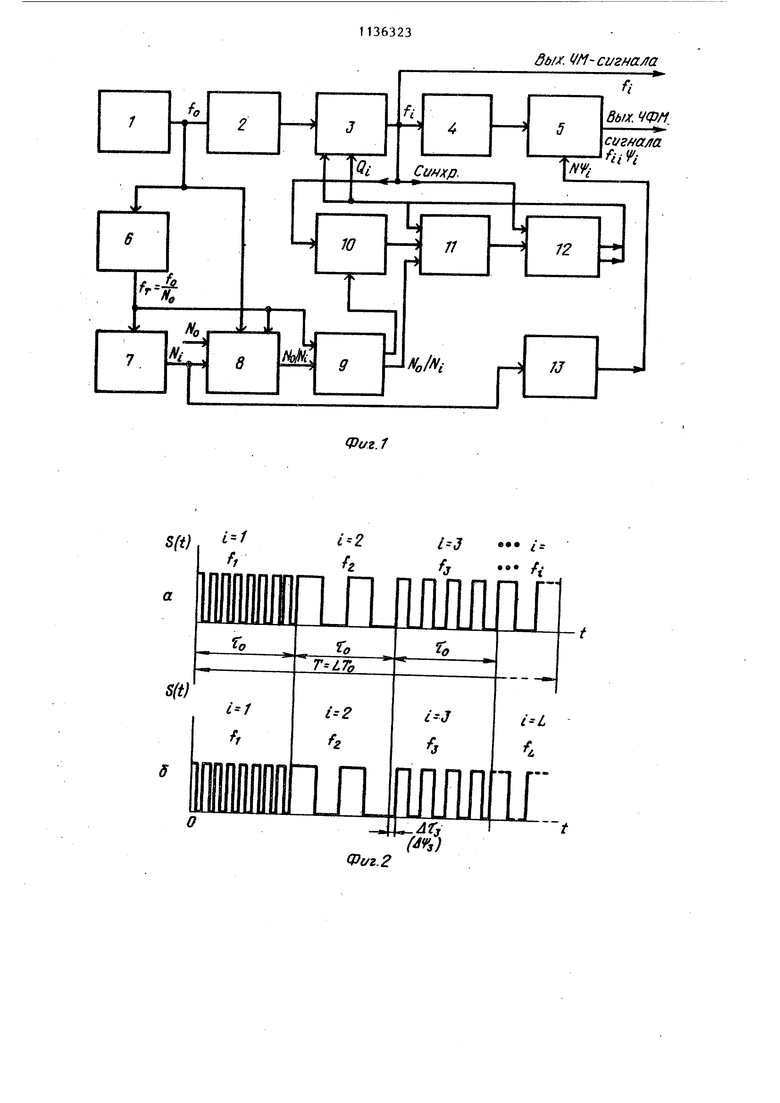

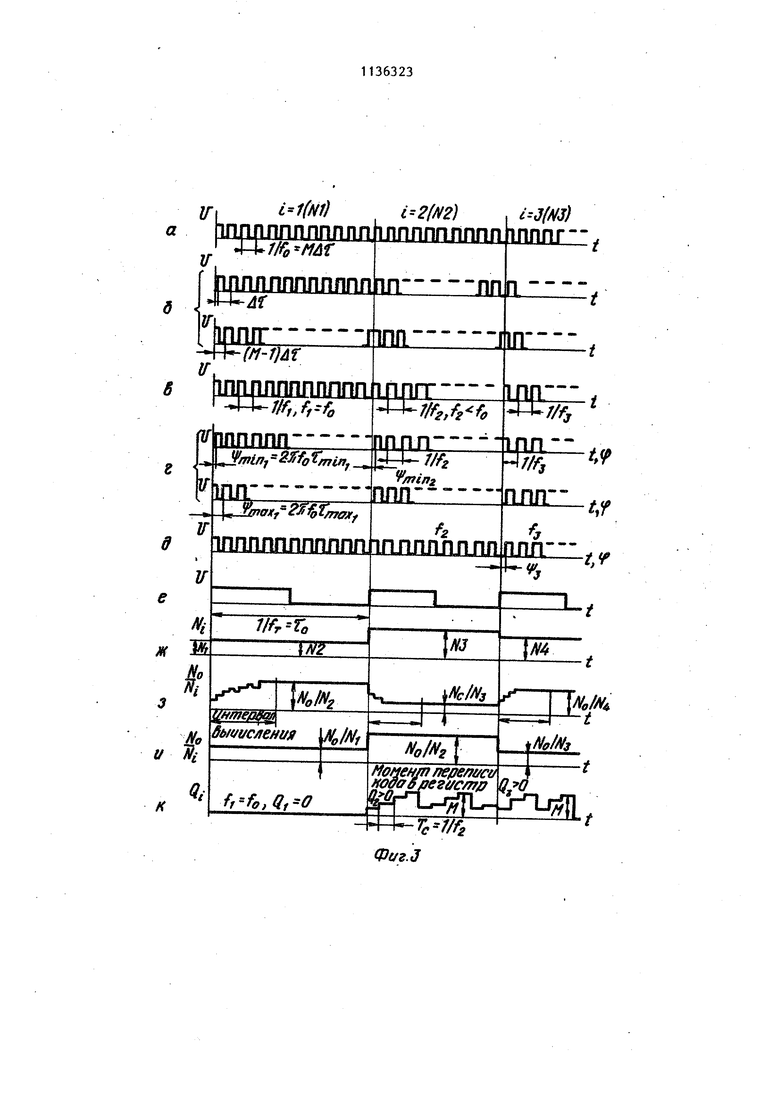

Изобретение относится к раднотехнике и мсжет использоваться для формирования сложных сигналов с частотной и частотно-фазовой манипуляцией и синтеза частот в радиолокации, свя зи, радиоизмерительной технике и т.д Известен формирователь сигнара с частотной манипуляцией, содержащий последовательно соединенные опорный генератор, накопитель кода управления фазой (накопительный сумматор), делитель кода фазы на код частоты, дискретный фазовращатель на основе управляемой линии задержки, триггерный делитель частоты и фильтр нижних частот lj . Однако данный формирователь обеспечивает только относительно узкий диапазон частот простого сигнала с частотной манипуляцией из-за наличия низкоскоростного узла - делителл кода фазы на код частоты, а также триггерного делителя частоты. Наиболее близким к предпагаемому является формирователь сложного сигнала с частотной и частотно-фазовой манипуляцией, содержащий последо вательно соединенные опорный генератор и тактовый делитель частоты, последовательно соединеннь е сумматор и первый блек памятИд ВЬЕХОДЫ разрядо которого соединены с первыми сигнальными входами сумматора., а также первый и второй дискретные фазовращатели, датгшк кода частоты и щифратор фазы, при этом вькод опорного ге нератора сое;щнен с входом перезаписи первого блока и через элемент ЗАПРЕТ, вход которого соединен с выходом переноса первого блока памяти, с входом первого дискретного фазовращателя, выход первого дискрет ного фазовращателя, управляющий вход которого соединен с выходами разря7JOB первого блока памяти,подключен к входу второго дискретного фазовращателя, выход тактового делителя частоты соединен через регистр с входо шифратора фазы и с входом датчика к да частоты, выход которого подключен к сумматору, при этом выход шифратора фазы соединен с управляюиснм входом второго дискретного фазовращателя 2 Однако ширина полосы частот выхо ного сигнала известного формировате ля сложного сигнала с частотной и частотно-фазовой мани1туляцией ограничена вследствие того, что с ростом числа дискретных частотных злементов возрастает число разрядов сумматора, производящего накопительное суммирование кода фазы, обратно пропорционально уменьшается скорость суммирования и прямо пропорционально растет сложность сумматора. Кроме того, возрастает и сложность датчика кода частоты. Цель изобретения - расширение полосы частот при увеличении числа дискретных частотных элементов выходного сигнала. i Поставленная цель достигается тем, что в формирователь сложного сигнала с частотной и частотно-фазовой манипуляцией, содержащий последовательно соединенные опорный генератор и тактовый делитель частоты, последовательно соединенные сумматор и первый блок памяти, выходы разрядов которого соединены с первыми сигнальными входами сумматора, а также первый и второй дискретные фазовращатели, датчик кода частоты и шифратор фазы, введены последовательно соединенные делитель кодов частоты, первые сигнальные входы которого соединены с выходами датчика кода частоты, а вторые сигнальные входы которого являются входом кода постоянного числа, равного числу периодов опорного сигнала в длительности дискретного частотного элемента выходного сигнала, и второй блок памяти, выходы старших разрядов которого соединены с вторыми сигнальными входами сумматора, а выходы младщих разрядов которого соединены с входами установки коэффициента деления введенного делителя частоты- с переменным коэффициентом деления, а также первый коммутатор, включенный между выходами первого дискретного фазовращателя и входом второго дискретного фазовращателя, и второй коммутатор, входы которого соединены с выходами второго дискретного фазовращателя, при зтом выход опорного генератора соединен с первым входом синхронизации делителя кодов частоты и с входом первого дискретного фазовращателя, выход тактового делителя частоты соединен с вторым входом сиюсрониза-ции делшт. теля кодов частоты, с входом синхронизации второго блока памяти и вхо;дом датчика кода частоты, выходы 1датчика кода частоты соединены с дами шифратора фазы, выходы которого подключены к управляющим входам второго коммутатора, выход первого коммутатора соединен с счетным входом делителя частоты с переменным к эффициентом деления и с входом синхронизации первого блока памяти, уп равлякицие входы и вход запрета-добав ления первого коммутатора соединены соответственно с выходами разрядов и с выходом переноса первого блока памяти, выход делителя частоты с пе ременным коэффициентом деления соеди ней с входом переноса сумматора, а выходы первого и второго коммутаторов являются соответственно выходами сложного сигнала с частотной и сложного сигнала с частотно-фазовой манипуляцией. На фиг, 1 представлена структурная электрическая схема формирователя сложного сигнала с частотной и частотно-фазовой манипуляцией;на фиг 2 - выходные сигналы из трех последовательно расположенш 1х дискретньвс частотных элементов на фиг. 3 - диаграммы процесса формирования выходных сигналов; на фиг. 4 - набега фазы при формировании одного элемента сложного сигнала с частотной манипуляцией. Формирователь елоокного сигнала : с частотной и частотно-фазовой манипуляцией содержит опорный генератор ; 1, первый дискретный фазовра1цат1ель 2 I пертый Коммутатор 3, второй дискретi ный фазоврщатель 4, второй коммута тор 5, тактовый делит ель 6 час то1ы, датчик 7 кода частоты, делитель 8 кодов частоты, второй блок 9 памяти, делитель 10 частоты с переменным коэффициентом деления (ДЩКД), суьшатор 11, первый блок 12 памяти вгафратор 13 фазы. Фо1 4ирователь сложного сигнала с частотной и частотно-базовой манипуляцией работает следую1цим образом. Вобщем слзгчае формируемый сложный сигнал с частотно-фазовой манипуляцией может быть представлен в следую щем вцде:/ i-U-iKol (t-(iM)V вх 23 1 - число дискретных частотных где элементов сложного сигнала с различными частотами заполнения; - номер дискретного частотного элемента от начала периода сигнала, i 1,2,3,...,,; длительность дискретного частотного элемента, прднесущая частота заполнения 1 -го дискретного частотного элемента (ft - фазовый сдвиг поднесущей -го дискретного частотного элемента, V - амплитуда, для простоты в дальнейшем принимается U 1. Значения функций в (1) можно представить как 1 при i е а . О при i ;-; .,..-, Г + 1 при . На фиг. 2а представлен сложный сигнал с частотной манипуляцией (4М) при , 0, состоящий из трех последовательно расположенных дискретных частотных элементов 4-1,2,3, а на фиг. 2 - сложный сигнал с частотно-фазовой манипуляцией (4ФМ) при ij, О, в частности, в третьем элементе 0. Как видно из фиг. 2,формируемые сигналы являются импульсными, бинарнооквантованными по уровню, и имеют симметричную форму меандр. При необходимости получения сигналов синуссяздальной формы их необходимо пропустить через фильтр нижних частот, выделяющий спектр первых гармоник меандров поднесущих. Процесс формирования первого дискретного частотного элемента (i 1) сложного сигнала с частотной манипуляцией можно проследить по фиг. 3. В этом элементе частота заполнения Ij равна ig - частоте опорного генератора 1, т.е. значение модулирующего частоту числа Nj (кода частоты, равного числу периодов синтезируемой поднесущей частоты заполнения i-го искретного частотного элемента CHI- нала ij в длительности дискретного астотного элемента сигнала N, f-Co ij/4f) равно HO, постоянному числу, авному числу периодов опорного сигнала в длительности дискретного частотного элемента входного сигнала Ho ±Qoo to/bi, - шаг дискретнос ти сигнала по частоте (ь I/LO VV. В этом случае сигнал с вькода опор ного генератора 1 поступает в т чение длительности дискретного частотного элемента через первый дискретный фазовращатель 2 и первый коммутатор 3 непосредственно на выход формирователя сложного сигнала с частотной и частотно-фазовой манипуляцией. Во втором дискретном частотном элементе ( 2) i; - i , и для его синтеза необходимо изменять задержку фронтов опорного сигнала в сторону запаздьтания с помощью коммутации с некоторой скоростью отводов пер вого дискретного фазовращателя 2 перрым коммутатором 3. На фиг. За показа ны -сигналы IQ частоты опорного генера тора 1, на фиг. сигналы частоты i.Q на отводах перового дискретного фазовращателя 2, сдвинутые по фазе друг относительно друга с шагом-дискретности й в пределах от О до (м-DAS i М - число дискретных значений фазы первого дискретного фазоврашателя 2 (число отводов), М 1/tout 27 й.(-, гделд. -, минимальный шаг дискретности по фазе. При поочередной коммутации отводов первого дискретного фазовращателя 2 первым коммутатором 3 формируется заданная частота заполнения (фиг . §) На фиг, 3 показаны сигналы на отводаз второго дискретного фазовращателя 4 с различными сдвигами по фазе, обеспечивакяцими наложение на ЧМ сигнал дополнительной фазовой ман пуляции, т.е. формирование ЧФМ сигна ла (фиг. Зо). Процесс формирования частоты заполнения поднесущей частоты i произ водится следующим образом. Поскольку частота является производной от фазы по времени, можно записать1 JCf;(t (2) 2 dt Текущее значение фaзыt ;(i) сигна4iltbeiM;tQ7(-5jii i 2ti - ;foHi).2iri i-cutn. (3) Здесь параметр t 1: -, (t) - условное время на выходе формирователя сложного сигнала с частотной и частотно-фазовой манипуляцией, пересчитанное от частоты ij к частоте о сжатое или растянутое в Nj/N, раз по сравнению с реальным текзпцим временем t , от начала формирования данного дискретного частотного элемента выходного сигнала О i t Сд , а параметр 2 (О - требуемое изменение во времени задержки фронтов импульсного сигнала частоты IQ. Можно представить изменение задержки в виде целого числа - отношения ее к шагу дискретности по задержке fcJ , т.е. Поскольку задержка может быть только дискретной, управляющее кодом фазы число будет всегда равно fSiWl где 21 целая часть числа Z . Учитывая, что максимальная задерж.ка первого дискретного фазовра1цателя 2 не превышает периода опорного сигнала 1/±о if, процесс суммирования числа Q (i) должен производиться по модулю Н (числу отводов первого дискретного фазовращателя 2, равному объему накопительного сумматора кода фазы, включающего , сумматор 11 и первый блок 12 памятн) a появление сигнала на выходе (переноса) первого блока 12 памяти эквивалентно сдвигу по задержке на ода1н период опорного сигнала и должно производить запрет (пропуск) или добавление сдвинутого по фазе одного импульса в последовательности, поступающей на отводы первого дискретного фазовращателя 2, При этом происходит сдвиг фазы в самом старшем разряде первого дискретного фазовращателя 2 на 2и. Число Q, (t ), управляющее задержкой (фазой), можно записать в следую щем ввде: oiT/ (у- Wo N: - ъ--о i ij Из (7) следует, что для синтеза частоты заполнения fj , отличной от частоты ig опорного генератора 1, необходимо, чтобы в момент начала тактового импульса, т.е. начала дискретного частотного элемента (фиг.Зе датчик 7 кода частоты вьщал число N; для следующего элемента (на фиг. ЗА момент начала 1-го дискретного частотного элемента - число Мл для второго-дискретного частотного элемента) . В делителе 8 кодов частоты делится код постоянного числа Ng на И , поступаквдий из датчика 7 кода частоты (в 1-ом дискретном частотном элементе V эа время меньшее длительности -дискретного частотного элемента tp (фиг. ЗО . Деление двоичных кодов может выполняться обычным способом, используемым в цифровых вычислительных машинах, например, путем вычитания делителя из делимого на ко инационном cyfiMaTope-вЕЛЧитателе и сдвига результата в регистре до получения заданной точности вычисления частного. В момент начала следующего тактового импульса частное (в данном случае Яд/Rj) переписывается во второй блок 9 памяти из делителя8 кодов частоты (фиг. За). С выходов его старших р 13р5ЩовЛ(, М поступает код на первью входы сумматора 11, а с выходов нладших (остальных) разрядов - на входы установки коэффициент Деления ЦЦЩ 10. Затеи производится с периодом 1/i (в данном случае - с периодом l/ig) в сумматоре 11 с блоком 12 памяти суммирование (накопление) кода фазы Qj(t) в соответствии с формулой (7) (фиг. Эх), код Q; (-t) подается с выхо дов разрядов блока 12 памяти на входы первого коммутатора 3 для коммутации отводов, а сигнал с выхода ; переноса - на вход запрета-добавлени первого дискретного фазовращателя 2. При этом выходные импульсы ДПКД 10 поступают на вход переноса сумматора 11, добавляя в чиcлoQi(t) результат суммирования в ДПКД 10 кода младших разрядов. Накопление кода фазы в сумматоре 11 осуществляется путем прибавления к входным числам на первых и вторых сигнальных входах кода с выхода первого блока 12 памяти, подаваемого на вторые входы сумматора 11. При объеме сумматора 11 и блока 12 памяти, равном М, процесс суммирования в соответствии с (7) автоматически производится по модулю М, а переполнение (импульс переноса) обеспечивает добавление или запрет фазового сдвига на 2и в первом дискретном фазовращателе 2, Для лучшей наглядности значения параллельных кодов чисел на фиг. 3%.Зк показаны условно в виде уровней, пропорциональных значениям кодов этих чисел. В момент поступления следующего (на фиг. Зе - третьего) тактового импульса вьппеописанные процессы повторяются, из делителя 8 кодов частоты вычисленное во втором элементе частное NO/ N вьщается во второй блок 9 памяти, с него - на ДПКЦ Ю и сумматор 11, далее в сумматоре IT и блоке 12 памяти осуществляется цифровое интегрирование - накопление кода фазы и управления сдвигом фазы в третьем дискретном частотном элементе, обеспечивая синтез поднесущей частоты i . После выдачи из датчика 7 кода частоты всех кодов L дискретных частотных элементов сложного сигнала с частотной манипуляцией начинается формирование следующего периода этого сигнала. При этом с приходом каждого очередного тактового импульса с тактового делителя б частоты датчик 7 кода частоты выдает очередное значение кода частоты, оно вносится в делитель 8 кодов частоты (с обнулением хранившегося в нем предьщущего значения чисел), вновь вычисляется частное, производится накопление кода фазы и задержка фронтов опорного сигнала с требуемой скоростью для синтеза нужной частоты заполнения. в качестве импульсов синхрониэации переписи числа в первом блоке 12 памяти используются импульсы с

выхода первого коммутатора 3, т.е. выходной сложный ЧМ сигнал. Это обеспечивает линейную зависимость значения поднесущей частоты от знача- . ния кода модулирующего частоту числа Hj 5 компенсируя обратную зависимость, возникающую при делении кодов HO/ Щ в делителе 8 кодов час-тоты. Кроме Toroj изменение кода фазы происходит при этом всегда в момент окончания импульса, что обеспечивает переключение сигналов на отводах первого дискретного фазовра-/ щателя 2 без разрыва По фазе, т.е. без паразитных провалов и выбросов в выходном сигналеSблагодаря Тому, что уровни сигналов (логическая 1 и логический О) на отводе, который отключается от выхода в момент коммутации, и на отводе, который в этот же момент подключается к выходу первого коммутатора 3, всегда совпадают.

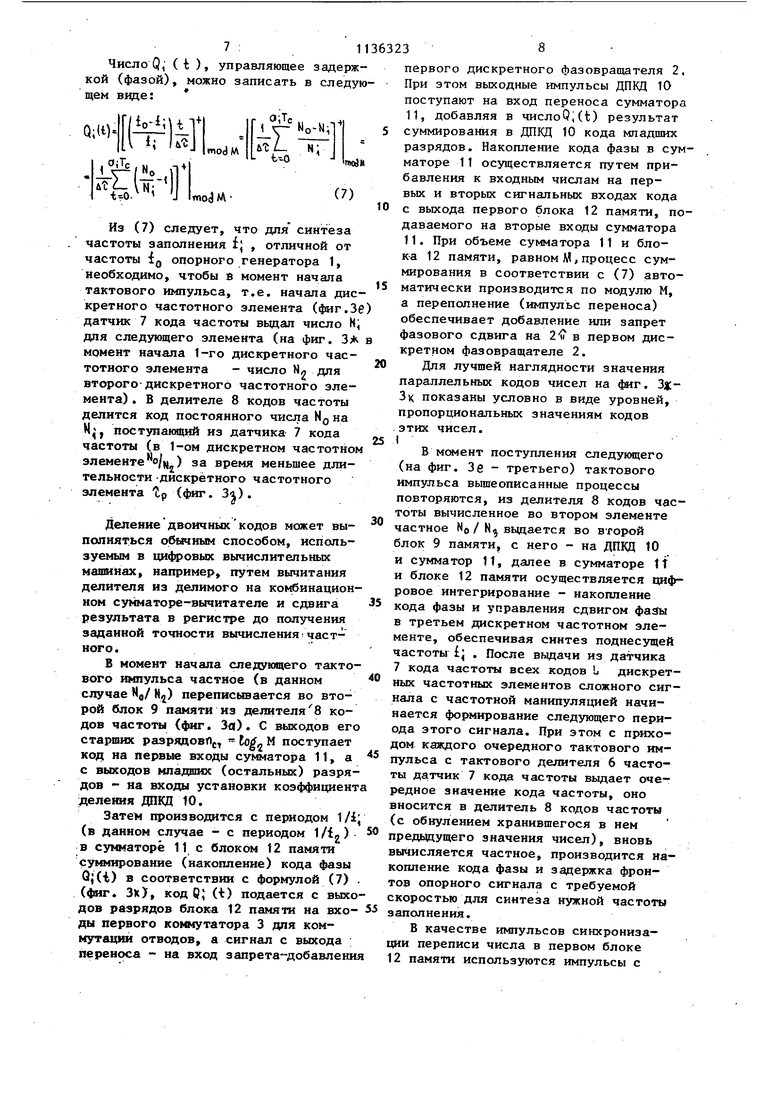

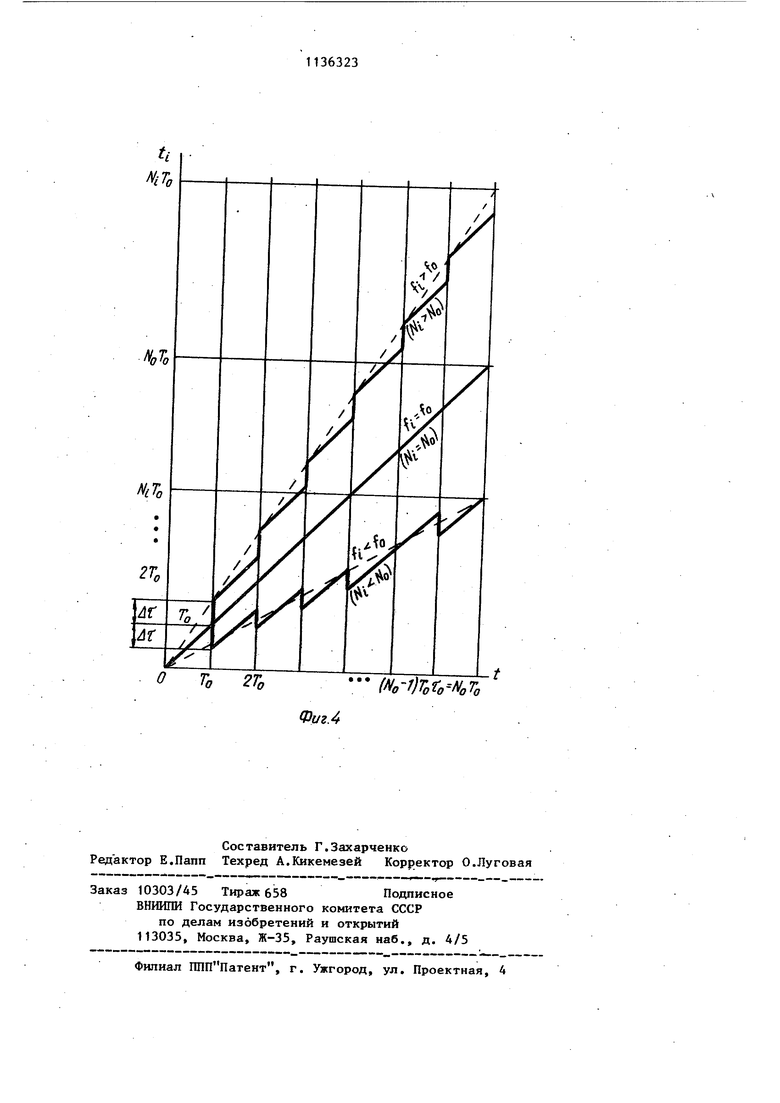

На фиг, 4 приведены графики набега (прироста) фазы выходного сложного ЧМ сигнала на отрезке длительностью в один дискретный частотный элемент д при формировании поднесущей частоты большей опорной (верхний график ломаная линия), равной опорной (средний график Прямая под углом 45) и меньшей опорнрй (нижний график - ломаная JIHHHH) . Штриховыми линиями на фиг, 4 показаны усредненные значения скорости набега фазы. По оси абсцисс на графике отложен отрезок реального текущего времени t , длительноетью tg 5 а по оси абсцисс - условное время i;5 (выралсение (3), пропорциональное задержке.(фазе) формируемого сигнала). График 4 позволяет более наглядно представить процесс изменения задержки (фазы) при форьшровании поднесущик частот.

В принципе значения чисел N М, а также объем делителя 8 кодов частоты могут быть выбраны любыми, однако для упрощения технической реализащ-ш формирователя сложного сигнала с час тотной и частотно-фазовой маняпуля- цией на хдафровык синхросхемах целесообразно приниьзать их кратными 2 в целочисленных степенях. Предлагаемый формирователь сложного сигнала с частотной и частотно-фазовой манипуля

- цией может быть вьтолнен на основе серийных цифровых микросхем.

Первый и второй дискретные фазовращатели 2 и 4 могут быть выполнены в виде линий задержки с отводами.

Запрет - добавление импульсов и реализация старших разрядов первого дискретного фазовращателя 2 может бы осуществлена на основе счетчика с изменением коэффициента деления на ± (выбор знака определяется знаком отклонения синтезируемой частоты от опорной).

Число разрядов в делителе 8 кодов частоты определяется требуемой точностью вычисления частного Mj/Hj. Для выполнения накопления кода фазы используется сумматор 11 с блоком 12 памяти, содержащий минимальное число разрядов, необходимое дпя управления коммутатором 3 с М входами, т.е. Og ogg М, а суммирование остальных (младших) разрядов выполняет ся в ДПКД 10, скорость выполнения счета в котором равна скорости одноразрядного накопительного сумматрра и не зависит от числа разрядов .

Этр позволяет в предлагаемим формирователе сложного сигнала с частотной и частотно-фазовой манипуляцией при большем числе дискретных частотных элементов выходного сигнала более чем на порядок расширить полосу,

Шифратор 13 фазы, обеспечивая наложение на формируемый сложный ЧМ . сигнал фазовой манипуляции, осзпцествляет подключение к выходу второго коммутатора 5 отвода второго даскретного фазовращателя 4 с такой фазойЧ , которая необходима в данном дискретном частотном элементе при подаче на его входы кода предыдущего элемента (кода частоты). Устранить этот сдвиг кода можно введением в состав шифратора 13 фазы регистра, включенного последовательно с датчиком 7 кода частоты, тактируемого по входу синхронизации от тактового делителя частоты 6,

Таким образом, в предлагаемом формирователе сложного сигнала значительно расширяется полоса частот при увеличении числа дискретных частотнык элементов выходного сигнала.

dbf. W-ci/zHu/ia

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь сигналов с частотно-фазовой манипуляцией | 1981 |

|

SU1021013A1 |

| Формирователь линейно-частотно-модулированных колебаний | 1982 |

|

SU1069126A1 |

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1385239A1 |

| Синтезатор частоты с частотной модуляцией | 1986 |

|

SU1345343A1 |

| Измеритель частотных ошибок | 1984 |

|

SU1291890A1 |

| Частотный манипулятор | 1980 |

|

SU873450A1 |

| Формирователь линейно-частотно-модулированных колебаний | 1982 |

|

SU1072247A1 |

| Синтезатор линейно-частотно-модулированныхКОлЕбАНий | 1978 |

|

SU830632A1 |

| Устройство для формирования сложного сигнала с частотной и частотно-фазовой манипуляцией | 1978 |

|

SU777871A1 |

| КОРРЕЛЯЦИОННЫЙ ПРИЕМНИК ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МОДУЛЯЦИЕЙ | 2014 |

|

RU2548010C1 |

ФОРМИРОВАТЕЛЬ СЛОЖНОГО СИГНАЛА С ЧАСТОТНОЙ И ЧАСТОТНО-ФАЗОВОЙ МАНИПУЛЯЦИЕЙ, содержащий последовательно соединенные опорный генератор и тактовый делитель частоты, последовательно соединенные сумматор и первый блок памяти, вькоды разрядов которого соединены с первыми сигнальными входами сумматора, а также первый и второй дискретные фазовращатели, датчик кода частоты и шиф;ратор фазы, отл ич ающийс я тем, что, с целью расширения полосы частот при увеличении числа дискретных частотных элементов выходного сигнала, в него введены последовательно соединенные делитель кодов частоты, первые сигнальные входы которого соединены с выходами датчика кода частоты, а вторые сигнальные вхо;ДЫ которого являются входом кода постоянного числа, равного числу периодов опорного сигнала в длительности дискретного частотного элемента выходного сигнала, и второй блок памяти, выходы старших разрядов которого соединены с вторыми сигнальными одами сумматора, а выходы младших разрядов которого соединены с входаi ми установки коэффициента деления I введенного делителя частоты с пере-, мэнным коэффициентом деления, а также первый коммутатор, включенный между выходами первого дискретного фазовращателя и входом второго дискретного фазовращателя, и второй коммутатор, входы которого соединены с выходами второго дискретного фазовращателя, при этом выход опорного генератора соединен с первым входом синхронизации делителя кодов часто-, ты и с входом первого дискретного фазовращателя, выход тактового делителя частоты соединен с вторым входом § синхронизации делителя кодов частоты, с входом синхронизации второго блока CfJ памяти к входом датчика кода частоты, выходы датчика кода частоты соединены с входами шифратора фазы, выходы которого подключены к управляю-: щим входам второго коммутатора,выходi первого коммутатора соединен со счетным входом делителя частоты с переменным коэффициентом деления и с входом синхронизации первого блока памяти, управляющие входы и вход запрета - добавления первого коммутатора соединены соответственно с. выходами разрядов и с выходом переноса первого блока памяти, выход делителя частоты с переменным коэффициентом деления соединен с входом переноса сумматора, а вькоды перво. го и второго коммутаторов являются соответственно выходами сложного сигнала с частотной и сложного сигнала с частотно азовой манш1уля1щей.

Фиг.7

T-LTo

i-1

fr fz

S f

Фf/г.J

TO 2To (No-l)

Фиг.4

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для формирования импульсных последовательностей с заданным законом изменения фазы | 1979 |

|

SU862134A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для формирования сложного сигнала с частотной и частотно-фазовой манипуляцией | 1978 |

|

SU777871A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-01-23—Публикация

1982-03-30—Подача