1 1

Изобретение относится к вычислительной технике, в частности к средствам контроля и диагностики неисправностей логических схем.

Цель изобретения - повьш1ение достоверности за счет исключения ложных комбинаций сигналов на входах дешифратора при распознавании мно гократных переходов из О в

О в Г- и наоборот.

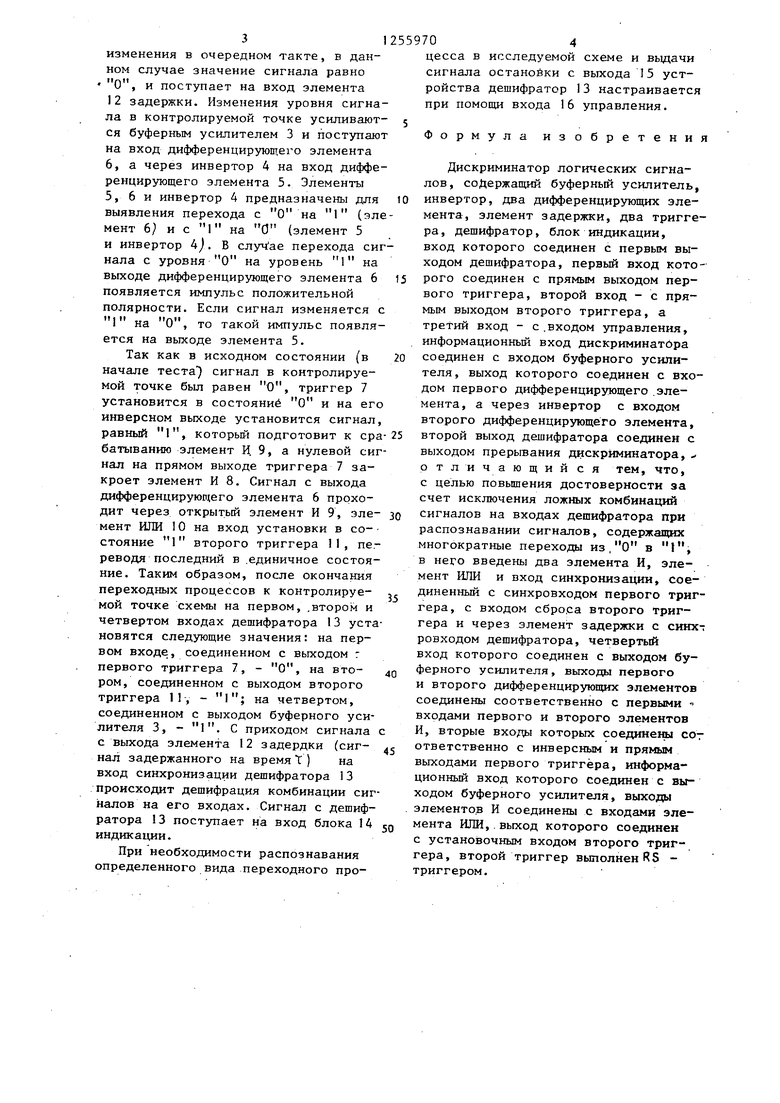

На фиг.1 изображен дискриминатор логических сигналов; на фиг.2 - виды распознаваемых переходных процессов и соответствующие им комбинации сигналов на входах дешифратора.

Устройство содержит входы и 2 буферньй усилитель 3, инвертор 4, дифференцирующие элементы 5 и 6, триггер 7, элементы И 8 и 9, элемент ИЛИ 10, триггер 11, элемент 12 задержки, дешифратор 13, блок 14 индикации,вьгход 15 прерывания, вход 16 управления.

Вход 1 устройства соединен с входом буферного усилителя 3. Вход 2 устройства соединен с синхронизирующим входом первого триггера 7, с входом элемента 12 задержки и входом установки в состояние О второго триггера 11. Выход буферного усилителя 3 подключен к информационному входу первого триггера 7, к. входу инвертора 4, к входу дифференцирующего элемента 6 и к четвертому входу дешифратора 13. Прямой выход первого .триггера 7 соединен с входом элемента И 8 и с входом дешифратора 13, инверсньй выход первого триггера 7 соединен с входом второго элемента И 9. Выход инвертора 4 соединен-с входом дифференцирующего элемента 5 Выход дифференцирующего элемента 5 соединен.с входом элемента И 8. Выход дифференцирующего элемента 6 со динен г входом элемента И 9. Выход элемента И 8 соединен с первым входом элемента ИЛИ 10, к второму входу которого подключен вьгход элемент И 9. , .

Вьгход элемента ИЛИ 10 соединен с входом установки в состояние 1 втрого триггера 11. Выход элемента 12 задержки и прямой выход второго тригера 1 1 соединен соответственно с входами дешифратора 13. Вход 16 управления соединен с третьим входом дешифратора. Первый выход дешифрато

55970

13 соединен с блоком 14 индикации. Второй выход дешифратора 13 соединен с выходом 15 прерывания дискриминато- ра.

В качестве первого триггера 7 может быть использован обычный триггер типа D, а в качестве второго триггера 1 1 - триггер типа RS. В качестве дешифратора 13 можно использовать JQ побой дешифратор на четыре информационных входа, имеющий синхровход. В качестве элементов индикации могут применяться печатающие устройства, различные устройства отобра- J5 жения информации с запоминанием результатов измерений и т.п.

Устройство работает следующим образом.

При распознавании многократного перехода с О на I сигналы на первом, втором и четвертом входах дешифратора 13 должны устанавливаться соответственно О, 1, 1 (фиг.2, строка 7).

Для распознавания переходного процесса вход 1 дискриминатора подключается к исследуемой точке схемы. После этого к входам контролируемого устройства прикладывается тест, длительность такта которого -., (т.е. интервала времени между соседними изменениями входных: сигналов исследуемой схемы) выбирается из условия

45

35

Г

где

I,

L- постоянная времени элемента

12 задержки;

- максимально возможная продолжительность переходного процесса в исследуемой точке схемы.

С началом приложения теста на вход 2 подается кратковременный импульс, длительность которого выбирается из условия

ч t.

где

t длительность импульса; время от начала приложения теста ко входам схемы до начала изменения уровня сигнала в исследуемой точке.

Этот импульс устанавливает в О второй триггер 11, способствует записи в первый триггер 7 того уровня сигнала, который имел место в исследуемой точке схемы до его первого

изменения в очередном такте, в данном случае значение сигнала равно О, и поступает на вход элемента 12 задержки. Изменения уровня сигнала в контролируемой точке усиливают- 5 ся буферным усилителем 3 и поступают на вход дифференцирующего элемента 6, а через инвертор 4 на вход дифференцирующего элемента 5. Элементы 5, 6 и инвертор 4 предназначены для Ю выявления перехода с О на 1 (элемент 6 и с 1 на О (элемент 5 и инвертор 4 j. В случ ае перехода сигнала с уровня О на уровень 1 на выходе дифференцирующего элемента 6 15 появляется импульс положительной полярности. Если сигнал изменяется с 1 на О, то такой импульс появляется на выходе элемента 5.

Так как в исходном состоянии (в 20 начале теста) сигнал в контролируемой точке был равен О, триггер 7 установится в состояние О и на его инверсном выходе установится сигнал, равный 1, который подготовит к ера-25 батыванию элемент И 9, а нулевой сигнал на прямом выходе триггера 7 закроет элемент И 8. Сигнал с выхода дифференцируюп 1его элемента 6 проходит через открытый элемент И 9, эле- зо мент ИЛИ 10 на вход установки в со- стояние 1 второго триггера 11, переводя последний в .единичное состояние. Таким образом, после окончания переходных процессов к контролируе- 5 мой точке схемы на первом, .втором и четвертом входах дешифратора 13 установятся следующие значения: на первом входе, соединенном с выходом г первого триггера 7, - О, на вто- 40 ром, соединенном с выходом второго триггера 11-, - на четвертом, соединенном с выходом буферного усилителя 3, - 1. С приходом сигнала с с выхода элемента 12 задердки (сиг- нал задержанного на время Т ) на вход синхронизации дешифратора 13 происходит дешифрация комбинации сигналов на его входах. Сигнал с дешифратора 13 поступает на вход блока 14 jg индикации.

При необходимости распознавания определенного вида переходного процесса в исследуемой схеме и выдачи сигнала останойки с выхода 15 устройства дешифратор 13 настраивается при помощи входа 16 управления.

Формула изобретени

Дискриминатор логических сигналов, соДержаЕЦий буферный усилитель, инвертор, два дифференцирующих элемента, элемент задержки, два триггера, дешифратор, блок индикации, вход которого соединен с первым выходом дешифратора, первый вход которого соединен с прямым выходом первого триггера, второй вход - с прямым выходом второго триггера, а третий вход - с .входом управления, информационный вход дискриминатбра соединен с входом буферного усилителя, выход которого соединен с входом первого дифференцирующего .элемента, а через инвертор с входом второго дифференцирующего элемента, второй выход дешифратора соединен с выходом прерьшания дискриминатора, отличающий ся тем, что, с целью повышения достоверности за счет исключения ложных комбинаций сигналов на входах дешифратора при распознавании сигналов, содержащих многократные переходы из,О в , в него введены два элемента И, элемент ИЛИ и вход синхронизации, соединенный с синхровходом первого триггера, с входом сбро.са второго триггера и через элемент задержки с сних ровходом дешифратора, четвертый вход которого соединен с выходом буферного усилителя, выходы первого и второго дифференцирующих элементов соединены соответственно с первыми входами первого и второго элементов И, вторые входы которых соедииешл со ответств-енно с инверсным и прямым выходами первого триггера, информационный вход которого соединен с выходом буферного усилителя, выходы элементо.в И соединены с входами элемента ИЛИ,.выход которого соединеи с установочным входом второго триггера, второй триггер выполнен RS - триггером.

Редактор Н.Данкулич

Составитель Н.Помякшева

Техред И.Попович Корректор М.Пожо

Заказ 4820/46 Тираж 728Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Дискриминатор логических сигналов | 1975 |

|

SU555354A1 |

| Устройство для распознавания образов | 1986 |

|

SU1361589A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1996 |

|

RU2115952C1 |

| Устройство для распознавания образов | 1987 |

|

SU1536412A2 |

| Устройство для отображения информации | 1979 |

|

SU892467A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СОПРОТИВЛЕНИЯ ИЗОЛЯЦИИ СЕТЕЙ ПОСТОЯННОГО ТОКА | 1991 |

|

RU2026561C1 |

| Устройство для контроля сопротивления изоляции сети постоянного тока | 1990 |

|

SU1774284A1 |

| Оптическое устройство распознавания номера движущегося объекта | 1980 |

|

SU907564A1 |

| Устройство для измерения параметров многополюсников | 1986 |

|

SU1478147A1 |

| Устройство для отображения ин-фОРМАции | 1979 |

|

SU805406A1 |

Изобретение относится к вычислительной технике, в частности к средствам контроля и диагностики неис- правностей логических схем. Цель изобретения - повышение достоверности. Устройство содержит буферный усилитель 3, инвертор 4, дифференцирукг- щие элементы 5 и 6, триггеры 7 и П, элемент 12 задержки, дешифратор 13 и блок 14 индикации. Введение элементов И 8 и 9 и элемента ИЛИ IО исключает ложные комбинации сигналов на входах дешифратора 13 при распознавании многократных переходов из в 1 tin О и наоборот. 2 ил. с СЛ да/г/

| Устройство для контроля прохождения импульсов | 1972 |

|

SU458787A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-09-07—Публикация

1984-11-26—Подача