1

Изобретение относится к области вычислительной техники и, в частности, к средствам контроля и диагностики неисправностей логических схем.

Известно устройство, предназначенное

для анализа и индикации потенциальных и импульсных сигналов в контролируемой логической схеме, которое содержит компараторы потенциалов 1 и О, входы которых соединяются с точкой схемы, где наблюдается сигнал, и триггеры, входы которых непосредственно или через логические элементы связаны с выходами компараторов, а выходы подключены к элементам индикации.

Недостатком являются ограниченные возможности классификации и. отображения логических сигналов.

Известно устройство,содержащее буферный усилитель, триггеры, инверторы и элемент ИЛИ, элемент индикации, выход которого соединен со входами триггеров, а входы - с выходом буферного усилителя и инверторов, входы которых связаны с дополнительньтми входами устройства, предназначенными для приема стробирующих сигналов ( например, от других точек контролируемой схемы).

Данное устройство позволяет фиксировать статические значения 1 и О сигналов и число их изменений. Однако и этих возможностей оказывается недостаточно для поиска неисправностей в сложных логических схемах с памятью.

Кроме того, оно не позволяет определить к какому такту теста, прикладываемого к контролируемой схеме, относятся изменения сигнала в наблюдаемой точке. В результате поиск неисправностей в схеме оказывается сложным и трудоемким процессом.

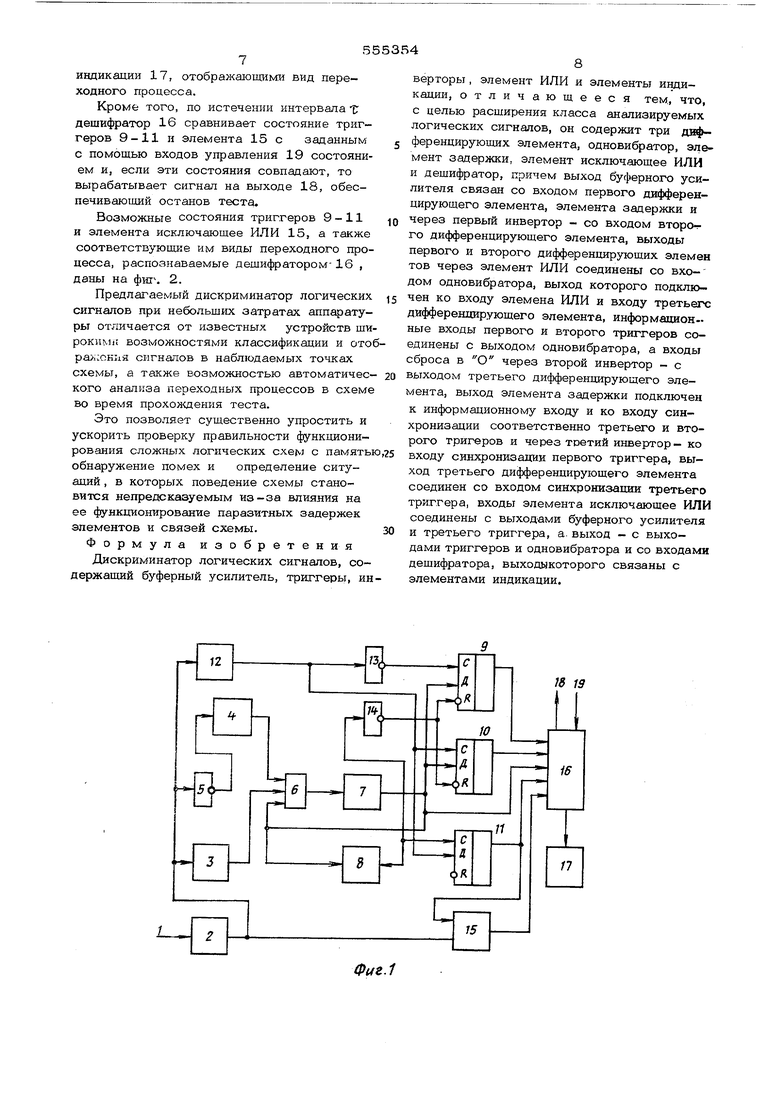

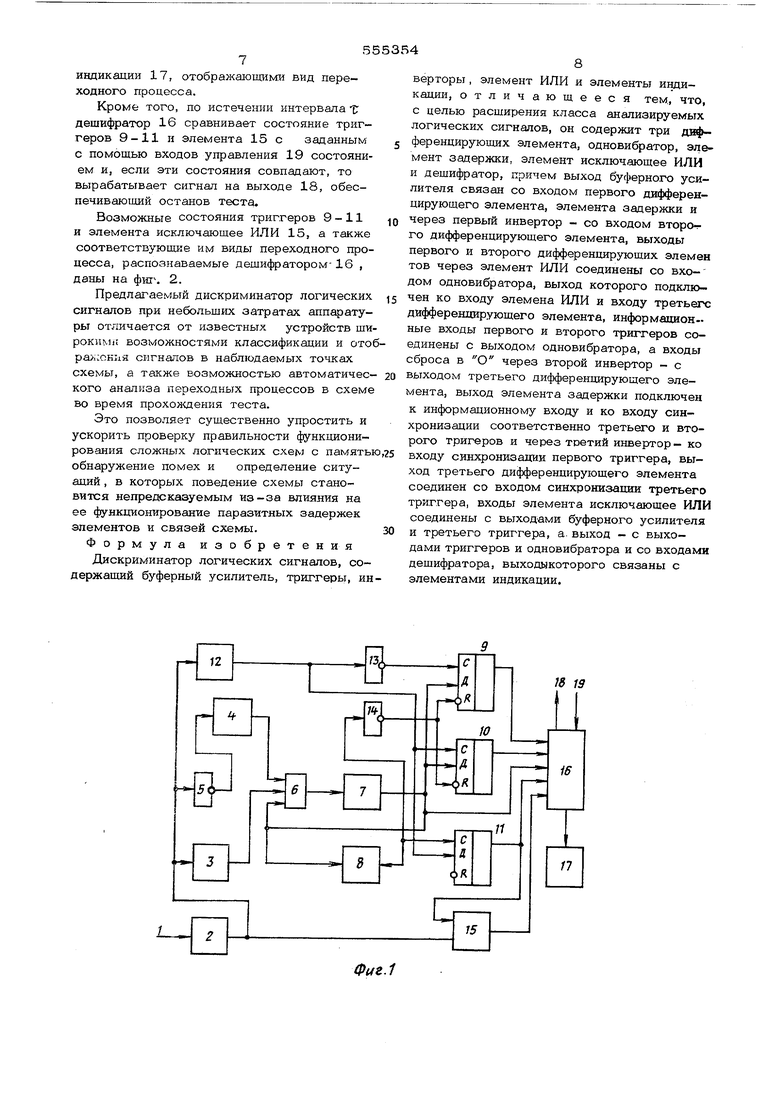

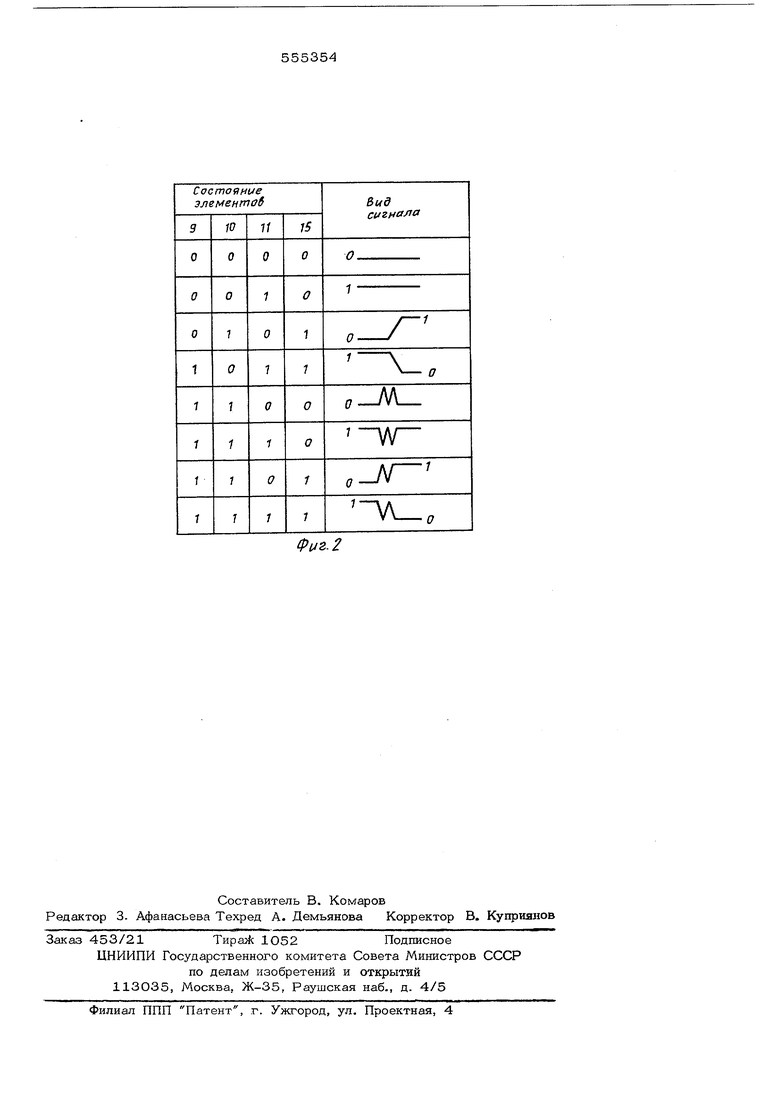

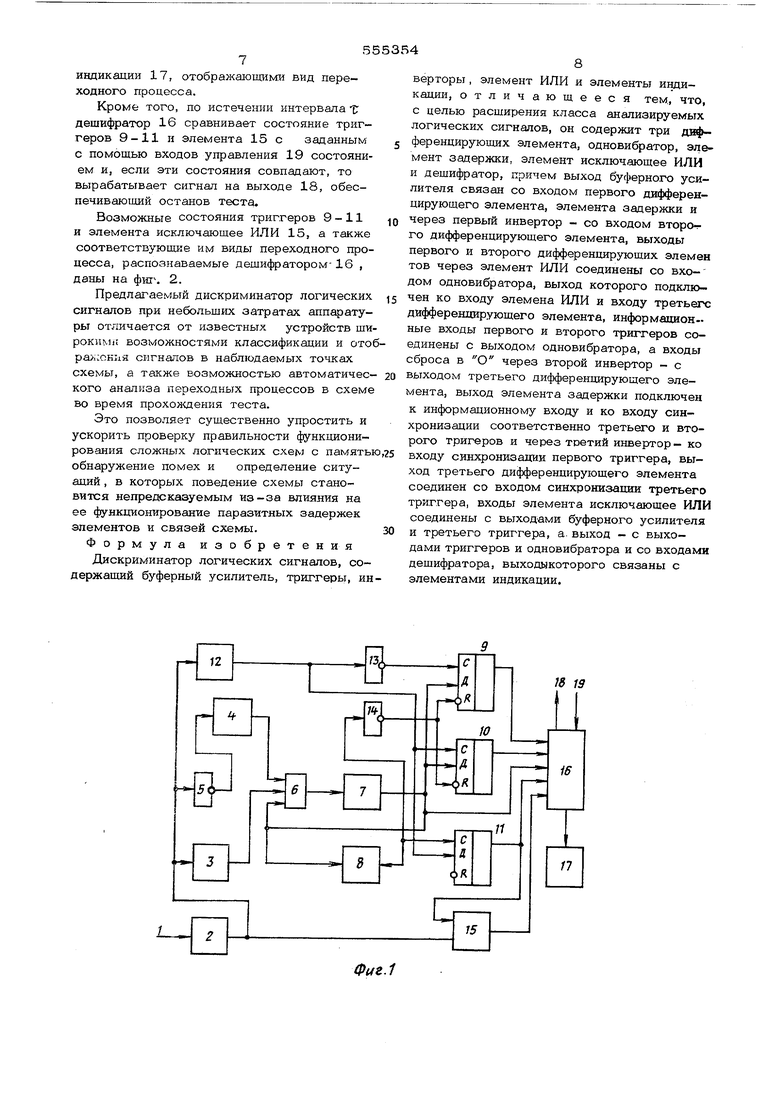

Это связано с тем, что для схем с памятью существенными являются не только статические значения сигналов в каждом такте работы, но и вид переходного процесса при смене одного статического значения другим. Некоторые виды переходных процессов в определенных точках схемы оказываются недопустимыми, так как приводят к зависимости установившегося состо5шия элеNieHTOB памяти от конкретных значений паразитных задержек элементов и связей схемы и, следовательно, делают ее поведение непредсказуемым. Причем для разных конфигураций схем, разных типов элементов памяти и разных внутренних состояний схемы недопустимы и могут быть совершенно различные виды переходных процессов. Если ограничиться наиболее широко распространенными на практике потенциальными логическими схемами, то для проверки правильности функционирования схемы на прикладываемой к ее входам последователь ности сигналов и фиксации всех ситуаций, в которых поведение схемы непредсказуемо оказывается необходимым различать следую щие виды сигналовнеизменное состояние О, неизменное состояние 1, од нократное изменение (гладкий фронт) с О на 1, однократное изменение (гладкий фронт) с 1 на положительные выбросы в состоянии О (статический риск в О ) ; отрицательные выбросы в состоянии (статический риск 1), многократное изменение при переходе с 1 на О (динамический риск в многократно изменение при переходе с О на 1 (дина мический риск в О ). Известное устройство не обеспечивает в полном объеме различение указанных видов сигналов и, таким образом, оказывается малопригодным для контроля сложных логических схем с памятью. Поскольку в устройстве отсутствуют сре ства для автоматического обнуления триггеров перед началом каждого такта теста и средства анализа состояния этих триггеров, оно не позволяет определить, к какому такту относятся зафиксированные изменения сигнала. Поэтому те ограниченные возможности классификации переходных процессов, которые имеются у устройства, могут быть реализованы только в неавтоматическом режиме, а именно путем наблюдения за индикацией при ручном запуске приложения к контролируемой схеме каждого очередного такта теста и ручном сбросе перед запуском каждого такта. Зто делает процесс анализа сигнала в схеме (ив частности, недОпустимых их изменений, вызывающих непредсказуемое поведение) очень трудоемким. Целью изобретения является расширение класса анализируемых логических сигналов. Зто достигается тем, что дискриминатор содержит три дифференцирующих элемента, одновибратор, элемент задержки, элемент исключаюш.ее ИЛИ и дешифратор. Причем выход, буферного усилителя связан со входом первого дифференцирующего элемента, элемента Усдержки и через первый инвертор со входом второго дифференцирующего элемента. Выходы первого и второго дифференцирующих элементов через элемент ИЛИ соединены со входом одновибратора вы.ход которого подключен ко входу элемента ИЛИ и входу третьего дифференцирующего элемента. Информационные входы первого и второго триггеров соединены с выходом од- новибратора, а входы сброса в О через второй инвертор - с выходом третьего дифференцирующего элемента. Выход элемента задержки подключен к информационному входу и ко входу синхронизации соответственно третьего и второго триггера и через третий инвертор - ко входу синхронизации первого триггера. Выход третьего дифференцирующего элемента соединен со входом синхронизации третьего триггера, входы элемента исключающее ИЛИ соединены с выходами буферного усилителя и третьего триггера, а выход - с выходами триггеров и одновибратора и со входами дешифратора, выходы которого связаны с элементами индикации. На фиг. 1 изображен дискриминатор; на фиг. 2 - распознаваемые виды переходных процессов и соответствующие им состояния триггеров. Дискриминатор содержит вход 1 устройства, буферный усилитель 2, первый дифференцирующий элемент 3, второй дифференцирующий элемент 4, первый инвертор 5, элемент ИЛИ 6, одновибратор 7, третий дифференцирующий элемент 8, первый триггер 9, второй триггер Ю, третий триггер 11 , элемент задержки 12, третий инвертор 13, второй инвертор 14, элемент исключающее ИЛИ 15, дещифратор 16, элементы индикации 17, выход 18 прерывания теста, входы 19 управления. Вход 1 устройства связан с остальными его элементами через буферный усилитель 2, который предотвращает искажение формы сигнала в -исследуемой точке логической схемы при подключении к ней дискриминатора. Выход элемента 2 связан с первьхм и вторым дифференцирующими элементами 3 и 4, причем связь со вторыми из этих элементов осуществляется через первый инвертор 5. Выходы дифференцирующих элементов 3 и 4 через элемент ИЛИ 6 соединены со входом одновибратора 7, на выходе которого включен третий дифференцирующий элемент 8. Выход одновибратора 7 подключен ко входу элемента ИЛИ 6. Перечисленные элементы и связи предназначены для обнаружения на входе 1 первого изменения сигнала, соответствующего началу очередного такта работы схемы (эти функции выполняют элементы 3-6, формирования временного интервала (одновибратор 7, определяющего максимально возможную длительность переходного процесса, в каждом такте, и формирования сигнала (дифференцирующий элемент 8), обеспечивающег приведение устройства в исходное состояни в начале каждого такта. Для фиксации различных видов изменения сигнала на входе 1 устройство содержит первый, второй и третий триггеры 911. Информационные входы (Д) триггеров 9,10 соединены с выходом одновибратора 7. Информационный вход триггера 11 и вход синхронизации (С) триггера 10 связаны через элемент задержки .12 с выходом буферного усилителя 2, вход синхронизации триггера 9 соединен с выходом эл мента задержки 12 через третий инвертор 13. Вход синхронизации триггера 11 непосредственно и входы сброса (R) триггеров 9 и 10 через второй инвертор 14 подключены к выходу третьего дифференцирующего элемента 8. Выходы буферного усилителя 2 и третье го триггера 11 соединены со входами элемента исключающее ИЛИ 15, который служит для сравнения состояния входа 1 до первого его изменения в текущем такте и установивщегося состояния входа в конце Этого такта. Выходы элемента 15, триггеров 9-11 и одновибратора 7 связаны со входами дешифратора 16, который предназначен для преобразования состояния указанных тригге ров в сигналы, соответствующ1;е определенным видам переходного процесса в исследу емой точке логической схемы (см. фиг.2). Выходы дешифратора 16 служат для визуального отображения переходного процесса. Дополнительный выход 18 предназначен дл выдачи сигнала прерывания (останова), при ладываемого к анализируемой схеме теста в том его такте, в котором в исследуемой точке схемы обнаружен определенный вид переходного процесса. Вид переходного про цесса (например, статический риск или динамический риск), при котором вырабатыва ется сигнал на выходе 18, задается с помошью входов управления 19. В качестве триггеров 9-11 могут быть использованы обычные управляемые фронтом триггеры типа Д. Устройство работает следующим образом. После подключения входа 1 к исследуемой точке логической схемы ко входам схе мы прикладывается тест. Длительность так та t теста (т.е. интервала между двумя соседними по времени изменениям; входных сигналов схемы) и длительность Т интервала, формируемого одновибратором 7, выбираются из условия т„ где Г - максимально возможная продолжительность переходного процесса в схеме. Длительность интервала Т устанавливается путем регулировки времязадающих цепей одновибратора 7. Каждое очередное изменение сигнала в исследуемой точке схемы, возникающее в результате приложения теста, фиксируется дифференцирующими элементами 3 и 4, пер вый из которых распознает изменение с О на 1, а второй - с 1 на О. Первое в очередном такте теста изменение сигнала в исследуемой точке вызывает появление импульса на выходе элемента ИЛИ 6, который производит запуск одновибратора 7. При этом за счет обратной связи с выхода одновибратора на одном из входов элемента ИЛИ 6 устанавливается сигнал 1, который в течение интервала t делает этот элемент нечувствительным ко всем последующим изменениям сигнала на входе 1 дискриминатора. На переднем фронте вырабатываемого одновибратором 7 импульса длительностью t дифференцирующий элемент 8 выдает короткий импульс, который обеспечивает приведение в исходное состояние триггеров 9-11. При этом триггеры 9,10 устанавливаются в О, а триггер 11-в состояни§, которое имело место в исследуемой точке схемы до первого его изменения в очередном такте. Далее задержанный элементом 12 (на время действия импульса начальной установки триггеров 9,10,11) сигнал со входа 1 передается на входы синхронизации триггеров 9,10, на информационных входах которых одновибратор 7 поддерживает сигнал 1 в течение всего интервала t . Если внутри этого интервала происходит хотя бы одно измерение сигнала на входе 1 с 1 на О, то первый триггер 9 устанавливается в 3, если происходит хотя бы одно изменение с О на 1, то устанавливается в 1 второй триггер 10. После окончания переходного процесса на входе 1 элемент исключающее ИЛИ 15 производит сравнение предшествующего (до первого изменения) состояния этого входа, зафиксированное третьим триггером 11, и установившегося состояния входа. При равенстве этих состояний выход элемента 15 имеет значение О , при неравенстве - 1. Далее состояние триггеров 9-11 и элемента 15 анализируется дешифратором 16, который управляет элементами индикации 17, отображающими вид переходного процесса. Кроме того, по истечении интервала t дешифратор 16 сравнивает состояние триггеров 9-11 и элемента 15 с заданным с помощью входов управления 19 состоянием и, если эти состояния совпадают, то вырабатывает сигнал на выходе 18, обеспечивающий останов теста. Возможные состояния триггеров 9-11 и элемента исключающее ИЛИ 15, а также соответствующие им виды переходного процесса, распознаваемые дещифратором16 , даны на фш 2. Предлагаемый дискриминатор логических сигналов при небольших затратах аппаратуры отличается от известных устройств щи poKHMi возможностями классификации и ото pa,;oHiiH сигналов в наблюдаемых точках схемы, а также возможностью автоматичес- 20

кого анализа переходных процессов в схеме во время прохождения теста.

Это позволяет существенно упростить и ускорить проверку правильности функционирования сложных логических схем с памятью,25 обнаружение помех и определение ситуаций , в которых поведение схемы становится непредсказуемым из-за влияния на ее функционирование паразитных задержек эпементов и связей схемы.30

Формула изобретения

Дискриминатор логических сигналов, содержащий буферный усилитель, триггеры, инмента, выход элемента задержки подключен к информационному входу и ко входу синхронизации соответственно третьего и второго тригеров и через тоетий инвертор - ко входу синхронизации первого триггера, выход третьего дифференцирующего элемента соединен со входом синхронизации третьего триггера, входы элемента исключающее ИЛИ соединены с выходами буферного усилителя и третьего триггера, а. выход - с выходами триггеров и одновибратора и со входами дещифратора, выходыкоторого связаны с элементами индикации. верторы, элемент ИЛИ и элементы индикации, отличающееся тем, что, с целью расщирения класса анализируемых логических сигналов, он содержит три дифференцирующих элемента, одновибратор, элемент задержки, элемент исключающее ИЛИ и дешифратор, причем выход буферного усилителя связан со входом первого дифференцирующего элемента, элемента задержки и через первый инвертор - со входом второго дифференцирующего элемента, выходы первого и второго дифференцирующих элемен тов через элемент ИЛИ соединены со входом одновибратора, выход которого подключен ко входу элемена ИЛИ и входу третьегс дифференцирующего элемента, информационные входы первого и второго триггеров соединены с выходом одновибратора, а входы сброса в О через второй инвертор - с выходом третьего дифференцирующего эле

| название | год | авторы | номер документа |

|---|---|---|---|

| Дискриминатор логических сигналов | 1984 |

|

SU1255970A1 |

| Оперативное запоминающее устройство с самоконтролем | 1988 |

|

SU1647655A1 |

| Устройство для ввода информации | 1984 |

|

SU1405042A1 |

| Оптико-электронное устройство для измерения линейных перемещений | 1988 |

|

SU1620835A1 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| Автоматический мост | 1976 |

|

SU687398A1 |

| Устройство для контроля цифровых блоков | 1981 |

|

SU1037259A1 |

| Устройство для проверки выполнения последовательности команд микропроцессора | 1984 |

|

SU1247874A1 |

| Фазовый дискриминатор | 1982 |

|

SU1125741A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

. 1

Фиг. 2

Авторы

Даты

1977-04-25—Публикация

1975-06-16—Подача