Изобретение относится к электросвязи и может использоваться в системах передачи информации для кодирования инверсных кодов.

Известен кодер, содержащий накопитель, распределитель импульсов, триггер и элемент ИЛИ.

Недостатками известного кодера являются низкое быстродействие и узкая область применения.

Наиболее близким по технической сущности к изобретению является кодер, содер- жащий накопитель, первый и второй распредели импульсов первый формирователь импульсов, тригпф и элемент ИЛИ, сумматор, два регистра, второй формирователь импульсов и два элемента И.

Недостатками прототипа являются узкие функциональные возможности.

Цель изобретения - расширение функциональных возможностей кодера за счет формирования кодов переменной длины.

Поставленная цель достигается тем, что в кодер, содержащий первый триггер, накопитель, информационные входы которого объединены с первичными информационными входами первого регистра и являются информационными входами устройства, выходы накопителя подключены к первым входам первого формирователя импульсов, выход которого подключен к первому входу первого элемента И, сумматор, выход которого подключен к первому входу второго регистра, выходы которого соединен с первыми входами второго формирователя импульсов, выход которого подключен к. первому входу второго элемента И, выход которого и выход первого элемента И подключены к пеовому и BTODOMV входам 00 CJ

о ю со

мента ИЛИ, выход которого является выходом устройства, введены третий регистр, блок сравнения, счетчик импульсов, второй триггер, третий и четвертый формирователи импульсов, коммутатор, третий и четвертый элементы И и дешифратор, информационные входы третьего регистра и первого триггера и первые входы третьего и четвертого элементов И являются соответственно установочным входом, входом запуска, управляющим и тактирующим входами устройства, выходы третьего регистра подключены к первым входам блока сравнения и входам дешифратора, выходы которого подключены к первым входам первого и второго формирователей импульсов, первым входам третьего формирователя импульсов и первой группе входов коммутатора, выходы счетчика импульсов подключены к вторым входам блока сравнения, выход которого подключен к входу обнуления счетчика импульсов и входу второго триггера, прямой выход которого подключен к второму входу второго элемента И, инверсный выход подключен к второму входу первого элемента И и входу четвертого формирователя импульсов, выход которого соединен с входами обнуления накопителя, первого и второго регистров и первого триггера, прямой и инверсный выходы которого подключены соответственно к вторым входам третьего и четвертого элементов И, выход третьего элемента И подключен к тактирующим входам счетчика импульсов, накопителя, второго и первого регистров, выходы первого регистра подключены к второй группе входов коммутатора и вторым входам третьего формирователя импульсов, выходы которых подключены соответственно к входам сумматора и второму информационному входу первого регистра.

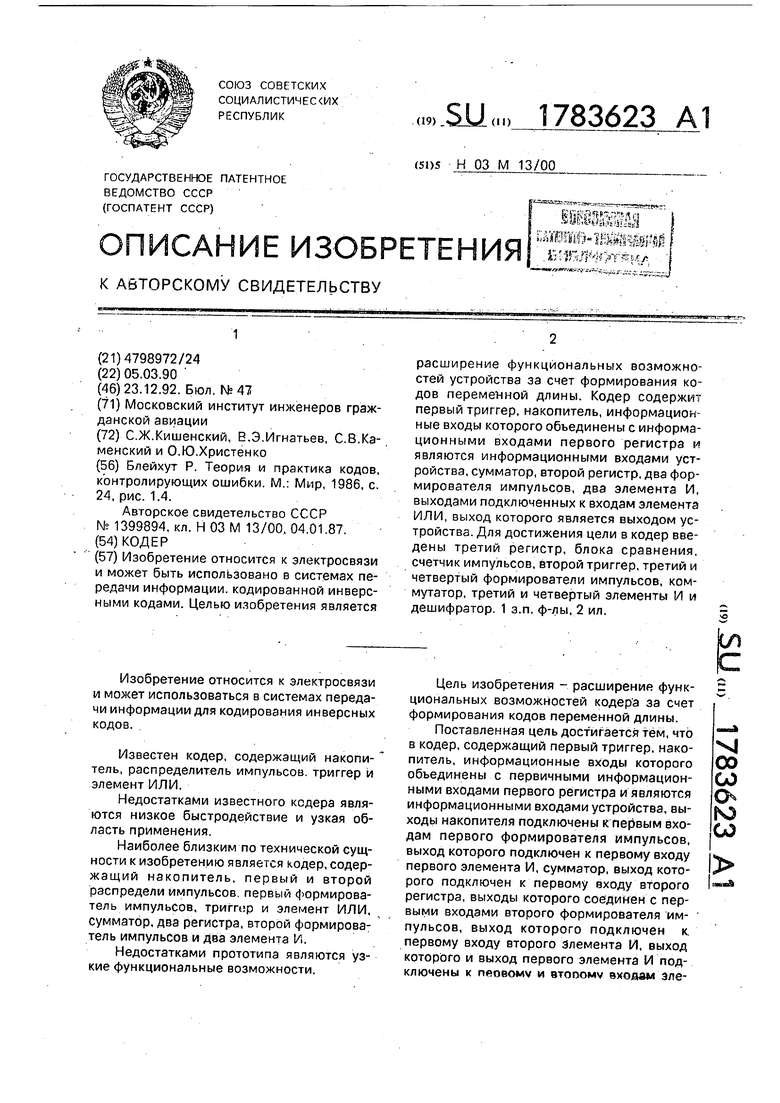

Кроме того, коммутатор содержит М-1 элементов И и М-2 элементов ИЛИ, где М - длина кодового слова, первые входы и выходы элементов И являются соответственно вторыми входами и выходами коммутатора, выходы с первого по (М-2)-й элементов ИЛИ подключены к вторым входам одноименных элементов И, первые входы всех элементов ИЛИ объединены с вторым входом (М-1)-го элемента И и являются первым входом первой группы входов коммутатора, (i+ 1)-e вхо- ды с первого по (М-Ы)-й элементов ИЛИ, где 1 1,М-2, объединены и являются (1+1)-м входом первой группы входов коммутатора.

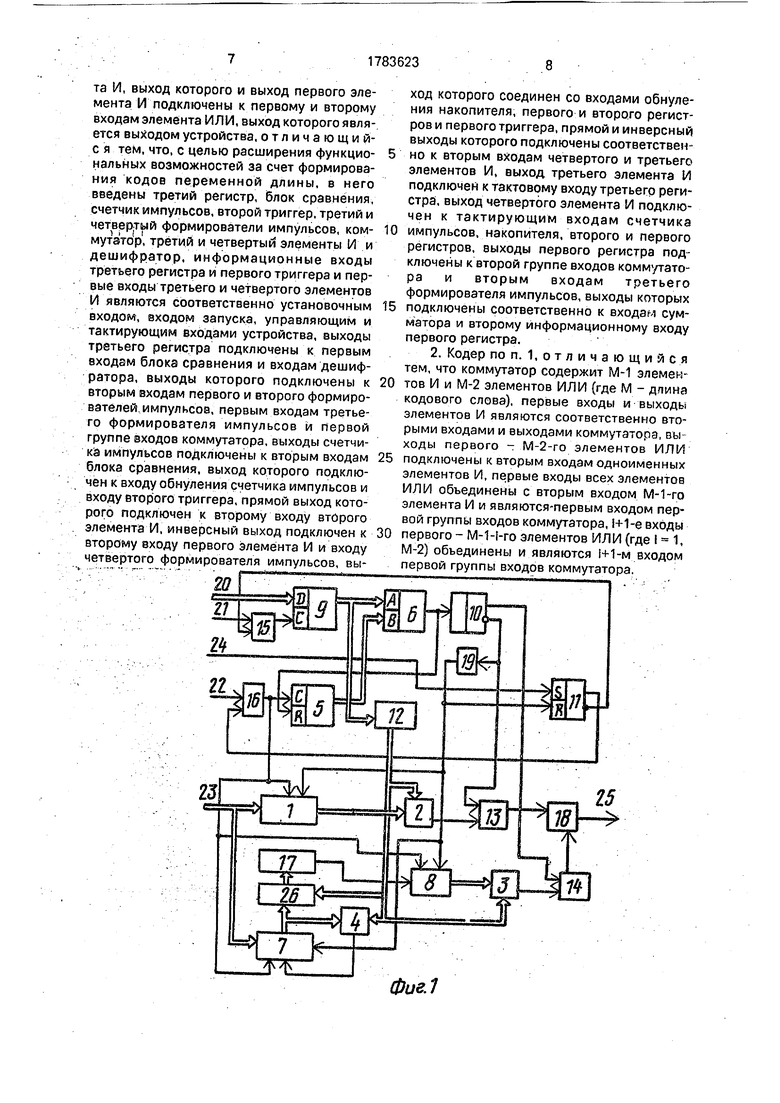

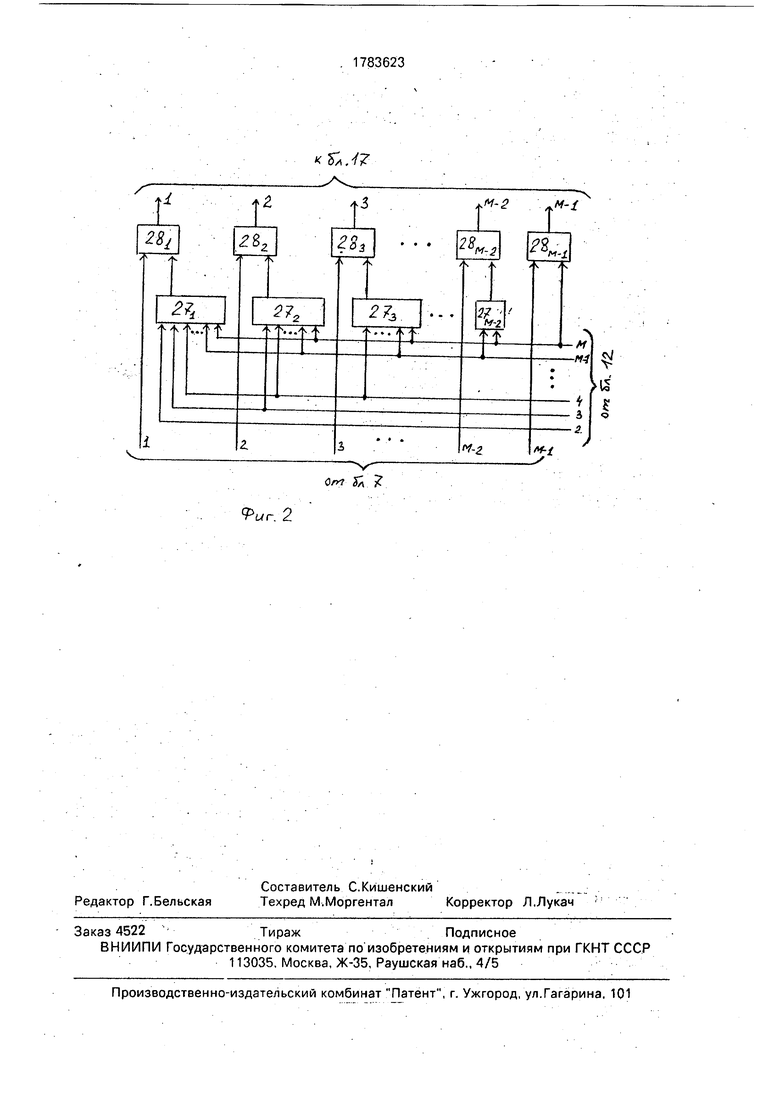

На фиг. 1 представлена структурная схема кодера; на фиг. 2 - структурная схема коммутатора.

Кодер содержит накопитель 1, первый формирователь 2 импульсов, второй и третий формировали 3 и 4 импульсов, счетчик 5, блок 6 сравнения, с первого по третий регистры 7-9, второй триггер 10, первый триггер 11, дешифратор 12, элементы 13-16

И с первого по четвертый, сумматор 17. элемент 18 ИЛИ, четвертый формирователь 19 импульсов, установочный вход 20, управляющий вход 21, тактирующий вход 22, информационный вход 23, вход 24 записи, выход

0 25, коммутатор 26.

Коммутатор 26 (фиг. 2) содержит элементы ИЛИ 271-27м-2 и элементы И 281-28м-1.

Изобретение обеспечивает кодирование информации инверсными кодами при

5 длинах информационных слов до некоторого числа М включительно; максимальная длина выходного кодового слова - 2 х М. Допустимы любые длины информационных слов от 1 до М. Разрядность накопителя,

0 первого и второго регистров - блоков 1, 7 и 8 - равна М. Формирователи 2-4 импульсов представляют собой совокупности двухвхо- довых элементов И, первые входы которых соединены соответственно с выходами бло-5 ков 1,8 и 7, а вторые одноименные входы всех формирователей объединены и соединены с выходами дешифратора 12 В каждом формирователе импульсов выходы всех элементов И объединены на входах М-вхо0 дового элемента ИЛИ, выход которого является выходом соответствующего формирователя импульсов.

Регистр 9 предназначен для хранения двоичного числа, представляющего длину

5 кодового слова (от 1 до М соответственно) В накопителе 1 записывается и выдвигается в канал связи информационное кодовое слово. В регистре 7 информационное кодовое слово циклически сдвигается для формиро0 вания проверочных символов, которые записываются в регистре 8 и из него поступают в канал связи.

Пусть необходимо передавать информацию в виде слов, закодированных (2 х К,

5 К) - инверсным кодом, где К - число информационных символов, К М.

Перед началом работы кодера в регистре 9 устанавливается текущая разрядность информационного кодового слова ее

0 двоичный код устанавливается на входе 20, управляющим сигналом на входе 21 через открытый сигналом с триггера 11 элемент И

15данный код записывается в регистр. Исходное состояние триггера 11 - нулевое. В

5 исходном состоянии все регистры также обнулены, как и триггеры; содержимое счетчика - нулевое. Тактовые импульсы на устройство не поступают, так как элемент И

16закрыт нулевым сигналом с прямого выхода триггера 11.

Информационное слово параллельным кодом заносится в накопитель, представляющий собой регистр памяти, а также в регистр 7. Процесс кодирования начинается подачей импульса запуска на вход 24. Триггер 11 устанавливается в единичное состояние и разрешает поступление на входе кодера тактовых импульсов. Модуль счета счетчика 5 равен М.

В нулевом такте работы разрешающий потенциал формируется на первом выходе дешифратора 12. При этом первый информационный символ информационного кодо вого слова с первого выхода накопителя 1 через блок 2 поступает на вход элемента 13, открытого сигналом с инверсного выхода триггера 10, и через элемент 18 поступает в канал связи. На нулевом такте на сумматоре (многовходовом сумматоре по модулю два) 17 формируется первый проверочный символ в соответствии с проверочной матрицей инверсного кода, имеющей вид

II НЮЙК Миз которой следует, что 1-й проверочный символ кода равен сумме по модулю два всех информационных символов, за исключением одноименного i-ro.

Таким образом, с входами сумматора 17 соединяются все разряды регистра 7 через коммутатор 26, который работает следующим образом (фиг, 2): если информационное слово имеет К разрядов, с К-го выхода дешифратора 12 получают положительный потенциал, через элементы ИЛИ 271-27к-1 открывающий соответствующие элементы И 281-28к-1, которые коммутируют значения соответствующих информационных символов, кроме старшего символа, для формирования текущего проверочного символа.

Формирователи импульсов 2 и 3 коммутируют соответственно старшие символы кодовых слов в элементы И 13 и 14. Формирователь 4 коммутирует К-й (старший) символ на последовательный информационный вход (младшего разряда) регистра 7.

В момент поступления первого тактового импульса значение первого проверочного символа записывается в первый разряд регистра 8, далее осуществляется сдвиг информационного слова в накопителе 1; в течение следующего такта работы кодера в канал связи поступает второй информационный символ. Производится также циклический сдвиг информационного слова в регистре 7, а счетчик15 инкремен- тируется.

Так продолжается до тех пор, пока со держимое счетчика (после К-1 тактов с при ходом К-го тактового импульса) не станет равным содержимому регистра 9. При 5 срабатывает блок сравнения и сбрасывав счетчик, а также устанавливает триггер 10 % единичное состояние, закрывая элемент И 13 и открывая элемент И 14. В течение следующих К тактовых интервалов происходит

0 вывод в канал связи проверочных символов. Вторичное достижение содержимым счетчика 5 равенства с содержимым регистра 9 вызывает повторное срабатывание блока сравнения, триггер 10 устанавливается в

5 нулевое состояние, и сбрасывается счетчик 5. По фронту сигнала с триггера 10 срабатывает формирователь 19, который выходным импульсом сбрасывает в исходное состояние триггер 11, регистры 7 и 8, устанавливая

0 кодер в исходное состояние.

В процессе кодирования триггер 11 запрещает запись нового кодового слова в регистр 9.

Информационное слбво записывается s

5 младшие разряды блоков 1 и 7, при этом содержимое из старших разрядов (например, при переходе к кодированию кодовых слов с меньшей разрядностью) не имеет значения, что обеспечивается формировате0 лями импульсов.

Регистры и накопитель могут быть выполнены на основе, например, микросхем типа К155ИР1, блок сравнения - на основе микросхемы К555СП1.

5 Таким образом, изобретение позволяет легко модифицировать разрядность кода в произвольных пределах с сохранением корректирующих свойств кода. Наличие регистра, содержащего длину кодового слова,

0 позволяет реализовать управление кодером от ЭВМ. Это дает возможность использовать кодер в адаптивных системах передачи данных, т.е. расширить его функциональные возможности.

5

Формула изобретения 1. Кодер, содержащий первый триггер, накопитель, информационные входы которого объединены с первыми информацион0 ными входами первого регистра и являются информационными входами устройства, выходы накопителя подключены к первым входам первого формирователя импульсов, выход которого подключен к первому входу

5 первого элемента И, сумматор, выход которого соединен с информационным входом второго регистра, выходы которого соединены с первыми входами второго формирователя импульсов, выход которого подключен к первому входу второго элемента И, выход которого и выход первого элемента И подключены к первому и второму входам элемента ИЛИ, выход которого является выходом устройства, отличающий- с я тем, что, с целью расширения функциональных возможностей за счет формирования кодов переменной длины, в него введены третий регистр, блок сравнения, счетчик импульсов, второй триггер, третий и четвертый формирователи импульсов, ком- мутз тор , третий и четвертый элементы И и дешифратор, информационные входы третьего регистра и первого триггера и первые входы третьего и четвертого элементов И являются соответственно установочным входом, входом запуска, управляющим и тактирующим входами устройства, выходы третьего регистра подключены к первым входам блока сравнения и входам дешифратора, выходы которого подключены к вторым входам первого и второго формирователей импульсов, первым входам третьего формирователя импульсов и первой группе входов коммутатора, выходы счетчика импульсов подключены к вторым входам блока сравнения, выход которого подключен к входу обнуления счетчика импульсов и входу второго триггера, прямой выход которого подключен к второму входу второго элемента И, инверсный выход подключен к второму входу первого элемента И и входу четвертого формирователя импульсов, выход которого соединен со входами обнуления накопителя, первого и второго регистров и первого триггера, прямой и инверсный выходы которого подключены соответственно к вторым входам четвертого и третьего элементов И, выход третьего элемента И подключен к тактовому входу третьего регистра, выход четвертого элемента И подключен к тактирующим входам счетчика

импульсов, накопителя, второго и первого регистров, выходы первого регистра подключены к второй группе входов коммутатора и вторым входам третьего формирователя импульсов, выходы которых

подключены соответственно к входам сумматора и второму информационному входу первого регистра.

2. Кодер по п. 1,отличающийся тем, что коммутатор содержит М-1 элементов И и М-2 элементов ИЛИ (где М - длина кодового слова), первые входы и выходы элементов И являются соответственно вторыми входами и выходами коммутатора, вы ходы первого - M-2-ro элементов ИЛИ

подключены к вторым входам одноименных элементов И, первые входы всех элементов ИЛИ объединены с вторым входом М-1-го элемента И и являются-первым входом первой группы входов коммутатора, i+1-e входы

первого - элементов ИЛИ (где 1 1, М-2) объединены и являются i+1-м входом первой группы входов коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для мажоритарного декодирования в целом | 1989 |

|

SU1688415A1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| Устройство для кодирования цифровой информации циклическими кодами | 1986 |

|

SU1336255A1 |

| Устройство для передачи и приема информации | 1988 |

|

SU1541651A1 |

| Пороговый декодер сверточного кода | 1982 |

|

SU1078654A1 |

| Декодирующее устройство для исправления ошибок | 1985 |

|

SU1295531A1 |

| Кодек несистематического сверточного кода | 1990 |

|

SU1714812A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДИСКРЕТНЫХ СИГНАЛОВ | 1991 |

|

RU2043660C1 |

| Устройство для устранения неопределенности дискретнофазовой модуляции | 1983 |

|

SU1095428A1 |

| Устройство цикловой синхронизации | 1984 |

|

SU1197122A1 |

Изобретение относится к электросвязи и может быть использовано в системах передачи информации, кодированной инверсными кодами. Целью ияобретения является расширение функциональных возможностей устройства за счет формирования кодов переменной длины. Кодер содержит первый триггер, накопитель, информационные входы которого объединены с информационными входами первого регистра и являются информационными входами устройства, сумматор, второй регистр, два формирователя импульсов, два элемента И, выходами подключенных к входам элемента ИЛИ, выход которого является выходом устройства. Для достижения цели в кодер введены третий регистр, блока сравнения, счетчик импульсов, второй триггер, третий и четвертый формирователи импульсов, коммутатор, третий и четвертый элементы И и дешифратор. 1 з.п. ф-лы. 2 ил.

Фие.1

K&.J7

о/хг &

Фиг. 2

| Блейхут Р | |||

| Теория и практика кодов, контролирующих ошибки | |||

| М.: Мир, 1986, с | |||

| Пишущая машина для тюркско-арабского шрифта | 1922 |

|

SU24A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Кодер | 1987 |

|

SU1399894A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-12-23—Публикация

1990-03-05—Подача