«

Изобретение относится к электроизмерительной технике и может быть использовано для построения преобразователей активной мощности переменного тока в цифровой код.

Цель изобретения - повьпиение точности.

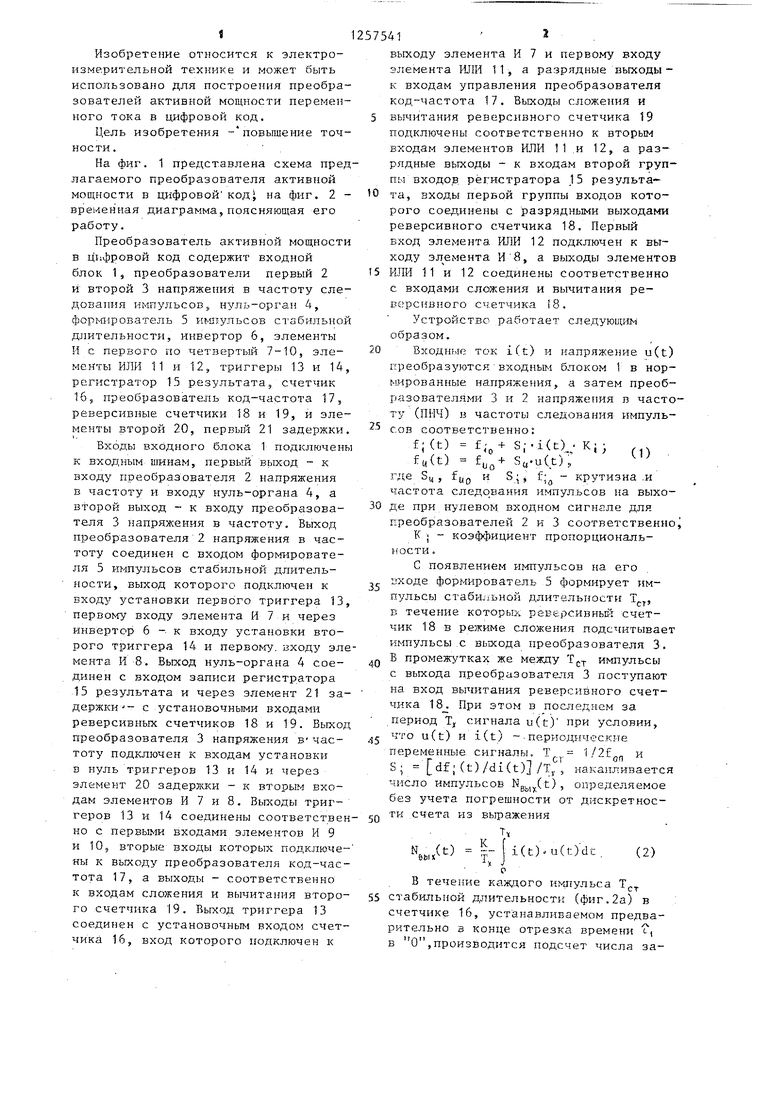

На фиг. 1 представлена схема предлагаемого преобразователя активной мощности в цифровой код на фиг. 2 - временная диаграмма,поясняющая его работу.

Преобразователь активной мощности в цифровой код содержит входной блок 1, преобразователи первый 2 и второй 3 напряжения в частоту следования импульсов 5 нуль-орган 4, формирователь 5 имл-ульсов ст абильнай длительности, инвертор 6, элементы И с первого по четвертый 7-10, элементы ИЛИ 11 и 12, триггеры 13 и 14, регистратор 15 результата, счетчик 16, преобразователь код-частота 17, реверсивные счетчики 18 и 19, и элементы второй 20, первый 21 задержки.

Входы входного блока 1 подключены к входным шинам, первый выход - к входу преобразователя 2 напряжения в частоту и входу нуль-органа 4, а второй выход - к входу преобразователя 3 напряжения в частоту. Выход преобразователя 2 напряжения в частоту соединен с входом формирователя 5 импульсов стабильной длительности, выход которого подключен к входу установки первого триггера 13, первому входу элемента И 7 и через инвертор 6 - к входу установки второго триггера 14 и первому, входу эле мента И 8. Выход нуль-органа 4 соединен с входом записи регистратора 15 результата и через элемент 21 задержки - с установочными входами реверсивных счетчиков 18 и 19. Выход преобразователя 3 напряжения в-частоту подключен к входам установки в нуль триггеров 13 и 14 и через элемент 20 задерлски - к вторым входам элементов И 7 и 8. Вьпсоды триггеров 13 и 14 соединены соответствен но с первыми входами элементов И 9 и 10, вторые входы которых подключены к выходу преобразователя код-частота 17, а выходы - соответственно к входам сложения и вычитания второго счетчика 19. Выход триггера 13 соединен С установочньгм входом счетчика 16, вход которого подключен к

57541 2

выходу элемента И 7 и первому входу элемента ИЛИ 11, а разрядные выходы- к входам управления преобразователя код-частота 17. Выходы сложения и

5 вь читания реверсивного счетчика 19 подключены соответственно к вторым входам элементов ИЛИ 11 .и 12, а разрядные вьтходы - к входам второй группы входов, регистратора 15 результа

to та, входы первой группы входов которого соединены с разрядными выходами реверсивного счетчика 18. Первый вход элемента ИЛИ 12 подключен к выходу элемента И 8, а выходы элементов

tS ИЛИ 11 и 12 соединены соответственно с входами сложения и вычитания реверсивного счетчика i8.

Устройстве работает следующим образом.

20 Входные ток i(t) и напряжение u(t) преобразуются входньп блоком 1 в нормированные напряжения, а затем преобразователями 3 и 2 напряжения в частоту (ПМЧ) J3 частоты следования импуль сов соответственно:

f;(t) f; S;.i(tb Kj) fi,(t) f,+ S,.u(t),

где Sy, f

uo

o io крутизна .и

частота следо вания импульсов на выхо- 30 де при нулевом, входном сигнале для гфеобразователей 2 и 3 соответственно

К j - коэффициент пропорциональности .

С появлением импульсов па его , гжоде формирователь 5 формирует импульсы стабильной длительности Т,,, в течение которых реверсивньп счетчик 18 в режиме сложения подсчитывает импульсы .с выхода преобразователя 3. Р Б промежутках же между Т,;- импульсы с выхода преобразователя 3 поступают на вход вычитания реверсивного счетчика 18. При этом в последнем за период Т( сигнала u(t) при условии, ...J что u(t) и i(t) периодические переменные сигналы. Т 1/2fд,, и S; df; (t)/di(t)/1. , накапливается число импульсов ) , определяемое без учета погрешности от дискретнос- Q ти счета из вьфажения

Т, N«.«(t) |-ji(t).u(t)dc, (2)

fi

В течение каждого ихлульса Т, 55 стабильной длительности (фиг.2а) в счетчике 16, устанавливаемом предварительно 3 конце отрезка времени с, в О,производится подсчет числа задержанных импульсов частотой следования fj (t) с выхода преобразователя 3 напряжения в частоту

N;{t) T.f;(t). (3) Выходной код счетчика 16 является управляющим для преобразователя код- частота 17, на выходе которого формируется частотно-импульсная последовательность со средней частотой следования при управляющем коде Nj(t)

, 2Mfi(t), (4) где М - коэффициент пропорциональности (м -||- -).

Так как (t) А, то всегда можно так подобрать f, чтобы . В нХчале очередного интервала Т, триггер 13 устанавливается в 1 (фиг, 2в), разрешая прохождение импульсов с выхода преобразователя 17 на вход сложения реверсивного счетчика 19 до появления ближайшего им- пульйа на выходе преобразователя 3 (фиг. 26), сбрасывающего триггер 13 в О. По окончании Т. устанавливается в 1 триггер 14 (фиг. 2г), разрешая прохождение импульсов с выхода преобразователя 17 на вход вычитания реверсивного счетчика 19 до появления ближайшего импульса на выходе преобразователя 3, сбрасывающего триггер 14 в О.

За очередной временной интервал (TC 2) суммарное показание счетчиков 18 и 19 при коэффициенте пересчета последнего М увеличится на число NV (Тсг-,н)-f;(t)M + + Т-С.) tf;(t)-2M Т,,. f;(t)x X М + (С, -tj)-f| (t) M, (5) причем первое слагаемое преобразованного выражения определяет результат счета для Т, а второе слагаемое - корректирующие поправки для второй и первой составляющих погрешностей соответственно предшествующей текущему TjjT и последующей на ним пауз

ri/fu(t) - Тс,.

По окончании периода исследуемых сигналов Т импульсом с выхода нуль- органа содержимое реверсивных счетчиков 18 и 19 переносится в регистратор 15, а счетчики 18 и 19 через время, определяемое элементом 21 задержки, сбрасываются.

Относительная погрешность от дискретности счета для одного Т не пре- вьш)ает

2575414

Si,., (6) а среднеквадратическое значение суммарной относительной погрешности от дискретности составит

T,{4(tl

i: tioJ(M-l; IJl

T,fu(

(7)

Предлагаемьй преобразователь активной мощности в цифровой код выгодно отличается от прототипа, так как имеет более высокую точность преобразования.

Действительно, отношение погрешностей от дискретности для предлагаемого преобразователя и прототипа составляет:

8. /S

t

t/M,.

При добавлении к показанию, мощности одного десятичного разряда М 10, получим

8,/Вд, 0,1,

Т.е-, точность преобразования увеличивается на порядок.

Формула изобретения

Преобразователь активной мощности

в цифровой код, содержащий входной блок, первый и второй преобразователи напряжения в частоту, нуль-орган, формирователь импульсов стабильной длительности, инвертор, первый и второй элементы И, первый реверсинный счетчик, регистратор результата и первый элемент задержки, причем входы входного блока являкзтся входами преобразователя активной мощности,

первый выход подключен к входу первого преобразователя напряжения в частоту и входу нуль-органа, а второй выход - к входу второго преобразователя напряжения в частоту, выход первого преобразователя напряжения в частоту соединен с входом формирователя импульсов стабильной длительности, выход которого подключен к первому входу первого элемента Н и

через инвертор - к первому входу

второго элемента И, выход нуль-органа соединен с входом записи рег ист- ратора результата и чсфез первый

элемент задержки с установочным входом первого реверсивного, счетчика разрядные выходы которого подключены к входам первой группы входо регистратора результата, отличающийся тем, что, с целью повышения точности, в него введены счет- .чик, преобразователь код-частота, второй реверсивный счетчик, первый и второй триггеры, третий и четвер- тьй элементы И, первый и второй элементы ИЛИ и второй элемент задержки, причем выход второго преобразователя напряжения в частоту подключен к входам сброса триггеров и через второй элемент задержки, - к вторым входам первого и второго ялементов И, входы установки первого и второго триггеров соединены соответственно с выходом формирователя ,сов стабильной длительности и выходом инвертора, а прямые выходы - с первыми 1зходами соответственно третьего и /четвертого элементов И, вторые входы

2575А16

которых подключены к выходу преобразователя код-частота, а выходы - соответственно к входам сложения и вычитания второго реверсивного счетчика, инверсньй выход первого триггера подключен к установочному входу счетчика, вход которого соединен с выходом первого элемента И и первым входом первого элемента ИЛИ, а разрядные

JO вьрходы - с входами управления преобразователя код-частота, выходы второго реверсивного счетчика соединены соответственно с. вторым входом первого элемента ИЛИ и первым входом втоJ5 рого элемента ИЛИ, разрядные выходы - с входами второй входов регистра результата, а установочньй вход - с вь ходом первого элемента задержки, второй вход второго элемен20 та ИЛИ подключен к выходу второго элемента И, а выходы первого и второго элементов ИЛИ соединены соответственно с входами сложения и вычитания первого реверсивного счетчика.

5

.IOLJL.

Гг

ЛfL rd-Jl--JL Jl-. ,

-. t

J. L

т

J. L

fCfrf

л

Редактор М.Петрова

Заказ 4912/42 Тираж 728Подписное

ВНИИИИ Государственного когдатета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприетие, г.Ужгород, ул.Проектная, 4

Составитель С.Кабиков

Техред Л.Олейник Корректор М.Самборская

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь активной энергии в цифровой код | 1986 |

|

SU1411678A1 |

| Способ преобразования активной мощности в цифровой код и устройство для его осуществления | 1980 |

|

SU995004A1 |

| Преобразователь активной мощностиВ КОличЕСТВО иМпульСОВ | 1979 |

|

SU845109A1 |

| Масштабный расширитель импульсов | 1982 |

|

SU1050104A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| Преобразователь активной энергии трехфазной сети в цифровой код | 1986 |

|

SU1363482A1 |

| Дельта-модулятор | 1988 |

|

SU1510090A2 |

| Измерительный преобразователь активной и реактивной составляющих синусоидального тока | 1990 |

|

SU1748079A1 |

| Устройство для определения звукоизоляции ограждающих конструкций | 1977 |

|

SU711614A1 |

| Система программного управления электроприводом | 1987 |

|

SU1481708A1 |

Изобретение относится к электроизмерительной технике и может быть использовано для построения преобразователей активной мощности переменного тока в цифровой код. Целью изобретения является повышение точности. Для достижения поставленной цели в устройство, содержащее входной блок 1, преобразователи 2 и 3 напряжения в частоту следования импульсов, нуль-орган 4, формирователь 5 импульсов стабильной длительности, инвертор 6, элементы И 7 и 8, регистратор 15 результата, реверсивный счетчик 18 и элемент 21 задержки, дополнительно введены элементы И 9 и 10, элементы ИЛИ 11 и 12, триггеры 13 и 14, счетчик 16, преобразователь код-частота 17, реверсивный счетчик 19 и элемент задержки 20. Устройство обеспечивает на порядок повышение точности преобразования. 2 ил. о. ел с: cpue.t

| Цифровой ваттметр | 1972 |

|

SU603914A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ преобразования активной мощности в цифровой код и устройство для его осуществления | 1980 |

|

SU995004A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-09-15—Публикация

1985-04-24—Подача