СП

СО

0t/eJ

М

31510

Изобретение относится к автоматике и вымислительной технике, и может быть использовано в устройствах цифровой обработки сигналов и является усовершенствованием устройства по авт.св. № ,

Цель изобретения - расширение области возможного применения за счет формирования выходного сигнала в формате многоуровневой дельта-модуляции с переключаемой квантующей характеристикой.

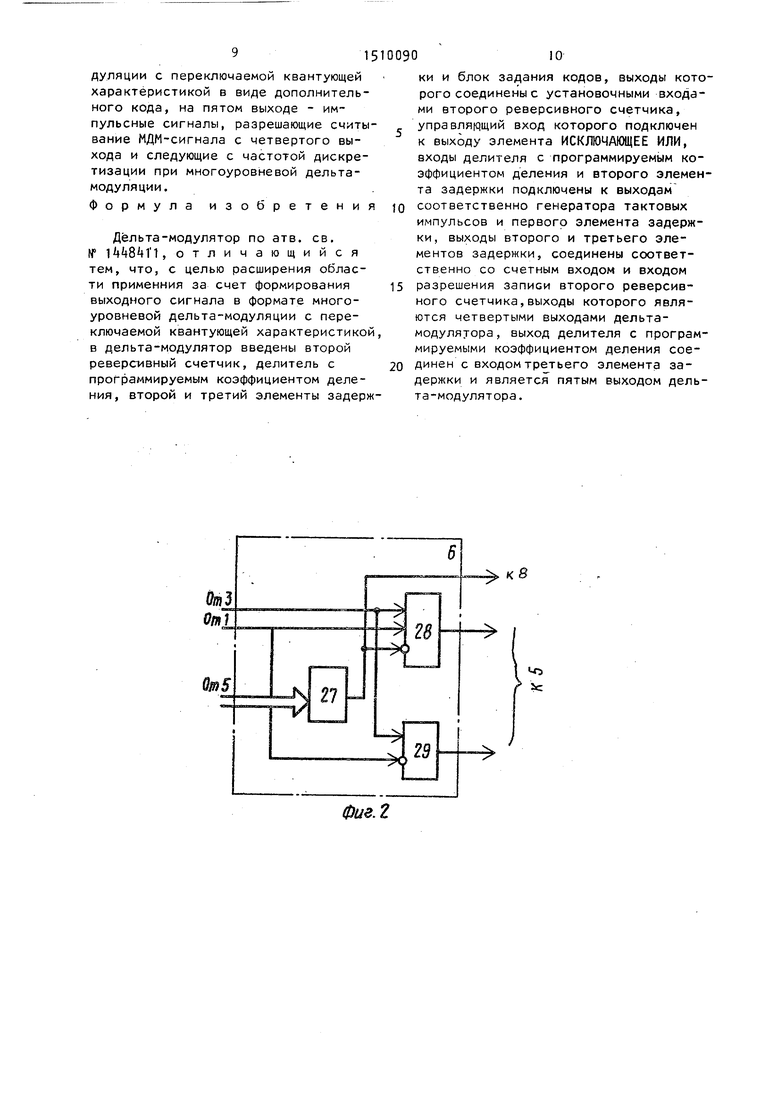

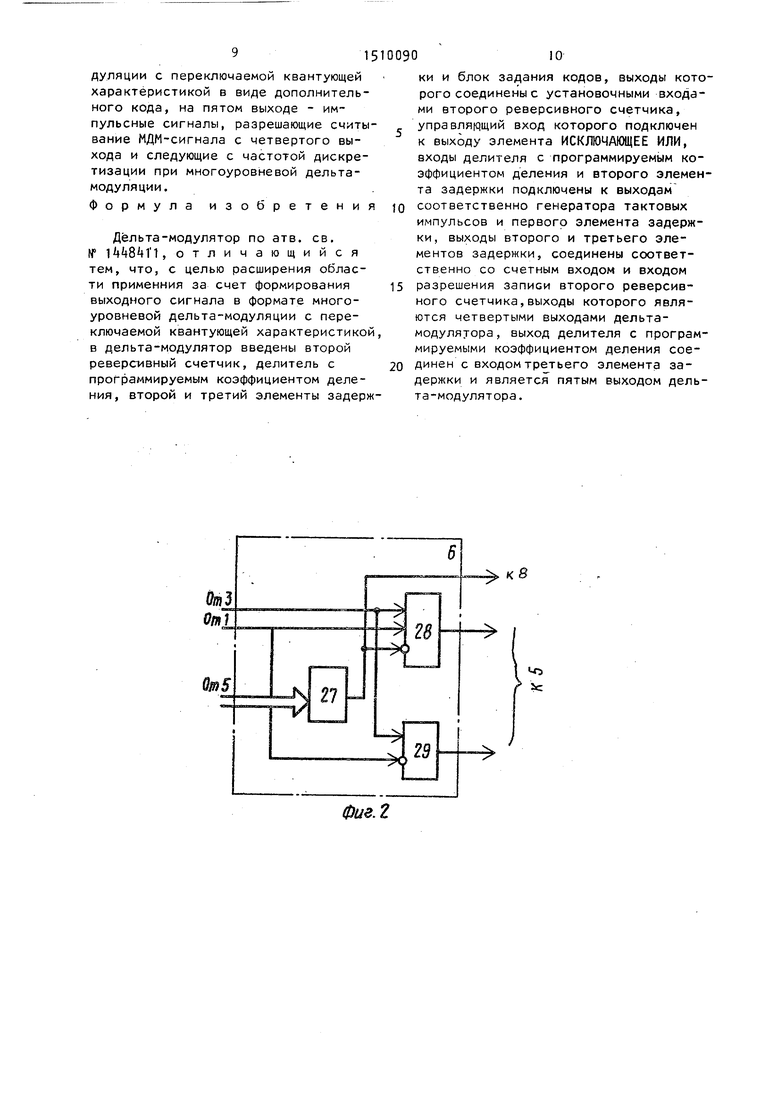

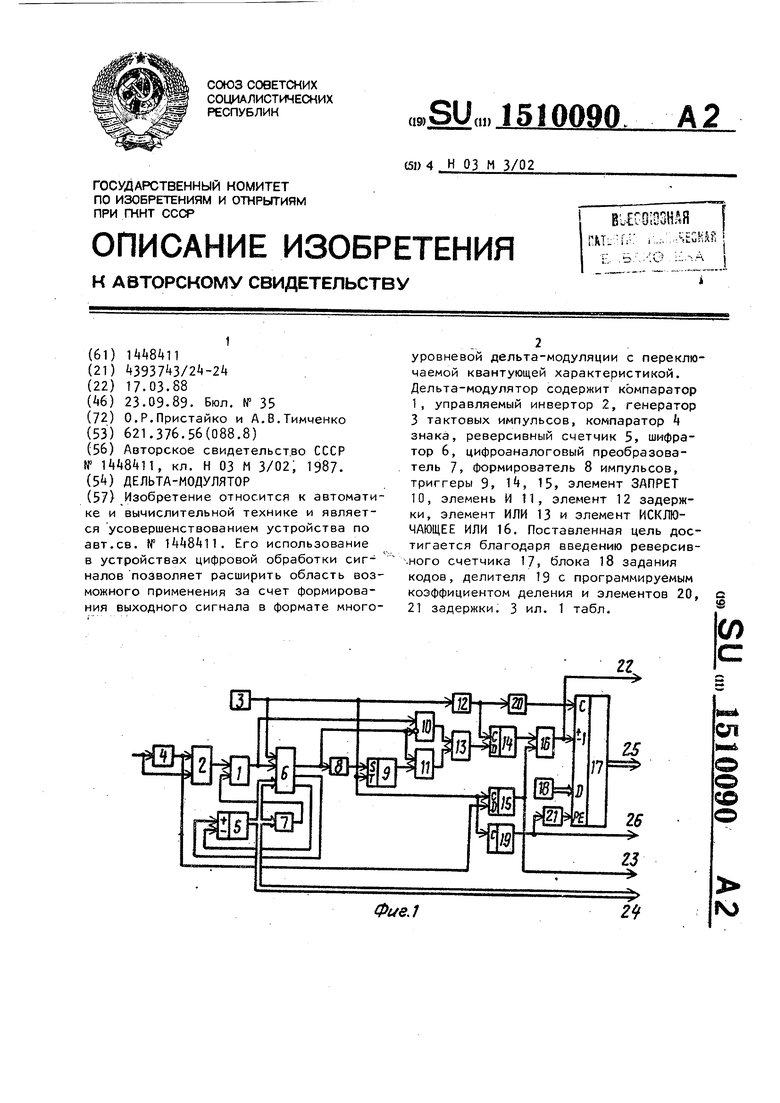

На фиг, 1 приведена функциональная схема дельта-модулятора, на фиг. 2 - выполнение шифратора; на фиг. 3 - временные диаграмм работы.

Дельта-модулятор содержит первый компаратор 1, управляемый инвертор 2, генератор 3 тактовых импульсов, вто- рой компаратор k знака, первый реверсивный счетчик 5, шифратор 6, цифро- аналоговый преобразователь 7, формирователь 8 импульсов, первый счетный триггер Э, элемент ЗАПРЕТ 10, элемент И 11, первый элемент 12 задержки, элемент ИЛИ 13, второй 14 и третий 15 D-триггеры, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 16, второй реверсивный счетчик 17, блок 18 задания кодов, делитель 19 с программируемым коэффициентом деле- ;Ния, второй 20 и третий 21 элементы задержки. На фиг, 1 обозначены первый 22, второй 23, третий 2k, четвертый 25 и пятый 2б выходы.

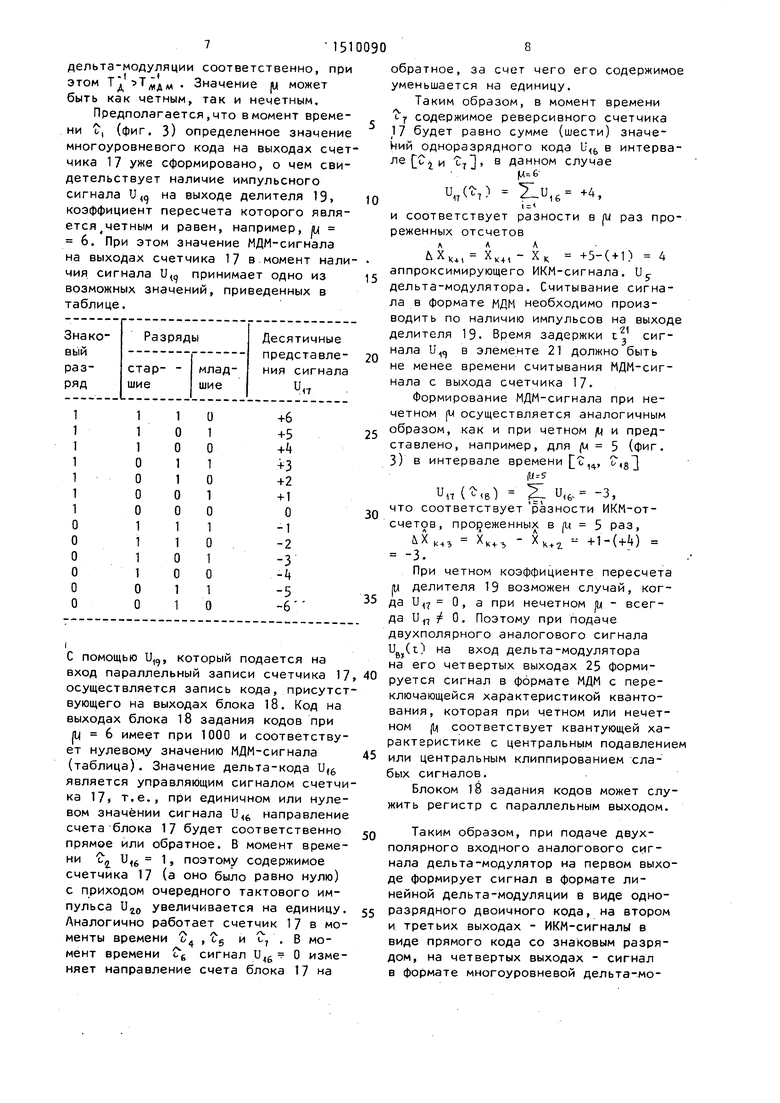

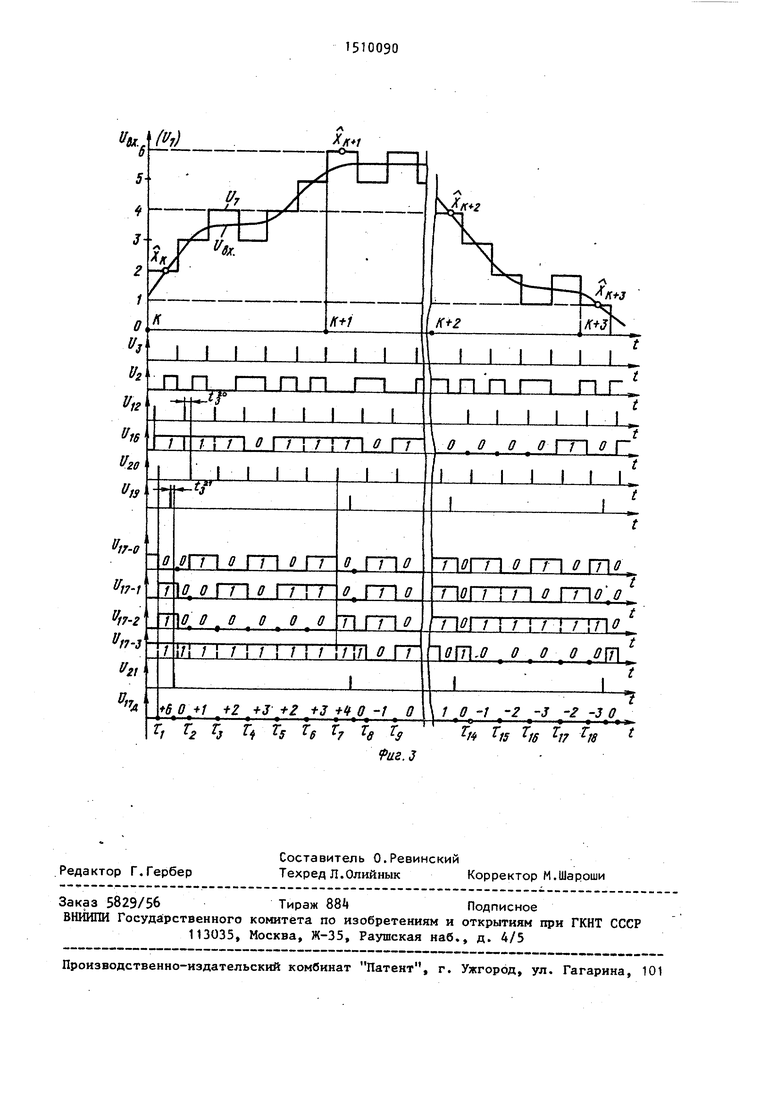

Шифратор 6 содержит (фиг. 2) элемент И 27, элементы ЗАПРЕТ 28 и 29,

Делитель 19 может быть выполнен в виде счетчика с переключаемым коэффи

циентом пересчета, когда выходы разрядов счетчика через переключатель соединены с входом обнуления счетчика.

На фиг. 3 представлены сигналы, появляющиеся на выходах соответствующих, блоков, причем обозначения фиг.1 и 3 совпадают.

Дельта-модулятор работает следующим образом.

Входной сигнал U(,(t) поступает на вход .управляе(ого инвертора 2 и вход компаратора знака. Компаратор k формирует выходные сигналы по правилу

Го, U,,(t)0,

Ь, , которые являются управляющими для блока 2. Управляющий инвертор 2 осу

0 5 0

ществляет преобразование входного сигнала по правилу

и ujt), и О,

5

0

5

0

5

V I ujt) , U4 1

т.е. выходной сигнал блока 2 является всегда неотрицательным.

Сигнал,. величина которого не выходит за интервал о, и„,где Ц - номинальное напряжение дельта-модуля- тора, с выхода инвертора 2 поступает на вход компаратора 1, на второй вход которого поступает напряжение обратной связи с преобразователя 7. Если сигнал преобразователя 7 меньше сигнала ) , положительный импульс компаратора 1 разрешает прохождение тактового импульса генератора 3 через шифратор 6 на вход сложения первого реверсивного счетчика 5- При этом величина аппроксимирующего напряжения преобразователя 7 увеличится на единицу дискретности U . Если ) и(с), то выходной импульс генератора 3 .через шифратор 6 поступает на вход вычитания счетчика 5, а это приводит к уменьшению на величину Д. сигнала преобразователя 7 обратной связи. Таким образом, при и ц е иЗ происходит слежение сигнала связи U- за сигналом U, а сигнал на первом выходе шифратора 6, фиксирующий максимальное состояние счетчика 5 отсутствует. На выходе элемента ЗАПРЕТ 10 формируется сигнал, соответствующий выходному сигналу компаратора 1, который через элемент ИЛИ 13 поступает на информационный вход триггера 14, так как сигнал на выходе элемента И 11 также отсутствует. Элемент -12 задержки необходим для согласования быстродействия блоков 1, 6 и 7 и задерживает тактовые сигналы генератора 3 на время t с ,где t - быстродействие блоков 1,5 - 7,10 и 13. Триггер 14 выполняет функцию фиксирующей цепи нулевого порядка.

Триггер 15 необходим для фиксации состояния выходного сигнала компаратора 4, которое обеспечивается с помощью тактовых импульсов генератора 3, а также управляет ра ботой элемента 1б. Выходной сигнал триггера 15 поступает на вход элемента ИСКЛОЧА- ЮЩЕЕ ИЛИ 16, в результате сигнал на выходе последнего при нулевом

состояни триггера 15 (U

1510090

вх

спаде Ug(t)

ется на обратное,

ветствует выходному сигналу триггера 1, при единичном (U -с 0) - инверсному выходному сигналу триггера 1 .

Таким образом, сигнал на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 1б соответствует приросту аппроксимирующего напряжения преобразователя 7. При этом, если входной сигнал монотонно возрастает, на выходе элемента 1б, являющегося первым выходом 22 дельта- модулятора, формируется дельта-последовательность, содержащая больше единиц, чем нулей. При монотонном это соотношение меняа в области, где

крутизна входного сигнала близка к нулю, число единиц и нулей в последовательности на выходе элемента 1б примерно одинаково. На выходе триггера 15 и выходах реверсивного счетчика 5, являющимися вторым 23 и третьим 2k выходами дельта-модулятора, формируется выходной сигнал в формате импульсно-кодовой модуляции (ИКМ), представленный прямым кодом со знаковым разрядом.

В случае равенства b выходные импульсы генератора 3 через шифратор заполняют реверсивный счетчик 5, в результате чего преобразователь 7 вырабатывает величину U-, , а на третьем выходе шифратора 6 появится импульс, который запрещает прохождение сигналов компаратора 1 через элемент ЗАПРЕТ 10, и разрешает прохождение импульсов триггера 9 через элементы И П .и ИЛИ 13 на вход триггера 1. До появления указанного импульса на третьем выходе шифратора 6 триггер 9 работает в счетном режиме, изменяя после прихода каждого тактового импульса с выхода блока 3 свое состояние на противоположное. Импульс на третьем выходе блока 6 через формирователь 8 переднего фронта устанавливает триггер 9 в единичное положение, благодаря чему устраняются сбои в выходном коде из-за неправильного фазирования выходных импульсов триггера 9.

Когда /Ug,f Иц, импульс с выхода генератора 3 не изменит состояние реверсивного счетчика 5, так как шифратор 6 блокирует прохождение тактовых импульсов на вход слежения счетчика 5 при полном его заполнения.

10

0) COOT- Одновременно с этим импульс с выхода генератора 3 изменит состояние триггера 9 на нулевое. Поэтому, при пре-. вышении входным сигналом номинального значения Uj, дельта-модулятора на выходе элемента 1б будет формироваться код -чередующая последовательность единиц и нулей, соответствующая знамению U. Таким образом, на первом выходе 22 устройства формируется одноразрядная дельта-последовательность, соответствующая входному сигналу, который находится в интервале С, UH з на втором 23 и третьем выходах формируется ИКМ-сигнал, соответствующий знаку и модулю аппроксимирующего сигнала в указанном диапазоне. При этом

20 сигналы формируются на выходах с

частотой повторения, определяемой частотой дискретизации при линейной дельта-модуляции. Если входной сигнал выходит за интервал f-U, U, на

25 первом выходе дельта-модуляторе формируется чередующая последовательность единиц и нулей, соотаетствую15

35

40

щая ограничению /Up( Uj,, а на втором и третьем выходах - сигнал в фор- 2Q мате ИКМ, равный приведенному ограничению.

Работа шифратора 6 полностью аналогична работе одноименного известного блока, понятна из приведенной на фиг. 2 функциональной схемы и в объяснениях не нуждается.

Формирование сигнала в формате многоуровневой дельта-модуляции (МДМ) на выходах второго реверсивно- гого счетчика 17, являющихся четвертыми выходами 25 устройства, осуществляется следующим образом.

Одноразрядный код U, поступает на вход сложения/вычитания реверсивного счетчика 17, на счетный вход которого через элемент 20 задержки поступают тактовые импульсы. Время

io„„

задержки сигнала t j в элементе 20 учитывает быстродействие триггера И и элемента 16 и должно быть больше времени прохождения сигнала через указанные блоки.

Делитель 19 обеспечивает деление частоты тактового генератора 3 с программируемым коэффициентом пересчета. , , : , i;, Тд /Т„д;, , где Тд и ,n- частоты дискретизации при линейной и многоуровневой

45

50

55

510090

- Од ге ге вы го вы ся но ща пе ру ва но ин ро ет ку ла

5

0

щая ограничению /Up( Uj,, а на втором и третьем выходах - сигнал в фор- Q мате ИКМ, равный приведенному ограничению.

Работа шифратора 6 полностью аналогична работе одноименного известного блока, понятна из приведенной на фиг. 2 функциональной схемы и в объяснениях не нуждается.

Формирование сигнала в формате многоуровневой дельта-модуляции (МДМ) на выходах второго реверсивно- гого счетчика 17, являющихся четвертыми выходами 25 устройства, осуществляется следующим образом.

Одноразрядный код U, поступает на вход сложения/вычитания реверсивного счетчика 17, на счетный вход которого через элемент 20 задержки поступают тактовые импульсы. Время

io„„

задержки сигнала t j в элементе 20 учитывает быстродействие триггера И и элемента 16 и должно быть больше времени прохождения сигнала через указанные блоки.

Делитель 19 обеспечивает деление частоты тактового генератора 3 с программируемым коэффициентом пересчета. , , : , i;, Тд /Т„д;, , где Тд и ,n- частоты дискретизации при линейной и многоуровневой

5

0

5

1510090

дельта-модуляции соответственно, при этом Тд , . Значение lu может быть как четным, так и нечетным.

Предполагается,что в момент времени о, (фиг. 3) определенное значение многоуровневого кода на выходах счетчика 17 уже сформировано, о чем свидетельствует наличие импульсного сигнала U на выходе делителя 19, коэффициент пересчета которого является четным и равен, например, /и 6, При этом значение МДМ-сигнала на выходах счетчика 17 в.момент нали чия. сигнала U, принимает одно из возможных значений, приведенных в таблице.

С помощью и,д, который подается на вход параллельный записи счетчика 17, осуществляется запись кода, присутствующего на выходах блока 18. Код на выходах блока 18 задания кодов при |11 6 имеет при 1000 и соответствует нулевому значению МДМ-сигнала (таблица). Значение дельта-кода и, является управляющим сигналом счетчика 17 т.е., при единичном или нулевом значении сигнала U, направление счета блока 17 будет соответственно прямое или обратное. В момент времени 1, поэтому содержимое счетчика 17 (а оно было равно нулю) с приходом очередного тактового импульса Ujo увеличивается на единицу. Аналогично работает счетчик 17 в моменты времени , и С, . В момент времени C g сигнал U О изменяет направление счета блока 17 на

5

8

обратное, за счет чего его содержимое уменьшается на единицу.

Таким образом, в момент времени содержимое реверсивного счетчика 17 будет равно сумме (шести) значе- Иий одноразрядного кода , в интервале С л и в данном случае

и-6) Z.U,, М,

|

и соответствует разности в раз прореженных отсчетов

л А А

0 5 5

0

и, (г

XK+I X К

+5-(+1) 4

аппроксимирующего ИКМ-сигнала. дельта-модулятора. Считывание сигнала в формате МДМ необходимо производить по наличию импульсов на выходе делителя 19. Время задержки сигнала , в элементе 21 должно быть не менее времени считывания МДМ-сигнала с выхода счетчика 17.

Формирование МДМ-сигнала при нечетном (Ч осуществляется аналогичным образом, как и при четном /м и представлено, например, для (U 5 (фиг. 3) в интервале времени о,,

(U--

и, (г,б) JL и,б. -3,

что соответствует разности ИКМ-от- счетов, про|эеженных в |i 5 раз,

X,,з Х,, - - +1-(+it) -3.

При четном коэффициенте пересчета /U делителя 19 возможен случай, когда и, О, а при нечетном |К - всегда и,7 0. Поэтому при подаче двухполярного аналогового сигнала UgjjCt) на вход дельта-модулятора на его четвертых выходах 25 формируется сигнал в формате МДМ с переключающейся характеристикой квантования, которая при четном или нечетном (1| соответствует квантующей характеристике с центральным подавлением или центральным клиппированием слабых сигналов.

Блоком 18 задания кодов может служить регистр с параллельным выходом.

Таким образом, при подаче двухполярного входного аналогового сигнала дельта-модулятор на первом выходе формирует сигнал в формате линейной дельта-модуляции в виде одноразрядного двоичного кода, на втором и третьих выходах - ИКМ-сигналЫ в виде прямого кода со знаковым разрядом, на четвертых выходах - сигнал в формате многоуровневой дельта-модуляции с переключаемой квантующей характеристикой в виде дополнительного кода, на пятом выходе - импульсные сигналы, разрешающие считывание МДМ-сигнала с четвертого выхода и следующие с частотой дискретизации при многоуровневой дельта- модуляции. Формула изобретения

Дельта-модулятор по атв. св. (f , отличающийся тем, что, с целью расширения области применния за счет формирования выходного сигнала в формате многоуровневой дельта-модуляции с переключаемой квантующей характеристикой в дельта-модулятор введены второй реверсивный счетчик, делитель с программируемым коэффициентом деления, второй и третий элементы задержки и блок задания кодов, выходы которого соединены с установочными входами второго реверсивного счетчика, управля|чщий вход которого подключен к выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, входы делителя с программируемым коэффициентом деления и второго элемента задержки подключены к выходам

O соответственно генератора тактовых импульсов и первого элемента задержки, выходы второго и третьего элементов задержки, соединены соответственно со счетным входом и входом

5 разрешения записи второго реверсивного счетчика,выходы которого являются четвертыми выходами дельта- модулятора , выход делителя с программируемыми коэффициентом деления сое0 динен с входом третьего элемента задержки и является пятым выходом дельта-модулятора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дельта-модулятор | 1987 |

|

SU1448411A1 |

| Дельта-модулятор | 1987 |

|

SU1425838A1 |

| Дельта-модулятор | 1990 |

|

SU1709531A2 |

| Дельта-модулятор | 1990 |

|

SU1718383A1 |

| Дельта-модулятор | 1987 |

|

SU1508350A2 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1987 |

|

SU1494210A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1989 |

|

SU1661968A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1989 |

|

SU1661969A1 |

| Дельта-модулятор | 1988 |

|

SU1543547A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1990 |

|

SU1716607A1 |

Изобретение относится к автоматике и вычислительной технике и является усовершенствованием устройства по а.с. N 1448411. Его использование в устройствах цифровой обработки сигналов позволяет расширить область возможного применения за счет формирования выходного сигнала в формате многоуровневой дельта-модуляции с переключаемой квантующей характеристикой. Дельта-модулятор содержит компаратор 1, управляемый инвертор 2, генератор 3 тактовых импульсов, компаратор 4 знака, реверсивный счетчик 5, шифратор 6,цифро-аналоговый преобразователь 7, формирователь 8 импульсов, триггеры 9, 14 , 15, элемент ЗАПРЕТ 10, элемент И 11, элемент 12 задержки, элемент ИЛИ 13 и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 16. Поставленная цель достигается благодаря введению реверсивного счетчика 17, блока 18 задания кодов, делителя 19 с программируемым коэффициентом деления и элементов 20, 21 задержки. 3 ил., 1 табл.

0/яЗ Oinl

Фие.г

r г 2 j

Г Гс г. Г;

# /У /( /7 /#

| Способ генерирования переменного тока | 1923 |

|

SU484A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-09-23—Публикация

1988-03-17—Подача