Изобретение относится к вычислительной технике, в частности к устройствам распределения заданий в вычислительной системе.

Цель изобретения - повышение достоверности выполнения пакета заданий за счет учета состояний процессоров, определенных по результатам выполнения предыдущих заданий.

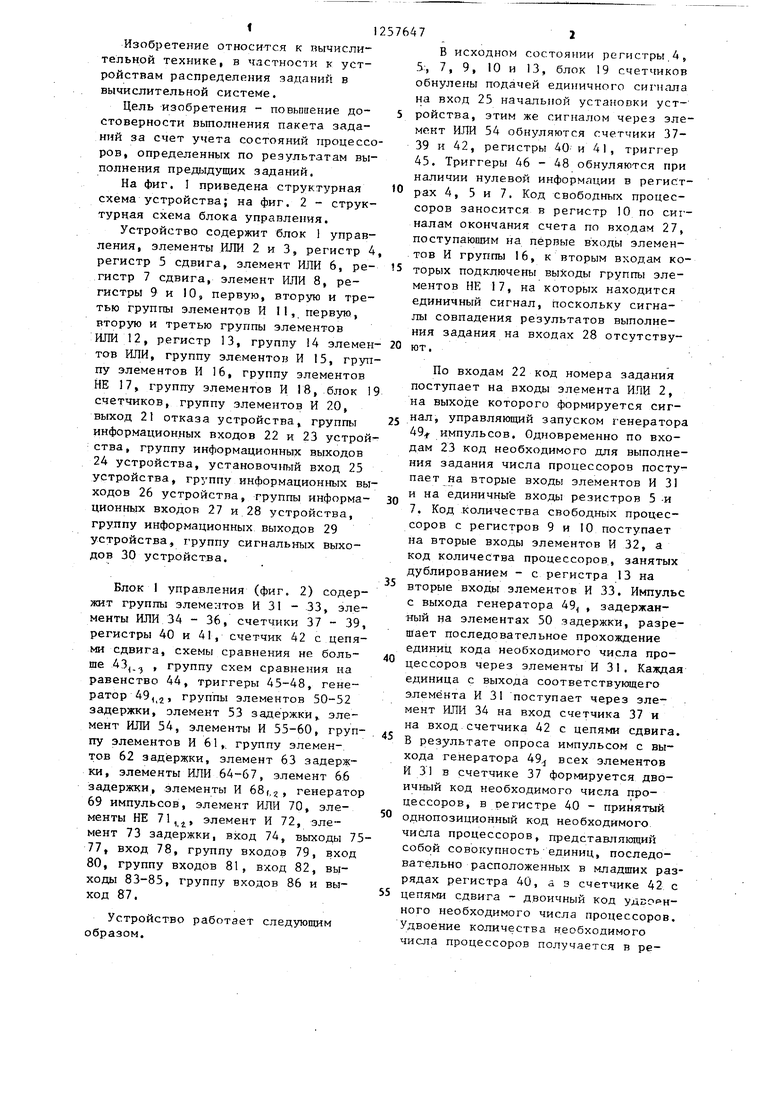

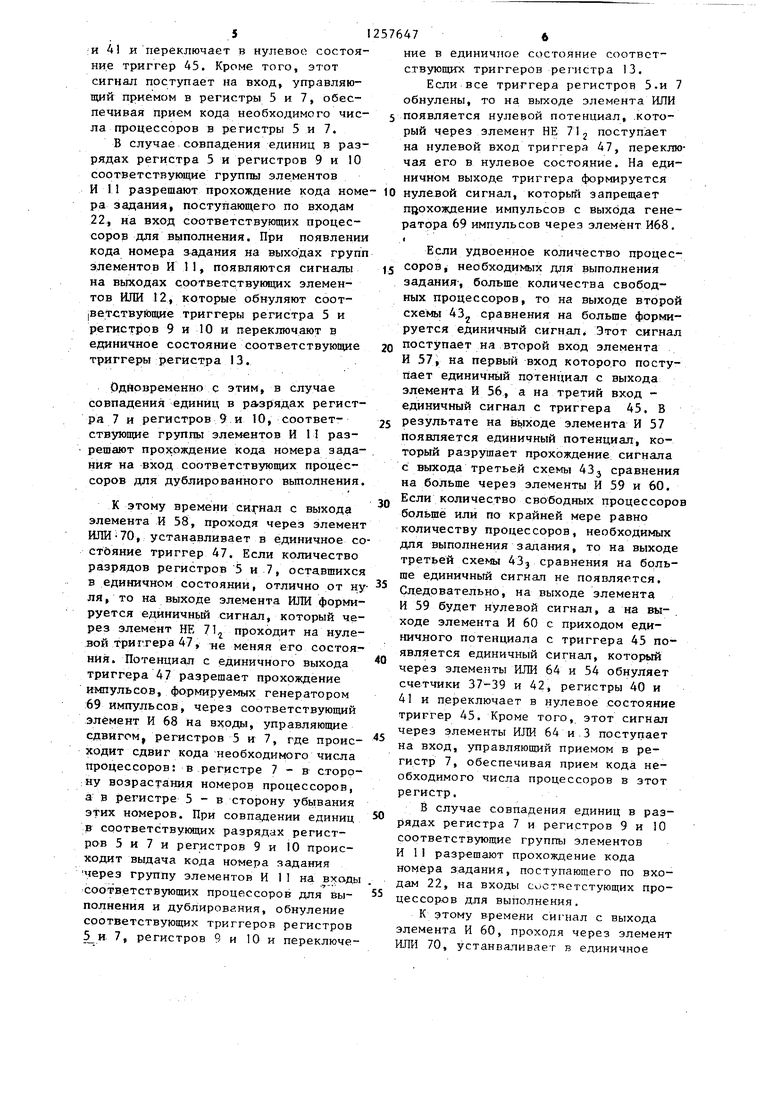

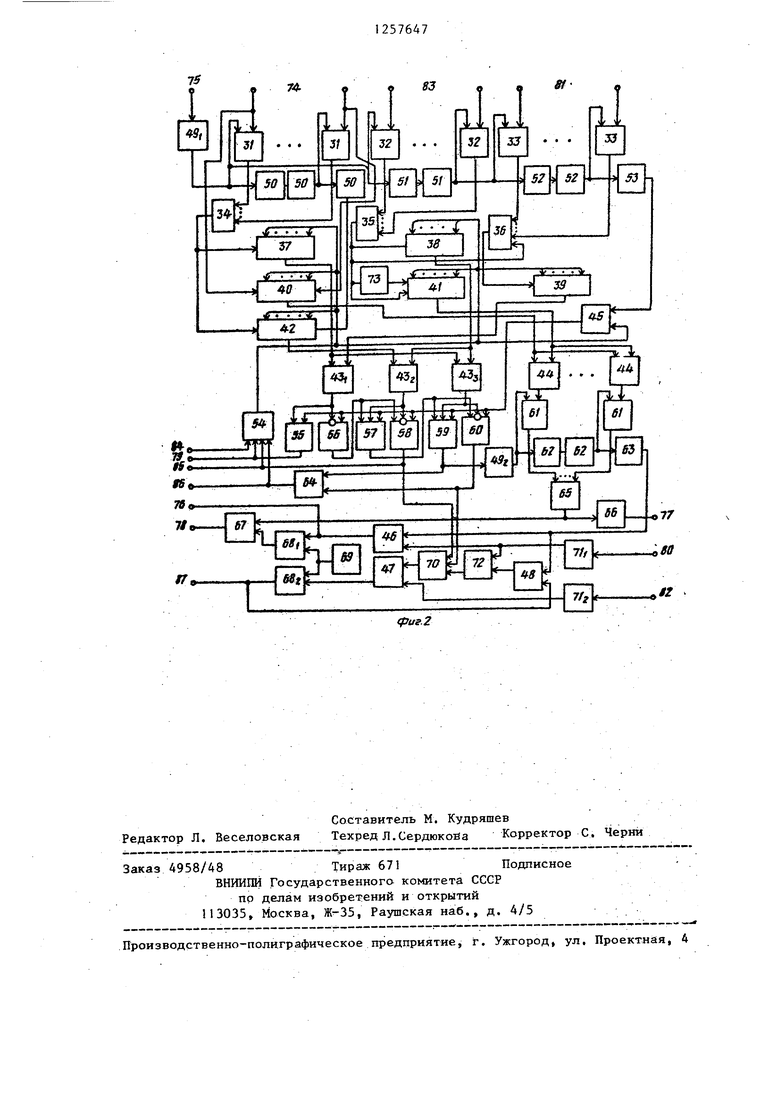

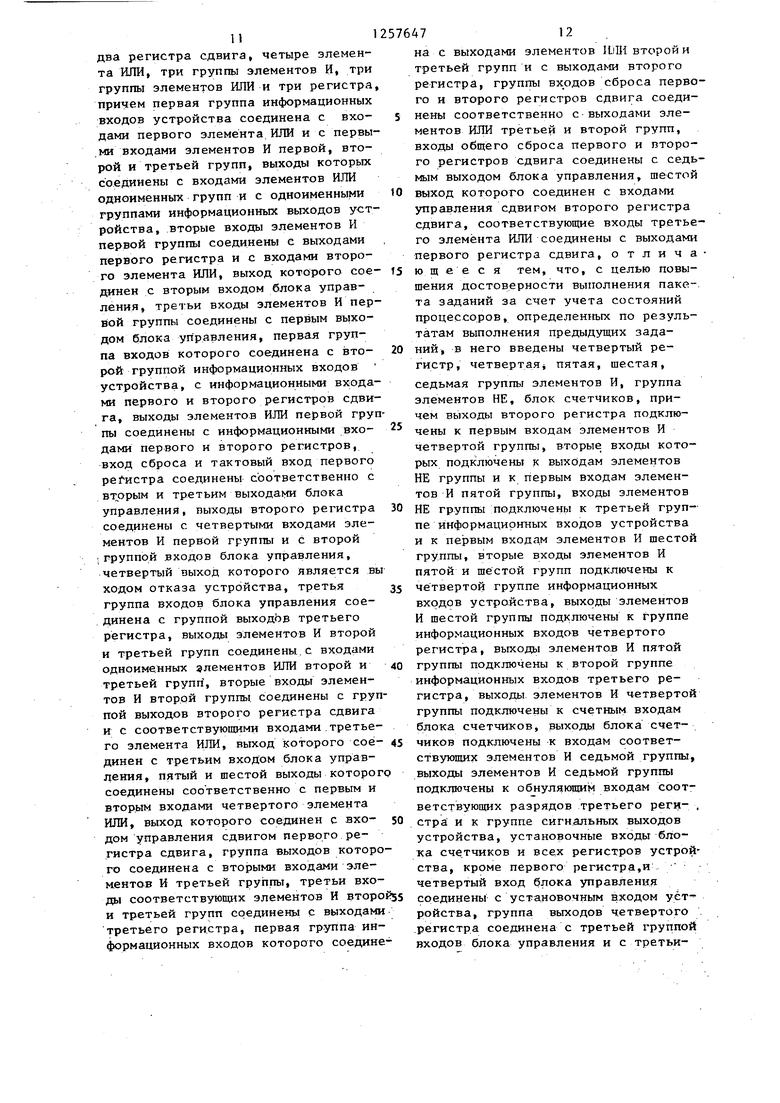

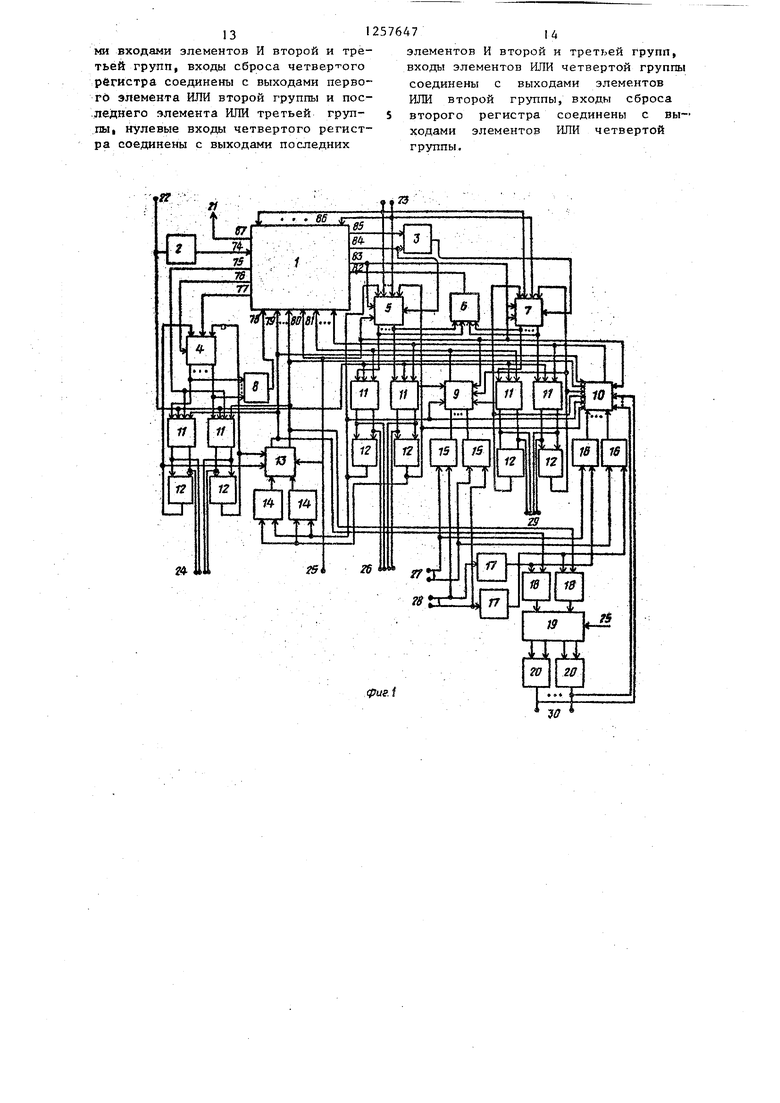

На фиг. I приведена структурная схема устройства; на фиг. 2 - структурная схема блока управления.

Устройство содержит блок 1 управления, элементы ИЛИ 2 и 3, регистр 4 регистр 5 сдвига, элемент ИЛИ 6, регистр 7 сдвига, элемент ИЛИ 8, регистры 9 и 10J первую, вторую и третью группы элементов И II, первую, вторую и третью группы элементов ИЛИ 12, регистр 13, группу 14 элементов ИЛИ, группу элементов И 15, группу элементов Ji 16, группу элементов НЕ 17, группу элементов И 18, блок 19 счетчиков, группу элементов И 20, выход 21 отказа устройства, группы информационных входов 22 и 23 устройства, группу информационных выходов 24 устройства, установочный вход 25 устройства, группу информационных выходов 26 устройства, группы информационных входов 27 и 28 устройства, группу информационных выходов 29 устройства, 1 руппу сигнальных выходов 30 устройства.

Блок I управления (фиг. 2) содержит группы элементов И 31 - 33, элементы ИЛИ 34 - 36, счетчики 37 - 39, регистры 40 и 41, счетчик 42 с цепями сдвига, схемы сравнения не больше 43 , группу схе.м сравнения на равенство 44, триггеры 45-48, генератор 49,,2 группы элементов 50-52 задержки, элемент 53 задержки, элемент ИЛИ 54, элементы И 55-60, группу элементов И 61,, группу элементов 62 задержки, элемент 63 задержки, элементы ИЛИ 64-67, элемент 66 задержки, элементы И 68, , генератор 69 импульсов, элемент ИЛИ 70, элементы НЕ 71,,, элемент И 72, элемент 73 задержки, вход 74, выходы 75 77, вход 78, группу входов 79, вход 80, группу входов 81, вход 82, выходы 83-85, группу входов 86 и выход 87.

Устройство работает следующим образом.

В исходном состоянии регистры.4, 5, 7, 9, 10 и 13, блок 19 счетчиков обнулены подачей единичного сигнала на вход 25 начальной установки устройства, этим же сигналом через элемент ИЛИ 54 обнуляются счетчики 37- 39 и 42, регистры 40 и 41, триггер 45, Триггеры 46 - 48 обнуляются при наличии нулевой информации в регистpax 4, 5 и 7. Код свободных процессоров заносится в регистр 10 по сигналам окончания счета по входам 27, поступаЮЕЦИм на первые входы элементов И группы 16, к вторым входам которых подключены выходы группы элементов НЕ 17, на которых находится единичный сигнал, поскольку сигналы совпадения результатов выполнения задания на входах 28 отсутствуют.

По входам 22 код номера задания поступает на входы элемента ИЛИ 2, на выходе которого формируется сигнал, управляющий запуском генератора 49.f импульсов. Одновременно по входам 23 код необходимого для выполнения задания числа процессоров поступает На вторые входы элементов И 31 и на единичные входы резистров 5 -и 7, Код количества свободных процессоров с регистров 9 и 10 поступает на вторые входы элементов И 32, а код количества процессоров, занятых дублированием - с регистра 13 на

вторые входы элементов И 33, Импульс с выхода генератора 49, , задержанный на элементах 50 задержки, разрешает последовательное прохождение единиц кода необходимого числа процессоров через элементы И 31. Каждая единица с вь1хода соответствующего элемента И 31 поступает через элемент ИЛИ 34 на вход счетчика 37 и на вход счетчика 42 с цепякш сдвига,

В результате опроса импульсом с выхода генератора 49,j всех элементов И 31 в счетчике 37 формируется двоичный код необходимого числа процессоров, в регистре 40 - принятый

однопозиционный код необходимого числа процессоров, представляющий собой совокупность единиц, последовательно расположенных в младших разрядах регистра 40, а з счетчике 42 с

цепями сдвига - двоичный код удпорн- ного необходимого числа процессоров, Удвоение количества необходимого числа процессоров получается в ре

зультате сдвига содержимого счетчи- ка 42 на один разряд влево по импуль- су, поступающему с последнего элемента 50 задержки на сдвигающий вход счетчика 42. Импульс с выхода первого генератора 49, импульсов, задержанный на элементах 51 задержки также разрешает последовательное прохождение единиц кода количества свободных процессоров через элементы И 32. Каждая единица с выхода соответствующего элемента И 32 поступает через элемент ИЛИ 35 на вход счетчика 38 и на вход, управляющий сдвигом регистра 41, производя сдвиг вправо содер- 15 жимого регистра, что обеспечивает освобождение старшего разряда для приема очередной единицы кода количества свободных процессоров через

10

элемент 73 задержки. Кроме того, каж-20 схемы 43 сравнения на больше фордая единица проходит через элемент ИЛИ 36 на вход счетчика 39. В результате этого в счетчиках 38 и 39 формируется двоичный код количества свободных процессоров, а в регистре 41 - однопозиционный код, представляющий собой совокупность единиц, количество которых равно количеству свободных процессоров.

Импульс с выхода последнего эле- мента 51 задержки, задержанный на .элементах 52 задержки, разрешает последовательное прохождение единиц кода количества процессоров, занятых дублированием, через элементы И 33. Каждая единица с выхода соответствующего элемента И 33 поступает через элемент ИЛИ 36 на вход счетчика 39, формируя тем самым двоичный код суммы количества свободных процессоров и количества процессоров, занятых дублированием.

Сигнал с выхода последнего элемента 52 задержки задерживается на

элементе 53 задержки. Время задержки 45Удвоенное количество процессоров, не

выбирается таким, чтобы импульс собходимых для вьтолнения зйдания,

выхода элемента 53 задержки переклю-меньше или по крайней мере равно кочал триггер 45 в единичное состояниеличеству свободных процессоров, то

только После того, когда на счетчи-на выходе второй схемы 43 сравнения ,

ках 37-39, регистрах 40 и 41 и счет- 50на больше единичный сигнал не появчике 42 с цепями сдвига закончится процесс формирования кодов.

Двоичный код необходимого числа процессоров, полученный на счетчике 37, поступает на первый вход первой схемы 43 сравнения на больше и на первый вход третьей схемы 43, сравнения на больше. Двоичный код уд15

576474

военного необходимого числа проце с- соров, полученный на счетчике 42, с цепями сдвига, поступает на первый вход второй схемы 43 сравнения на 5 больше. Двоичный код количества свободных процессоров, полученный на счетчике 38, поступает на вторые входы второй 43j и третьей 43} схем сравнения на больше, а двоичный код 10 суммы количества свободных процессоров и количества процессоров, занятых дублированием, полученный на счетчике 39 - на второй вход первой схемы 43 сравнения на больше.

Если количество процессоров, необходимых для выполнения задания, больше суммы количеств свободных процессоров и процессоров, занятых дублированием, то на выходе первой

мируется единичный сигнал, который поступает на первый вход элемента И 55, на второй вход которого поступает единичный сигнал с триггера 45 в результате на выходе элемента И 55 появляется единичный потенциал, который поступает на выход 21 в качестве сигнала отказа от выполнения задания. Кроме того, этим сигналом через элемент ИЛИ 54 производится обнуление счетчиков 37-39 и 42, регистров 40 и 41, и триггер 45 переключается в нулевое состояние. При этом на выходе элемента И 56 формируется нулевой сигнал, который блоки-.

рует выходы второй 43 и третьей 43 схем сравнения на больше.

Если количество, необходимых про- цессоров меньше или равно количеству свободных, то на выходе элемента И 56 появляется единичный потенциал, который разрешает прохождение сигнала с выхода второй схемы 432, сравнения через элементы И 57 и 58. Если

J

Удвоенное количество процессоров, не

ляется. Следовательноj нулевой сигнал с выхода элемента И 57 .блокирует выход третьей схемы 43 сравнения, а на выходе элемента И 58 .с появлением единичного потенциала с триггера 45 формируется единичный сигнал, который через элемент ИЛИ 54 обнуляет счетчики 37-39 и 42, регистры 40

и 4 л переключает в нулевое состояние триггер 45. Кроме того, этот сигнал поступает на вход, управляющий приемом в регистры 5 и 7, обеспечивая прием кода необходимого числа процессоров в регистры 5 и 7.

В случае совпадения единиц в разрядах регистра 5 и регистров 9 и 10 соответствующие группы элементов

И 11 разрешают прохождение кода номе- 10 нулевой сигнал, которьп1 запрещает

ра задания, поступающего по входам 22, на вход соответствующих процессоров для выполнения. При появлении кода номера задания на выходах групп элементов И 11, появляются сигналы на выходах соответствующих элемен тов ИЛИ 12, которые обнуляют соот- ретствуйщие триггеры регистра 5 и регистров 9 и 10 и переключают в единичное состояние соответствующие триггеры регистра 13.

Одновременно с этим, в случае совпадения единиц в ра-зрядах регистра 7 и регистров 9 и 10, соответствующие групгы элементов И 1I разрешают прохождение кода номера зада- ния- на вход соответствуюпщх процессоров для дублированного выполнения.

К этому времени сигнал с выхода элемента И 58, про-ходя через элемент ИЛИ-УО, устанавливает в единичное со- стЬяние триггер 47. Если количество разрядов регистров 5 и 7, оста,вщихся

15

20

25

30

прохождение импульсов с выхода ген ратора 69 импульсов через элемент И6 I ,

Если удвоенное количество проце соров, необходимых для выполнения задания-, больше количества свободных процессоров, то на выходе втор схемы 43 сравнения на больше форм руется единичный сигнал Этот сигн поступает на второй вход элемента И 57, на первый вход которого пос пает единичньгй потенциал с выхода элемента И 56, а на третий вход - единичный сигнал с триггера 45. результате на выходе элемента И 5 появляется единичный потенциал, ко торый разрушает прохождение сигнал с выхода третьей схемы 43з сравнен на больше через элементы И 59 и 60 Если количество свободных процессо больщё или по крайней мере равно количеству процессоров, необходимы для выполнения задания, то на выхо третьей схемы 43з сравнения на бол ше единичный сигнап не появля тся

в единичном состоянии, отлично от ну- 35 Следовательно, на выходе элемента

ля, то на выходе элемента ИЛИ формируется единичный сигнап, который через элемент НЕ 71 проходит на нулевой триггера 47, не меняя его состояния. Потенциал с единичного выхода триггера 47 разрешает прохождение импульсов, формируемых генератором :69 импульсов, через соответствующий элемент И 68 на входы, управляющие сдвигом, регистров 5 и 7, где проис- ходит сдвиг кода необходимого числа процессоров: в регистре 7 - в сторо- :ну возрастания номеров процессоров, а в регистре 5 - в сторону убывания этих номеров. При совпадении единиц В соответствующих разрядах регистров 5 и 7 и регистров 9 и 10 происходит выдача кода номера задания через группу элементов И 11 на соответствующих процессоров для вы- 55 полнения и дублирования, обнуление соответствующих триггеров регистров 5 и. 7, регистров 9 и 10 и переключеИ 59 будет нулевой сигнал, а на вы ходе элемента И 60 с приходом единичного потенциала с триггера 45 п является единичный сигнал, который через элементы ИЛИ 64 и 54 обнуляе счетчики 37-39 и 42, регистры 40 и 41 и переключает в нулевое состоян триггер 45. Кроме того, этот сигна через элементы ИЛИ 64 и.3 поступае на вход, управляющий приемом в регистр 7, обеспечивая прием кода не обходимого числа процессоров в это регистр.

В случае совпадения единиц в ра рядах регистра 7 и регистров 9 и соответствующие группы элементов И 11 разрешают прохождение кода номера задания, поступающего по вх дам 22, на входы состиетстующих пр цессоров для выполнения,

К этому времени си1-цал с выхода элемента И 60, проходя через элеме ИЛИ 70, устанваливает в единичное

ние в единичное состояние соотвст- ствующкх триггеров регистра 13,

Если все триггера регистров 5.и 7 обнулены, то на выходе элемента ИЛИ 5 появляется нулевой потенциал, .который через элемент НЕ 712 поступает на нулевой вход триггера 47, переключая его в нулевое состояние. На единичном выходе триггера формируется

прохождение импульсов с выхода генератора 69 импульсов через элемент И68, I ,

Если удвоенное количество процессоров, необходимых для выполнения задания-, больше количества свободных процессоров, то на выходе второй схемы 43 сравнения на больше формируется единичный сигнал Этот сигнал поступает на второй вход элемента И 57, на первый вход которого поступает единичньгй потенциал с выхода элемента И 56, а на третий вход - единичный сигнал с триггера 45. В результате на выходе элемента И 57 появляется единичный потенциал, который разрушает прохождение сигнала с выхода третьей схемы 43з сравнения на больше через элементы И 59 и 60. Если количество свободных процессоров больщё или по крайней мере равно количеству процессоров, необходимых для выполнения задания, то на выходе третьей схемы 43з сравнения на больше единичный сигнап не появля тся.

Следовательно, на выходе элемента

И 59 будет нулевой сигнал, а на выходе элемента И 60 с приходом единичного потенциала с триггера 45 появляется единичный сигнал, который через элементы ИЛИ 64 и 54 обнуляет счетчики 37-39 и 42, регистры 40 и 41 и переключает в нулевое состояние триггер 45. Кроме того, этот сигнал через элементы ИЛИ 64 и.3 поступает на вход, управляющий приемом в регистр 7, обеспечивая прием кода необходимого числа процессоров в этот регистр.

В случае совпадения единиц в разрядах регистра 7 и регистров 9 и 10 соответствующие группы элементов И 11 разрешают прохождение кода номера задания, поступающего по входам 22, на входы состиетстующих процессоров для выполнения,

К этому времени си1-цал с выхода элемента И 60, проходя через элемент ИЛИ 70, устанваливает в единичное

: . 7 .

состояние триггер 47. Если количество триггеров регистра 7, оставшихся в единичном состоянии, отлично от нуля, на выходе элемента ИЛИ 6 формируется единичный сигнал, который через элемент НЕ 712 проходит на нулевой вход триггера 47, не меняя его состояни Я. Потенциал с единичного выхода триггера 47 разрешает прохождение импульсов, формируемых гене ратором 69 импульсов, на вход, уп- равляювшй сдвигом, регистра 7, где происходит сдвиг кода необходимого числа процессоров в сторону возрастания номеров процессоров. При сок- падении едданид в соответствующих разрядах регистра 7 и-регистров 9 и 10 происходит вьздача кода номера задания через группу элементов И П на входы соответствующих процессоров и обнуление соответствующих разрядов регистра; 7 и регистров 9 и 10.

Если все разряда регистра 7 обнулены, то на выходе элемента ИЛИ 6 появляется нулевой потенциал, который через второй инвертор 712 поступает на нулевой вход триггера 47, переключая его в нулевое состояние. На единичном выходе триггера формируется нулевой ситная, который запре щает прохождение импульсов с выхода генератора 69 импульсов через эле- меит И 68.

Если количество процессоров, необходимых для выполнения задания, больше количества свободных процессо ров, то на выходе третьей схемы 43 сравнения на больше формируется еди- иич{0 1й сигнал. Этот сигнал поступает на второй вход элемента И 59, на первый вход которого поступает единичный потенциал с вь1хода элемента И 57, а на третий вход - единичш 1й .сигнал с триггера 45. В результате на выходе элемента И 59 появляется единичный потенциал, который через элементы ШШ 64 и 3 поступает на вход, управляющий приемом в регистр 7, обеспечивая прием кода необходимого числа процессоров в этот регистр, а через элементы ИЛИ 64 и 54 обнуляет счетчики 37-39 и 42, регистры 40 и 41 и переключает в нулевое .состояние триггер 45. Кроме того,этот потенциал запускает второй генератор 49грдиночных импульсов.

Одновременно однопозиционный код количества свободных процессорюв,

576478

находящийся в регистре 41, поступает на первые входы одноразрядных схем 44 сравнения на равенство, на вторые входы которых поступают соответству- 5 ющие разряды однопозшшчэнного кода количества процессоров, необходимых для выполнения задания, находящегося в регистре 40, Если на входы одноразрядной схемы сравнения на ра10 венство поданы одинаковые сигналы

(оба нули или оба единицы), то на выходе схемы появляется нулевой потенциал, если на входе - разные сигналы, то на выходе формируется единич- Г5 ный потенциал. Таким образом, на выходах одноразрядных схем 44 сравнения на равенство образуется одно- позиционный код, представляющий собой совокупность единиц, количество 20 которых равно разности меаду количеством процессоров, необходимых для выполнения задачи, и количеством бодных процессоров.

Импульс с выхода второго генерато- 25 ра 49, , задержанный на элементах задержки 62, разрешает последовательное прохождение единиц кода разности через элементы И 61. Каждая единица с выхода соответствующего элемента

30 И 61 поступает через элементы ШШ 65 . и 67 на вход, управляюций сдвигом, регистра 4, производя сдвиг вправо содержимого регистра, что обеспечивает освобождение старшего разряда ,, для приема очередной единицы кода разности через элемент 66 задержки. Сигнал с выхода последнего элемен- та 62 задержки задерживается на элементе 63 задержки (время задержки д .выбирается таким, чтобы импульс с вы- хода элемента 63 задержки переключал триггеры 46 и 48 в единичное состояние только после того, когда на регистре 4 закончится процесс формиро- 5 вания кода).:

В случае совпадения единиц в разрядах регистров 4 и 13 при появлении единичного потенциала с триггера 46 соответствующие группы элементов

0 И I1 разрешают прохождение кода номера задания, поступающего по шинам номера задания, на вход соответствующих процессоров для их освобождения от дублирования. При появлении кода

5 номера задания на выходах групп элементов И 11 появляются сигналы на входах соответствующих элементов ИЛИ 12, которые обнуляют соответ

ствующие триггеры регистров 13 и 4 и переключают в единичное состояние соответствующие триггеры регистров 9 и 10.

Если Количество триггеров регистра 4, оставшихся в единичном состоянии, отлично от нуля, то на выходе элемента ИЛИ 8 формируется единичный сигнал, который через элемент НЕ 71 проходит на нулевой вход триггера 47, не меняя его состояния, Потен- 1щал с единичного выхода триггера 46 разрешает прохождение импульсов, формируемых генератором 69 импульсов через соответствующий элемент И 68 И элемент ИЛИ 67 на вход, управлякаци сдвигом регистра 4, где происходит сдвиг кода в сторону убыв ания номе-. ров процессоров. ри совпадении единиц в соответствующих разрядах реги- стров 4 и 13 происходит вьщача кода номера задания через группу элемен тов И 11 на входа соответствуютшх процессоров для их освобождения от дублированного выполнения заданий, обнуление соответствующих триггеров 4 и 13 и переключение в единичное еЬстояние соответствующих триггеров регистров 9 и 10.

Если ,все триггеры регистра 4 обнулены, то на выходе элемента ИЛИ В появляется нулевой потенциал, которы через элемент НЕ 7 Ц поступает на нулевой вход триггера 46, переключая его в нулевое состояние, На единич- ком ьъкоде.триггера формируется нуле вой сигнал, который запрещает прохождение импульсов с выхода генератора 69 импуяь.сов через соответствуй- щий элемент И 68. Одновременно с этим еданичньш сигнал с выхода элемента НЕ 7 проходит через элемент И 72, на второй вход которого подается единичньШ потенциал с выхода триггера 48, и элемент ИЛИ 70, уста- навливая триггер ,47 в единичное состояние.

В случае совпадения разрядов регистра 7 и регистров 9 и Ю группы

;элементов И II разрешают прохождение кода номера задания на входы со- ртёетствующих процессоров. При появлений кода номера задания на выходах групп элементов ИИ появляются сигналы на выходах элементов ИЛИ 12, которые обнуляют триггеры регнст/ров 7, 9 и 10, Если количество триггеров регистра 7, оставшихся в еди

10

20

25

15

35. 4045

5764710

ничном состоянии, отлично от нуля, на выходе элемента ИЛИ 6 формируется единичный сигнал, который через элемент 712 проходит на нулевой вход триггера 47, не меняя его состояния. Потенциал с единичного выхода триггера 47 разрешает прохождение импульсов, формируемых генератором 69 Им- пульсов, на вход, управляющий сдвигом регистра 7, где происходит сдвиг кода необходимого числа процессоров в сторону возрастания номеров процессоров. При совпадении разрядов регистров 7, 9 и 10 происходит выдача кода номера задания через группу элементов И {1 на входа процессоров и обнуление разрядов регистров 7, 9 и 10VE.cjm нее триггеры регистра 7 обнулены, то на выходе элемента ИЛИ 6 появляется нулевой потенциал, который через элемент НЕ 7 поступает на нулевой вход триггера 47, переключая его в нулевое состояние. На единичном выходе триггера формируется сигнал, который запрещает прохождение импульсов с выхода генератора 69 импульсов через элемент И 68.

По окончании выполнения задания с процессоров на входы 27 поступают сигналы окончания выполнения задания, которые подключены к первым входам элементов И 15 и 16, к вторым входам группы элементов И 15под- ключен сигнал совпадения результатов выполнения задания, при совпадении сигналов взводятся соответству- юпще триггеры регистра 9, к вторым входам группы элементов И 16 подключен .сигнал несовпадения результатов выполнения задания, сформированный группой з1лементов НЕ 17. Таким образом, группа элементов И 16 управляет тгриемом в регистр 10. Кроме .того, сигнал несовпадения результатов вьшолнения задания с процессоров, занятых дублированием, поступает на счетный вход соответствующего счетчика блока 9. Если количество несовпадений в счетчике становится больше или равно трем, то ма выходе соответствующего элемента И 20 формируется сигнал блокировки, который обну- 4яет соответствующий разряд регистра 0.

55 Формула изобретения

Устройство для распределения заданий, содержащее блок управления,

30

50

11

два регистра сдвига, четыре элемента ИЛИ, три группы элементов И, три группы элементов ИЛИ и три регистра причем первая группа информационных входов устройства соединена с входами первого элемента.ИЛИ и с первыми входами элементов И первой, второй и третьей групп, выходы которых соединены с входами элементов ИЛИ одноименных групп и с одноименными группами информационных выходов устройства, вторые входы элементов И первой группы соединены с выходами первого регистра и с входами второго элемента ИЛИ, выход которого сое- динен с вторым входом блока управления, третьи входы элементов И первой группы соединены с первым выходом блока управления, первая группа входов которого соединена с второй группой информационных входов устройства, с информационными входами первого и второго регистров сдвига, выходы элементов ИЛИ первой группы соединены с информационными входами первого и второго регистров, вход сброса и тактовый вход первого ре1 истра соединены соответственно с втррым и третьим выходами блока управления, выходы второго регистра соединены с четвертыми входами элементов И первой группы и с второй

.группой входов блока управления, четвертый выход которого является вы ходом отказа устройства, третья группа входов блока управления соединена с группой выходов третьего регистра, выходы элементов И второй и третьей групп соединены.с входами одноименных элементов ИЛИ второй и третьей групп , вторые входы элементов И втор.рй группы, соединены с группой выходов второго регистра сдвига и с соответствующими входами .третьего элемента ИЛИ, выход которого сое- динен с третьим входом блока управления, пятый и шестой выходы которог соединены соответственно с первым и вторым входами четвертого элемента ИЛИ, выход которого соединен с вхо- дом управления сдвигом первого регистра сдвига, группа выходов которого соединена с вторыми входами элементов И третьей группы, третьи входы соответствующих элементов И второ и третьей групп соединень с выходами

третьего регистра, первая группа информационных входов которого соедине

10

20

25

t5 4550 55

25764712

на с выходами элементов lliffl второй и третьей групп и с выходами второго регистра, группы сброса первого и второго регистров сдвига соединены соответственно с выходами элементов ИЛИ третьей и второй групп, входы общего сброса первого и второго регистров сдвига соединены с седьмым выходом блока управления, шестой выход которого соединен с входами управления сдвигом второго регистра сдвига, соответствующие входы третьего элемента ИЛИ соединены с выходами первого регистра сдвига, отличающее с я тем, что, с целью повышения достоверности выполнения паке-, та заданий за счет учета состояний процессоров, определенных по результатам выполнения предыдущих заданий, в него введены четвертый регистр, четвертая, пятая, шестая, седьмая группы элементов И, группа элементов НЕ, блок счетчиков, причем выходы второго регистра подключены к первым входам элементов И четвертой группы, вторые входы которых подключены к выходам элементов НЕ группы и к первым входам элементов И пятой группы, входы элементов НЕ группы подключены к третьей группе информационных входов устройства и к первым входам элементов И шестой группы, вторые входы элементов И пятой и шестой групп подключены к четвертой группе информационных входов устройства, выходы элементов И шестой группы подключены к группе информационных входов четвертого регистра, выходы элементов И пятой группы подключены к второй группе информационных входов третьего регистра, выходы, элементов И четвертой группы подключены к счетным входам блока счетчиков, выходы блока счетчиков подключены к входам соответствующих элементов И седьмой группы, выходы элементов И седьмой группы подключены к обнуляющим входам соответствующих разрядов третьего реги- , стра: и к группе сигнальных выходов устройства, установочные входы блока сче.тчиков и всех регистров устройства, кроме первого регистра,и четвертый вход блока управления соединены с установочным входом уёт- ройства, группа выходов четвертого . регистра соединена с третьей группой входов блока управления и с третьи30

35

40

ми входами элементов И второй и третьей групп, входы сброса четвер т ого регистра соединены с выходами первого элемента ИЛИ второй группы и пос- .деднего элемента ИЛИ третьей группы i нулевые входы четвертого регистра соединены с выходами последних

элементов И второй и третьей Групп, входы элементов ИЛИ четвертой группы соединены с выходами элементов ИЛИ второй группы, входы сброса второго регистра соединены с выходами элементов ИЛИ четвертой группы.

fT

12

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения заданий | 1980 |

|

SU903876A1 |

| Устройство для распределения заданий в вычислительной системе | 1982 |

|

SU1022164A1 |

| Устройство для распределения заданий в сетях электронных вычислительных машин | 1982 |

|

SU1075261A1 |

| Устройство для управления распределенной вычислительной системой | 1982 |

|

SU1136159A1 |

| Устройство для распределения заданий вычислительной системе | 1982 |

|

SU1100623A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1481762A2 |

| Устройство для распределения заданий процессорам | 1983 |

|

SU1126963A1 |

| Устройство для распределения заданий процессорам | 1984 |

|

SU1246096A1 |

| Устройство для распределения заданий процессорам | 1989 |

|

SU1615721A1 |

| Устройство для распределения заданий процессорам | 1984 |

|

SU1183967A1 |

Изобретение относится к облас- Iти вычислительной техники и может :быть использовано в устройствах для распределёгшя заданий в многопроцессорных вычислительны х системах. Цель изобретения - повьтение достоверное- : ти выполнения пакета заданий за счет учета состояний процессоров, определенных по результатам выполнения предыдущих заданий. Устройство содержит блок управления, элементы ИЛИ, группы элементов И, группы элементов ИЖ, регистры, группу элементов НЕ, блок счетчиков, два регистра сдвига. В устройстве можно использовать естественную избыточность в многопроцессорных вычислительных системах и, тем самым, повьтшать достоверность выполнения пакета заданий. 2 ил. i (Л to ел к Р5 i4 Ч

| Паровозный котел | 1928 |

|

SU9572A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для распределения заданий | 1980 |

|

SU903876A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-15—Публикация

1984-04-13—Подача