1022164

входами первого и второго эпементов И, ственно с первым и вторым входами з&входы и выходы второго и третьего фор- пуска б пока и с единичными входами пер мирователей импульсов соединены соответ- вого и второго триггеров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения заданий в сетях электронных вычислительных машин | 1982 |

|

SU1075261A1 |

| Преобразователь двоичного кода в унитарный код | 1982 |

|

SU1049897A1 |

| Цифровой интегратор | 1981 |

|

SU1035605A1 |

| Устройство для моделирования дискретного радиоканала | 1980 |

|

SU962999A1 |

| Устройство для управления распределенной вычислительной системой | 1982 |

|

SU1136159A1 |

| Устройство для распределения заданий | 1984 |

|

SU1257647A1 |

| Устройство для контроля электронной вычислительной машины | 1981 |

|

SU1019451A1 |

| Устройство для сопряжения | 1982 |

|

SU1051526A1 |

| Устройство для деления двоичных чисел | 1975 |

|

SU646331A1 |

| Следящий аналого-цифровой преобразователь | 1979 |

|

SU799129A1 |

1. УСТРОЙСТВО ДЛЯ РАСПРЕДЕЛЕНИЯ ЗАДАНИЙ В ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЕ, содержащее бпок управпения, nepaift регистр и элемент ИЛИ, выход которого соединен с первым входом запуска блока управпения, входы элемента ИЛИ соединены с прямыми выходами регистра сдвига, информационный вход которого соединён с зходом кода . числа процессоров устройства, выход пе| вого регистра соединен с первым входом группы блоков элементов И, отличающееся тем, что, с целью расширения области применения, устройство сосержит бпок счетчиков, блок элементов И, два элемента задержки, блок выделения экстремального, числа, элемент И и второй регистр, вход сброса которого соединен с выходом блока элементов И, с суммируюитм входом блока счетчиков, с вторым входом группы блоков элементов и и с входом сброса регистра сдвига, инверсный выход которого соединен с входом элеК1ента И, выход которого сое.динен с BTOfsjM входом запуска блока управления, с управляющим входом первого регистра, с управляющим входом второго регистра, инверсный выход которого соединен с первым входом блока выделения экстремального числа, выход которого соединен с информационшлм входом второго регистра, прямой выход которого соединен с первым входом блока элементов И, с вторым входом блока выделения экстремального числа и с первым информационным входом блока утьравления, первый выход которого соедИ нен с втоуым входом блока элементов И и через первый элемент задержки - с входом управпения регистра сдвига, прямой выход последнего разряда которого соединен с входом его первого разряда, прямой выход регистра сдвига соединен с третьим входом блока элементов И и с вторым информационным вхоцол блока управпения, второй выход которого соединен с третьим входом блока выделення (Л экстремального числа и Через второй элемент задержки - с тактовым входом с. второго регистра,. Четвертый, вход блока выделения экстремального числа соедкнец: с выходом блока счетчиков, вычитающий вход которого соединен с входом кокиа обслуживания устройства. 2. Устройство по п. 1, о.т л и ч а ts9 ю щ е е с я тем, что блок упраштения 12 содержит схему сравнения, три формирователя импульсов, два триггера, генератор импульсов и два элемента И, причем Од первый, второй входы и выход схемы i4 сравнения соединены соответственно с первым, вторым информационными входами блока и с входом первого формирове тепя импульсов, выход которого соединен с нулевыми входами первого и второго триггеров, единичные выходы которых соединены соответственно с первыми входами первого и второго элементов И, выходы которых являются соответственно первым и вторым выходами блока, генератора импульсов соединен с вторыми

1

Изобретение относится к вычиспитепьной технике, в частности к устройствам для распре деления заданий в вычиспитепь-, ной системе.

Известно устройство управления об 5 меном, содержащее регистр готовности процессоров, блок управления, счетчик номера абонента, сборку сигналов требований обмена, элемент ИЛИ окончания распределения. В устройстве аналнэиру- 10 ется готовность абонентов к обмену и организуется обмен выбранного абонекн та в ЭВМ 1. ..

Недостатком известного устройства является низкое стродейсгвве и не- 15 возможность организации обмена со сво бодными абонентами с учетшг свобод«НЫх пиний связи.

Наиболее близким к ядреднагаемому является устройство для распределения 20 заданий процессором, содержащее бпок управления поиском и распределением, элемент ИЛИ, регистр готовности процессоров, регистр сдвига, элементы И И. : 25

Недостаток этогч устройства состоит в невозможности распредепения заданий в вычислитепьной системе по критерик минимальной очереди. i

Цель изобретения - расширение об- Q: пасти применения устройства. .

Шставпенная цепь достигается тем, что в устройство для распределения эаAaKuJt в вычислительной системе, содержа щее блок управления, первый регистр и 35 алемигт ИЛИ, выход соединен с первым ъкоаам запуска блока управления, вжоды элемента ИЛИ соединены с прямБши Ш1 ходами регистра сдвига, нв формааионный вход которого соединен с 40 ВХОДОМ кода числа процессоров устройства, выход iJtepBoro регистра соединён спервым входом группы блоков элементов , введены блок счетчиков, блок элемев тов И, два элемента задержки, блок вы- « депвннй экстремального числа, апемент и второй регистр, вход сброса которого соединен с выходом блока элементов И, с суммирующим входом блока счетчиков, с вторым входом группы блоков элементов И и с входом сброса регистра сдвига, инверснь1й выход которого соедишн с входом элемента И, выход которого соединен с вторым входом запуска блока управления, с управляющим входом первого регистра и с управляющим входом второго регистра, инверсный выход которого соединен с первым входом блока выделения экстремального числа, выход которого соединен с информационным входом второго регистра, прямой выход которого соединен с nepEfciM входом блока элементоВ И, с вторым входом блока выделения экстремального числа и с первым И№|{юрмационным входом блока управления, первый выход которого соединен с вторым входом блока элементов И и через пзерный элемент задержки - с входом yrt1эавления регистра сдвига, прямой выход последнего разряда которого соединен с входом его первого разряда, прямой выход регистра сдвига соединен с третьим вхОдсы бпока элементов И и с вторым информационным входом блока управления, второй выход которого соединен с третьим BKoacfM блока выделения экстремального числа и через второй элемент задержки - с тактовым входом второго регистра, четвертый вход блока выделения экстремального числа соединен с выходом блока счетчиков, вычитающий вход которого соединен с входом конца обслуживания устройства.

Кроме того, бпок управления содержит схему сравнения, три формирователя импульсов, два TpHiftrepa, генератор импуль сов и два элемента И, причем первый, второй входы и выход схемы сравнения соединены соответственно с первым, вторым информаиионн1 1ми вводами блока и с входом первого формирователя импульсов выход которого соединен с нулевыми

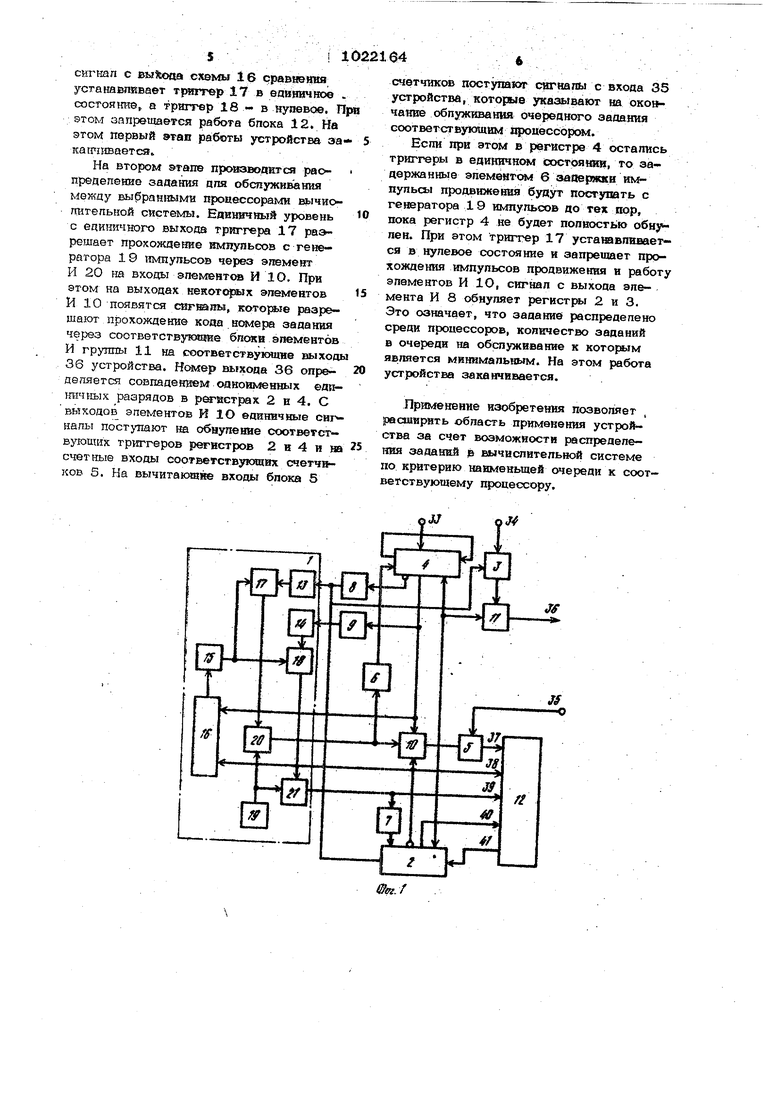

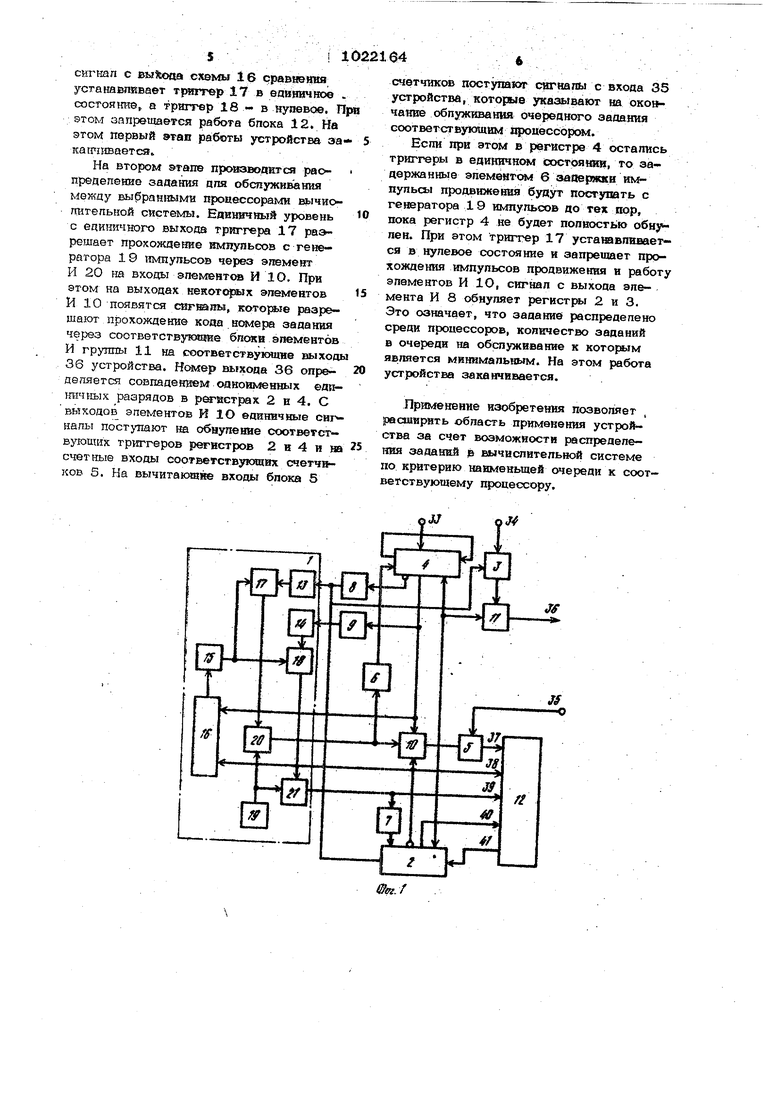

входами первого н второго трштеров, единичные выхощ которых соединены со10ответственно с первыми входами первого и второго эпементов И, выходы которых являются соответственно первый и вторым выходами блока, выход генератора импульсов соединен с вторыми входами первого н второго эпементов И, входы и выходы второго и третьего формирователей цмпупьсов соединены соответственно с первым и вто{и 1м входами запуска блока и с единичными входами первого и второго триггеров. На фиг. 1 представ1пена структурная схема предлагаемого устройства; на фиг. 2 - структурная схема бпока дпя выделения экстремального чиспа. Устройство содержит блок 1 управпения, регистр 2,3 vi 4 сдвига, блок 5 счетчиков, элементы 6 и 7 задержки, первый элемент И 8, элемент ИЛИ 9, блок эпементов И 10, группу блоков эле ментов И 11, блок 12 выделения экстре мального числа. Блок 1 управления вклк чает формирователи 13, 14 и 15 импульсов, схему 16 , триггеры 17 и 18, генератор 19 импульсов, эпементы И 20 и 21, блок 12 для выделения экстремального числа содержит блок 22регистров, блок поразрядных углов 23анализа, блоки элементов И 24, 25 и 26, блоки элементов ИЛИ 27 и 28, блок элементов И-НЕ 30, блок элементов ИЛИ 31, блок элементов И 32, входал 33,34 и 35, выходы 36 устройства входы 37-40 и выход 41 блока 12 для выделения экстремального числа. Устройство работает следующим образом. В исходном состоянии рб|гистры 2,3 И 4 и триггеры 17 и 18 обнулевы. В счетчиках бпока 5 и в регистрах 22 бло ка 12 хранится код количества заданий в очереди на обслуживание к процессору вычислительной систем. Триггеры 29 бпока 12 для выоепеЦия экстремального чиспа йахрдится в единичном состоянии. Устройство распределяет задания на те процессоры вычислительной систеMbJ, количество заданий в очереди на обслуживание к кЬторым является Минимальным., В работе устройства можно выделить два. этапа. На первом этапе производится выбор достаточного для обс/туживания постухт-; ющего задания количества процессоров, количество заданий в очереди на обслуживание к котором является минималь ным.. По входам 33 и 34 устройства соответственно в регистры 2 и 3 записы44ваются код чиспа необходимых дпя авыпоп нения задания процессоров и код номере задания. При этом триггер 18 уста ввпивается в единичное состояние и через элемент И 21 с генератора 19 нмлупь- сов сигнал поступает на вход 39 н разрешает работу блока 12, в котором прои;эводится поразрядимй анализ сравниваемых чисел. Если в первом разряде ч№сел имеется и О я 1, то через элементы И 24 и 25 узлов 28 анализа на блок элементов ИЛИ 31 и 27 поступают единичные сигналы. На выходе срответ ствующего элемента И-НЕ ЗО будет сформирован нулевой сигнал, которым закрывается соответствующий элемент И 32. Через элементы И 26 и ИЛИ 28, относящиеся к тем регистрам 22, в первом разряде которых записан О, сигнал постутюет на входы установки в нулевое состояние соответствующихтриггеров 29, Элементы И 24 и 25 соответствующих узлов 23 анализа закрываются, и единичный сигнал будет только на выходе элемента ИЛИ 31. Ни выходе элемента И-НЕ ЗО формируется единичный сигнал, по которюму открывается элемент И 32. Далее производится анализ следующего разряда оставшихся сравнительных чисел. Если же в первом разряде сравниваемых чисел содержатся только или топъко единицы, то на ы 1ходе эг1ементов И-НЕ 30 будет единичный сигнал, кото- . 1Я.1й открывает элемент И 32. Спедовательно, в этом случае пройсзвоцится анализ второго или последующих рва- . рядов. После того, как вое р азрйщ орав . ниваемых чисел будут проашгшзированы, на выходе элемента И 32 с рмируется единичный уровень. При этом на аяхспах 41 хранится код номеров регистров 22 содержащих минимальное число. Код номеров регистров, содержащих минимальное число и соответствующих вечерам процессоров, количество заданий в очереди на обспуживашю к которилм является минимальным заносится в регистр 2. Если код числа {юобходимых процессоров превышает код числа выбранных, то из числа невыбраиных для распределения процессоров снова выбирается код номеров процессоров, количество заданий в очереди на обслуживание к KOTOffciM является минимальным. При этом число выбранных номеров процеосоров увеличивается. Если код числа необходимых процессо ров не превышает числа выбранных, то сигнал с BbJlaooa схемы 16 рравшиия устанавливает триггер 17 в едвнвчнов . состоят ©, а триггеров - в нупевсю. Пр этом запрещается работа бпока 12. На этом первый этап работы устройстве эакагппшаетсз.. На втором этапе производится распредепение задания апя обслуживания между выбранными процессорами вь1чиопнтепьной системы. Единичный уровень с единичного выхода триггера 17 разрешает прохождение импульсов с генератора 19 tiMnynbcoB через эгеемент И 20 па входы зпементов И 1О, При этом на выходах некоторых элементов И 10 появятся снгвэдал, которые разрешают п|эо хождение кода.номеf задания через соответствукяше бпокв эпементов И группы 11 на соответствующие выходы 36 устройства. Нсямер вьгхода 36 опредепяетс5з совпадением одноименных едиШ1Ч1шх разрядов в р истрах 2 н 4. С выходов эпементов И 1О единичные сигнапы постутшют та обнуление соответствующих триггеров регистров 2 н 4 и да счет ные входы соответствующих счетчиКОБ S. На Бычитающда входы бпока 5 счетчиков поступают сигналы с входа 35 устройства, которые укаШ1вают на окончание обпуживания очередного задания соответствующим процессором. Еспи при этом в регистре 4 остапись триггеры в единичном состояшвд, то задержанные эпементом 6 задаржки импульсы продвижения будут пскягупать с генератора 19 импульсов до тех пор, пока регистр 4 не будет полностью обну пен. При этом триггер 17 устадавпнвается в нулевое состояние и запрещает прохождения импульсов продвижения и работу элементов И 1О, сигнал с выхода эпемента И 8 обнуляет perHCTfa-i 2 и 3. Это означает, что задание распределено среди процессоров, количество заданий в очереди на обслуживание к которлм яв/юется минимальным. На этом работа устройства заканчивается. Применение изобретения позволяет , расширить область применения устройства за счет возможности распределегдая заданий э вычислительной системе по критерию наименьшей очереди к соответствующему процессору.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Волномер | 1922 |

|

SU474A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для распределения заданий процессорам | 1977 |

|

SU629538A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-06-07—Публикация

1982-03-01—Подача