вого и п-го каналов и четвертых элементов ИЛИ всех остальных каналов и первыми входами шестых элементов И соответствующих каналов, вторые входы которых соединены с выходами первых элементов ИЛИ соответствующих каналов, выход шестого элемента И -1-го канала (,,..,, п-1 соединен с первым входом пятого элемента ИЛИ i-го канала и с -м входом первого элемента ИЛИ-НЕ, выходы шестых элементов И первого и п -го каналов соединены с первыми входами четвертых элементов ИЛИ соответственно первого и п -го каналов и с соответствующими входами .первого элемента ИЛИ-НЕ, выход которого соединен с вторыми входами чет вертых элементов ИЛИ первого и «п -го каналов и пятых элементов ИЛИ всех остальных каналов, выходы четвертого элемента ИЛИ первого и п -го каналов соединены с вторыми входами элементов И-НЕ соответственно с первого и п-го каналов, выход пятого элемента ИЛИ -го канала соединен с вторым входом элемента И-НЕ i-ro канала, единичный выход триггера пер вого канала соединен с вторым входом пятого элемента И и первыми входами с первого по четвертый элементов И первого канала, единичный выход триггера i-ro ( 2,... п ) канала соединен с первыми входами с первого по четвертый элементов И i-го канала.выход элемента ИЛИ-НЕ i-ro канала соединен с вторым входом пятого элемента И i-ro канала, выходы пятых.элементов И всех каналов являются выходами устройства, выходы вторых элементов ИЛИ первого и п-г каналов соединены с первыми входами 118 третьих элементов ИЛИ соответственно первого и п -го каналов и с соответ-г ствующими входами второго элемента ИЛИ-НЕ, выход в.торого элемента ИЛИ i -го канала (,..., h-1) соединен с первьш входом четвертого элемента ИЛИ i-го канала и с -м входом второго элемента ИЛИ-НЕ, выход которого соединен с вторыми входами третьих элементов ИЛИ первого и п -го каналов и четвертых элементов ИЛИ i-X каналов, вторые входы первого и второго элементов И каждого канала соединены с соответствующими выходами (т- 1) раэряда ( iTi - число запросов) сдвигающего регистра своего канала, вторые входы третьего и четвертого элементов И кажд.ого канала соединены с соответствующими выходами m -го разряда сдвигающего регистра своего канала, информационный вход которого соединен.с соответствующим входом кода приоритета устройства, выход элемента И соединен со счетным входом счетчика импульсов и с входами сдвига сдвигаюющих регистров всех каналов, выход счетчика импульсов соединен с первым входом схемы сравнения, второй вход которой соединен с выходом регистра, информационный вход которого соединен с входом кода коэффициента пересчета устройства, вход режима которого соединен с входом второго триггера, единичный и нулевой входы которого соединены с третьими входами соответственно первого и третьего элементов И и второго и четвертого элементов И всех каналов .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования сетевых графов | 1981 |

|

SU1013965A1 |

| Многоканальное операционное устройство | 1982 |

|

SU1124292A1 |

| Арифметико-логическое устройство | 1983 |

|

SU1176321A1 |

| Многоканальное устройство для подключения абонентов к общей магистрали | 1985 |

|

SU1401459A1 |

| Устройство для управления распределенной вычислительной системой | 1981 |

|

SU972509A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Устройство для распределения заданий в сетях электронных вычислительных машин | 1982 |

|

SU1075261A1 |

| Мультимикропрограммное устройство управления | 1985 |

|

SU1256026A1 |

| Многоканальное устройство для контроля параметров | 1990 |

|

SU1725191A1 |

| Устройство для определения экстремального числа | 1984 |

|

SU1226441A1 |

УСТРОЙСТВО ,ТЛЯ РАСПРЕДЕЛЕНИЯ ЗАДАНИЙ ПРОЦЕССОРАМ, содержащее Л каналов ( р - число решаемых задач), каждый из которых, кроме первого и п-го, содержит четыре элемента И, три элемента ИЛИ, элемент ИЛИ-НЕ и триггер, первый канал Содержит четьфе элемента И, два элемента ИЛИ и триггер, а п -и канал содержит четыре элемента И, два элемента ИЛИ, элемент ИЛИ-НЕ и триггер, причем в каждом канале выходы первого и второго элементов И соединены с соответствующими входами первого элемента ИЛИ, выходы третьего и четвертого элементов И соединены с соответствующими входами второго элемента ИЛИ, нулевой выход триггера канала (i 2 П-1) соединен с первым входом третьего элемента ИЛИ i-го канала, второй вход которого, кроме второго канала, соединен с выходом третьего элемента ИЛИ ( i - 1)-го канала и первым входом элемента ИДИ-НЕ i -го канала, единичный выход триггера i-ro канала соединен с вторым входом элемента ИЛИ-НЕ i -го канала, нулевой выход триггера первого канала соединен с вторым входом третьего элемента ИЛИ и первым входом элемента ИЛИ-НЕ второго канала, единичный выход триггера п-го канала соединен с первым входом элемента ИЛИ-НЕ п-го канала, второй вход которого соединен с выходом третьего элемента ИЛИ (п-1)-го канала, отличающееся тем, что, с целью расширения области применения, оно содержит генератор тактовых импульсов, элемент задержки, элемент И, счетчик импульсов, схему сравнения, i регистр, два триггера, два элемента ИЛИ-НЕ, а в каждом i-м канале(Л сдвигающий регистр, пятый и шестой элементы И, четвертый и пятый элементы ИЛИ и элемент И-НЕ, а первый и п-й каналы содержат сдвигающий регистр, пятый и шестой элементы И, третий и 1етвертый элементы ИЛИ и элемент И-НЕ, причем выход генера00 тора тактовых импульсов соединен со со с первым входом элемента И, второй вход которого соединен с единичным О) выходом первого триггера, единич ный вход которого соединен с входом пуска устройства, нулевой ° вход первого триггера соединен с выходом схемы сравнения, с входом сброса счетчика импульсов, с первыми входами пятых элементов И всех каналов и через элемент задержки с нулевыми входами триггеров всех каналов, единичные входы которых соединены с выходами элементов И-НЕ соответствующих каналов, пер- . вые входы которых соединены с выходами третьих элементов ИЛИ пер

Изобретение относится к вычислительной технике, и может быть использовано при организации вычислительного процесса по обработке пакета задач в многопроцессорной (многомашинной) вычислительной системе.

Цель изобретения - расширение области применения.

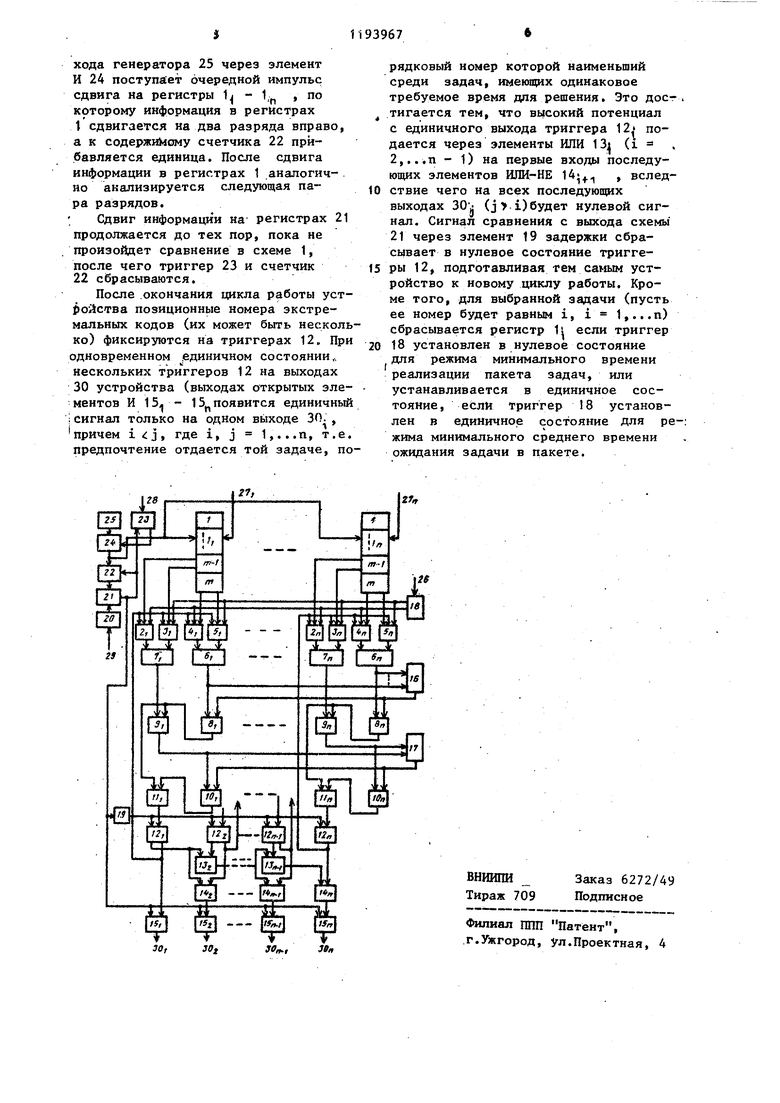

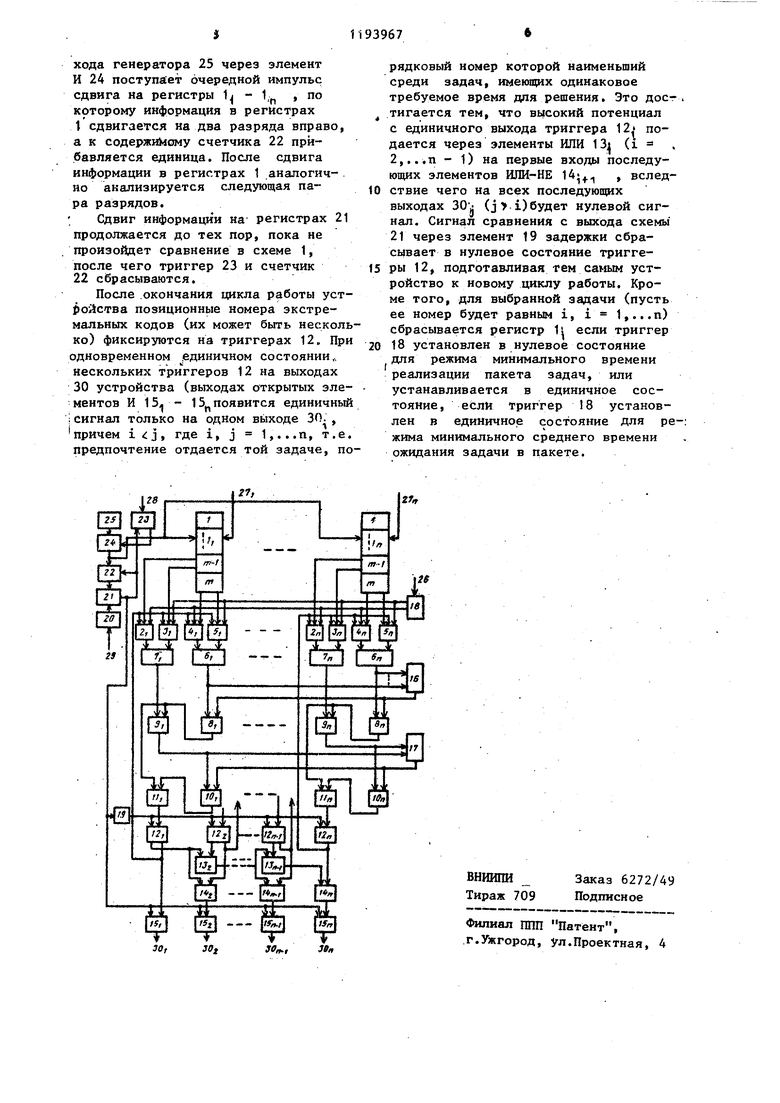

На чертеже представлена структурная схема устройства.

Устройство содержит: га - разрядные сдвигающие (со сдвигом на два разряда в сторону старших разрядов) регистры Ц - If, (п - количество задач в пакете) по числу задач в пакете первые 2 - 2 вторые 3 - Зп , третьи 4 - 4г, и четвертые 5 - 5, элементы И, вторые 6 - 6|, и первые 7 - 7 элементы ИЖ, элементы ИЖ 3 - 8, шестые элементы И 9 - 9 , элементы ИЛИ 10 - Юп , элементы И-НЕ 11 - 11 , триггеры 12 - 12п , элементы ИЛИ 132 - , элемент ты ИЛИ-НЕ 14 - 14| , пятые элементы И 15 - 15. , второй элемент ИЖ-НЕ 16, первый элемент ИПИ-НЕ 17 второй триггер 18, элемент 19 эадержки, регистр 20, схему 21 срав нения, счетчик 22 импульсов, пер-, вый триггер 23, элемент И 24, гене ратор 25 тактовых импульсов, вход 26 режима работы, информационные входы 27;, - 27 , пусковой вход 28, установочный вход 29, выходы 30 ЗОр, устройства, В исходном состоянии на регистра 1 находятся коды, соответствуюг е весам задач и заносимые по вхо дам 27j . Все триггеры 12 устанавливают в нулевое состояние (уста новочные входы не показаны). . На триггер 18 по входу 26 заноси ся код режима работы устройства, а на регистр 20 по входу 29 - код коэффициента пересчета счетчика 22, р ного числу m/2-l, (m - разрядность регистров 1). Единичному (нулевому) состоянию триггера 18 соответствует режим распределения задач по процессорам вычислительной системы по критерию минимума (максимума) веса задачи соответственно. Работа устройства начинается посл сброса триггеров Ч 2 установки тригге ра 23 по входу 26, в результате чего открывается элемент И 24. К этому времени коды с выходов двух триггеров старших разрядов m -го и (т - 1 го регистров 1 поступают через одноименные элементы И 2 или И 3, на третьи, входы которых подается высокий потенциал с обратных выходов одноименных триггеров 12, и элемент ИЖ 7 для (га - 1)-го разряда, и элемент И 4 или И 5 (в зависимости от состояния триггера 18) для га-го разряда для последующего анализа. В начале анализируются старшие разряды п кодов. Дпя этого сигнал с выхода элемента ИЛИ 6 (i 1,..п поступает на i-й вход элемента ИЛИНЕ 16 и на первый вход элемента ИЖ В., на второй вход которого поступает сигнал с выхода элемента ИЛИНЕ 16. Если во всех старших т-х разрядах регистров 1 хранится нуль, то на выходе элемента ИЛИ-НЕ 16 будет сигнал логической единицы, во всех других случаях на выходе элемента ИЖ-НЕ 16 сигнал логического нуля. Сигнал с выхода элемента ИЛИ 8 поступает на первый вход элемента И-НЕ 11. и первый вход элемента И 9 , второй вход которого подсоединен к выходу элемента ИЛИ /. , на котором находится сигнал состояния (m-l)-ro триггера регистра 1j. Сигнал с выхода элемента И 9 поступает на i-й вход элемента ИЖ-НЕ 17 и на первый вход элемента ИЛИ 10 , второй вход которого подсоединен к выходу элемента ИЛИ-НЕ 17, а выход - к второму входу элемента И-НЕ 11.. Таким образом, если хотя бы на одном, например, i-м регистре 1(i 1,.., п) в (m-l)-M разряде содержится код единицы,то на выходе элемента И 9 будет сигнал логической единицы, который поступает на i-й вход элемента ИЖ-НЕ 17 (при наличии хотя бы одного единичного сигнала на триггерах т-го и (т-1)го разрядов регистра Ij , j 1,... п). С выхода элемента РШИ-НЕ 17 сигнал логического нуля поступает на один из входов элементов ИЖ 10, на второй вход каждого из которых поступает сигнал логической единицы с выхода элемента И 9 . Поэтому, если на выходе элемента ИЛИ 6 высокий потенциал, то на выходе элемента И-НЕ 11. нулевой потенциал. В случае, если значение т-го разряда регистра 1, равно нулю, то на выходе элемента «Ж 6. будет сигнал логического нуля, на выходе элементов ИЛИ 8. , ИЛИ 10 - также сигнал логического нуля, а на выходе элемента И-НЕ 11. появится сигнал логической единицы, который перебросит триггер 12- в единичное состояние, после чего прекращается подача высокого потенциала с обратного выхода триггера 12- на третьи входы элементов И 2 и И З; (i 1,...п). Аналогична работа устройства и при других комбинациях старншх двух разрядов регистров 1. Для анализа следующей пары разрядов сравниваемых кодов с вы

| Многоканальное устройство приоритетных прерываний с автоматической выработкой кода приоритетной заявки | 1974 |

|

SU548859A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для распределения заданий процессорам | 1980 |

|

SU964643A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-10-07—Публикация

1984-05-25—Подача