Изобретение относится к радиотехнике и может испольэоваться для формирования пинейно-частотно-моду- пированнмх (ЛЧМ) сиг-налов в различных системах коротковолновой связи, сейсмологии, радиолокации.,

Цель изобретения - рас11 ирение рабочего диапазона частот.

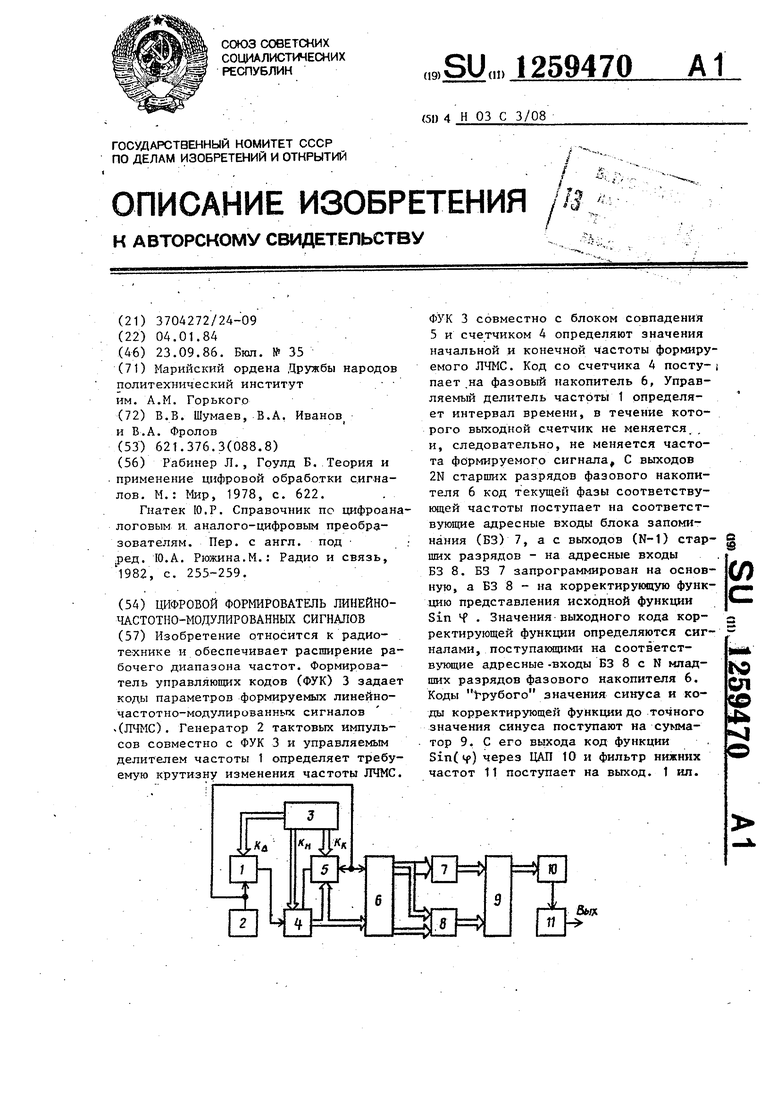

На че.ртеже представлена структурная электрическая схема предложенного цифрового формирователя ЛЧМ сигналов.

Цифровой формирователь ЛЧМ сигналов содержит управляемый делитель 1 частоты, генератор 2 тактовых им- пулхзсов, формирователь 3 управляющих кодов, счетчик 4, блок 5 совпадения, фазовый накопитель 6, первый блок 7 запоминания, второй блок 8 запоминания, сумматор 9, цифроана- логовый преобразователь (ЦАП) 10, фильтр 1t нижних частот (ФНЧ).

Цифровой формирователь ЛЧМ сигналов работает следующим образом.

Формирователь 3 управляющих кодов задает коды параметров формируемых ЛЧМ сих налов: код начальной частоты (К„) , код конечной частоты (К|) и код временного интервала постоянного значения приращения фазы заданной частоты (Кд ). Генератор 2 тактовых импульсов совместно с формирователем 3 и управляемым делителем 1 частоты определяет требуемую крутизну изменения частоты ЛЧМ сигнала. Формирователь 3 совместно с блоком 5 совпадения и счетчиком 4 определяет зна- чения начальной и конечной частоты формируемого ЛЧМ сигнала. Фазовый накопитель 6 представляет собой многоразрядный накапливающий сумматор.

Синтезирование ЛЧМ сигнала производится изменением в определенные моменты времени вькодной частоты с заданным шагом. В исходном состоянии в управляемый делитель 1,частоты записан код (Кд), определяющий время интервала формирования одной частоты

Т

им т.

- к,

т. г.

где Т . - период следования тактовых импульсов генератора 2.

В счетчик 4 записан код (К,) на- чальной частоты формируемого сигнала. На один из входов блока 5 совпадения поступает код конечной частоты

(К) формируемого сигнала. Заданные значения кодов К, К и К Носту- пают с формирователя 3 управляющих кодов формируемого ЛЧМ сигнала, который может состоять, например, из трех многоразрядных кодовых переключателей. Выходной многоразрядный код с выхода счетчика 4 поступает на второй информационный вход блока 5 совпадения и на вход фазового накопителя 6.

Импульсы с генератора 2 тактовьпс импульсов поступают на управляющие входы управляемого делителя 1 частоты, блока 5 совпадения и на вход записи фазового накопителя 6. В фазовом накопителе 6 с приходом каждого,тактового импульса происходит суммирование входного кода заданной частоты, поступающего со счетчика 4, с существующим в данный момент выходным кодом. Эта операция представляет собой не что иное, как изменение фазы формируемого сигнала на величину, определяемую выходным кодом счетчика 4, код которого в начальный момент-времени равен входному коду начальной часто ты (Кц), поступающему с вькода формирователя 4.

Управляемь й делитель 1 частоты пропускает на свой выход только те входные импульсы, номера которых кратны записанному коду (Kj.) ,

поступающему с одного из выходов формирователя 3, и определяет интервал времени, а течение котэрого выходной код счетчика 4 не меняется, а следовательно, не меняется частота формируемого сигнала. Каждый выходной импуЛьс с управляемого делителя 1 частоты поступает на счетный . вход счетчика 4, изменяя его выходной код на единицу, что соответствуёт изменению частоты выходного сигнала на величину, которая определяется частотой генератора 2 тактовых импульсов и разрядностью фазового Накопителя б

50

uF F.

т-г

где п - разрядность фазового накопителя 6;

-частота следования тактовьпс импульсов;

-шаг изменения частоты выходного сигнала.

3

Крутизна изменения выходного ЛЧМ сигнала задается и определяется также частотой генератора 2 и кодом К

По достижении значения выходного кода счетчика 4 кода конечной частоты (К ) блок 5 срвпадения, представляющий собой многовходовый элемент и , пропустит первьй же импульс с выхода генератора 2 тактовых импульсов на управляющий вход счетчика 4, устанавливая на его выходе код начальной частоты, возвращая всю систему в исходное состояние.

С вьпсодов 2N старших разрядов фазового накопителя 6 к од текущей фазы соответствующей частоты поступает соответственно на N адресных входов первого блока 7 запоминания. Код с выходов (N-1) старших разрядов фазового накопителя 6 поступает соответственно на (N-1) старших адресных входов второго блока 8 запоминания..

Первый блок 7 запоминания запрограммирован на основную SinCH j ) , а второй блок 8 запоминания - на корректирующую fp ( + JaW) функцию представления исходной функции синуса SinCtf), где SinCM) - значения функции на L -ом поддиапазоне в i-ой точке аргумента (фазы); i () значение функции t-го поддиапазона в точке (i + j) аргумента.

Обе функции Sin(4j) иЕ-СЧ +йдч) задаются в виде таблиц, запрограммированных в блоках 7 и 8 запоминания.

Одна из таблиц задает значения Sin(4,- ) в некоторых тЬчках ( ) с определенным интервалом, другая таб лица - точные значения f. (if; +344) по каждому из этих интервалов, а весь интервал изменения ti-разрядно- го аргумента (фазы) включает в себя 2 узловых точек, из числа которых вычисляется 2 поддиапазонов.

Значение исходной синусоидальной функции Sin( v ) в поддиапазоне С в точке ( 4j JAtp) определяется как сумма значений синусоидальной функции Sin( ) в узловой точке (Ч{ ) и .значения корректирующей функции (4,. tJAVf) в точке (.f) соответствующей текущей фазы.

Для каждого поддиапазона используется только одна корректирующая функция. Для определения значения синусоидальной функ1щи между узловы259470-4

ми точками необходимо, чтобы коррек тирующая функция определялась в , точках аргумента.

Тогда суммарный объем блоков 7 и 5 8 запоминания для хранения значений синусоидальной функции в узловых точках SinС ) и корректирующих функций f(Ч. Ju4) определяется выражением10

2 -h

sin

7 т / id - н

t

ts

20

5

где -2 - количество ячеек блоков

запоминания, в которых хранятся значения синуса g,- в узловых точках; 2 - количество ячеек, в которых хранятся значения одной корректирующей функции; 2 - количество корректирующих функций во всем интервале изменения аргумента (фазы);

S - количество используемых вы ходных старших разрядов фазового накопителя. Значения выходного кода корректирующей функции определяется сигнала- 0 ми, поступаюш 1М11 на N младших адрес- ньк входов второго блока 8 запоминания с соответствующих N выходов младших разрядов фазового накопителя 6. Выходные коды грубого значения 5 синуса и коды значений корректирующей функдаи до точного значения синуса поступают соответственно с выходов первого и второго блоков 7 и 8 запоминания на входы cy№faTopa 9. 0 В результате суммирования кодов основной и корректирующей функции на выходе сумматора 9 получается код синусоидальной функции Sin(M ) SinXM-j) +( (ч -ju4 ), из кото- 5 рого в ЦАП 10 формируется соответствующее аналоговое напряжение значений синусоиды.

ФНЧ 11 формирует из сигнала ступенчатого напряжения гармонический 0 синусоидальный сигнал.

Формула изобретения

Цифровой формирователь линейно- 5 частотно-модулированных сигналов, содержащий формирователь управляющих кодов, выход кода начальной частоты которого соединен с информационным

входом счетчика, фазовый naKonvtrenb, вход записи которого соединен с выходом генератора тактовых импульсов, информациопные входы - с разрядными выходами счетчика, а выходы 2N старших разрядов - с соответствующими адресными входами первого блока запоминания, и последовательно соединенные сумматор, цифроаналоговый преобразователь и фильтр нижних частот, при этом первый вход сумматора соединен с выходом первого блока запоминания, отличающийся тем, чт.о, с целью расширения рабочего диапазона частот, в него введены второй блок запоминания, каждый из старших адресных входов которого соединен с соответствующим из (N-1) выходов старших-разрядов фазового накопителя, а каждый из г ладших адресных

Редактор Л. Гратшшо

Составитель Г. Захарченко

Техред А.Кравчук . Корректор Л- Зимокосов

Заказ 5138/57Тираж 816 . Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 11S035, Москва, Ж-35, Раушская наб., д. Д/5

ТронзвоДственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

входов - с соотве тствующим из N выходов младших разрядов фазового накопителя, выход - с вторым входом сумматора, блок совпадения, первый и второй информационные входы которого соединены соответственно с выходом кода конечной частоты формирователя управляюгцих кодов и выходом счетчика, управляющий вход - с вых-одом генератора тактовых импульсов, а выход - с входом записи счетчика, а также управляемый делитель частоты, сигнальный вход которого соединен с выходом кода временного интервала постоянного значения приращения фазы заданной частоты, формиров ателя управляющих кодов, управляющий вход - с выходом генератора тактовых импульсов, а выход соединен со счетным входом счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1385239A1 |

| СИНТЕЗАТОР ЧАСТОТ | 1991 |

|

RU2007843C1 |

| Корреляционный измеритель фазовых соотношений узкополосных случайных процессов | 1990 |

|

SU1714616A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ СЛОЖНЫХ СИГНАЛОВ | 1990 |

|

SU1841066A2 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ СЛОЖНЫХ СИГНАЛОВ | 1988 |

|

SU1841042A1 |

| ФОРМИРОВАТЕЛЬ ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 1992 |

|

RU2033685C1 |

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1385238A2 |

| Генератор синусоидальных сигналов | 1990 |

|

SU1734189A1 |

| Генератор синусоидальных сигналов качающейся частоты | 1985 |

|

SU1279077A1 |

| СПОСОБ УПРАВЛЕНИЯ ЭЛЕКТРОПРИВОДОМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2020724C1 |

Изобретение относится к радиотехнике и обеспечивает расширение рабочего диапазона частот. Формирователь управляющих кодов (ФУК) 3 задает коды параметров формируемых линейно- частотно-модулированньтх сигналов (ЛЧМС). Генератор 2 тактовых импульсов совместно с ФУК 3 и управляемым делителем частоты 1 определяет требуемую крутизну изменения частоты ЯЧМС. ФУК 3 совместно с блоком совпадения 5 и счетчиком 4 определяют значения начальной и конечной частоты формируемого ЛЧМС. Код со счетчика 4 посту-) пает .на фазовьй накопитель 6, Управ- ляемъй делитель частоты 1 определяет интервал времени, в течение которого выходной счетчик не меняется., и, следовательно, не меняется частота формируемого сигнала, С выходов 2N старших разрядов фазового накопителя 6 код текущей фазы соответствующей частоты поступает на соответствующие адресные входы блока запоминания (БЗ) 7, а с выходов (N-1) старших разрядов - на адресные входы БЗ 8. БЗ 7 запрограммирован на основную, а ВЗ 8 - на корректирующую функцию представления исходной функции Sin Ч . Значения выходного кода корректирующей функции определяются сигналами, поступакицимн на соответствующие адресные -входы БЗ В с N младших разрядов фазового накопителя 6. Коды Грубого значения синуса и коды корректирующей функции до точного значения синуса поступают на суьма- тор 9. С его выхода код функции Sin( ч) через ЦАП 10 и фильтр нижних частот 11 поступает на выход. 1 ил. I (Л с СП 4

| Рабинер Л., Гоулд Б | |||

| Теория и применение цифровой обработки сигналов | |||

| М.: Мир, 1978, с | |||

| УГЛОМЕРНЫЙ ПРИБОР | 1922 |

|

SU622A1 |

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

| Справочник по цифроана- логовым и | |||

| аналого-цифровым преобразователям | |||

| Пер | |||

| с англ, под ,ред | |||

| Ю.А | |||

| Рюжина.М.: Радио и связь, 1982, с | |||

| Гудок | 1921 |

|

SU255A1 |

Авторы

Даты

1986-09-23—Публикация

1984-01-04—Подача