-I

СО

оо

СП

ъо

со со

Изобретение относится к радиоэлектронике и может быть использовано для формирования сигналов с заданным законом изменения фазы, в.частности, в калибраторах фазы, синтезаторах час- частот, синтезаторах с полиномиальны законом изменения частоты.

Цель изобретения - повышение точности формирования заданного закона изменения фазы выходного сигнала.

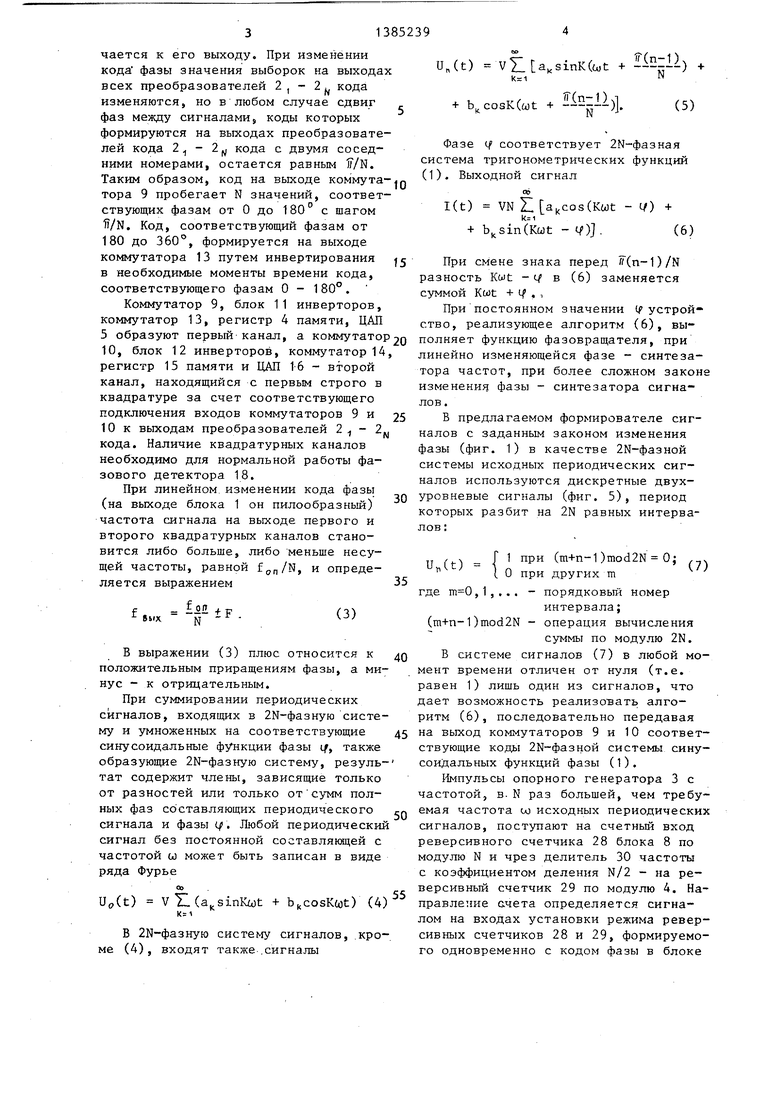

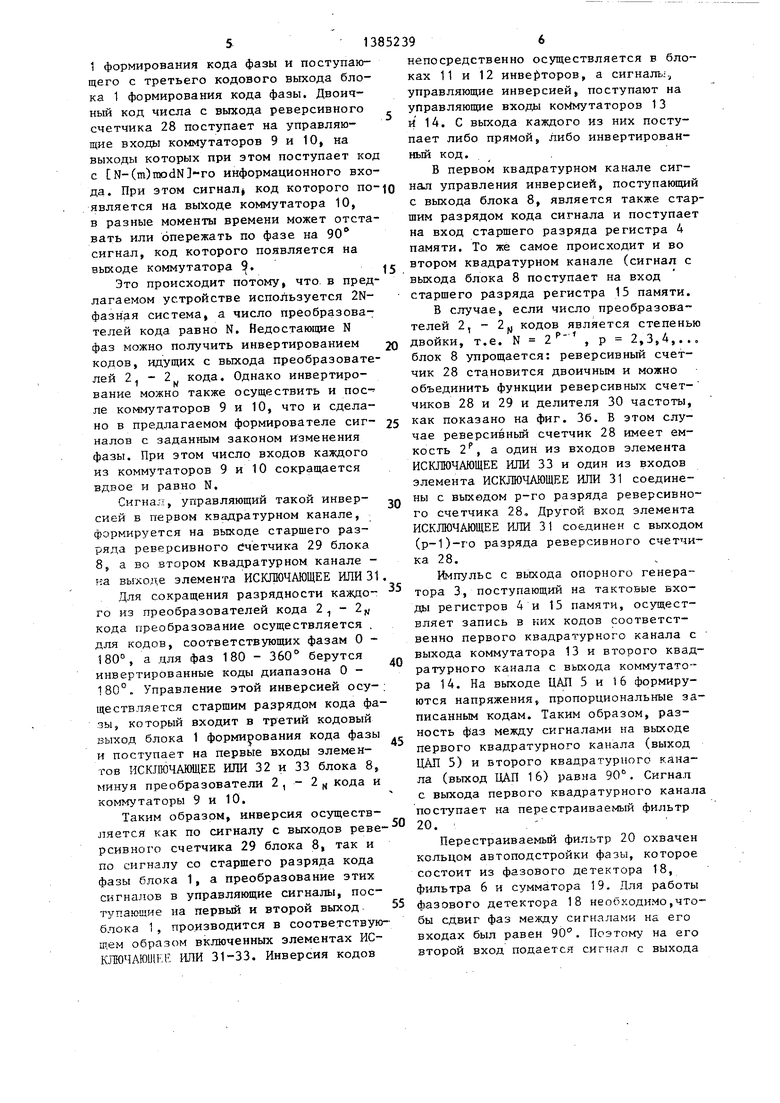

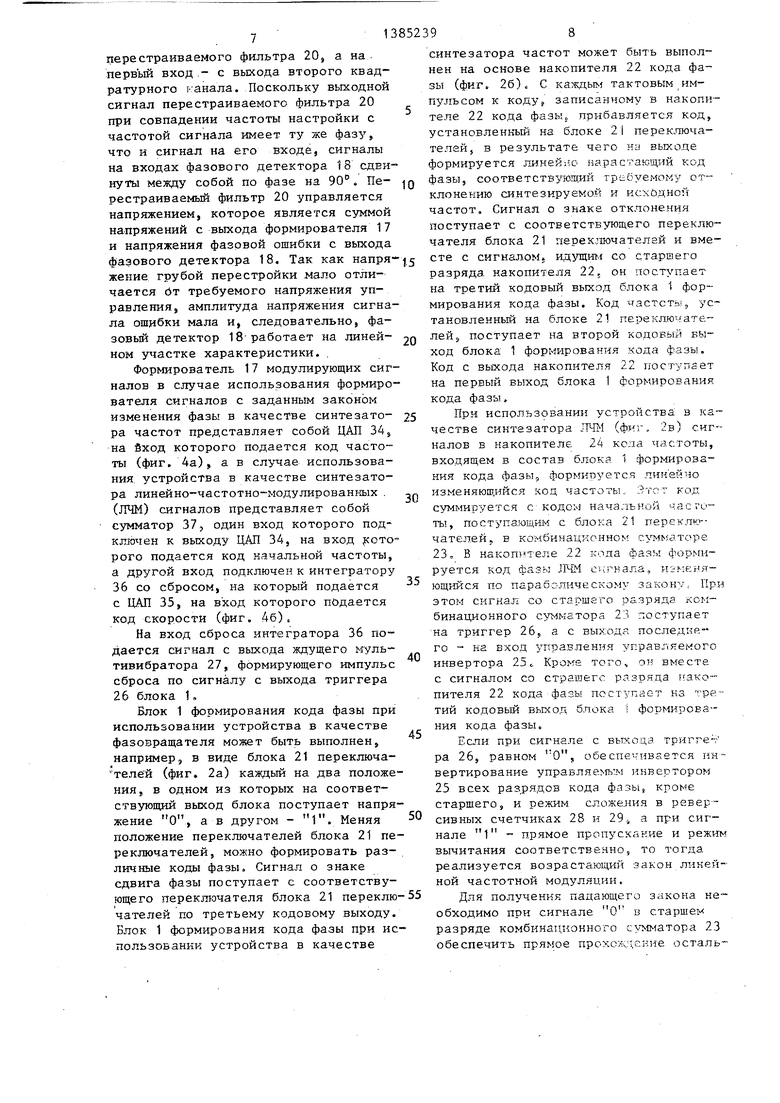

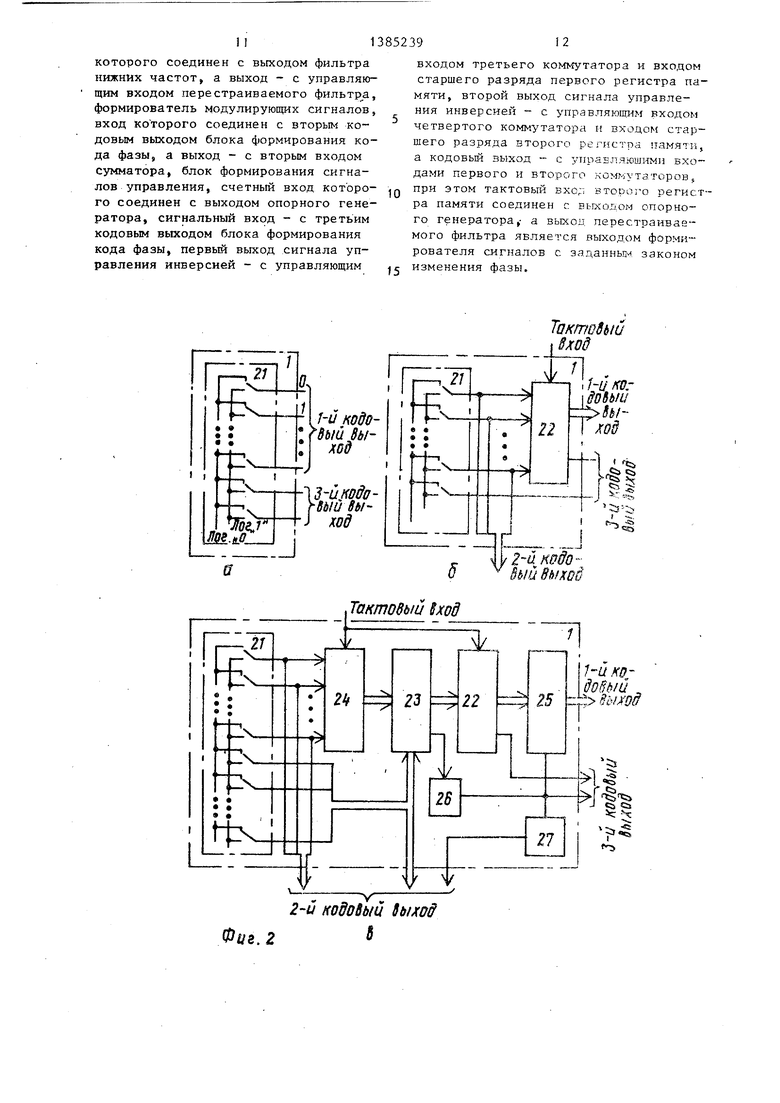

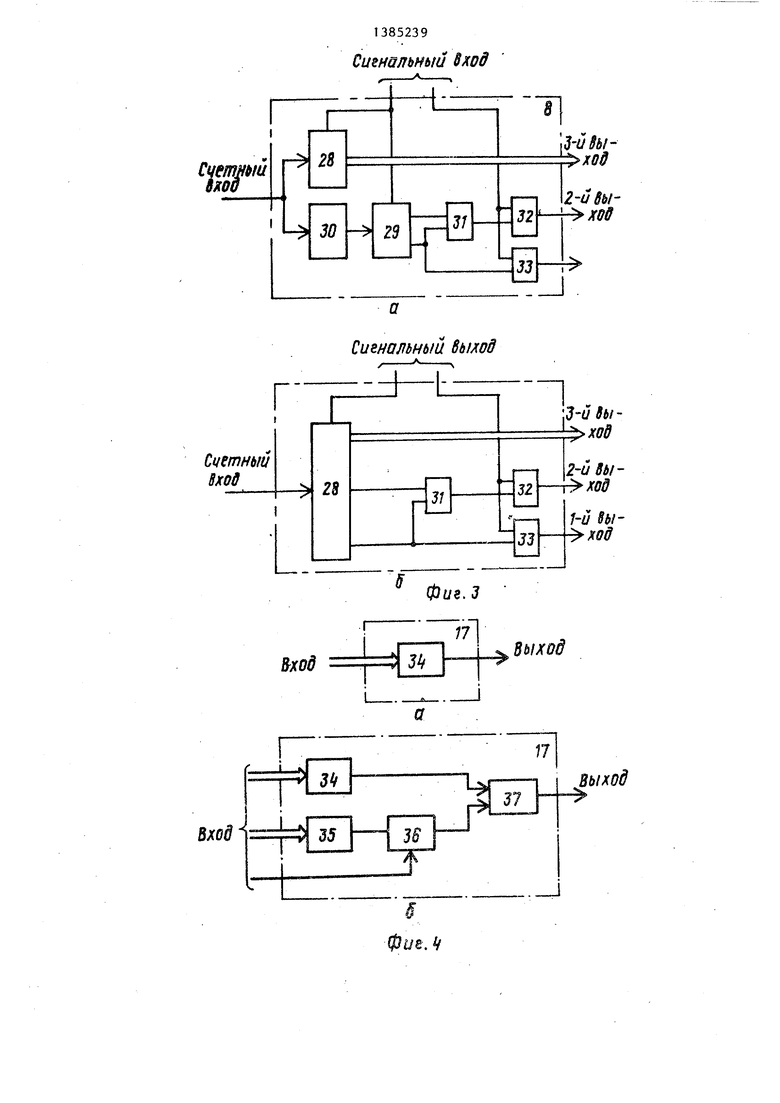

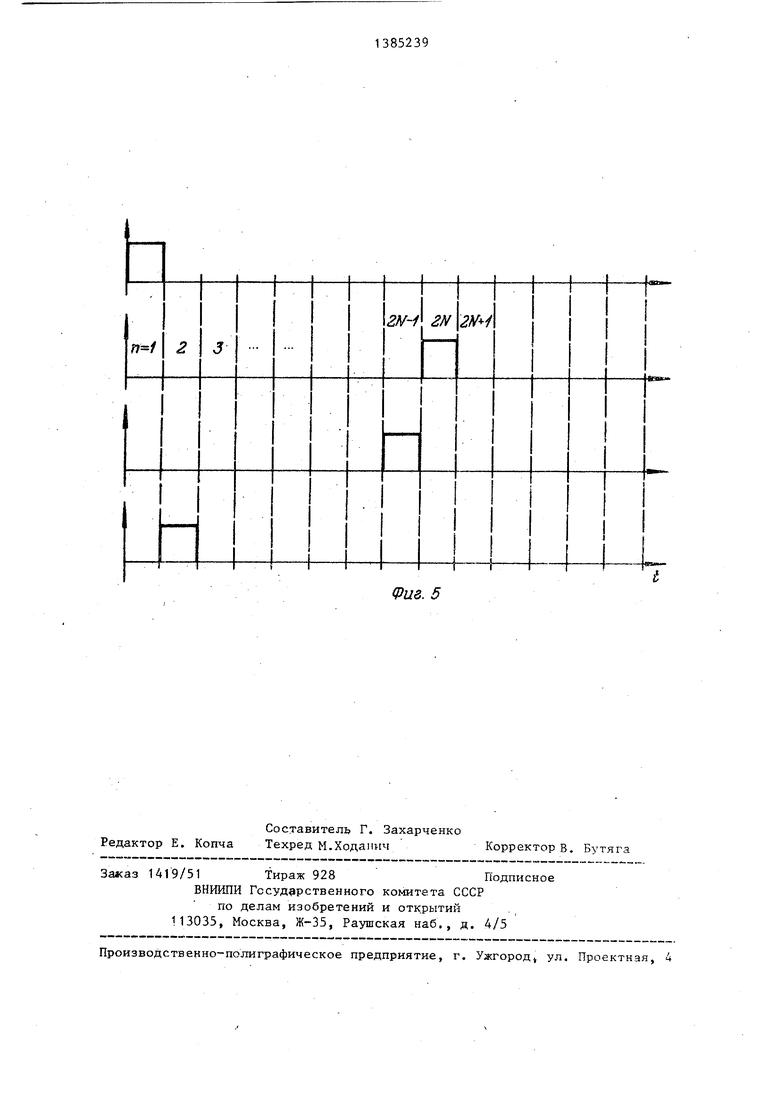

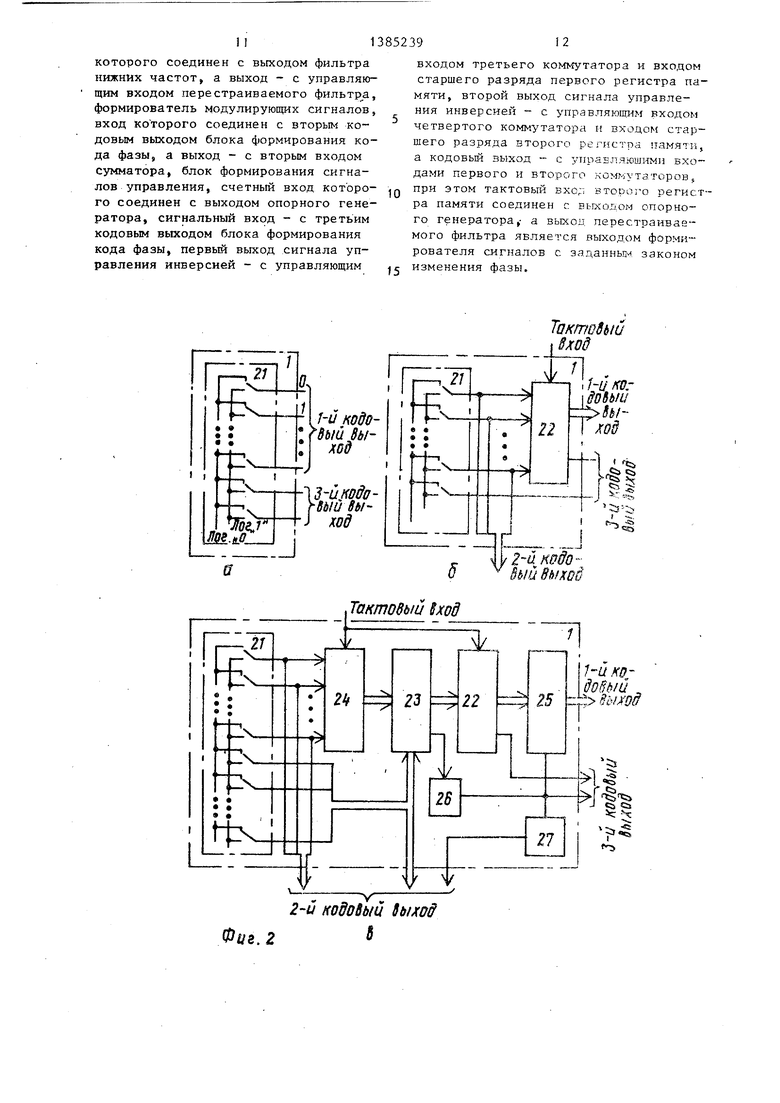

На фиг. 1 изображена структурная электрическая схема предлагаемого формирователя сигналов с заданным законом изменения фазы; на фиг. 2 - примеры реализации блока формирования кода фазы; на фиг. .3 - примеры реализации блока формирования сигналов управления; на фиг. 4 - примеры реализации формиройателя модулирующих сигналов; на 4мг. 5 - диаграммы исходных двухуровневых сигналов.

Формирователь сигналов с заданным законом изменения фазы содержит блок 1 формирования кода фазы, N преобра- зователей кода 2 - 2, опорный генератор 3, первый регистр 4 памяти, первый цифроаналоговый преобразователь (ЦАП) 5, фильтр 6 нижних частот. (ФНЧ), делитель 7 частоты, блок 8 формирования сигналов управления, перЕьй 9 и второй 10 коммутаторы, первый 11 и второй 12 блоки инверторов, третий 13 и четвертьй 14 коммутаторы, второй, регистр 15 памяти, второй U/iTi 16, формирователь 17 модулирующих сигналов, фазовый детектор 18j сумматор 19J перестраиваемый фильтр 20.,

Блок 1 формирования кода фазы

(фиг. 2а) содержит блок 21 переключателей. Блок 1 формирования кода фазы (фиг. 26) содержит блок 21 переключателей и накопитель 22 кода фазы. Блок 1 формирования кода фазы (фиг. 2в) содержит блок 21 переключателей, накопитель 22 кода фазы, комбинационный сумматор 23, накопитель 24 кода частоты, управляемый инвертор 25, триггер 26 и ждущий мультивибратор 27.

Блок 8 формирования сигналов управления (фиг. За) содержит первый 28 и второй 29 реверсивные счетчики, делитель 30 частоты, первый 31, второй 32 и третий 33 элементы ИСКЛЮЧАЮЩЕЕ Ш1И„ Блок 8 формирования сигналов управления (фиг, 36) содержит первьй реверсивный счетчик 28, первый 31,

второй 32 и третий 33 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ.

Формирователь 17 модулирующих сигналов (фиг. 4а) содержит цифроаналоговый преобразователь (ЦАП) 34. Формирователь 17 модулирующих сигналов (фиг. 46) содержит ЦАП 34, дополнительный ЦАП 35, интегратор 36 и сумматор 37.

Формирователь сигналов с заданным законом изменения фазы работает следующим образом.

В каждом q-M такте опорного генератора 3 на выходе делителя 7 частоты с коэффициентом деления q возникает импульс, который поступает на тактовый вход блока 1 формирования кода фазы, на первом кодовом выходе которого формируется код фазы 1(без старшего разряда), поступающий далее на входы преобразователей 2 ц ко да, где N - четное. На выходе п-го из N преобразователей кода формируется код синусоидальной функции

Z,.sin,..

п 1, 2,..., N,

(1).

который поступает на соответствующий вход коммутатора 9. Частота F каждой из этих синусоидальных функций определяется выражением

F

К f в

Q Г

(2)

где Q - емкость накопителя;

f (Л, - частота сигнала опорного генератора 3;

Кр - код частоты, поступающий с

блока 21 переключателей блока 1 формирования кода фазы.

Частота fon/Q является тактовой частотой накопителя 22 кода фазы и накопителя 24 кода частоты.

Принцип действия формирователя сигнала с заданным законом изменения фазы основан на том, что синусоидальньй ступенчатый сигнал получают последовательным считыванием сдвинутых по фазе на iT/N выборок синусоидальной функции, формируемых в преобразователях 2, - 2 кода. Коды, соответствующие значениям этих выборок, подаются на N входов коммутатора 9, один из которых на определенное время подключается к его выходу. При изменении кода фазы значения выборок на выходах всех преобразователей 2 , - 2 кода изменяются, но в любом случае сдвиг фаз между сигналами, коды которых формируются на выходах преобразователей кода 2 - 2| кода с двумя соседними номерами, остается равным f/N. Таким образом, код на выходе коммутатора 9 пробегает N значений, соответствующих фазам от О до 180 с шагом ff/N. Код, соответствующий фазам от 180 до 360°, формируется на выходе коммутатора 13 путем инвертирования в необходимые моменты времени кода, соответствующего фазам О - 180°.

Коммутатор 9, блок 11 инверторов, коммутатор 13, регистр 4 памяти, ЦАП

При постоянном значении (f устрой ство, реализующее алгоритм (6), вы5 образуют первый-канал, а коммутатор2о полняет функцию фазовращателя, при

10, блок 12 инверторов, коммутатор 14, регистр 15 памяти и ЦАП 1-6 - второй канал, находящийся с первым строго в квадратуре за счет соответствующего подключения входов коммутаторов 9 и 25 10 к выходам преобразователей кода. Наличие квадратурных каналов необходимо для нормальной работы фазового детектора 18.

При линейном изменении кода фазы (на выходе блока 1 он пилообразный) частота сигнала на выходе первого и второго квадратурных каналов становится либо больше, либо меньше несущей частоты, равной , и определяется выражением

30

линейно изменяющейся фазе - синтеза тора частот, при более сложном зако изменения фазы - синтезатора сигналов .

В предлагаемом формирователе сиг налов с заданным законом изменения фазы (фиг. 1) в качестве 2М-фазной системы исходных периодических сигналов используются дискретные двухуровневые сигналы (фиг. 5), период которых разбит на 2N равных интерва лов :

35

U,(t)

1 при (т+п-1 )niod2N 0;

О при других m

где ,1,... - порядковый номер

f М + F - вых - г .

(3)

В выражении (3) плюс относится к положительным приращениям фазы, а минус - к отрицательным.

При суммировании периодических сигналов, входящих в 2Н-фазную систему и умноженных на соответствующие синусоидальные функции фазы tf, также образующие 2N-фaзнyю систему, результат содержит члены, зависящие только от разностей или только от сумм полных фаз составляющих периодического сигнала и фазы д. Любой периодический сигнал без постоянной составляющей с частотой со может быть записан в виде ряда Фурье

00

Uo(t) v E.(a sinKa)t + b cosKwt) (4)

Krl

в 2К-фазную систему сигналов,.кроме (4), входят также-.сигналы

) vflta.sinKCcot + -- -т:--)

N

ГГ(п-1)

+ b,cosKa.t -f ).

(5)

Фазе (f соответствует 2М-фазная система тригонометрических функций (1). Выходной сигнал

I(t) VN Zi (K6dt - I/) +

+ (Kut - t/) .

(6)

При смене знака перед (n-1)/N разность Kwt - (-С в (6) заменяется суммой Ktot + If , ,

При постоянном значении (f устрой ство, реализующее алгоритм (6), выполняет функцию фазовращателя, при

линейно изменяющейся фазе - синтезатора частот, при более сложном законе изменения фазы - синтезатора сигналов .

В предлагаемом формирователе сигналов с заданным законом изменения фазы (фиг. 1) в качестве 2М-фазной системы исходных периодических сигналов используются дискретные двухуровневые сигналы (фиг. 5), период которых разбит на 2N равных интервалов :

U,(t)

1 при (т+п-1 )niod2N 0;

(7)

О при других m

где ,1,... - порядковый номер

интервала; (m+n-1)mod2N - операция вычисления

суммы по модулю 2N. В системе сигналов (7) в любой момент времени отличен от нуля (т.е. равен 1) лишь один из сигналов, что дает возможность реализовать алгоритм (6), последовательно передавая на выход коммутаторов 9 и 10 соответствующие коды 2Ы-фазной системы синусоидальных функций фазы (1).

Iiмпyльcы опорного генератора 3 с частотой, в. N раз большей, чем требуемая частота оо исходных периодических сигналов, поступают на счетный вход реверсивного счетчика 28 блока 8 по модулю N и чрез делитель 30 частоты с коэффициентом деления N/2 - на реверсивный счетчик 29 по модулю 4. Направление с,чета определяется сигналом на входах установки режима реверсивных счетчиков 28 и 29, формируемого одновременно с кодом фазы в блоке

5

1 формирования кода фазы и поступающего с третьего кодового выхода блока 1 формирования кода фазы. Двоичный код числа с выхода реверсивного счетчика 28 поступает на управляющие входы коммутаторов 9 и 10, на выходы которых при этом поступает к с CN-(m)rDodN -ro информационного вхда. При этом сигнал код которого n является на выходе коммутатора 10, в разные моменты времени может отствать или опережать по фазе на 90 сигнал, код которого появляется на выходе коммутатора 9.

Это происходит потому, что. в прелагаемом устройстве используется 2N фазная система, а число преобразователей кода равно N. Недостающие N фаз можно получить инвертированием кодов, идущих с выхода преобразоватлей 2, - 2 кода. Однако инвертирование можно также осуществить и пос ле коммутаторов 9 и 10, что и сделано в предлагаемом формирователе сигналов с заданным законом изменения фазы. При этом число входов каждого из коммутаторов 9 и 10 сокращается вдвое и равно N.

Сигна.-л, управляющий такой инверсией в первом квадратурном канале, формируется на выходе старшего разряда реверсивного Счетчика 29 блока 8, а во втором квадратурном канале на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3

Для сокращения разрядности каждо

2i

го из преобразователей кода кода преобразование осуществляется , для кодов, соответствующих фазам О - 180°, а для фаз 180 - ЗбО берутся инвертированные коды диапазона О - 180°. Управление этой инверсией осуществляется старшим разрядом кода фазы, который входит в третий кодовый выход блока 1 формирования кода фазы и поступает на первые входы элементов ИСЮГОЧАЮЩЕЕ ИЛИ 32 и 33 блока 8, минуя преобразователи 2 , - 2 кода и коммутаторы 9 и 10.

Таким образом, и.нверсия осуществляется как по сигналу с выходов реверсивного счетчика 29 блока 8, так и по сигналу со старшего разряда кода фазы блока 1, а преобразование этих сигналов в управляющие сигналы, поступающие на первый и второй выход- блока 1, производится в соответствующем образом включенных элементах ИС- КЛЮЧАЮиП Е ИЛИ 31-33. Инверсия кодов

.

-io15

20

25

30

35

40

; 5550

непосредственно осуществляется в блоках 11 и 12 инверторов, а сигналЬ . управляющие инверсией, поступают на управляющие входы ко14мутаторов 13 и 14. С выхода каждого из них поступает либо прямой, либо инвертированный код.

В первом квадратурном канале сигнал управления инверсией, поступающий с выхода блока 8, является также старшим разрядом кода сигнала и поступает на вход старшего разряда регистра 4 памяти. То же самое происходит и во втором квадратурном канале (сигнал с выхода блока 8 поступает на вход старшего разряда регистра 15 памяти.

В случае, если число преобразователей 2, -2.1 кодов является степенью Р-.1

двойки, т.е. N 2 , р 2,3,4,.., блок 8 упрощается: реверсивный счетчик 28 становится двоичным и можно объединить функции реверсивных счет- чиков 28 и 29 и делителя 30 частоты, как показано на фиг. 36. В этом случае реверсивный счетчик 28 имеет емкость 2, а один из входов элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 33 и один из входов элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 31 соединены с выходом р-го разряда реверсивного счетчика 28, Другой вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 31 соединен с выходом (p-l)-ro разряда реверсивного счетчи ка 28.

Импульс с выхода опорного генератора 3, поступающий на тактовые входы регистров 4 и 15 памяти, осуществляет запись в них кодов соответственно первого квадратурного канала с выхода коммутатора 13 и второго квадратурного канала с выхода коммутатора 14. На выходе ЦАП 5 и 16 формируются напряжения, пропорциональные записанным кодам. Таким образом, разность фаз между сигналами на выходе первого квадратурного канала (выход ЦАП 5) и второго квадратурного канала (выход иДП 16) равна 90°, Сигнал с выхода первого квадратурного канала поступает на перестраиваемый фильтр 20.

Перестраиваемый фильтр 20 охвачен кольцом автоподстройки фазы, которое состоит из фазового детектора 18, фильтра 6 и сумматора 19. Для работы фазового детектора 18 необходимо,чтобы сдвиг фаз между сигналами на его входах был равен 90. Поэтому на его второй вход подается сигнал с выхода

перестраиваемого фильтра 20, а на. перв ый вход .- G выхода второго квадратурного канала. Поскольку выходной сигнал перестраиваемого фильтра 20 при совпадении частоты настройки с частотой сигнала имеет ту же фазу, что и сигнал на его входе, сигналы на входах фазового детектора 18 сдвинуты между собой по фазе на 90. Перестраиваемый фильтр 20 управляется напряжением, которое является суммой напряжений с выхода формирователя 17 и напряжения фазовой ошибки с выхода

синтезатора частот может быть выполнен на основе накопителя 22 кода фазы (фиг. 26), С каждьпч тактовым импульсом к кодУе записанному в накопителе 22 кода фазьЕ прибавляется код, установленный на блоке 21 перек.таоча- телей, в результате чего на выходе формируется линеййс нарастающий код фазыз соответствующий тре6уемо1 5у отклонению синтезируемой и исходной частот. Сигнал о знаке отклонения поступает с соответствующего переключателя блока 21 певек.зточателай и вме

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1327267A1 |

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1385238A2 |

| Формирователь сигналов с угловой модуляцией | 1985 |

|

SU1241411A1 |

| Генератор синусоидальных сигналов | 1990 |

|

SU1734189A1 |

| Фазовый модулятор | 1986 |

|

SU1388974A2 |

| Умножитель частоты | 1989 |

|

SU1695487A1 |

| Цифровой формирователь трехфазных синусоидальных сигналов | 1990 |

|

SU1732418A1 |

| Преобразователь угла поворота вала в код | 1988 |

|

SU1594689A1 |

| Цифровой синтезатор частот | 1988 |

|

SU1566454A1 |

| Устройство автоматической подстройки линейного закона частотной модуляции | 1984 |

|

SU1218463A1 |

Изобретение относится к радиоэлектронике. Для повышения точности формирования заданного закона изменения фазы выходного сигнала в устр- во введены блок 8 формирования сигналов управления, коммутаторы (К) 10, 13 и 14, блоки 11 и 12.инверторов, регистр 15 памяти ЦАП 16, формирователь 17 модулирующих сигналов, фазовый детектор 18, сумматор 19, перестраиваемый фильтр 20, В каждом q-м тракте опорного г-ра 3 на вьпсоде делителя 7 частоты с коэф. деления q возникает импульс, к-рьй поступает на тактовый вход блока 1 формирования кода фазы. На 1-м кодовом выходе блока 1 формируется код фазы 4, поступающий на преобразователи (П) 2 2-2 1 Н кода. На выходе п-го из П формируется код sin-функции, поступающий на соответствующий вход К 9. Принцип действия устр-ва основан на том, что sin-ступенчатый сигнал получают последовательным считыванием сдвинутых по фазе на /N выборок sin- функции, формируемых в П 2 - 2. Коды, соответствующие значениям этих вы- выборок, подаются на N входов К 9, При изменении кода фазы значения вы- ;борок на выходах П 2 - 2 j изменяют- ся. Но сдвиг фаз между сигналами, коды к-рых формируются на выходах П (О (Л 2v - 2 HJ с двумя соседними номерами. остается равным /T/N. 5 ил.

фазового детектора 18. Так как напря-|5 сигналом, идущим со старшего

25

30

35

жепие грубой перестройки .мало отличается Ьт требуемого напряжения управления, амплитуда напряжения сигнала ошибки мала и, следовательно, фа- зовьй детектор 18-работает на линей- 20 ном участке характеристики.

Формирователь 17 модулирующих сигналов в случае использования формирователя сигналов с заданным законом изменения фазы в качестве синтезатора частот представляет собой ДАЛ 34, на йход которого подается код частоты (фиг. 4а), а в случае использования устройства в качестве синтезатора линейно-частотно-модулированкых . (ЛЧМ) сигналов представляет собой сумматор 37, один вход которого подключен к выходу ЦАП 34, на вход ;кото- рого подается код начальной частоты, а другой вход подключен к интегратору 36 со сбросом, на который подается с ЦАП 35, на вход которого подается код скорости (фиг. 4б).

На вход сброса интегратора 36 подается сигнал с выхода ждущего ryль тивибратора 27, формирующего импульс сброса по сигналу с выхода триггера 26 блока 1.

Блок 1 формирования кода фазы при использовании устройства в качестве фазовращателя может быть выполнен, например, в виде блока 21 переключа- теле й (фиг, 2а) каждый на два положения, в одном из которых на соответствующий выход блока поступает напряжение О, а в другом - 1. Меняя положение переключателей блока 21 переключателей, можно формировать различные коды фазы. Сигнал о знаке сдвига фазы поступает с соответствующего переключателя блока 21 переклю-55 чателей по третьему кодовому выходу. Блок 1 формирования кода фазы при использовании устройства в качестве

40

45

разряда накопителя 22, он поступает на третий кодовый выход блока 1 фор мирования кода фазы. Код тастсты, у тановленный на блоке 21 переклю ате леЙ5 поступает на второй кодовый вы ход блока 1 формирования кода . Код с выхода накопителя 22 поступае на первый выход блока 1 формировани кода фазы,

При использовании устройства: з к честве синтезатора ЛЧМ (фиг. 2в} си налов в накопителе 24 ксла частоты входящем в состав блока 1 формирова ния кода фазы, формируется лии ейчо изменяющийся код частоты. Этот код суммируется с кодо начальной час го ты, поступающим с блока 21 переключателей, в комбинационном c TvfMaTope 23 о В накоп1 :теоЧе 22 кода форми руется код фазь ЛЧМ ег гкала, изменя ющийся по параболическому закону, П этом сигнал со старшего разряда ком бинационного cyt-iNJaTopa 23 поступает на триггер 26., а с выхода последкего - на вход управления управляемог инвертора 25 Кроме того, он вместе с сигналом со стратеге разряда нако пителя 22 кода фазь постз пает на тр тий кодовый выход блока i формирова ния кода фазы.

Если при сигнале с выхода тригге ра 26, равном О, обеспечивается и вертирование управляемъ ь) инвертором 25 всех разрядов кода фазы кроме старшего, и режим сложения в ревер сивных счетчиках 28 и 29j а при сиг нале 1 - прямое пропускание и реж вычитания соответственно, то тогда реализуется возрастающий закон лине ной частотной модуляции.

Для получения падающего закона н обходимо при сигнале О в старшем разряде комбинацконного сумматора 2 обеспечить прямое прохс ;. 1.екне остал

5 сигналом, идущим со старшего

5

0

5

0

5

0

5

разряда накопителя 22, он поступает на третий кодовый выход блока 1 формирования кода фазы. Код тастсты, установленный на блоке 21 переклю ате- леЙ5 поступает на второй кодовый выход блока 1 формирования кода . Код с выхода накопителя 22 поступает на первый выход блока 1 формирования кода фазы,

При использовании устройства: з качестве синтезатора ЛЧМ (фиг. 2в} сигналов в накопителе 24 ксла частоты, входящем в состав блока 1 формирования кода фазы, формируется лии ейчо изменяющийся код частоты. Этот код суммируется с кодо начальной час готы, поступающим с блока 21 переключателей, в комбинационном c TvfMaTope 23 о В накоп1 :теоЧе 22 кода формируется код фазь ЛЧМ ег гкала, изменяющийся по параболическому закону, При этом сигнал со старшего разряда комбинационного cyt-iNJaTopa 23 поступает на триггер 26., а с выхода последке го - на вход управления управляемого инвертора 25 Кроме того, он вместе с сигналом со стратеге разряда накопителя 22 кода фазь постз пает на третий кодовый выход блока i формирования кода фазы.

Если при сигнале с выхода тригге-v ра 26, равном О, обеспечивается инвертирование управляемъ ь) инвертором 25 всех разрядов кода фазы кроме старшего, и режим сложения в реверсивных счетчиках 28 и 29j а при сигнале 1 - прямое пропускание и режим вычитания соответственно, то тогда реализуется возрастающий закон линейной частотной модуляции.

Для получения падающего закона необходимо при сигнале О в старшем разряде комбинацконного сумматора 23 обеспечить прямое прохс ;. 1.екне осталь

ных разрядов через управляемый инвертор 25 и режим вычитания реверсивных счетчиков 28 и 29, а при сигнале 1 инвертирование и режим сложения соответственно.

На :выходе; триггера 26 формируется перепад, означающий окончание ЛЧМ сигнала. По этому перепаду формирует ся узкий импульс в щцущем мультивибраторе 27, являющийся сигналом сброса в О интегратора 36, Этот сигнал поступает на второй кодовый выход блока 1 формирования кода фазы наряду с кодом начальной частоты и кодом скорости, идущих с блока 21 переключателей.

Преобразователи 2 н кода могу быть, например, . выполнены на основе постоянного запоминающего устройства (ПЗУ) соответствующего объема.

Формирователь сигналов с заданным законом изменения фазы.осуществляет перенос сигнала, сформированного на низкой частоте, на несущую частоту, что позволяет максимально использовать разрядную сетку блока 1 формирования кода фазы и преобразователей 2, - 2 кода и снизить требования к быстродействию эти-х узлов.. Перенос на несущую частоту осуществляется цифровыми метод.ш, причем используетс лишь один канал фо я шрования, а второй канал является вспомогательньм, обеспечивающим нормальную работу фазового детектора 18,

Следящий фи:тьтр9 состоящий из пе рестраиваемого фильтра 20 и цепи автоподстройки фазы, Не вносит фазовог сдвига между его входом и выходом, а второй квадратурный канал, необходимый для нормальной работы фазового детектора 18 идентичен первому квадратурному каналу.

Следящий фильтр имеет значительно сниженный размах напряжения на выходе. Это достигается тем, что фазовым детектором 18 формируется не все напряжение, управляющее перестраиваемым фильтром 20, а только напряжение сиг .нала ошибки, которое значительно ме ньше напряжения грубой перестройки, поступающего с выхода формирователя 17 модулирующих сигналов При этом фазовый детектор 18 работает на линейном участке характеристики. Кроме того., приняты меры, обеспечивающие точный 90 Градусный сдвиг фаз между квадратурнь ми каналами.

ормула

10

3 о

бретения0

0

с

Q

Ь

Формирователь сигналов с заданным законом изменения фазы, содержащий последовательно соединенные опорньй Генератор и делитель частоты, выход которого соединен с тактовым входом блока формирования кода фазы, N преобразователей кода, входы которых со единены с первым кодовым выходом блока формирования «кода фазы, а выходы первого, второго о., N-ro преобразователей кода соединены соответственно с первым, вторым,..., N-M сигналь ными входами первого коммутатора, последовательно соединенные первый регистр памяти, тактовый вход которого соединен с выходом опорного генератора, и первый цифроаналоговый преобразователь, а также фильтр нижних частот, о тличающий ся тем,- что, с целью повышения точности формирования заданного закона изменения 5 фазы выходного сигнала;, в него введены второй коммутатор, первый, второй, ,..,N/2-й сигнальные входы которого соединены соответственно с выходами (N/2+1)-ro, (N/2+2)-ro,o,., N-ro преобразователей кода.а (N/2+1)-й, ()-й,..., N-й а гнальные входы соответственно с .выходами первого, второго,., I, преобразователей кода, где N - четное число, третий коммутатор, первый сигнальный вход ко- которого соединен с выходом первого коммутатора5 а выход - с входом млад- ших разрядов перво1-о регистра памяти, первый блок инверторов, который включен между выходом первого oм yтaтo- ра и вторым сигнальным входом третьего коммутатора, четвертый коммутатор,

первьй сигнальный вход котосого сое-

дннен с вьтходом второго коммутатора,, второй блок инвертора,, который включен мехщу выходом второго ко даутато- ра и вторыь сигнальным входом четвертого коммутатора, последовательно соединенные второй регистр памяти, вход младших разрядов котс-рого соединен с выходок четвертого коммутатора, второй цкфроаналоговый преобразователь и фазовый детекторS выход которого соеди яек с входом фильтра нижних час- тот, перестраиваемый фильтр, сигналь- нтий вход которого соединен с выходом цифроаналоговОго преобразователя, а выход - с вторым входом фазового детектора, сумма гор, первый вход

5

0

5

0

которого соединен с вьгходом фильтра нижних частот, а выход - с управляющим входом перестраиваемого фильтр а, формирователь модулирующих сигналов, вход которого соединен с вторым кодовым выходом блока формирования кода фазы, а выход - с вторым входом сумматора, блок формирования сигналов управления, счетный вход которого соединен с выходом опорного генератора, сигнальный вход - с третьим кодовым выходом блока формирования кода фазы, первый выход сигнала управления инверсией - с управляющим

J-U кодо- fBbia Sbi- ход

3 йко/и- ьыи 8ыход

2-й кодовый Ьыход Фиг. 2

входом третьего коммутатора и входом старшего разряда первого регистра памяти, второй выход сигнала управления инверсией - с управляющим входом четвертого коммутатора и вxoдo f старшего разряда второго регистра памят ., а кодовый выход - с упранляюшими входами первого и второго коммутаторов,; при этом тактовый вхо;: BTODOJ O регистра памяти соединен с вьгходом опорного генератора,- а выход перестраиваемого фильтра является выходом формирователя сигналов с эаданньп. законом изменения фазы.

Тактовый

И,-.-..

ш

11

,. ;.ч.,

.

hi и Выход

, Тактовый Sxod

1385239

Сигнальный Sxod

Сигнальный былод

2 J

2N

Фиг. 5

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1327267A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-03-30—Публикация

1986-11-20—Подача