N)

Изобретение относится к радиоэлектронике и может быть использовано для формирования сигналов с заданным законом изменения фазы, например, в ка- либраторах фазы, синтезаторах частот, синтезаторах с полиноминальным законом изменения частоты.

Цель изобретения - расширение полосы частот формируемых сигналов.

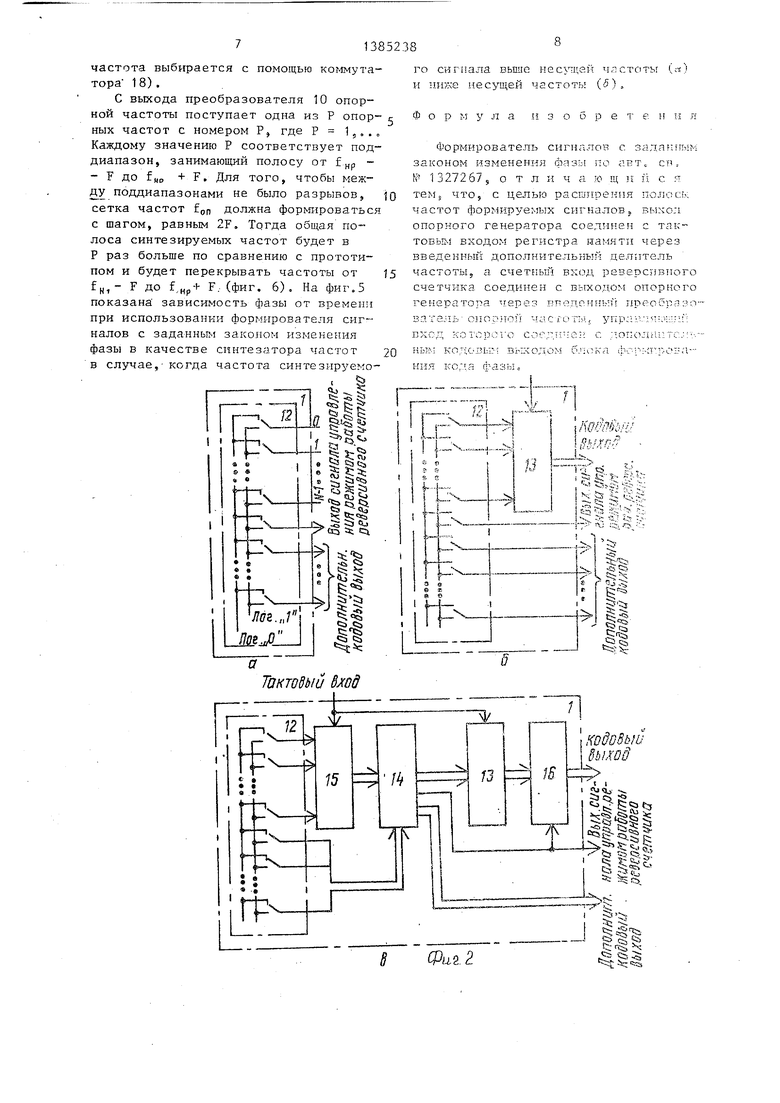

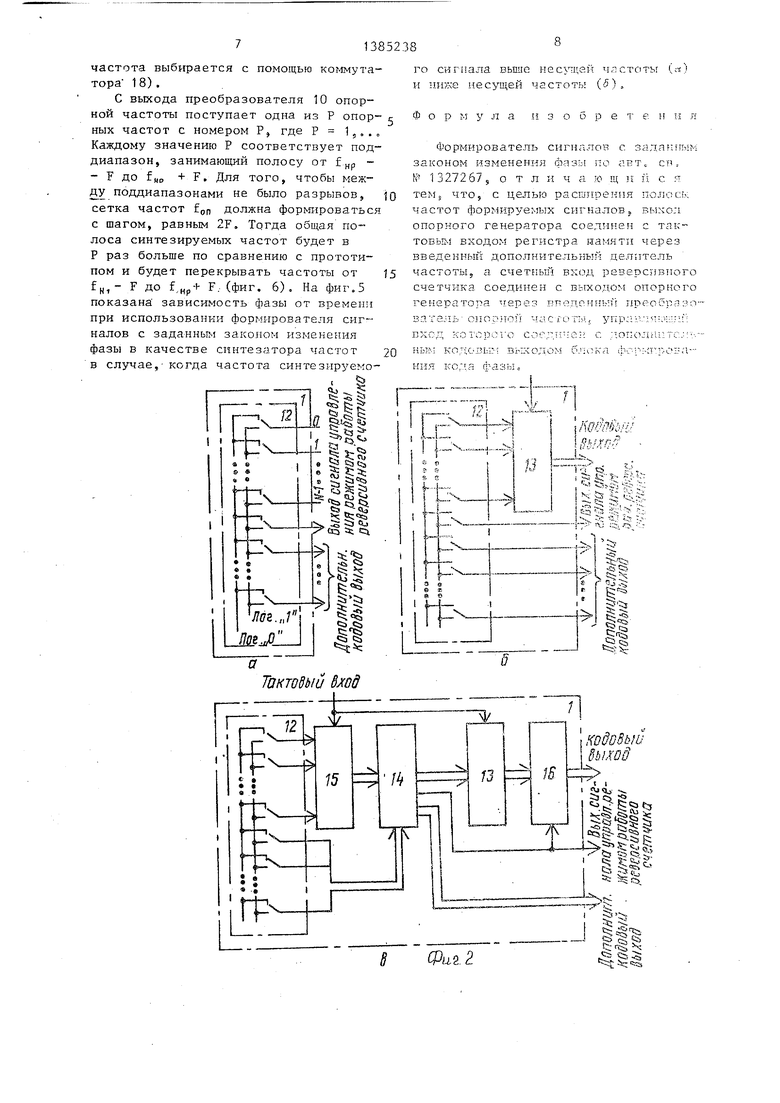

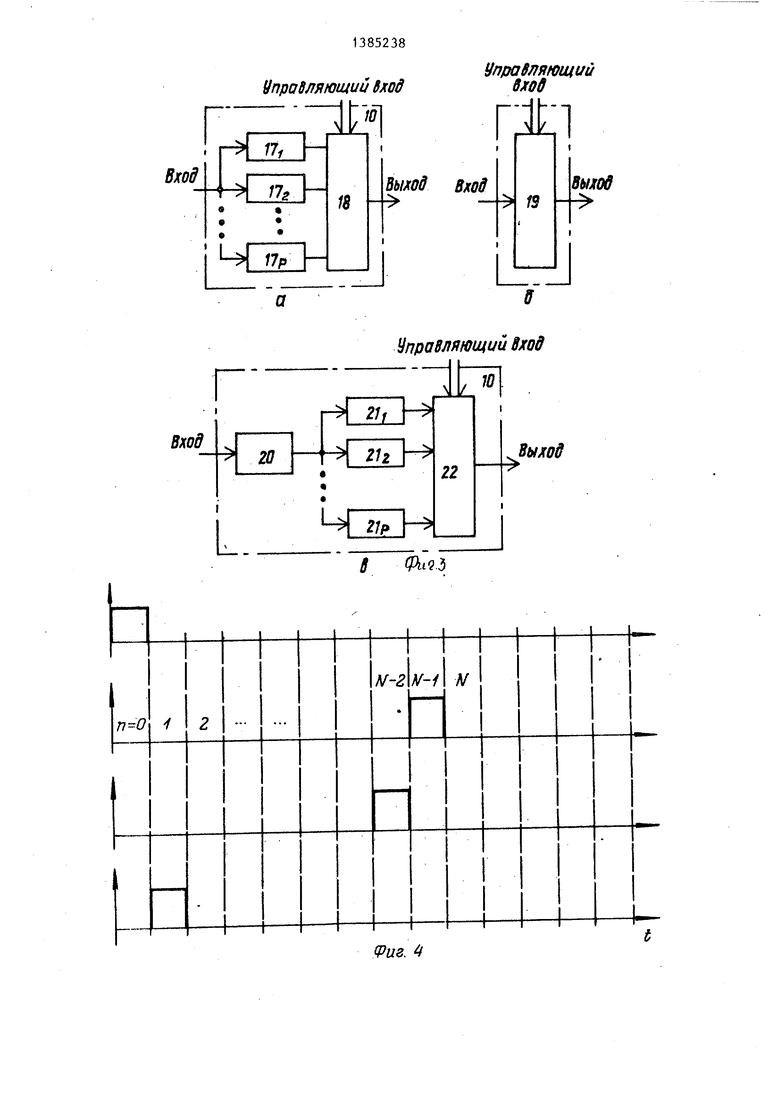

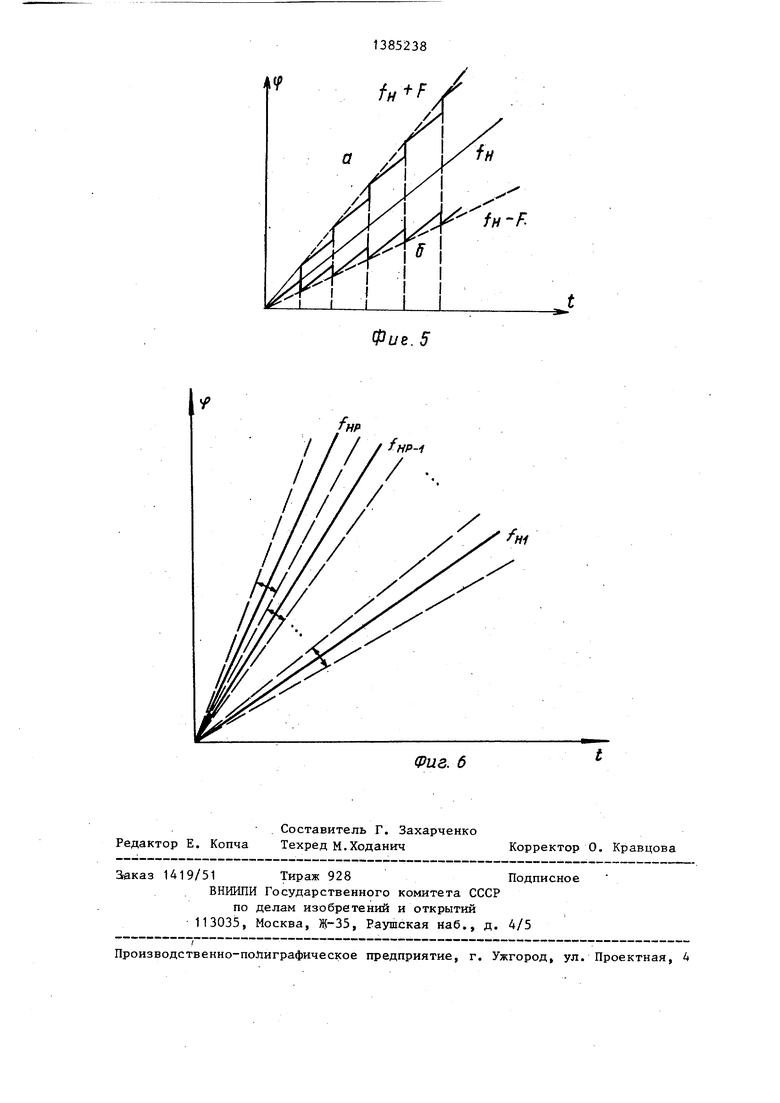

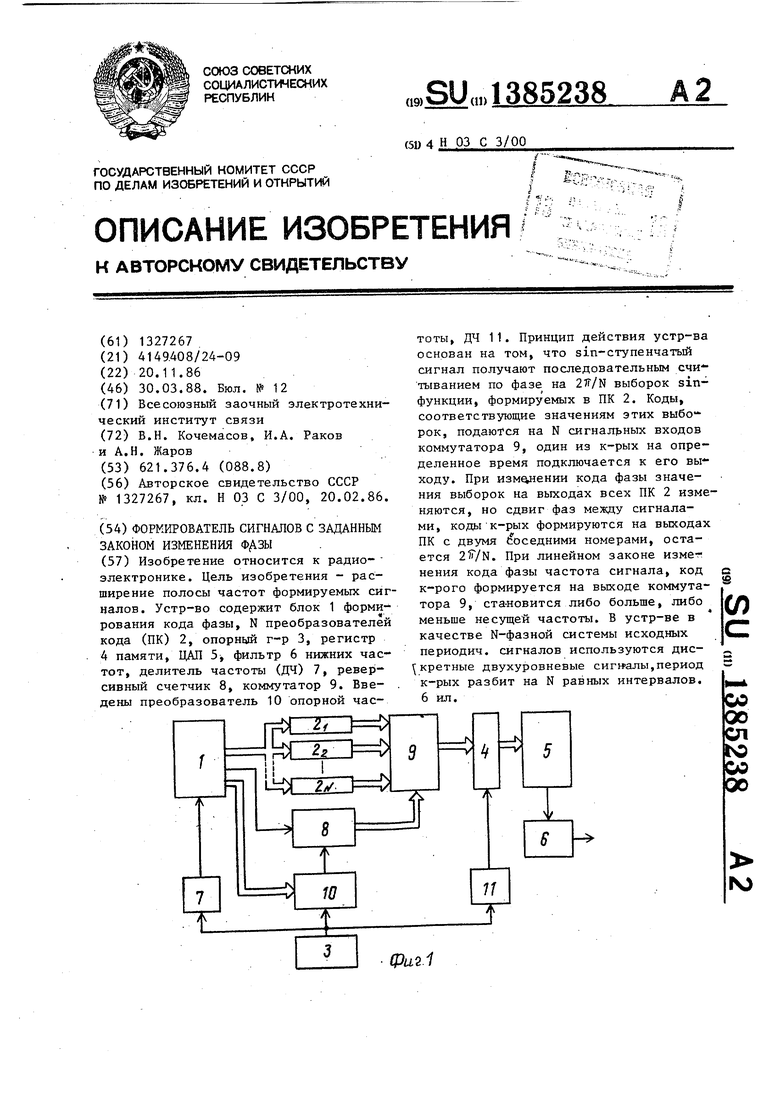

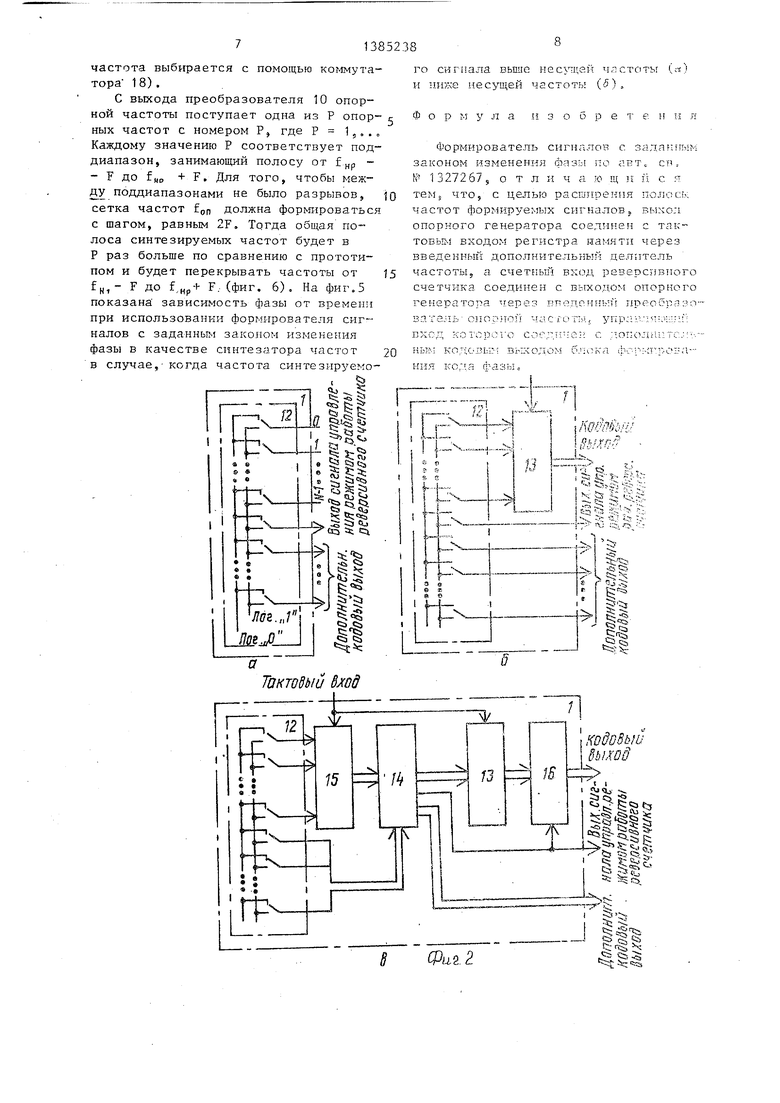

На фиг. 1 изображена структурная электрическая схема предлагаемого формирователя сигналов с заданным законом изменения фазы; на фиг. 2 - примеры реализации блока формирования кода фазы; на ijsir. 3 - примеры реализации преобразователя опорной частоты; на фиг, 4 - диаграммы системы используемых исходных двухуровневых . сигналов; на фиг. 5 - график зависи- мости фазы от времени при использовании формирователя сигналов с заданным законом изменения фазы в качестве синтезатора частот; на фиг. 6 - график зависимости фазы от времени при раз- ных значениях несущей частоты f

Формирователь сигналов с заданным законом изменения фазы содержит блок

Iформирования кода фазы, N преобра- зователей 2 ,-2 кода, опорный генератор 3, регистр 4 памяти, цифроана- логовый преобразователь (ЦАП) 5, фильтр 6 нижних частот (ФНЧ), дели тель 7 частоты, реверсивный счетчик 8, коммутатор 9|, преобразователь 10 опорной частоты, дополнительный делитель

I1частоты.

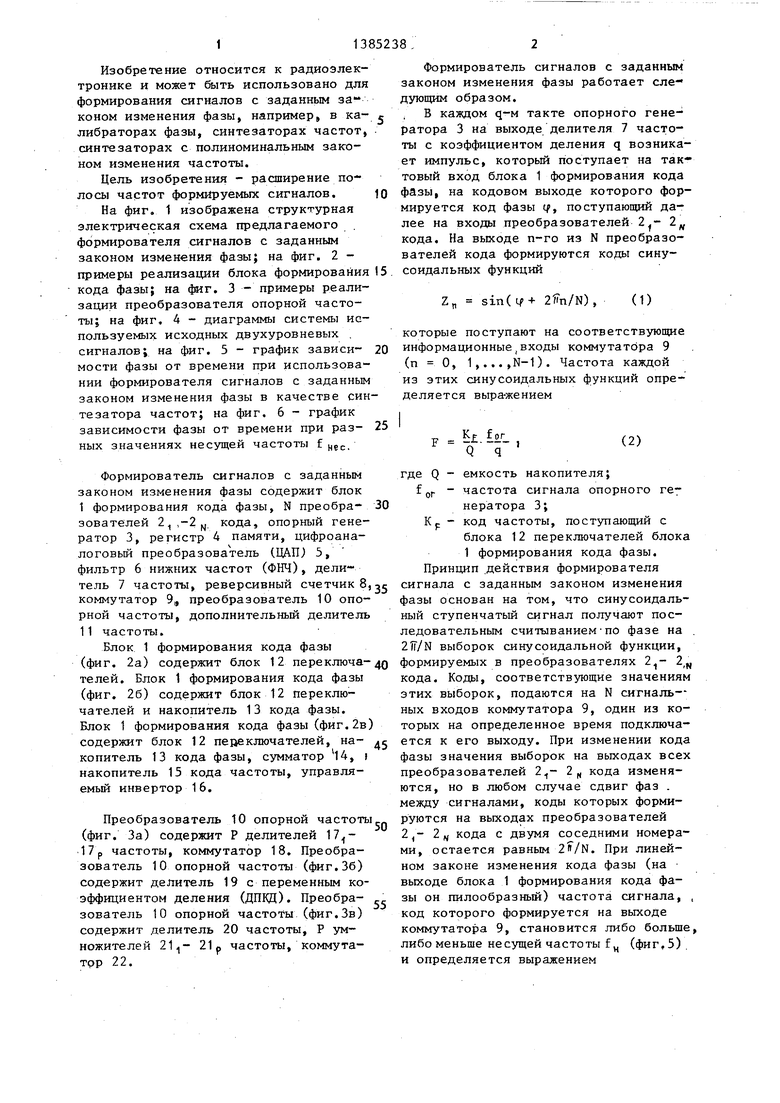

Блок 1 формирования кода фазы (фиг. 2а) содержит блок 12 переключателей. Блок 1 формирования кода фазы (фиг. 26) содержит блок 12 переключателей и накопитель 13 кода фазы. Блок 1 формирования кода фазы (фиг.2в) содержит блок 12 певеключателей, на- копитель 13 кода фазы, сумматор 14, i накопитель 15 кода частоты, управляемый инвертор 16.

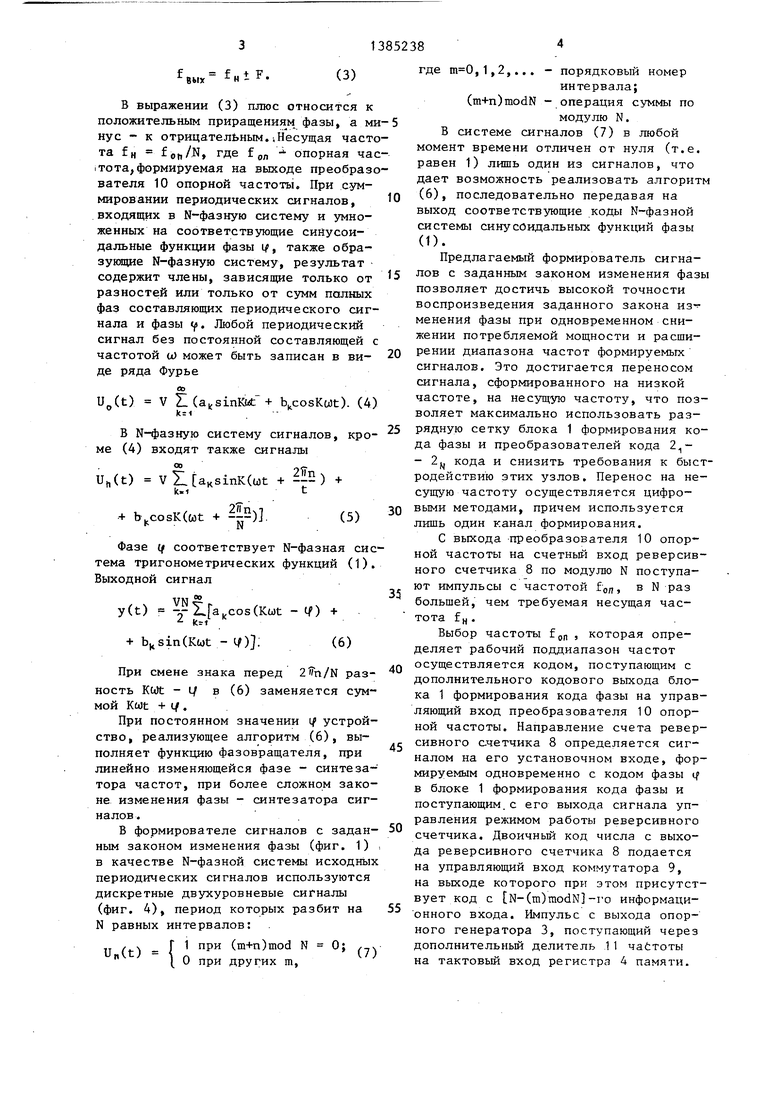

Преобразователь 10 опорной частоты (фиг. За) содержит Р делителей 17р частоты, коммутатор 18. Преобразователь 10 опорной частоты (фиг.36) содержит делитель 19 с переменным коэффициентом деления (ДПКД). Преобразователь 10 опорной частоты (фиг.Зв) содержит делитель 20 частоты, Р умножителей 21р частоты, коммута- трр 22.

Формирователь сигналов с заданным законом изменения фазы работает еле- дующим образом.

В каждом q-M такте опорного генератора 3 на выходе делителя 7 частоты с коэффициентом деления q возникает импульс, который поступает на тактовый вход блока 1 формирования кода фазы, на кодовом выходе которого формируется код фазы (f, поступающий далее на входы преобразователей 2 кода. На выходе п-го из N преобразователей кода формируются коды синусоидальных функций

г„ sin( 2WN), (1)

которые поступают на соответствующие информационные,входы коммутатора 9 (п О, 1,...,N-1). Частота каждой из этих синусоидальных функций определяется выра-жением

F Б. ki . Q q

(2)

0 с

0 с

0

5

где Q - емкость накопителя;

fgr частота сигнала опорного генератора 3;

Кр - код частоты, поступающий с

блока 12 переключателей блока 1 формирования кода фазы.

Принцип действия формирователя сигнала с заданным законом изменения фазы основан на том, что синусоидальный ступенчатый сигнал получают последовательным считыванием ПО фазе на 2f/N выборок синусоидальной функции, формируемых в преобразователях 2, кода. Коды, соответствующие значениям этих выборок, подаются на N сигналь- ных входов коммутатора 9, один из которых на определенное время подключается к его выходу. При изменении кода фазы значения выборок на выходах всех преобразователей 2 кода изменяются, но в любом случае сдвиг фаз . между сигналами, коды которых формируются на выходах преобразователей 2,- 2 кода с двумя соседними номерами, остается равным . При линейном законе изменения кода фазы (на выходе блока 1 формирования кода фазы он пилообразный) частота сигнала, , код которого формируется на выходе коммутатора 9, становится либо больше, либо меньше несущей частоты f (фиг,5) . и определяется выражением

ВЫХ

fntF.

(3)

В выражении (3) плюс относится к положительным приращениям фазы, а ми-5 нус - к отрицательным.iНесущая частота « fot,/N, где f on - опорная час- Iтота,формируемая на выходе преобразователя 10 опорной частоть. При сум10

мировании периодических сигналов, входящих в N-фазную систему и умноженных на соответствующие сийусои- дальные функции фазы (f, также образующие N-фазную систему, результат содержит члены, зависящие только от

разностей или только от сумм полных фаз составляющих периодического сигнала и фазы /. Любой периодический сигнал без постоянной составляющей с частотой о) может быть записан в ви- де ряда Фурье

OD

U.Ct) V Е (а| 8шЬал; + b.cosKwt). (4) kn

В N-фазную систему сигналов, кроме (4) входят также сигналы

00„,..

Urt(t) vlLiaKsinK(ut + --2) + k.iС

+ b.cosK(tot + --). f.N

(5)

Фазе If соответствует N-фазная система тригонометрических функций (1). Выходной сигнал

y(t) -.-lfa,cos(K6)t - tf) + . - Icn

+ (Kut - t/)}.(6)

При смене знака перед ZTn/N раз- ность KWt - t/ в (6) заменяется суммой KuJt + I/.

При постоянном значении (f устройство, реализующее алгоритм (6), выполняет функцию фазовращателя, при линейно изменяющейся фазе - синтеза- тора частот, при более сложном законе изменения фазы - синтезатора сигналов.

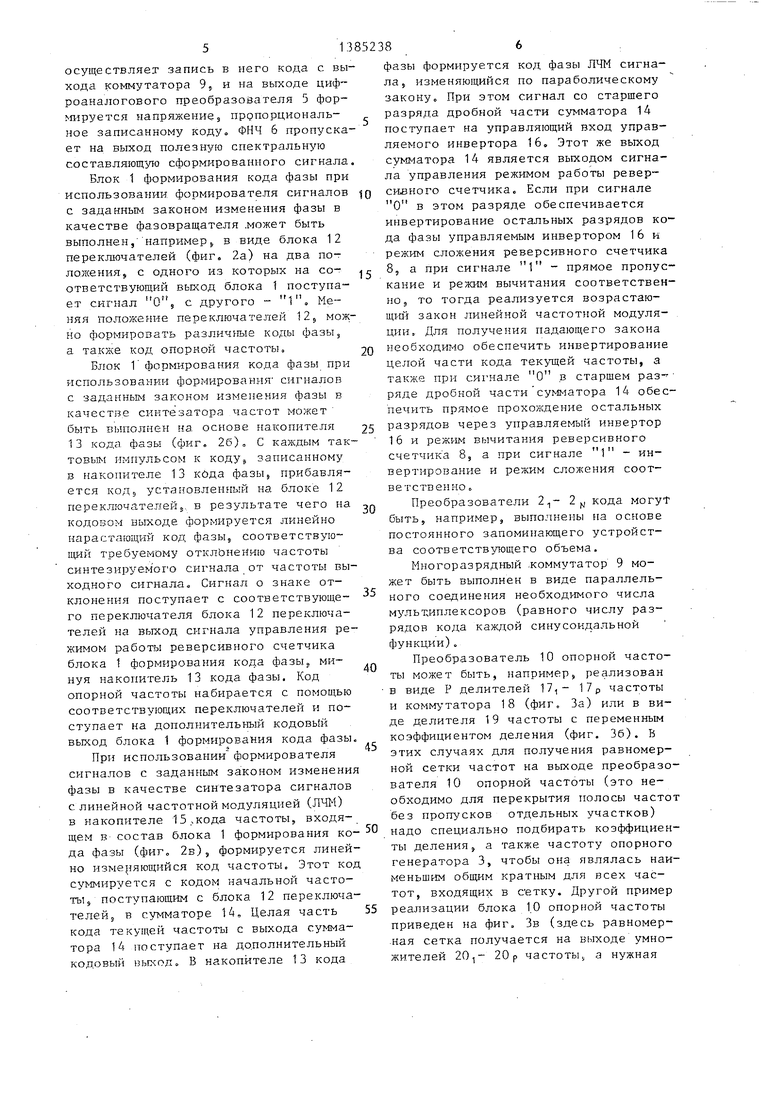

В формирователе сигналов с задан- ным законом изменения фазы (фиг. 1) в качестве N-фазной системы исходных периодических сигналов используются дискретные двухуровневые сигналы (фиг. 4), период которых разбит на N равных интервалов:

и (t) Р (m+n)mod N 0; О при других т.

5

0

5

0

30

35

50 55

где ,1,2,... - порядковый номер

интервала;

(m+n)modN - операция суммы по модулю N.

В системе сигналов (7) в любой момент времени отличен от нуля (т.е. равен 1) лишь один из сигналов, что дает возможность реализовать алгоритм (6), последовательно передавая на выход соответствующие коды N-фазной системы синусоидальных функций фазы (1).

Предлагаемый формирователь сигналов с заданным законом изменения фазы позволяет достичь высокой точности воспроизведения заданного закона из- менений фазы при одновременном снижении потребляемой мощности и расширении диапазона частот формируемых сигналов. Это достигается переносом сигнала, сформированного на низкой частоте, на несзпцую частоту, что позволяет максимально использовать разрядную сетку блока 1 формирования кода фазы и преобразователей кода - 2ц кода и снизить требования к быстродействию этих узлов. Перенос на несущую частоту осуществляется цифро- вьми методами, причем используется лишь один канал формирования.

С выхода преобразователя 10 опорной частоты на счетньш вход реверсивного счетчика 8 по модулю N поступают импульсы с частотой fon, в N раз большей, чем требуемая несущая частота f н .

Выбор частоты , которая определяет рабочий поддиапазон частот осуществляется кодом, поступающим с дополнительного кодового выхода блока 1 формирования кода фазы на управляющий вход преобразователя 10 опорной частоты. Направление счета реверсивного счетчика 8 определяется сигналом на его установочном входе, формируемым одновременно с кодом фазы if в блоке 1 формирования кода фазы и поступающим.с его выхода сигнала управления режимом работы реверсивного счетчика. Двоичный код числа с выхода реверсивного счетчика 8 подается на управляющий вход коммутатора 9, на выходе которого при этом присутствует код с N-(m) информационного входа. Импульс с выхода опорного генератора 3, поступающий через дополнительньй делитель 1 1 ча(тоты на тактовый вход регистра 4 памяти.

осуществляет запись в него кода с выхода коммутатора 9, и на выходе циф роаналогового преобразо)зателя 5 формируется напряжениеэ пропорциональное записанному коду ФНЧ 6 пропускает на выход полезную спектральную составляющую сформированного сигнала Блок 1 формирования кода фазы при использовании формирователя сигналов с заданным законом изменения фазы в качестве фазовращателя .может быть выполнен, например в виде блока 12 переключателей (фиг. 2а) на два положения, с одного из которых на соответствующий выход блока 1 поступасигнал О

| п

с другого

1

Ме

няя положение переключателей 12 можно формировать различные коды фазы, а также код опорной частоты,

BjfOK 1 формирования кода фазы при использовании формирования сигналов с заданным законом изменения фазы в качестве синтезатора частот может быть вьшолнен на основе накопителя 13 кода, фазы (фиг. 2б)„ С каждым тактовым импульсом к коду, записанному в накопителе 13 кода фазы, прибавляется код, установленный на блоке 12 переключателей,, в результате чего на кодовом выходе формируется линейно нарастающий код фазы5 соответствующий требуемому отклЬнеНию частоты синтезируем ог о сигнала от частоты выходного сигнала Сигнал о знаке отклонения поступает с соответствующего переключателя блока 12 переключателей на выход сигнала управления режимом работы реверсивного счетчика блока t формирования кода фазы, минуя накопитель 13 кода фазы. Код опорной частоты набирается с помощью соответствующих переключателей и поступает на дополнительный кодовь5й выход блока 1 формирования кода фазы

При использовании формирователя сигналов с заданным законом изменения фазы в качестве синтезатора сигналов с линейной частотной модуляцией (ЛЧМ) в накопителе 15,кода частоты, входящем в состав блока 1 формирования кода фазы (фиг„ 2в), формируется линейно измеряюпщйся код частоты. Этот код суммируется с кодом начальной частоты, поступающим с блока 12 переключателей; в сумматоре 14, Целая часть кода текущей частоты с выхода сумматора 14 поступает на дополнительный кодовый выход. В накопителе 13 кода

. 3852386

фазы формируется код фазы ЛЧМ сигнала, изменяющийся по параболическому закону. При этом сигнал со старшего разряда дробной части сумматора 14 поступает на управляющий вход управляемого инвертора 16. Этот же выход сумматора 14 является выходом сигнала управления режимом работы реверсивного счетчика. Если при сигнале

to

15

25

30

35

20

,

55

40

45

50

О в этом разряде обеспечивается инвертирование остальных разрядов кода фазы управляемым инвертором 16 и режим сложения реверсивного счетчика 8, а при сигнале 1 - прямое пропускание и ретким вычитания соответственно, то тогда реализуется возрастаю- щи11 закон линейной частотной модуляции. Для получения падающего закона необходимо обеспечить инвертирование целой части кода текущей частоты, а также при сигнале О в старшем раз- ряде дробной части сумматора 14 обеспечить прямое прохождение остальных разрядов через управляемый инвертор 16 и режим вычитания реверсивного счетчика 8, а при сигнале 1 - инвертирование и режим сложения соответственно .

Преобразователи 2 кода могут быть, например, выполнены на основе постоянного запоминающего устройства соответствующего объема.

Многоразрядный ,коммутатор 9 может быть вьшолнен в виде параллельного соединения необходимого числа мульт иплексоров (равного числу разрядов кода каждой синусоидальной функции).

Преобразователь 10 опорной частоты может быть, например, реализован в виде Р делителей 17р частоты и коммутатора 18 (фиг. За) или в виде делителя 19 частоты с переменным коэффициентом деления (фиг. Зб). В этих случаях для получения равномерной сетки частот на выходе преобразователя 10 опорной частоты (это необходимо для перекрытия полосы частот без пропусков отдельных участков) надо специально подбирать коэффициенты деления, а также частоту опорного генератора 3, чтобы она являлась наименьшим общим кратным для всех частот, входящих в сетку. Другой пример реализации блока 1.0 опорной частоты приведен на фиг, Зв (здесь равномерная сетка получается на выходе умножителей 20i 20р частоты, а нужная

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1385239A1 |

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1327267A1 |

| Устройство для определения вероятностных характеристик фазы случайного процесса | 1985 |

|

SU1300510A2 |

| Цифровой синтезатор частот | 1988 |

|

SU1517016A1 |

| Цифровой синтезатор сигналов | 1988 |

|

SU1626314A1 |

| Устройство для управления автономнымиНВЕРТОРОМ | 1979 |

|

SU830631A1 |

| Цифровой синтезатор частот | 1988 |

|

SU1566454A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ФАЗЫ РАДИОСИГНАЛА | 1992 |

|

RU2050552C1 |

| УСТРОЙСТВО ПОИСКА И СЛЕЖЕНИЯ ЗА ШИРОКОПОЛОСНЫМ СИГНАЛОМ | 1983 |

|

SU1840276A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР СИГНАЛОВ | 2004 |

|

RU2257669C1 |

Изобретение относится к радио- - электронике. Цель изобретения - расширение полосы частот формируемых сигналов. Устр-во содержит блок 1 формирования кода фазы, N преобразователей кода (ПК) 2, опорный г-р 3, регистр 4 памяти, ЦАП 5 фильтр 6 нижних частот, делитель частоты (ДЧ) 7, ревер - сивный счетчик 8, коммутатор 9. Введены преобразователь 10 опорной частоты, ДЧ 11. Принцип действия устр-ва основан на том, что sin-ступенчатый сигнал получают последовательным счи- тыванием по фазе на 27r/N выборок sin- функции, формируемых в ПК 2. Коды, соответствующие значениям этих выбо рок, подаются на N сигнальных входов коммутатора 9, один из к-рых на определенное время подключается к его вы ходу. При изменении кода фазы значения выборок на выходах всех ПК 2 изменяются, но сдвиг фаз между сигналами, коды к-рых формируются на выходах ПК с двумя Ьоседними номерами, остается . При линейном законе измег- нения кода фазы частота сигнала, код к-рого формируется на выходе коммутатора 9, становится либо больше, либо меньше несущей частоты. В устр-ве в качестве N-фазной системы исходных периодич. сигналов используются дис- кратные двухуровневые сигналы,период к-рых разбит на N равных интервалов. 6 ил. с (Л

Тактовый ёмд

кодовый Ьыкод

t 1

1 - Сг S 3 t-T

Sill I

- ь --:гК5;;; .

fell

Фи2.2

-,v vvi, w:

t

Управляющий дход

И

Вход

Вход

.

Управляющий Sxod

Г

It

Выход Вход

fS

Выход

У

S

Управляющий 8ход

Выход

8 Фи гЪ

ы-г

V-/

V

иг.

Фив. 5

HP-i

л

Hi

Фиг. б

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1327267A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-03-30—Публикация

1986-11-20—Подача