1

Изобретение относится к автоматике и вычислительной технике и может быть использовано дли контроля логических схем (блоков), имеющих большое число входов, и определения неисправностей в них.

Цель изобретения - повьппенйе быстродействия контроля и расширение функциональных возможностей за счет того, что в каждом цикле работы устройства (с тактовой частотой) устанавливается новая случайная последовательность на всех выходах генератора случайных последовательностей и дополнительной индикации неисправности, проявляющейся в переходном режиме .

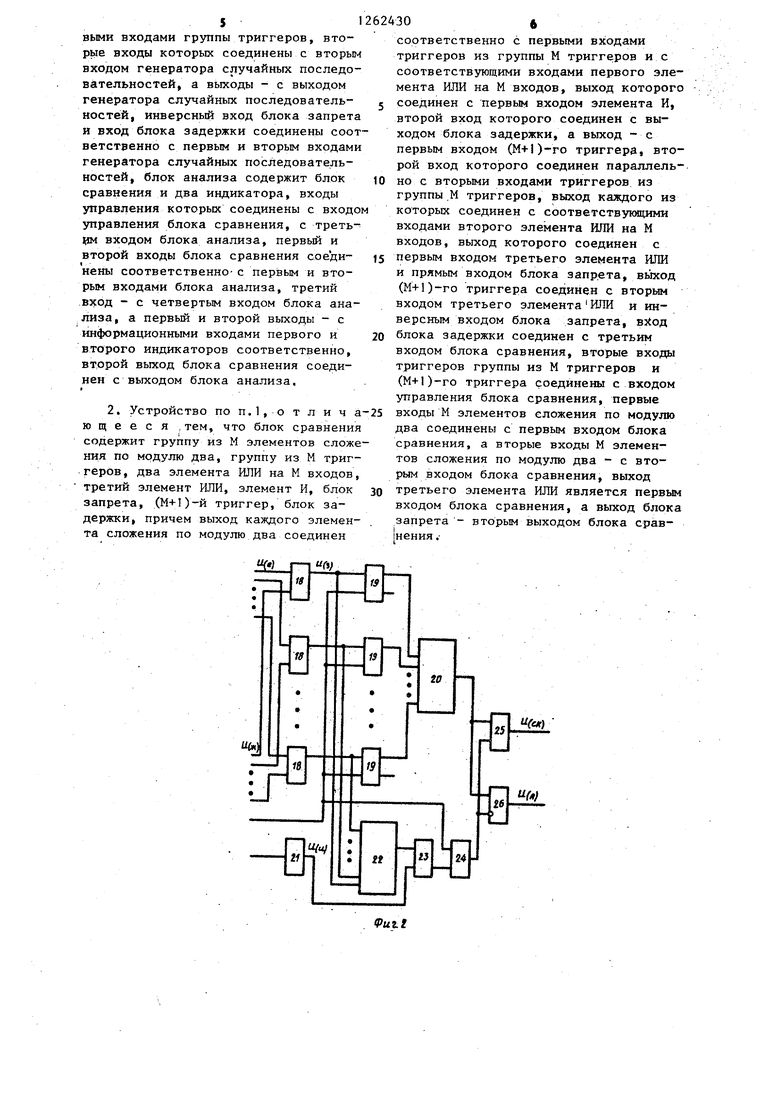

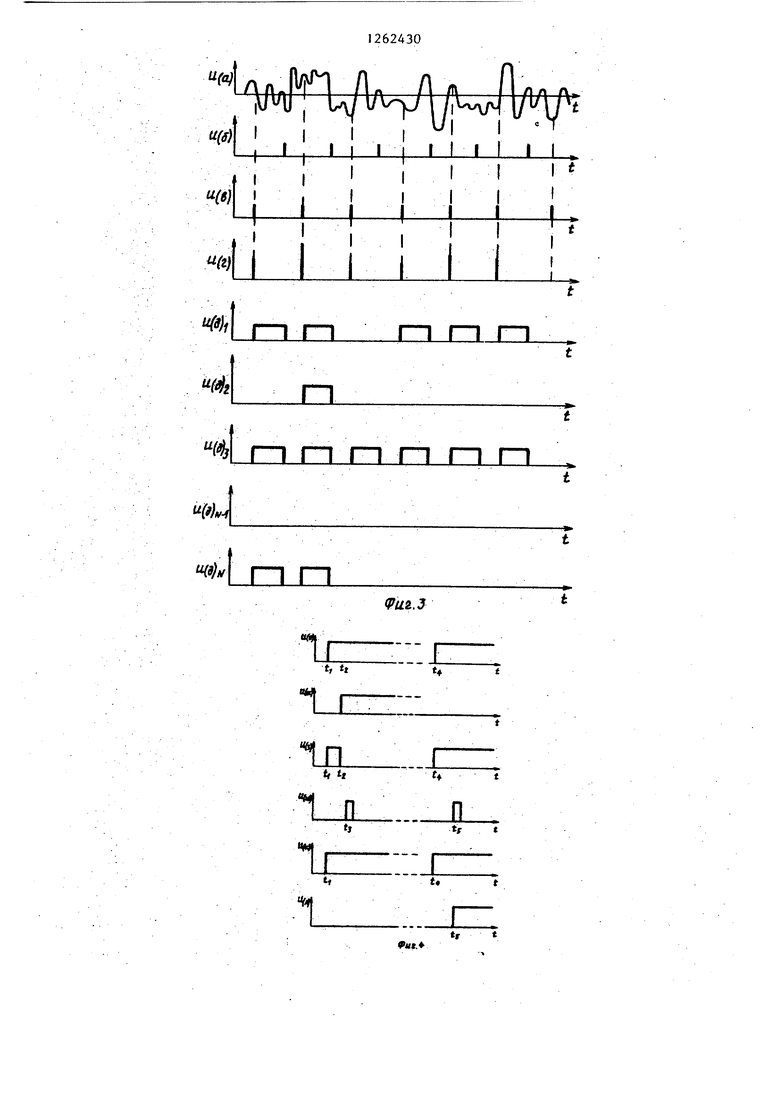

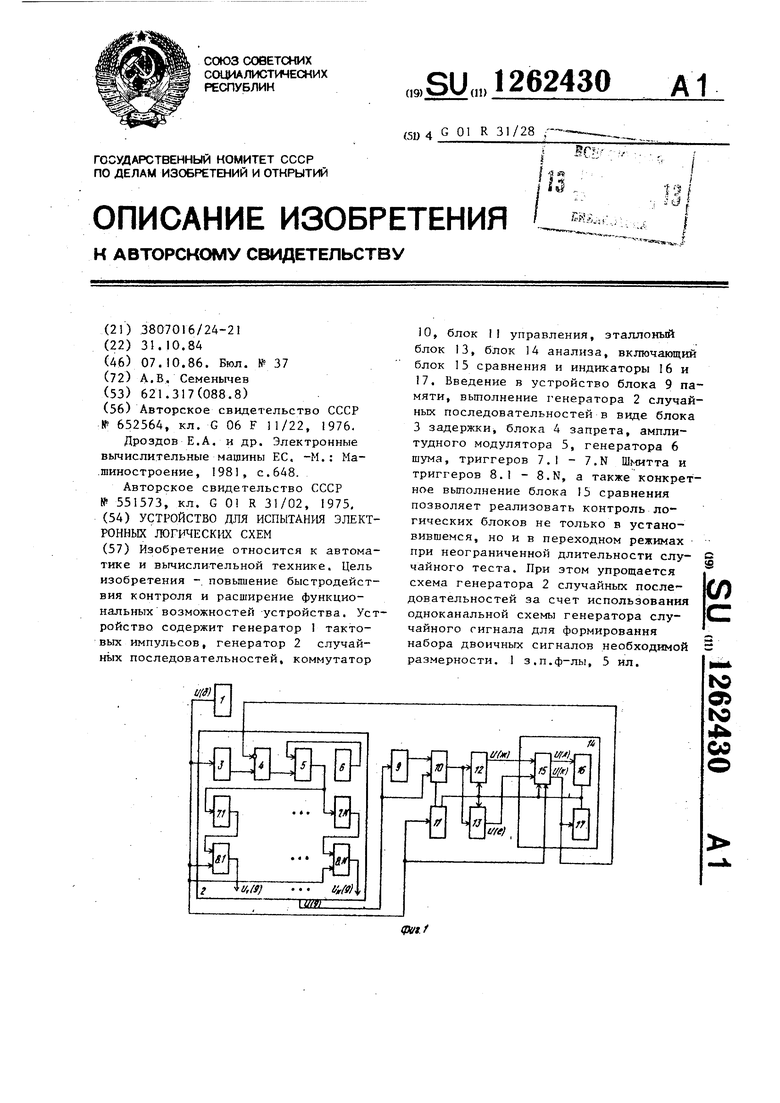

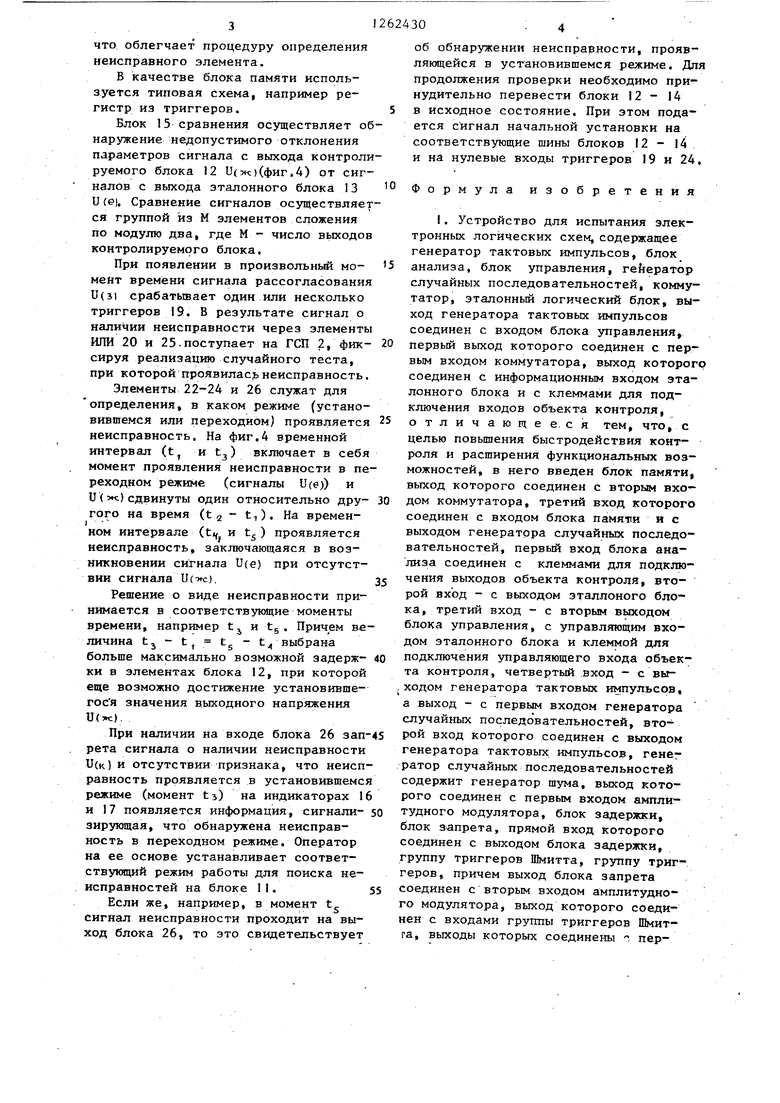

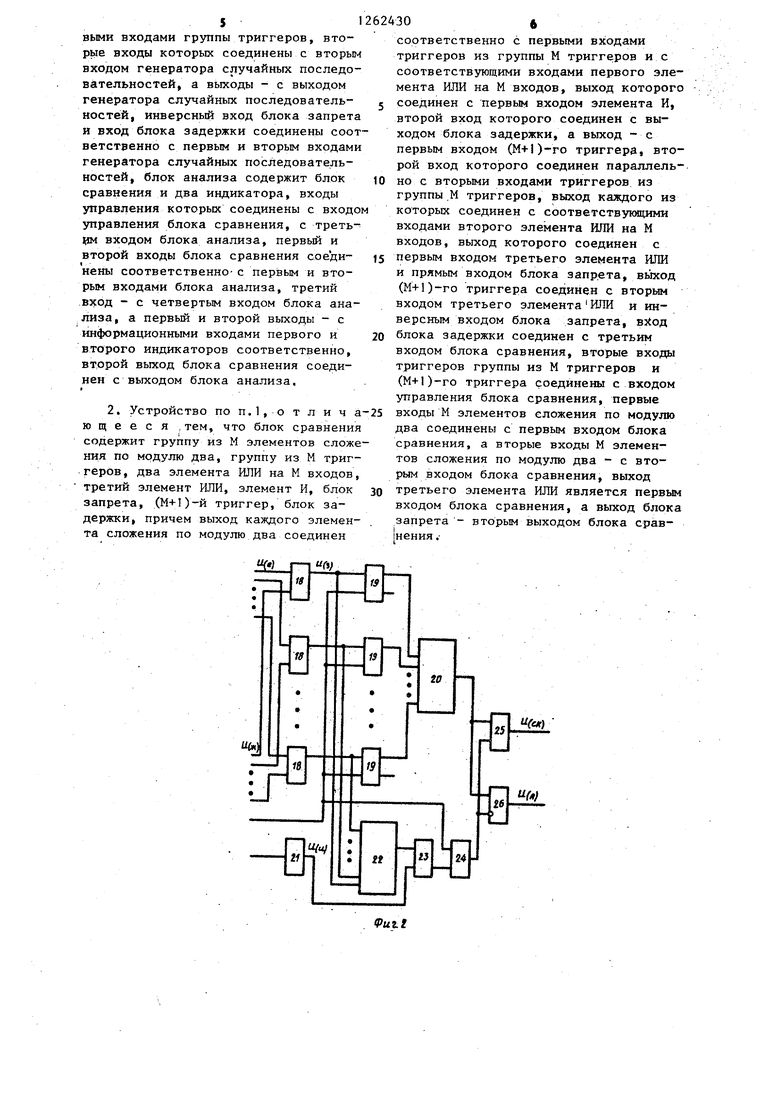

На фиг.1 представлена структурная схема устройства; на фиг,2 - функциональная схема блока сравнения; на фиг. 3 - идеализированные эпюры напряжений в обозначенных точках схемы по фиг.1; на фиг.4 - эпюры напряжений в обозначенных точках схемы по фиг.2; на фиг.5 - функциональная схема блока индикации

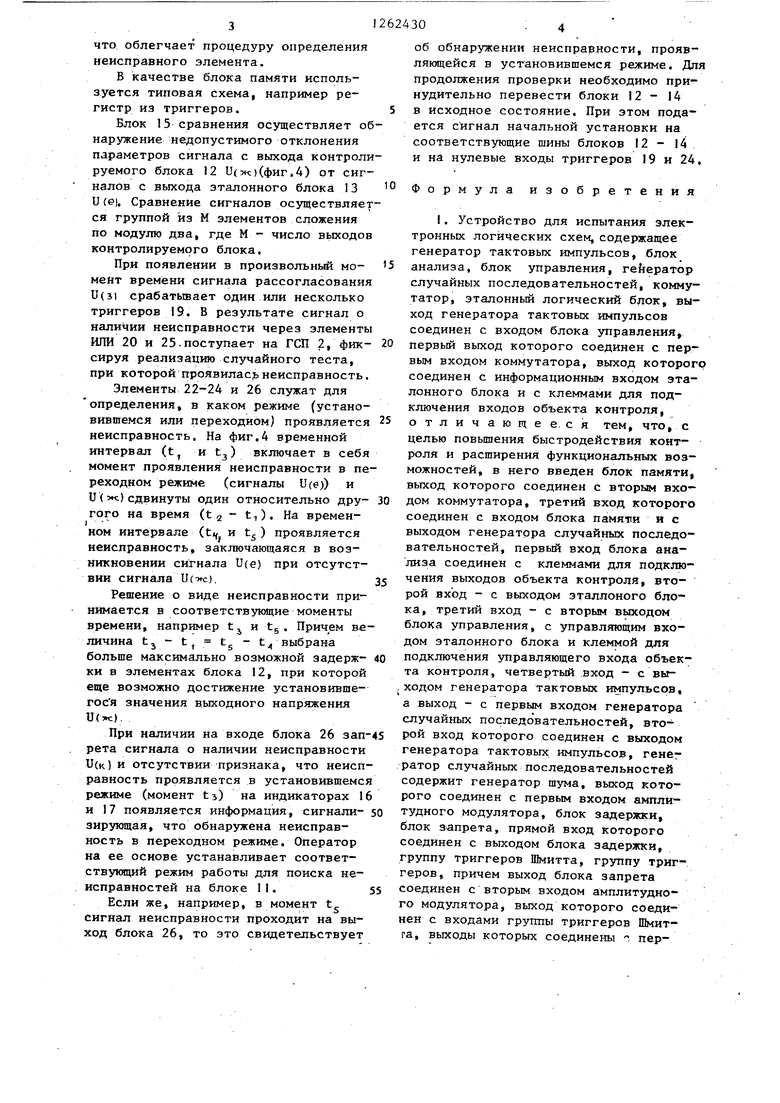

Устройство содержит генератор 1 тактовых импульсов (ГТИ), генератор .2 случайных последовательностей (ГСП), содержащий блок 3 задержки, блок 4 запрета, амплитудный модулятор 5 (AM), генератор 6 шума 7.1 7.N. ЦЫитта, триггеры 8.1-8.N, блок 9 памяти, коммутатор 10, блок 11 управления (БУ), контролируемый блок 12, эталонный блок 13, блок 14 анализа (БА), содержащий блок I5 сравнения и индикаторы 16 и 17.

Блок 15 сравнения содержит .группу элементов 18 сложения по модулю два, группу триггеров 19, элемент ИЛИ 20, блок 21 задержки, элемент ШШ 22, элемент И 23, триггер 24, элемент ИЛИ 25 и блок 26 запрета.

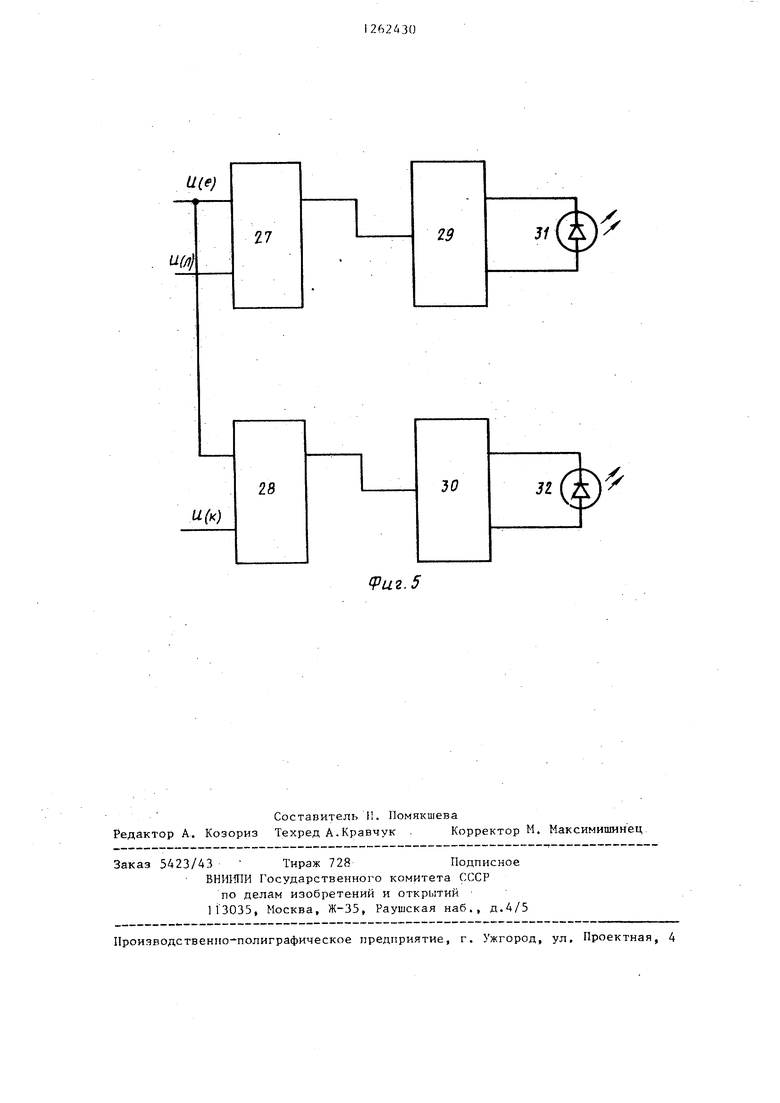

Индикаторы 16 и 17 содержат триггеры 27 и 28, усилители 29 и 30 мощности и элементы 32 и 32 индикации.

Устройство работает следующим образом.

Вырабатьшаемое ГШ 6 случайное напряжение поступает на AM 5, где используется для модуляции задержаннЕ)1х тактовых импульсов U(6), снимаемых с блока 3 задержки и проходящих через блок 4. Управление работой блока 4 осуществляется сигналом U(K), снимемым с выхода элемента ИЛИ 25.

624302

Средняя амплитуда импульсов UCr) равна

(Г) (M.C мин )/2, (1) где и, - напряжение срабатьгоания

5элемента из Группы 7.17.N с максимальным пороговым напряжением; мин напряжение срабатывания элемента из группы 7.1107.N с минимальным пороговым напряжением. При этом обеспечивается в случае равномерного закона распределения напряжения шума на входе AM равная 15 вероятность всех возможных реализаций теста.

Выходное напряжение АИ 5 представляет собой периодическую последовательность амплитудно-модулйрованнЫх 20 импульсов U(r) , которые поступают одновременно на все N входов группы триггеров 7 Шмитта, имеющих различные пороги срабатывания, равномерно распределенные в интервале (,,.2 и„„„ ). На фиг.З изображен случай, когда минимальным напряжением срабатьшания обладает третий триггер 7.3 иЬ1Итта, а наибольщим - (М-1)й триггер. Соответствующие напряжения обо30 значены как U(d1j и U(d)| ,

В зависимости от величины амплитуды импульса и(г) срабатьтает то или иное число триггеров Шмитта.

В каждом такте реализация теста 35 сугцествует на выходе группы триггеров 8.1-8. N в течение времени

Т .T-tj,a. Т «Т, . . С2) где Т - период следования тактовых

импульсов.; 40 7,„а задержка тактовых импуль. сов в блоке 3; 1 - длительность тактовых импульсов.

Импульсы и(6) используются для 45 установки триггеров 8 в исходное (нулевое) состояние. Длительность задержки в блоке 3 должна быть1 о а Дпя обеспечения высокого быстродействия необходимо выбиратьIjcia мини50 мально возможной величины.

Коммутатор 10 осуществляет подачу на входы блоков 12 и 13 одинаковых случайньгх реализаций теста с вьсхода генератора 2 или блока 9 памяти. При55 чем с выхода ГСП.2 сигнал снимается в режиме контроля. В режиме поиска неисправностей запомненная реализация теста поступает с выхода блока 9, что облегчает процедуру определения неисправного элемента. В качестве блока памяти используется типовая схема, например регистр из триггеров. Блок 15 сравнения осуществляет об наружение недопустимого отклонения параметров сигнала с выхода контроли руемого блока 12 и(ж;)(фиг.4) от сигналов с выхода эталонного блока 13 и (е). Сравнение сигналов осуществляет ся группой из М элементов сложения по модулю два, где М - число вькодов контролируемого блока. При появлении в произвольный момент времени сигнала рассогласования U(j| срабатьшает один или несколько триггеров 19. В результате сигнал о наличии неисправности через элементы ИЛИ 20 и 25.поступает на ГСП 2, фиксируя реализацию случайного теста, при которой проявилась неисправность. Элементы 22-24 и 26 служат для определения, в каком режиме (установившемся или переходном) проявляется неисправность. На фиг.4 временной интервал (t, и t) включает в себя момент проявления неисправности в пе реходном режиме (сигналы U(e)) и и (э««) сдвинуты один относительно другого на время (tа - ti)« На временt) проявляется ном интервале неисправность, заключающаяся в возникновении сигнала U(e) при отсутствии сигнала и(т«:). Решение о виде неисправности принимается в соответствующие моменты t, и tg. Причем ве времени, например личина tj - t, tg - t4 выбрана больще максимально возможной задержки в элементах блока 12, при которой еще возможно достижение установивщегося значения выходного напряжения При наличии на входе блока 26 зап рета сигнала о наличии неисправности U(K) и отсутствии признака, что неисп равность проявляется в установившемс режиме (момент ts) на индикаторах 1 и 17 появляется информация, сигнализирующая, что обнаружена неисправность в переходном режиме. Оператор на ее основе устанавливает соответствующий режим работы для поиска неисправностей на блоке II. Если же, например, в момент t сигнал неисправности проходит на выход блока 26, то это свидетельствует об обнаружении неисправности, проявляющейся в установившемся режиме. Для продолжения проверки необходимо принудительно перевести блоки 12 - 14 в исходное состояние. При этом подается сигнал начальной установки на соответствующие шины блоков 12 - 14 и на нулевые входы триггеров 19 и 24, Формула изобретения I. Устройство для испытания электронных логических схем, содержащее генератор тактовых импульсов, блок анализа, блок управления, гейератор случайных последовательностей, коммутатор, эталонный логический блок, выход генератора тактовых импульсов соединен с входом блока згправления, первый выход которого соединен с первым входом коммутатора, выход которого соединен с информационным входом эталонного блока и с клеммами для подключения входов объекта контроля, отличающее, ся тем, что, с целью повьш1ения быстродействия контроля и расширения функциональных возможностей, в него введен блок памяти, выход которого соединен с вторым входом коммутатора, третий вход которого соединен с входом блока памяти и с выходом генератора случайных последовательностей, первый вход блока анализа соединен с клеммами для подкдпочения выходов объекта контроля, второй вход - с выходом эталлоного блока, третий вход - с вторым выходом блока управления, с управляющим входом эталонного блока и клеммой для подключения управляющего входа объекта контроля, четвертый вход - с выходом генератора тактовых импульсов, а выход - с первым входом генератора случайных последовательностей, второй вход которого соединен с выходом генератора тактовых, импульсов, генег ратор случайных последовательностей содержит генератор шума, выход которого соединен с первым входом амплитудного модулятора, блок задержки, блок запрета, прямой вход которого соединен с выходом блока задержки, группу триггеров Шмитта, группу триггеров, причем выход блока запрета оединен с вторым входом амплитудно о модулятора, выход которого соедиен с входами группы триггеров Шмитга, выходы которых соединены . пер5выми входами группы триггеров, вторые входы которых соединены с вторым входом генератора случайных последовательностей, а выходы - с выходом генератора случайных последовательностей, инверсный вход блока запрета и вход блока задержки соединены соот ветственно с первым и вторым входами генератора случайных последовательностей, блок анализа содержит блок сравнения и два индикатора, входы управления которых соединены с входо управления блока сравнения, с третьум входом блока анализа, первьй и второй входы блока сравнения соединены соответственно-с первым и вторым входами блока анализа, третий вход - с четвертым входом блока анализа, а первый и второй выходы - с информационными входами первого и второго индикаторов соответственно, второй выход блока сравнения соединен с выходом блока анализа. 2. Устройство по П.1, о т л и ч ю щ е е с я ,тем, что блок сравнени содержит группу из М элементов слож ния по модулю два, группу из М триг геров, два элемента ИЛИ на М входов третий элемент ИЛИ, элемент И, блок запрета, (М+1)-й триггер, блок задержки, причем выход каждого элемен та сложения по модулю два соединен

fU 30 соответственно с первыми входами триггеров из группы М триггеров и с соответствующими входами первого элемента ИЛИ на М входов, выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом блока задержки, а выход - с первым входом (М+1)-го триггера второй вход которого соединен параллельно с вторыми входами триггеров из группы.М триггеров, выход каждого из которых соединен с соответствукицими входами второго элемента ИЛИ на М входов, выход которого соединен с первым входом третьего элемента ИЛИ и прямым входом блока запрета, выход (М+)-го триггера соединен с вторым входом третьего элементаИЛИ и инверсным входом блока запрета, вход блока задержки соединен с третьим входом блока сравнения, вторые входы триггеров группы из М триггеров и (М+1)-го триггера соединены с входом управления блока сравнения, первые входы М элементов сложения по модулю два соединены с первым входом блока сравнения, а вторые входы М элементов сложения по модулю два - с вторым входом блока сравнения, выход третьего элемента ИЛИ является первым входом блока сравнения, а выход блока запрета - вторым выходом блока сравнения ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для автоматического контроля генератора случайных чисел | 1982 |

|

SU1038942A1 |

| Устройство для контроля генератора случайных чисел | 1983 |

|

SU1087993A1 |

| Устройство для диагностирования логических схем | 1988 |

|

SU1684757A1 |

| Устройство для контроля многовыходных цифровых узлов | 1984 |

|

SU1176333A1 |

| Устройство для контроля генератора случайных чисел | 1983 |

|

SU1088011A1 |

| Устройство для функционального контроля интегральных схем | 1988 |

|

SU1737465A1 |

| Способ диагностирования состояния технического объекта с выбросами параметров и устройство для его осуществления | 1988 |

|

SU1573461A1 |

| Устройство для моделирования систем массового обслуживания | 1981 |

|

SU962970A1 |

| УСТРОЙСТВО ДЛЯ АНАЛИЗА РОДОВОЙ ДЕЯТЕЛЬНОСТИ | 1998 |

|

RU2130645C1 |

| Устройство для локализации неисправностей | 1988 |

|

SU1674128A1 |

Изобретение относится к автоматике и вьRиcлитeльнoй технике. Цель изобретения -. повышение быстродействия контроля и расширение функциональных возможностей устройства. Устройство содержит генератор 1 тактовых импульсов, генератор 2 случайнь1Х последовательностей, коммутатор 10, блок II управления, эталлоный блок 13, блок 14 анализа, включающий блок 15 сравнения и индикаторы 16 и 17. Введение в устройство блока 9 памяти, вьтолнение генератора 2 случайных последовательностей в виде блока 3 задержки, блока 4 запрета, амплитудного модулятора 5, генератора в шума, триггеров 7.1 - 7.N Шмитта и триггеров 8.1 - 8.N, а также конкретное вьтолнение блока 15 сравнения позволяет реализовать контроль логических блоков не только в установившемся, но и в переходном режимах при неограниченной длительности слу чайного теста. При этом упрощается схема генератора 2 случайных послвдовательностей за счет использования одноканальной схемы генератора случайного сигнала для формирования набора двоичных сигналов необходимой размерности. 1 з.п.ф-лы, 5 ил. to Р ю и 00

41 I I I

П

Щ rn m ГП n ГП n

(/

M n n

1c

TJ:

n

V i|

TJL

1

Pti2..3

| Фрезерный станок для обработки вкладышей, например, для спецукупорки | 1940 |

|

SU65256A1 |

| Дроздов Е.А | |||

| и др | |||

| Электронные вычислительные машины ЕС | |||

| -М.: Ма.шиностроение, 1981, с.648 | |||

| Устройство для испытания логических блоков | 1975 |

|

SU551573A1 |

| Способ очистки нефти и нефтяных продуктов и уничтожения их флюоресценции | 1921 |

|

SU31A1 |

Авторы

Даты

1986-10-07—Публикация

1984-10-31—Подача