(54) УСТРОЙСТВО ДЛЯ ИСПЫТАНИЯ ЛОГИЧЕСКИХ БЛОКОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для автоматического поиска дефектов в логических блоках | 1982 |

|

SU1108451A1 |

| УСТРОЙСТВО АУТЕНТИФИКАЦИИ ПРОГРАММНЫХ МОДУЛЕЙ | 1998 |

|

RU2146834C1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1383370A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для контроля логических блоков | 1986 |

|

SU1372324A1 |

| Устройство для диагностики логических блоков | 1988 |

|

SU1672452A1 |

1

Изобретение относится к области автоматики и вычислительной техники, а именно к испытательной аппаратуре для вычислительной техники и может быть использовано в аппаратуре проверки и поиска неисправносте в ячейках и блоках, построенных на интегральных схемах.

Известно устройство, состоящее из генератора тактов, выход которого соединен со входом регистра строба и через последовательно соединенные блоки задержки со входами соответственно:буфера, шагового генератора и блока сравнения, регистра строба, вход которого соединен с выходом генератора тактов, а выход со входом буфера и входом регистра случайных кодов, генератора случайных кодов, вход которого соединен с выходом регистра строба, а выход со входом буфера, аходы которого соединены с выходами регистра строба, генератора случайных кодов и через блок задержки с выходом генератора тактов, а выходы со входами эталонного логического блока и через шаговый генератор со входами проверяемого логического блока, входы которого соединены с выходами буфера, а выходы, со входами устройства сравнения, шагового генератора, входы которого соединены с выходами буфера и через два последовательно соединенных блока задержки с выходом генератора тактов а выходы со входами проверяемого логического блока,входы которого соединены с выходами шагового генератора, а выходы через двоичный дискриминатор со входами блока сравнения, устройства сравнения, входы которого соединены с выходами эталонного: логического блока и через двоичный дискриминатор с выходами проверяемого логического блока ГЛ ,.

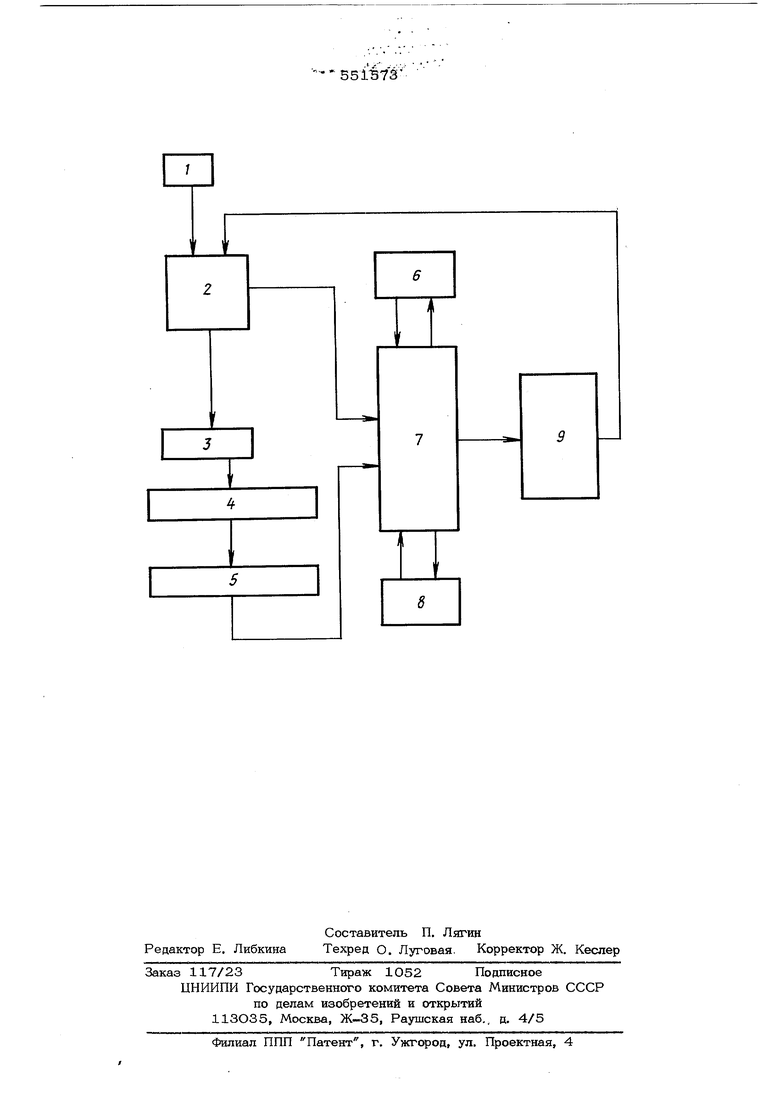

Недостатком этого устройства является то, что выходы эталонного логического блока соединены с выходами генератора случайных кодов через буфер, а входы проверяемого логического блока соединены с выходами генератора случайных кодов через шаговый генератор и буфер. Поэтому невозможно перед началом проверки устанавливать проверяемый и эталонный блоки, содержашие схемы с элементами памяти, в идентичное состояние. Кроме того, в процессе проверки на входах этих блоков могут возникать запрещенные комбинации. В связи с этим на данном устройстве можно проверять только логические блоки, не содержащие схем с элементами памяти. Все это значительно снижает функциональные возможности известного устройства. Цель изобретения - расширение функциональных возможностей устройства. Это достигается тем, что в устройство для испытаний логических блоков, содержащее генератор тактов, генератор случайных кодов, эталонный и логический блок и блок сравнения, введены блок управления, дешифратор, П - разрядный сумматор по той 2 и коммутатор, при этом блок управления включен между выходами генератора тактов и блока сравнения и входами коммутатора и генератора случайных кодов, между выходом которого и вторым входом коммутатора вклю чены последовательно соединенные дешифратор и Т) -разрядный сумматор по тоб 2 , а выходы коммутатора соединены соответствен но с блоком сравнения и входными зажимам эталонного и испытуемого логического блока к выходным зажимам которых подключены тре тий и четвертый входы коммутатора. На чертеже представлена блок-схема устройства для испытаний логических блоков Устройство состоит из генератора тактов 1 блока 2 управления, генератора 3 случайных кодов, дешифратора 4, -Г) -разрядного сумматора 5 по mod 2, эталонного логического бло ка 6, коммутатора 7, проверяемого логичес кого блока 8 и блока 9 сравнения. Соответствующие выходы блока 2 управления соединены со входами генератора 3 и соответствующими входами коммутатора 7. Соответствующие входы блока 2 управления соединены с выходом генератора 1 и выходами блока 9 сравнения. Выходы генератора 3 соединены со входами дешифратора 4. Выходы дешифратора 4 соединены со входами И-разрядного сумматора 5 поППОЗЗ. Соот ветствующие выходы коммутатора 7 соединены со входами блока 9 сравнения, эталон ного логического блока 6 и проверяемого логического блока 8, Соответствующие входы коммутатора 7 соединены с выходами И-разрядного сумматора 5 1ПОа 2 ,эталонного логического блока 6, проверяемого логического блока 8, а также соответствующими выходами блока 2, Работает устройство следующим образом. Перед началом проверки коммутатор 7 в соответствии с предварительной установкой блока 2, коммутирует внешние контакты проверяемого и эталонного логических блоКОВ 8 и 6 или на вход блока 9 (выходные контакты), или на выход Т| -разрядного cjrMMaTOpa по ГЛОЗ 2 .(входные контакты). Проверка начинается с того, что проверяемый и эталонный логические блоки устанавливаются в идентичное состояние, для чего на входы этих логических блоков подаются коды бегущей 1 и бегущего О. При проверке частота с генератора 1 через блок 2 вырабатывает очередной случайный код на генераторе 3, который возбуждает соответствующую шину дешифратора 4 и перебрасывает соответствующий разряд Я -разрядного сумматора 5 по И1о32 в противоположное состояние. Образованный таким образом случайный код через коммутатор 7 поступает на входы проверяемого и эталонного логических блоков 8 и 6, выходы с которых через коммутатор 7 поступают на устройство сравнения 9. При неравенстве реакции проверяемого и эталонного логических блоков 8 и 6 сигнал неравенства через устройство управления 2 прерывает частоту, поступающую на генератор 3, и все устройство находится в статическом состоянии. На индикации блока 9 видны номера выходных контактов, давших разную реакцию. Далее при помощи специальных щупов, объединенных схемой сравнения, проверяют потенциалы в идентичных точках проверяемого и эталонного логических блоков 8 и 6, двигаясь от несовпавших выходных контактов. Неисправным элементом считается тот, потенциалы на входах которого равны, а выходы разные. При устранении неисправности блок 2 управления пропустит частоту на вход генератора 3 и проверка будет продолжена. ЕСЛИ вместо генератора случайных кодов используется генератор псевдо-случайных кодов, то длину генератора выбирают в зависимости от необходимого периода повторения псев до-случайных кодов, а на дешифратор заводят тольков К разрядов данного генератора. К выбирается из соотношения П 2 где И - общее количество внешних контактов проверяемого (эталонного) логического блока. Полнота проверки на предлагаемом устройстве оценивается из следующих соображений. Блоки (ячейки), выполненные на интегральных схемах с количеством внешних контактов более 200, как правило, состоят из взаимонезависимых логических схем (исключая цепи нуления) с количеством внешних входных контактов не более 20. При этом регистр, состоящий из 2 разрядов, каждый из которых имеет Q входных контактов, необходимо рассматривать как устройство, состоящее изг взаимонезависимых схем, так как для проверки регистра не нужен полный перебор кодов на всех его входных контактах, равный 2 а достаточно, чтобы полный набор был на входных контактах каж дого из 2 разрядов. Запрещенных комбинаций на входах этих схем не возникает из-за условия: каждый последующий код отличается от предыдущего только на один разряд. Запрещенными (для трштеров серии логика явл5потся комбинации, при которых оба активных потенциала (на единичном и нулевом входах) одновременно сменяются на пассивны и т риггер может стать в любое состояние. Комбинации, при которых на обоих входах активные потенциалы не являются запрещенными, так как при правильной работе выходы триггеров проверяемого и эталонного логических блоков определены и идентичны, а очередной проверочный код оба потенциала одновременно сменить на пассивные не может. Вероятность проверки любой взаимонезависимой логической схемы даже полным пе ребором (для проверки обычно используется часть кодов полного перебара) при 4 мин про верке на частоте 1МГц, количестве входных контактов взаимонезависимой схемы равном 15 и общем количестве внешних контактов блока (ячейки) 360 равна: -0-) о,998. а- п / где X - количество входных контактов взаим независимой логической схемы:, Tl - общее число входных контактов; N - количество тактов за время проверк Использование этого устройства позволит повысить функциональные возможности и эффективность использования испытательной аппаратуры при проверках логических блоков на больших частотах и имеющих неограниченное количество внешних контактов. При этом снимаются ограничения на содержание в проверяемых блоках схем с элементами памяти. Следует отметить также, что вероятность проверки логических блоков очень велика, а необходимость в составлении проверочных тестов отсутствует. Формула изобретения Устройство для испытания логических блоков, содержащее генератор тактов, генератор случайных кодов, эталонный логический блок и блок сравнения, о т л и ч а ю- щ е е с я тем, что, с целью расширения функциональных возможностей устройства, в него введены блок управления, дешифратор, -fl -разрядный сумматор по mod 2 и коммутатор , при этом блок управления включен между выходами генератора тактов и блока сравнения и входами коммутатора и генератора случайных кодов между выходом которог-о и вторым входом коммутатора включены последовательно соединенные дешифратор и И -разрядный сумматор по mod Я i выходы коммутатора, соединены соответственно с блоком сравнения и входными зажимами эталонного и испытуемого логического блока, к выходным зажимам которых подключены третий и четвертый входы коммутатора. Источники информации, принятые во внимание при экспертизе: 1. Патент США № 36146О8,кл. 32473, 1971 (прототип).

Г

Авторы

Даты

1977-03-25—Публикация

1975-12-15—Подача