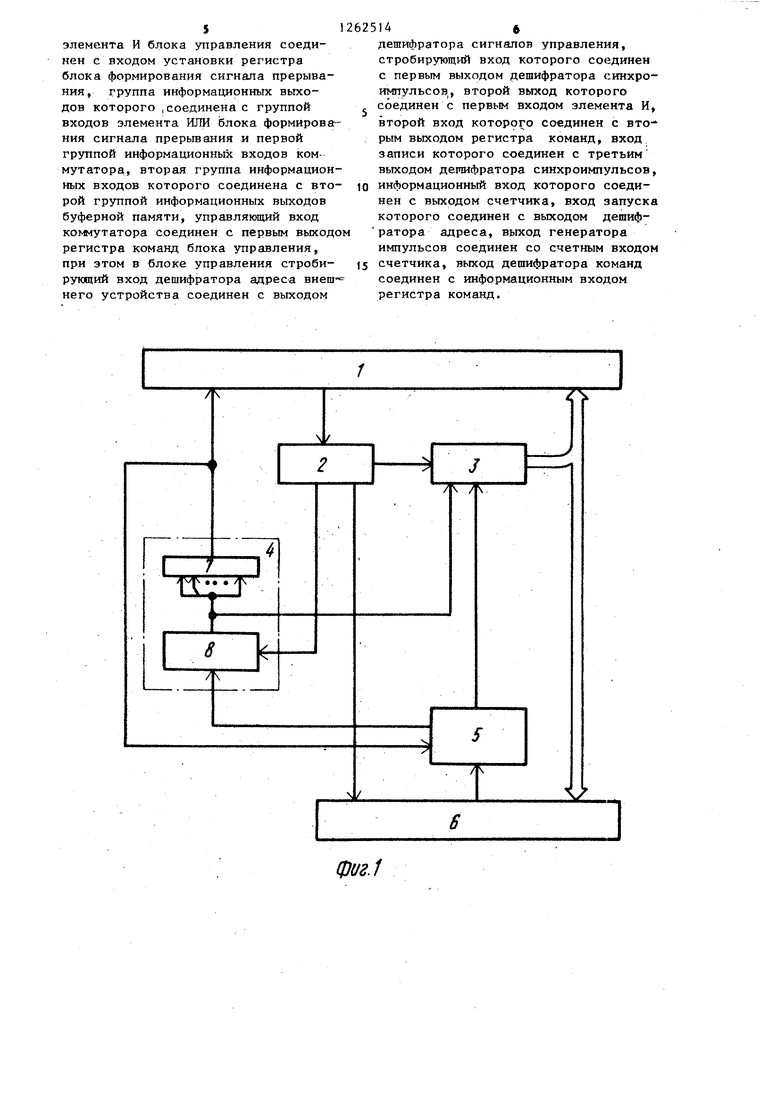

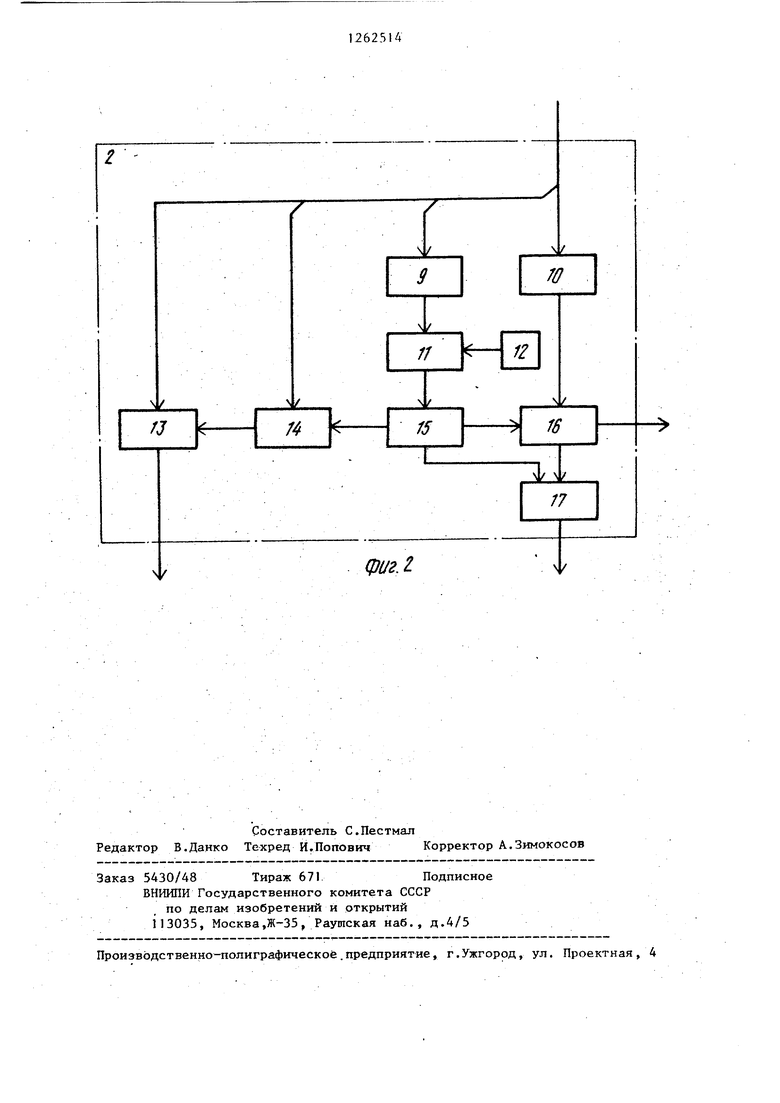

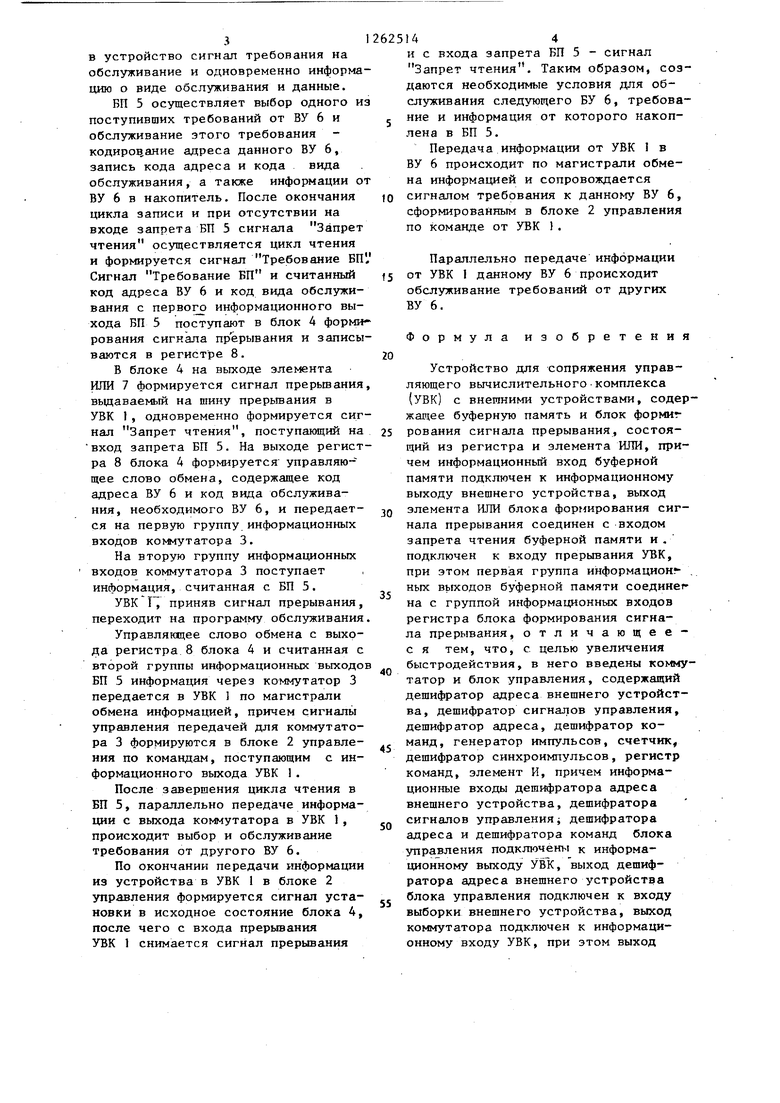

I Изобретение относится к вычисли тельной техники и может применяться при построении вычислительных систe 1 и, в частности, для управления кo Iмyтaциeй в электронных телеграфных станциях. Целью изобретения является увеличение быстродействия при. обмене информацией между управляющим вычис лительным комплексом и внешними уст ройст-вами путем одновременного обслуживания нескольких внешних устройств . На фиг.1 представлена структурна схема устройстваJ на фиг.2 - схема блока управления. Устройство содержит управляющий вычислительный комплекс (УВК) 1, блок 2 управления, коммутатор 3, блок 4 формирования сигнала прерыва ния, буферную память (БП) 5, внешнее устройство (ВУ) 6. Блок 4 включает элемент КПИ 7 и регистр 8. Блок 2 управления содержит дешиф ратор 9 адреса, дешифратор 10 команд, счетчик 11, генератор 12 импульсов, дешифратор 13 а дреса внешнего устройства, дешифратор 14 сигналов управления, дешифратор 15 синхроимпульсов, регистр 16 команд элемент И 17. Ялок 2 управления предназначен для формирования сигналов управлени определяющих передачу информации и коммутатора в УВК 1; выставления си налов требования в ВУ 6; определения конца обмена информащ ей и фор мирования сигнала сброса при этом для блока4. Коммутатор 3 предназначен для переключения потоков информации от блока 4 или от БП 5 в УВК 1 . Блок 4 формирования сигнала пре рывания предназначен для формирова сигнала прерывания и выставления его на шину прерывания в УВК 1 и одновременного формирования сигнала Запрет чтения, передаваемого НП 5, а также для формирования управляющего слова обмена , вьщаваемо го в коммутатор 3 при поступлении от БП 5 сигнала Требование БП кодов адреса ВУ 6 и вида обслужива ния, необходимого ВУ.6. БП 5 предназначена для обслужив ния требований от БУ 6. Работа блока 2 управления происходит следующим образом. 142. По входу блока 2 управления из УВК одновремен1то поступают адрес устройства, сопряжения, адрес внеш-. него устройства (при обмене информацией в .направлении-УВК 1 - ВУ 6), сигналы управления. Лдрес, устройства сопряжения дешифрируется в депшфраторе 9, на выходе которого появляется сигнал пуска для счетчика II. На счетный вход счетчика II поступают тактоBF.iie и№1ульсы от генератора 12 импульсов. Определенные соотояния счетчика II дешифрируются дешифратором 15синхроимпульсов, осухцествляя таким образом распределение во времени работы блока 2 управления. Адрес ВУ поступает на дешифратор 3, а сигналы управления - на дешифратор 14 сигналов управления и дешифратор 10 команд. Дешифратор 14 сигналов управления на. определенном шаге дешифратора 15 синхроимпульсов вырабатывает сигнал управления для дешифратора 13 адреса ВУ. На выходе дешифратора 13 появляется сигнал требования, передаваем,й в соответствующее поступившему адресу ВУ 6. Совокупность сигналов управления-, образующих команду от УВК 1, дешифрируется в дешифраторе 10 команд. Дешифрированная команда на определенном uiare дешифратора 15 синхроимпульсов записывается в регистр 16 команд. Соответствующие команде сигналы с выхода регистра 16 команд одновременно передаются на входы элемента И 17 и коммутатор 3. На определенном шаге дешифратора 15 синхроимпульсов (в конце обмена УВК 1 - устройство сопряжения) на входах элемента И 17 происходит совпадение сигналов и на выходе формируется сигнал установки, передаваемьп1 в блок 4 формирования сигнала прерывания. Устройство работает след:утощим образом. Исходным состоянием устройства является состояние после включения питания или после завершения обмена информацией между устройством и УВК I, а также в режиме ожидания при отсутствии в БП 5 очередного сообщения, когда в цепях внешних; связей с УВК 1 и ВУ 6 отсутствуют сигналы. При необходимости связи с УВК 1 ВУ 6 по информационному входу выдает 3 в устройство сигнал требования на обслуживание и одновременно информа цию о виде обслуживания и данные. БП 5 осуществляет выбор одного и поступивших требований от ВУ 6 и обслуживание этого требования кодирование адреса данного ВУ 6, запись кода адреса и кода вида обслуживания, а также информации о ВУ 6 в накопитель. После окончания цикла записи и при отсутствии на входе запрета БП 5 сигнала Запрет чтения осуществляется цикл чтения и формируется сигнал Требование БП Сигнал Требование БП и считанный код адреса ВУ 6 и код вида обслуживания с первогю информационного выхода БП 5 поступают в блок 4 форми рования сигнала прерывания и записы ваются в регистре 8. В блоке 4 на выходе элемента ИЛИ 7 формируется сигнал прерьшания выдаваемый на шину прерьшания в УВК 1, одновременно формируется сиг нал Запрет чтения, поступающий на вход запрета БП 5. На выходе регист ра 8 блока 4 формируется управляю- щее слово обмена, содержащее код адреса ВУ 6 и код вида обслуживания, необходимого ВУ 6, и передается на первую группу.информационных входов коммутатора 3. На вторую группу информационных входов коммутатора 3 поступает информация, считанная с БП 5. УВК }, приняв сигнал прерывания, переходит на программу обслуживания Управляющее слово обмена с выхода регистра В блока 4 и считанная с второй группы информационных выходо БП 5 информация через коммутатор 3 передается в УВК 1 по магистрали обмена информацией, причем сигналь управления передачей для коммутатора 3 формируются в блоке 2 управления по командам, поступающим с информационного выхода УВК 1. После завершения цикла чтения в БП 5, параллельно передаче информации с выхода коммутатора в УВК 1, происходит выбор и обслуживание требования от другого ВУ 6. По окончании передачи информации из устройства в УВК 1 в блоке 2 управления формируется сигнал установки в исходное состояние блока 4, после чего с входа прерывания УВК 1 снимается сигнал прерывания 144 и с входа запрета БП 5 - сигнал Запрет чтения. Таким образом, создаются необходимые условия для обслуживания следующего БУ 6, требование и информация от которого накоплена в БП 5. Передача информации от УВК 1 в ВУ 6 происходит по магистрали обмена информацией и сопровождается сигналом требования к данному ВУ 6, сформироваиным в блоке 2 управления по команде от 1 . Параллельно передаче информации от УВК I данному ВУ 6 происходит обслуживание требований от других ВУ 6. Формула изобретения Устройство для сопряжения управляющего вычислительногокомплекса (УВК) с внеганими устройствами, содержагдее буферную память и блок формиг рования сигнала прерывания, состоящий из регистра и элемента ИЛИ, причем информационный вход буферной памяти подключен к информационному выходу внешнего устройства, выход элемента ИЛИ блока формирования сигнала прерывания соединен с входом запрета чтения буферной памяти и. подключен к входу прерьшания УВК, при этом первая группа информацион ных выходов буферной памяти соединег на с группой информационных входов регистра блока формирования сигнала прерывания, отличающеес я тем, что, с целью увеличения быстродействия, в него введены коммутатор и блок управления, содержащий дешифратор адреса внешнего устройства, дешифратор сигналов управления, дешифратор адреса, дешифратор команд, генератор импульсов, счетчик, дешифратор синхроимпульсов, регистр команд, элемент И, причем информационные входы дешифратора адреса внешнего устройства, дешифратора сигналов управления дешифратора адреса и дешифратора команд блока управления подключены к информационному выходу УВК, выход дешифратора адреса внешнего устройства блока управления подключен к входу выборки внешнего устройства, выход коммутатора подключен к информационному входу УВК, при этом выход элемента И блока управления соединен с входом установки регистра блока формирования сигнала прерывания, группа информационных выходов которого , соединена с группой входов элемента ИЛИ блока формирова ния сигнала прерывания и первой группой информационных входов коммутатора, вторая группа информацион ных входов которого соединена с вто рой грзшпой информационных выходов буферной памяти, управляющий вход коммутатора соединен с первым выход регистра команд блока управления, при этом в блоке управления стробирующий вход дешифратора адреса внеш него устройства соединен с выходом 1А6 дешифратора сигналов управления, стробирующий вход которого соединен с первым выходом дешифратора синхроимпульсов,, второй выход которого соединен с первым входом элемента И, второй вход которрго соединен с вто рым выходом регистра команд, вход записи которого соединен с третьим выходом депшфратора синхроимпульсов, информационный вход которого соединен с выходом счетчика, вход запуска которого соединен с выходом дешифратора адреса, выход генератора импульсов соединен со счетным входом счетчика, выход депгафратора команд соединен с информационным входом регистра команд.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с абонентом | 1986 |

|

SU1334154A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1985 |

|

SU1288709A1 |

| Устройство для сопряжения канала ввода-вывода с абонентом | 1989 |

|

SU1695312A1 |

| Устройство для сопряжения ЭВМ с внешним устройством | 1986 |

|

SU1401470A1 |

| Селекторный канал | 1982 |

|

SU1053096A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1985 |

|

SU1307462A1 |

| Селекторный канал | 1983 |

|

SU1160427A1 |

| Устройство для сопряжения ЭВМ с магистралью ввода-вывода периферийных устройств | 1983 |

|

SU1160426A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЯ | 1994 |

|

RU2108623C1 |

| Устройство для ввода-вывода информации | 1985 |

|

SU1325489A1 |

Изобретение относится к вычислительной технике и может применяться при построении вычислительных систем, в частности для управления коммутацией электронных телеграфных станциях. Основной задачей устройства является повышение быстродействия при обмене информацией между управляющим вычислительным комплексом и внешними устройствами за счет одновременного обслуживания нескольких внешних устройств. Устройство содержит блок управления, коммутатор, буферную память и блок формирования сигнала прерьтания. 2 нп.

f

747ч

;.1

8

фиг.1

7

| Устройство для сопряжения цифровой вычислительной машины с линиями связи | 1979 |

|

SU864276A1 |

| Авторское свидетельство СССР 758123, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-07—Публикация

1985-01-03—Подача