4

Изобретение относится к вычислительной технике и предназначено для сопряжения внешних устройств с ЭВМ.

Цель изобретения - повышение производительности за счет обеспечения двустороннего обмена информацией и увеличения объема буферной памяти.

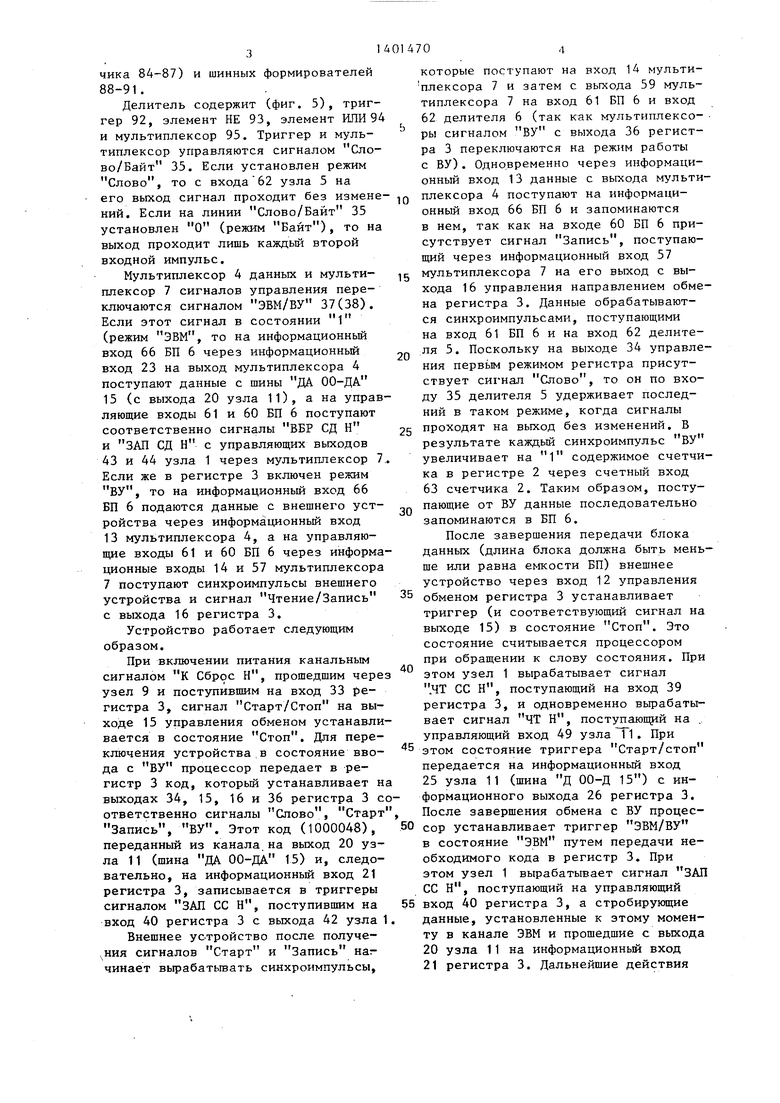

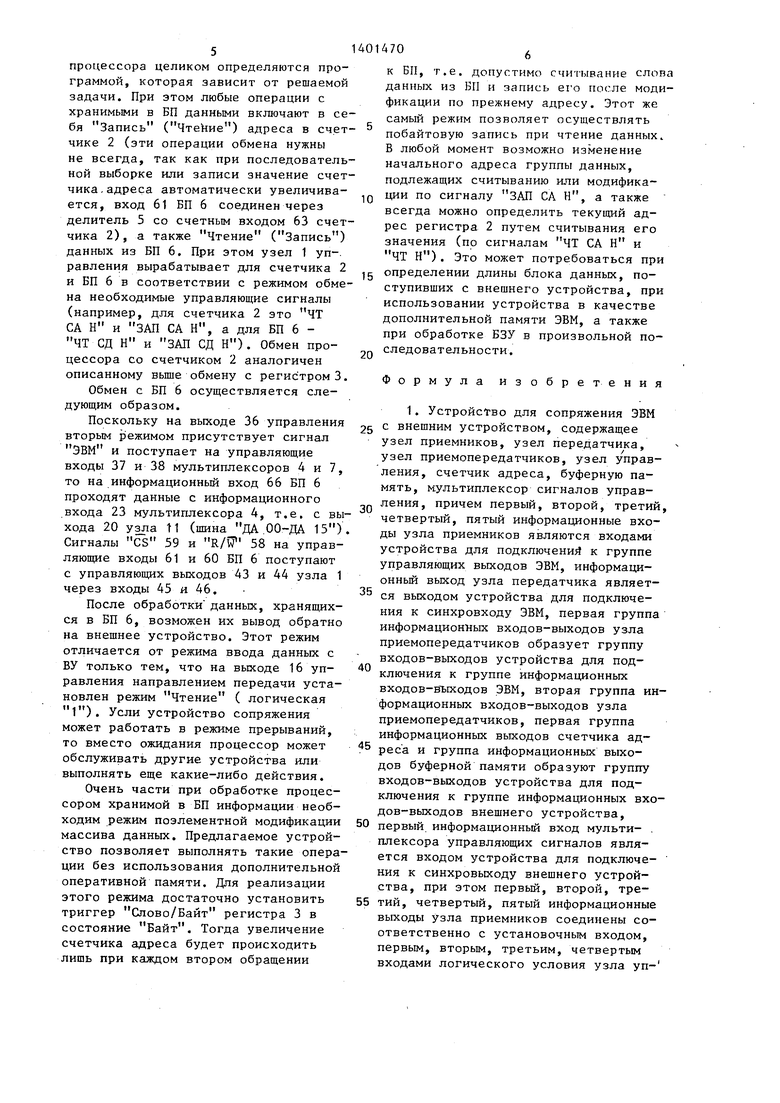

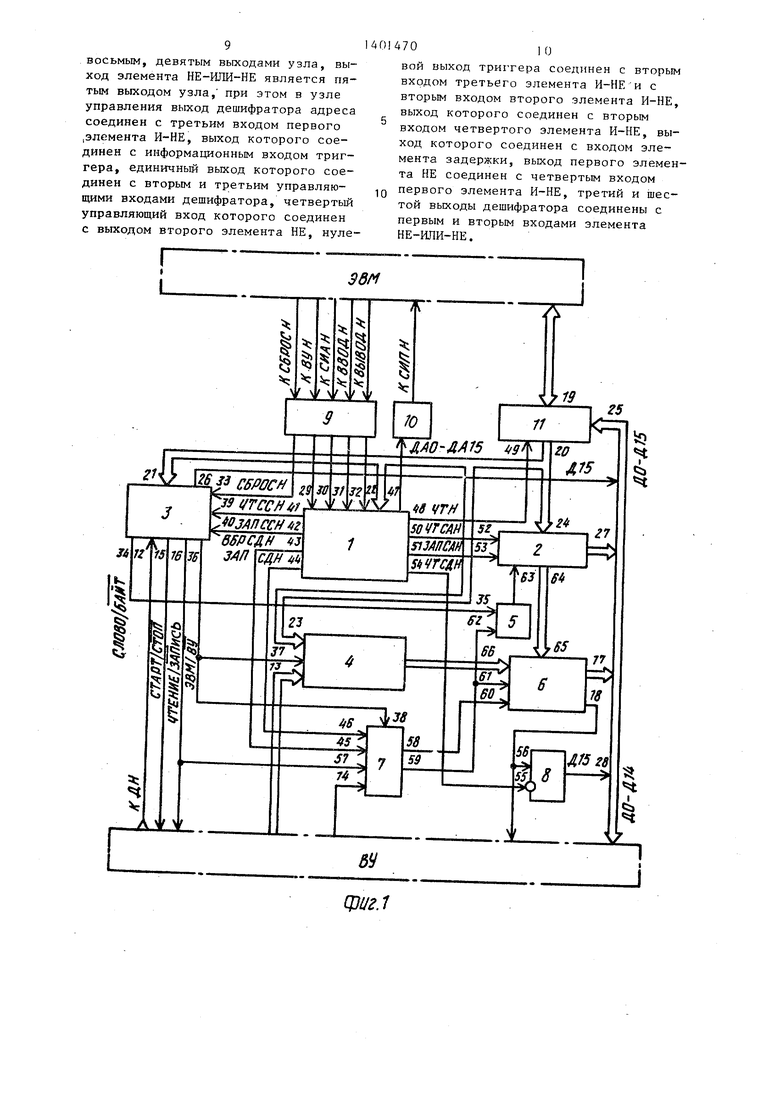

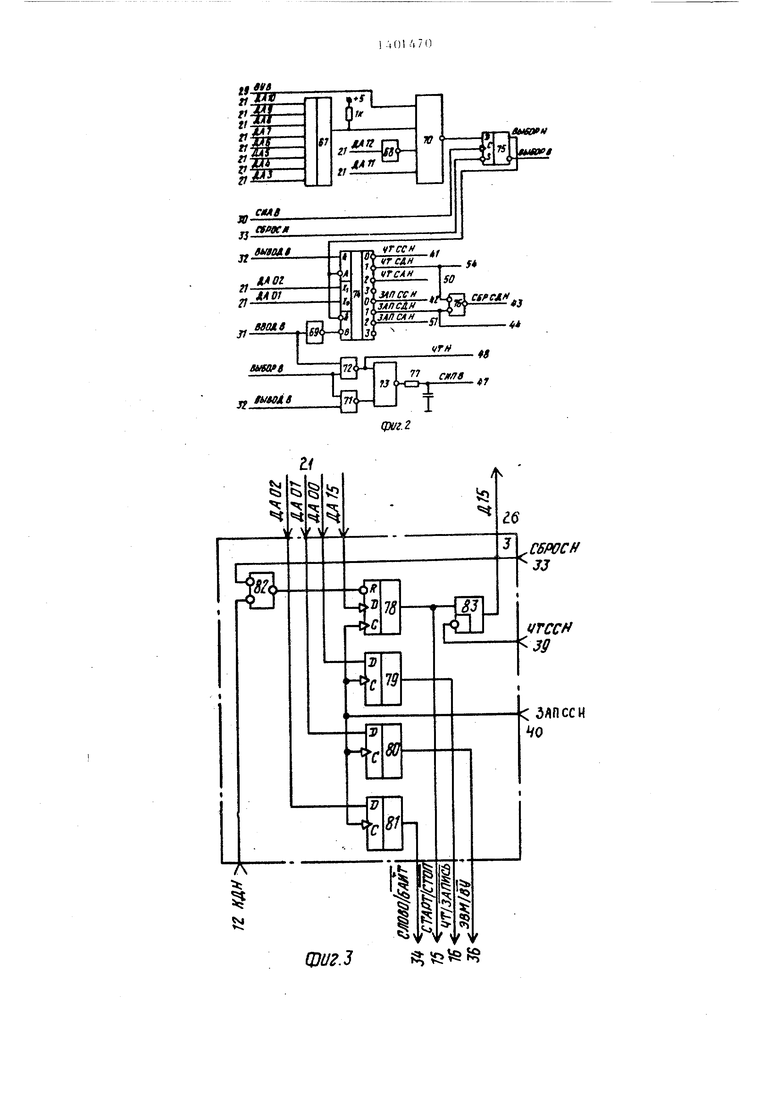

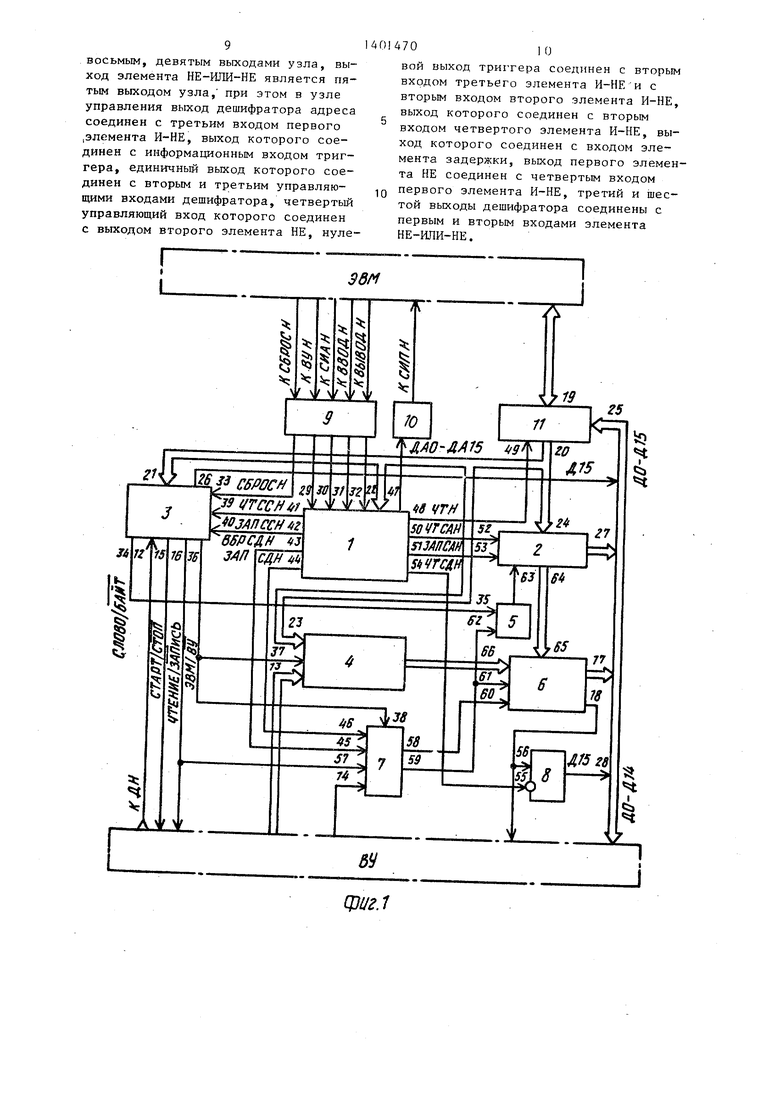

На фиг. 1 представлена блок-схема устройства; на фиг,, 2 - узел управ- ления; на фиг. 3 - регистр состояния на фиг. 4 - схема счетчика адреса; на фиг, 5 - схема делителя.

Устройство сопряжения содержит (фиг, 1) узел 1 управления, счетчик

2адреса, регистр 3 состояния, мультиплексор 4 данных, делитель 5, буферную память (БП) 6, мультиплексор

7 сигналов управления, шинный формирователь 8, узел 9 приемников, узел 10 передатчика, узел 11 приемопередатчиков, входы и выходы 12-66 узлов устройства.

Узел 1 управления содержит (фиг, 2). дешифратор 67 адреса, эле- менты НЕ 68 и 69, элементы И-НЕ 70-73 дешифратор 74, триггер 75, элемент НЕ-ШШ-НЕ 76, элемент 77 задержки.

Узел управления предоставляет процессору возможность обмена с устройством для сопряжения при помощи лишь трех слов в адресном пространстве ОЗУ ЭВМ, Это слово состояния (СС), слово данных (СД) и слово адреса (СА При обращении к первому слову процессор может обмениваться с регистром

3состояния, при обращении к второму - с БП 6, а при обращении к третьму - с регистром 2 (фиг, 1),

.Узел управления работает следующим образом,

При появлении присвоенного устройству адреса на линиях ДА 12 (фиг, 2) и логической единицы на линии ВУ В 29 на выходе элемента И-НЕ 70 появляется низкий уровень, который канальным сигналом СИА В 30 заносится в триггер 75, Появление 1 на нулевом выходе триггера 75 (сигнал Выбор в) говорит об обращении процессора к устройству. Выбор конкретного слова (СС, СД, СА) определяется состояниями линий ДА 01, ДА 02, которые управляют дешифратором. Появление сигнала Выбор Б на входах элементов И-НЕ 71 и 72 раз решает прохождение сигналов Ввод В 31 и Вывод в 32 и, следовательно, появление сигнала СИП В 47, а появ

Q

c

,.

5

5

45 50 5

0

ление сигнала Выбор Н на входах дешифратора 74 разрешает его работу, В зависимости от того, осуществляет ли процессор цикл Чтение или Запись, на входы дешифратора 74 и элементов И-НЕ 72 и 71 поступает либо сигнал Ввод В 31 либо Вывод В 32. В любом случае с некоторой задержкой появляется сигнал СИП В 47, который поступает в узел 10, Если был.цикл Чтение, то вырабатывается сигнал ЧТ Н 48, который поступает на управляющий вход 49 узла 11 и переводит его в состояние передачи, а также в зависимости от кода на линиях ДА 01 и ДА 02 вырабатывается один из сигналов ЧТ ССН 41, ЧТ СДН 54 или ЧТ САН 50, управляющих передачей данных соответствующего слова в процессор. Аналогично, при выполнении процессором цикла Запись появляется один из сигналов ЗАП ССН 42, ЗАП СД Н или ЗАП СА . При обращении процессора к слову данных в любом цикле вырабатывается сигнал ВБР СД Н 43, который может поступать через мультиплексор 7 в ВП 6,

Регистр 3 состояния (фиг, 3) содержит четыре регистра Старт/Стоп 78, Чтение/Запись 79, ЗВМ/ВУ 80, Слово-Байт 81, элемент НЕ-ШШ-НЕ 82 и шинный формирователь 83,

При обращении процессора к слову состояния возможна запись необходимого кода в триггеры регистра состояния сигналом ЗАП ССН 40, а также чтение состояния триггера 78 по сигналу ЧТ СС Н 39,.По этому сигналу шинный формирователь-83 передает на линию Д 15 (26) состояние триггера 78, Этот триггер отличается от трех других еще и тем, что сбрасывается при включении Питания ЭВМ сигналом Сброс Н 33, или по инициативе внешнего устройства сигналом КД Н (конец данных) 12 при помощи элемента НЕ-ИЛИ-НЕ 82, Состояние этого триггера всегда передается внешнему устройству через выход 15 управления обменом. Сигнал Чтение/Запись 16 с соответствующего триггера также. пбступает на ВУ с выхода 16 управления направлением обмена,

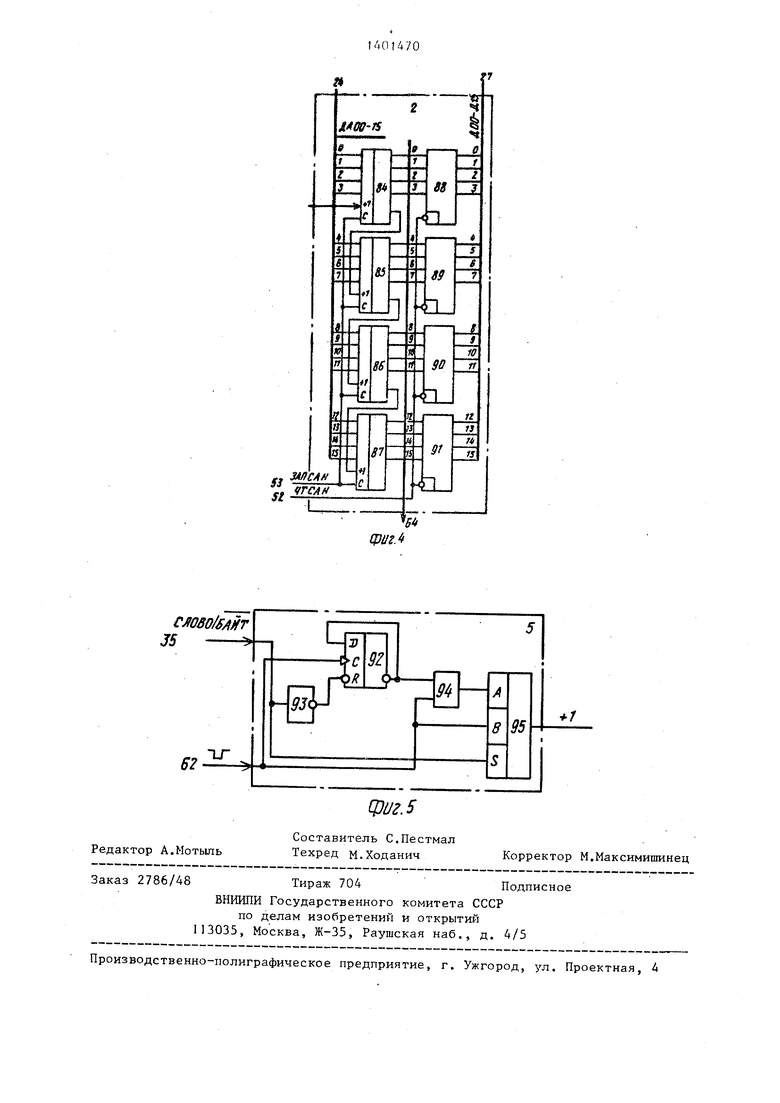

Счетчик 2 адреса состоит (фиг, 4) из шестнадцатиразрядного двоичного счетчика с возможностью параллельной записи (четыре четырехразрядных счетчика 84-87) и шинных формирователей 88-91.

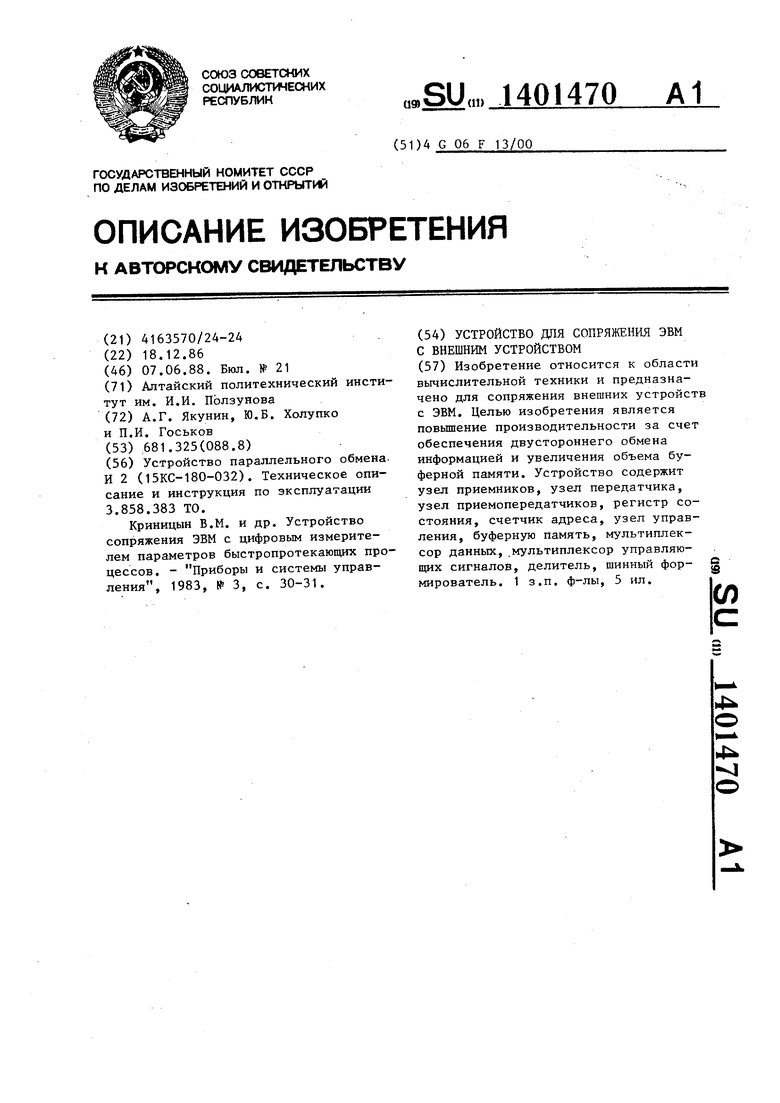

Делитель содержит (фиг. 5), триггер 92, элемент НЕ 93, элемент ИЛИ 94 и мультиплексор 95. Триггер и мультиплексор управляются сигналом Слово/Байт 35. Если установлен режим Слово, то с входа 62 узла 5 на его выход сигнал проходит без изменений. Если на линии Слово/Байт 35 установлен О (режим Байт), то на выход проходит лишь каждый второй входной импульс.

Мультиплексор 4 данных и мультиплексор 7 сигналов управления переключаются сигналом ЭВМ/ВУ 37(38). Если этот сигнал в состоянии (режим ЭВМ, то на информационный вход 66 БП 6 через информационный вход 23 на выход мультиплексора 4 поступают данные с шины ДА 00-ДА 15 (с выхода 20 узла 11), а на управляющие входы 61 и 60 БП 6 поступают соответственно сигналы ВБР СД Н и ЗАЛ СД Н с управляющих выходов 43 и 44 узла 1 через мультиплексор 7. Если же в регистре 3 включен режим ВУ, то на информационный вход 66 БП 6 подаются данные с внешнего устройства через информационный вход 13 мультиплексора 4, а на управляющие входы 61 и 60 БП 6 через информационные входы 14 и 57 мультиплексора 7 поступают синхроимпульсы внешнего устройства и сигнал Чтение/Запись с выхода 16 регистра 3.

Устройство работает следующим образом.

При включении питания канальным сигналом к Сброс Н, прошедшим через узел 9 и поступившим на вход 33 регистра 3, сигнал Старт/Стоп на выходе 15 управления обменом устанавливается в состояние Стоп. Для переключения устройства,в состояние ввода с ВУ процессор передает в регистр 3 код, который устанавливает на выходах 34, 15, 16 и 36 регистра 3 соответственно сигналы Слово, Старт Запись, ВУ. Этот код (1000048), переданный из канала,на выход 20 узла 11 (шина ДА 00-ДА 15) и, следовательно, на информационный вход 21 регистра 3, записывается в триггеры сигналом ЗАП СС Н, поступившим на вход 40 регистра 3 с выхода 42 узла 1

Внешнее ус-тройство после получе ния сигналов Старт и Запись на:чинает вьфабатьгоать синхроимпульсы.

0

5

0

5

0

которые поступают на вход 14 мульти- плексора 7 и затем с выхода 59 мультиплексора 7 на вход 61 БП 6 и вход

62делителя 6 (так как мультиплексо- ры сигналом ВУ с выхода 36 регистра 3 переключаются на режим работы

с ВУ). Одновременно через информационный вход 13 данные с выхода мультиплексора 4 поступают на информационный вход 66 БП 6 и запоминаются в нем, так как на входе 60 БП 6 присутствует сигнал Запись, поступающий через информационный вход 57 мультиплексора 7 на его выход с выхода 16 управления направлением обмена регистра 3. Данные обрабатываются синхроимпульсами, поступающими на вход 61 БП 6 и на вход 62 делителя 5. Поскольку на выходе 34 управления первьм режимом регистра присутствует сигнал Слово, то он по входу 35 делителя 5 удерживает последний в таком режиме, когда сигналы проходят на выход без изменений. В результате каждый синхроимпульс ВУ увеличивает на 1 содержимое счетчика в регистре 2 через счетный вход

63счетчика 2. Таким образом, поступающие от ВУ данные последовательно запоминаются в БП 6.

После завершения передачи блока данных (длина блока должна быть меньше или равна емкости БП) внешнее устройство через вход 12 управления

обменом регистра 3 устанавливает

триггер (и соответствующий сигнал на выходе 15) в состояние Стоп. Это состояние считывается процессором при обращении к слову состояния. При этом узел 1 вырабатывает сигнал .ЧТ СС Н, поступающий на вход 39 регистра 3, и одновременно вырабатывает сигнал ЧТ Н, поступаюпц й на управляющий вход 49 узла 11, При

5 этом состояние триггера Старт/стоп передается на информационный вход 25 узла 11 (шина Д 00-Д 15) с информационного выхода 26 регистра 3. После завершения обмена с ВУ процессор устанавливает триггер ЭВМ/ВУ в состояние ЭВМ путем передачи необходимого кода в регистр 3. При этом узел 1 вырабатывает сигнал ЗАП СС Н, поступающий на управляющий

5 вход 40 регистра 3, а стробируклцие данные, установленные к этому моменту в канале ЭВМ и прошедшие с выхода

20узла 11 на информационный вход

21регистра 3. Дальнейшие действия

0

0

процессора целиком определяются программой, которая зависит от решаемой задачи. При этом любые операции с хранимыми в БП данными включают в себя Запись (Чтение) адреса в счетчике 2 (эти операции обмена нужны не всегда, так как при последовательной выборке или записи значение счетчика, адреса автоматически увеличивается, вход 61 БП 6 соединен через делитель 5 со счетным входом 63 счетчика 2), а также Чтение (Запись) данных из БП 6. При этом узел 1 уп-. равления вырабатывает для счетчика 2 и БП 6 в соответствии с режимом обмена необходимые управляющие сигналы (например, для счетчика 2 это ЧТ СА Н и ЗАЛ СА Н, а для БП 6 - ЧТ СД Н и ЗАП СД Н). Обмен процессора со счетчиком 2 аналогичен описанному выше обмену с регистром 3.

Обмен с БП 6 осуществляется следующим образом.

Поскольку на выходе 36 управления вторым режимом присутствует сигнал ЭВМ и поступает на управляющие входы 37 и 38 мультиплексоров 4 и 7, то на информационный вход 66 БП 6 проходят данные с информационного входа 23 мультиплексора 4, т.е. с выхода 20 узла t1 (шина ДА .00-ДА 15). Сигналы CS 59 и 58 на управляющие входы 61 и 60 БП 6 поступают с управляющих выходов 43 и 44 узла 1 через входы 45 и 46.

После обработки данных, хранящихся в БП 6, возможен их вывод обратно на внешнее устройство. Этот режим отличается от режима ввода данных с ВУ только тем, что на выходе 16 управления направлением передачи установлен режим Чтение ( логическая 1). Уели устройство сопряжения может работать в режиме прерываний, то вместо ожидания процессор может обслуживать другие устройства или выполнять еще какие-либо действия.

Очень части при обработке процессором хранимой в БП информации необходим режим поэлементной модификации массива данных. Предлагаемое устройство позволяет выполнять такие операции без использования дополнительной оперативной памяти. Для реализации этого режима достаточно установить триггер Слово/Байт регистра 3 в состояние Байт. Тогда увеличение счетчика адреса будет происходить лишь при каждом втором обращении

к БП, т.е. допустимо считывание слова данных из БП и запись ei o после модификации по прежнему адресу. Этот же самый режим позволяет осуществлять побайтовую запись при чтение данных. В любой момент возможно изменение начального адреса группы данных, подлежащих считыванию или модификации по сигналу ЗАП СА Н, а также всегда можно определить текущий адрес регистра 2 путем считывания его значения (по сигналам ЧТ СА Н и ЧТ Н). Это может потребоваться при

определении длины блока данных, поступивших с внешнего устройства, при использовании устройства в качестве дополнительной памяти ЭВМ, а также при обработке БЗУ в произвольной по20

следовательности.

Формула изобретения

1. Устройство для сопряжения ЭВМ

с внешним устройством, содержащее узел приемников, узел передатчика, узел приемопередатчиков, узел управления, счетчик адреса, буферную память, мультиплексор сигналов управления, причем первый, второй, третий, четвертый, пятый информационные входы узла приемников являются входами устройства для подключение} к группе управляющих выходов ЭВМ, информаци- онньй выход узла передатчика является выходом устройства для подключения к синхровходу ЭВМ, первая группа информационных входов-выходов узла приемопередатчиков образует группу входов-выходов устройства для подключения к группе информационных входов-в ыходов ЭВМ, вторая группа информационных входов-выходов узла приемопередатчиков, первая группа информационных выходов счетчика адрес а и группа информационных выходов буферной памяти образуют группу входов-выходов устройства для подключения к группе информационных входов-выходов внешнего устройства,

первый информационный вход мульти- . плексора управляющих сигналов является входом устройства для подключения к синхровыходу внешнего устройства, при этом первый, второй, третий, четвертый, пятый информационные выходы узла приемников соединены соответственно с установочным входом, первым, вторым, третьим, четвертым входами логического условия узла управления, первый выход которого соединен с информационным гзходом узла передатчика, второй выход узла управления соединен с управляющим входом узла приемопередатчиков, группа информационных выходов которого соединена с группой информационных входов счетчика адреса и с группой входов логического условия узла управления третий и четвертый выходы которого соединены соответственно с входами чтения и записи счетчика адреса, вторая группа информационных выходов которого соединена с группой адресных входов буферной памяти, входы разрешения и записи-чтения которой соединены соответственно с первым и вторым информационными выходами мультиплексора управляющих сигналов второй и третий информационные входы которого соединены соответственно с пятым и шестым выходами узла управления, отличающееся тем, что, с целью повьш1ения производительности, в него введены регистр состояния, мультиплексор данных, делитель, шинный формирователь, причем первый установочный вход регистра состояния является входом устройства для подключения к установочному выходу внешнего устройства, информационный выход буферной памяти соединен с информационным входам шинного формирователя и является выходом устройства для подключения к информационному входу внешнего устройства, первая группа информационных входов мультиплексора данных образует группу входов устройства для подключения к группе информационных выходов внешнего устройства, первый информационный выход регистра состояния является выходом устройства для подключения к входу запуска внешнего устройства, второй информационный выход регистра состояния соединен с четвертым информационным входом мультиплексора управляющих сигналов и является выходом устройства для подключения к входу чтения-записи внешнего устройства третий информационный выход регистра состояния и информационный выход шинного формирователя соединены со старшим разрядом второй группы информационных входов-выходов узла приемопередатчиков, при этом группа информационных выходов узла приемопередатчиков соединена с группой

5

10

15

20

25

8

информационных иходг1В рогистра состояния и с второй группой информационных входов мультиплексора данных, управляюп1 1Й вход которого соединен с четвертым информационным выходом регистра состояния и с управляющим входом мультиплексора управляющих сигналов, первый информационный выход которого соединен с тактовым входом делителя, разрешающий вход которого соединен с пятым информационным выходом регистра состояния, входы чтения и записи которого соединены соответственно с седьмым и восьмым вькодами узла управления, девятый выход которого соединен с управляющим входом шинного формирователя, установочный вход регистра состояния соединен с первым информационным выходом узла приемников, выход делителя соединен со счетным входом счетчика адреса, группа информационных выходов мультиплексора данных соединена с группой информационных входов буферной памяти,

2. Устройство по п. 1, отличающееся тем, что узел управления содержит дешифратор адреса, триггер, дешифратор, четьфе элемента И-НЕ, два элемента НЕ, элемент НЕ-ШИ-НЕ, элемент задержки, причем группа информационных входов дешифратора адреса, первый, второй информационные входы дешифратора, вход первого элемента НЕ, первый вход первого элемента И-НЕ образуют группу входов логического условия узла, второй вход первого элемента И является первым входом логического условия узла, синхровход триггера является вторьм входом логического условия узла, первый управляющий вход дешифратора соединен с первым входом второго элемента И-НЕ и является

45 четвертым входом логического условия узла, вход второго элемента И соединен с первым входом третьего элемента И-НЕ и является третьим входом логического условия узла, еди50 ничный вход триггера является установочным входом узла, выход элемента задержки является первым выходом узла, выход третьего элемента И-НЕ соединен с первым входом четвертого

55 элемента И-НЕ и является вторым выходом узла, первый, второй, третий, четвертый, пятый, шестой выход дешифратора являются соответственно третьим, четвертым, шестым, седьмым.

30

ЗБ

40

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения канала ввода-вывода с абонентом | 1989 |

|

SU1695312A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1985 |

|

SU1288709A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитных дисках | 1986 |

|

SU1410046A1 |

| Устройство КЭШ-памяти | 1988 |

|

SU1675881A1 |

| Устройство для имитации неисправностей | 1988 |

|

SU1661766A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЯ | 1994 |

|

RU2108623C1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Устройство для сопряжения многоблочной памяти с процессором и вводно-выводными устройствами | 1984 |

|

SU1280645A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

Изобретение относится к области вычислительной техники и предназначено для сопряжения внешних устройств с ЭВМ. Целью изобретения является повышение производительности за счет обеспечения двустороннего обмена информацией и увеличения объема буферной памяти. Устройство содержит узел приемников, узел передатчика, узел приемопередатчиков, регистр состояния, счетчик адреса, узел управления, буферную память, мультиплексор данных,.мультиплексор управляющих сигналов, делитель, шинный формирователь. 1 з.п. ф-лы, 5 ил. (Я

фцг.1

а

«ел

ff-Ш Stt ,

r t1 t1 V

ff

Ml---

jj евиоея

jjIMMI

фиг.З

TO

75

дмгу«

tuuft

.C6POCH

jj

vrccff

39

с 5ЛПССН

HQ

СЛ080/ АЙГ ЗВ

Редактор А.Мотыль

Составитель С.Пестмал Техред М.Ходанич

Ц}и г, 5

Корректор М.Максимишинец

| Устройство параллельного обмена | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Криницын В.М | |||

| и др | |||

| Устройство сопряжения ЭВМ с цифровым измерителем параметров быстропротекающих процессов | |||

| - Приборы и системы управления, 1983, № 3, с | |||

| Способ обработки медных солей нафтеновых кислот | 1923 |

|

SU30A1 |

Авторы

Даты

1988-06-07—Публикация

1986-12-18—Подача