Изобретение относится к области вычислительной техники и может быть использовано для сопряжения управляющей микроэвм с системами управления и контроля быстропротекающих процессов.

Целью изобретения яв11яется повьше ние пропускной способности устройства.

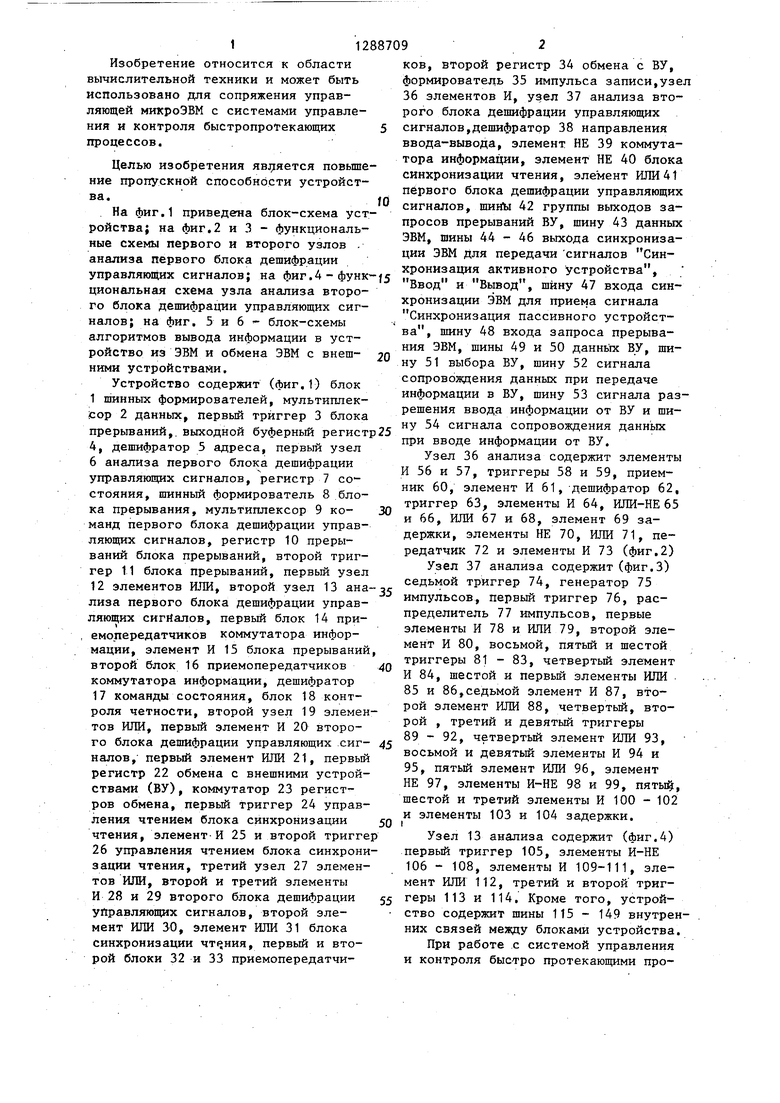

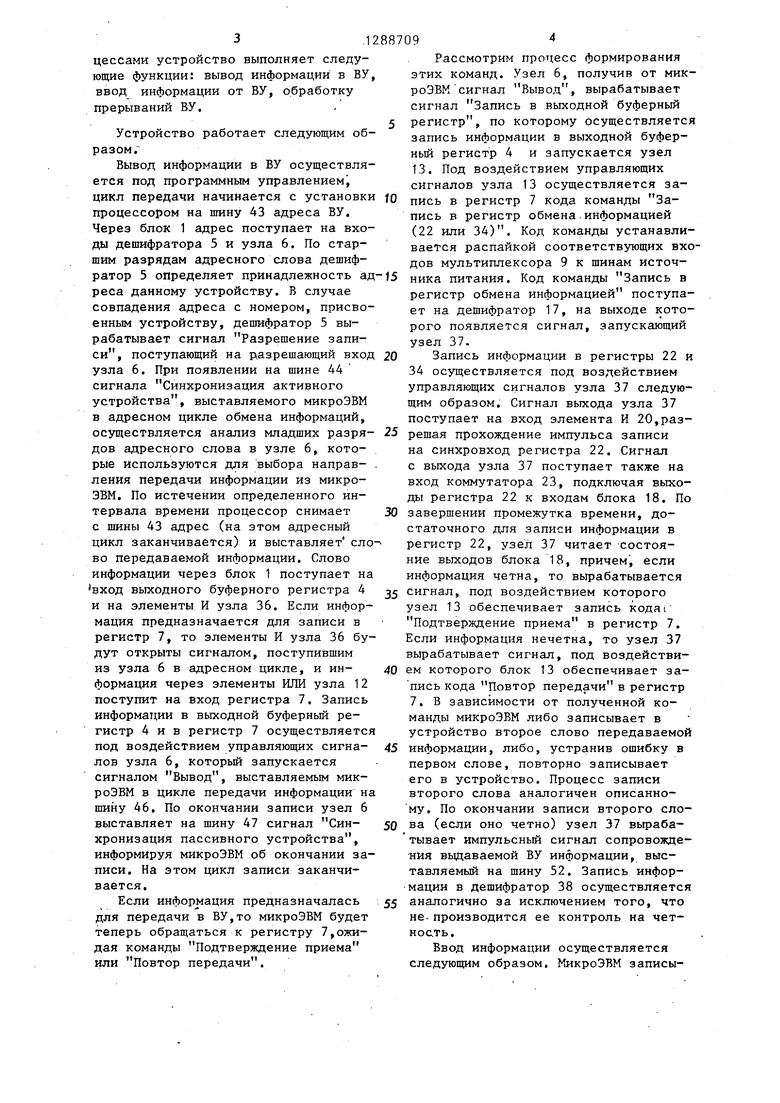

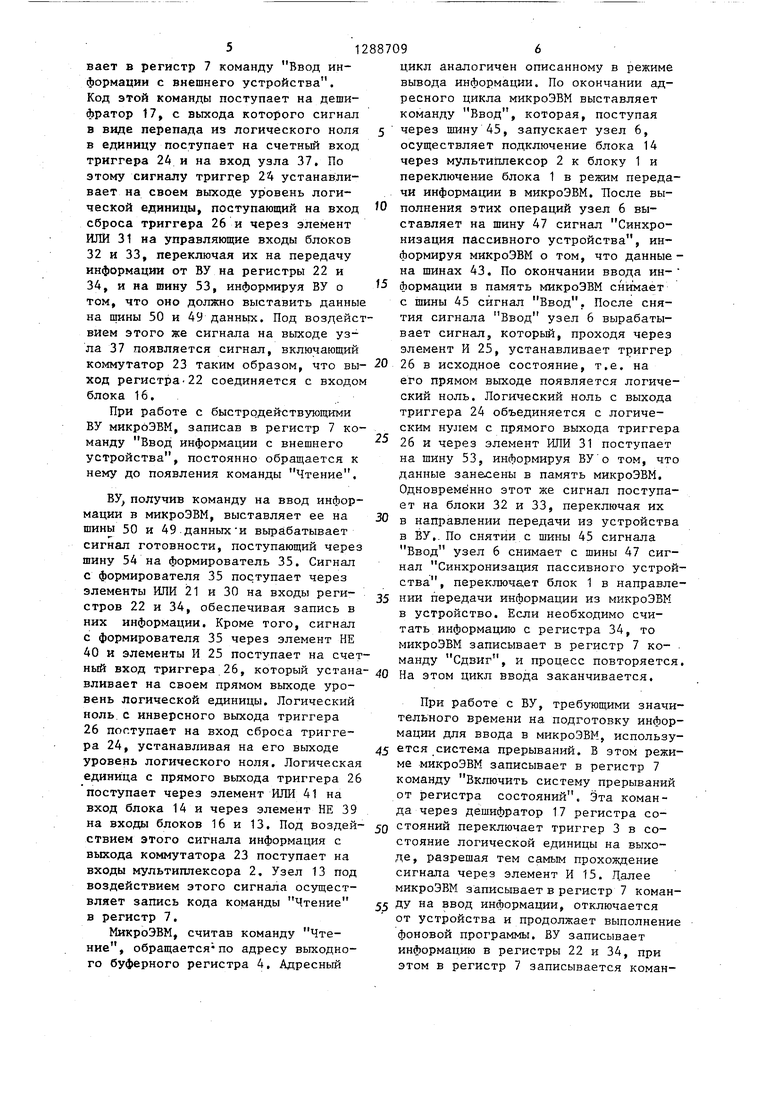

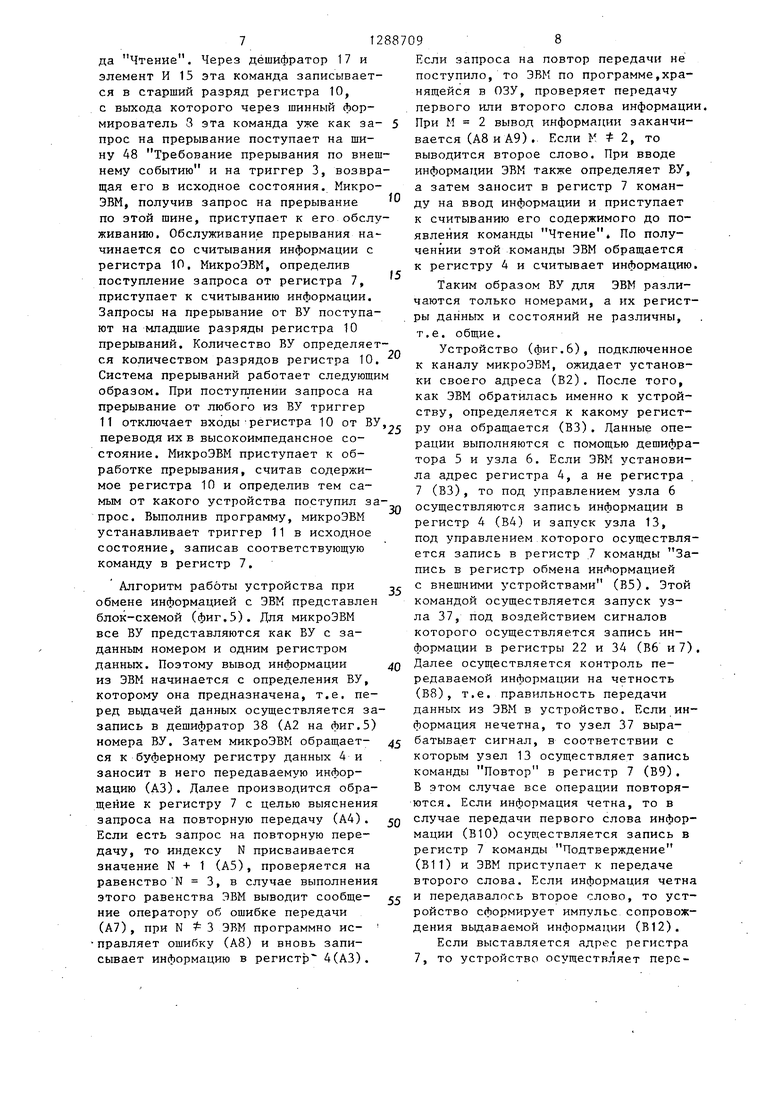

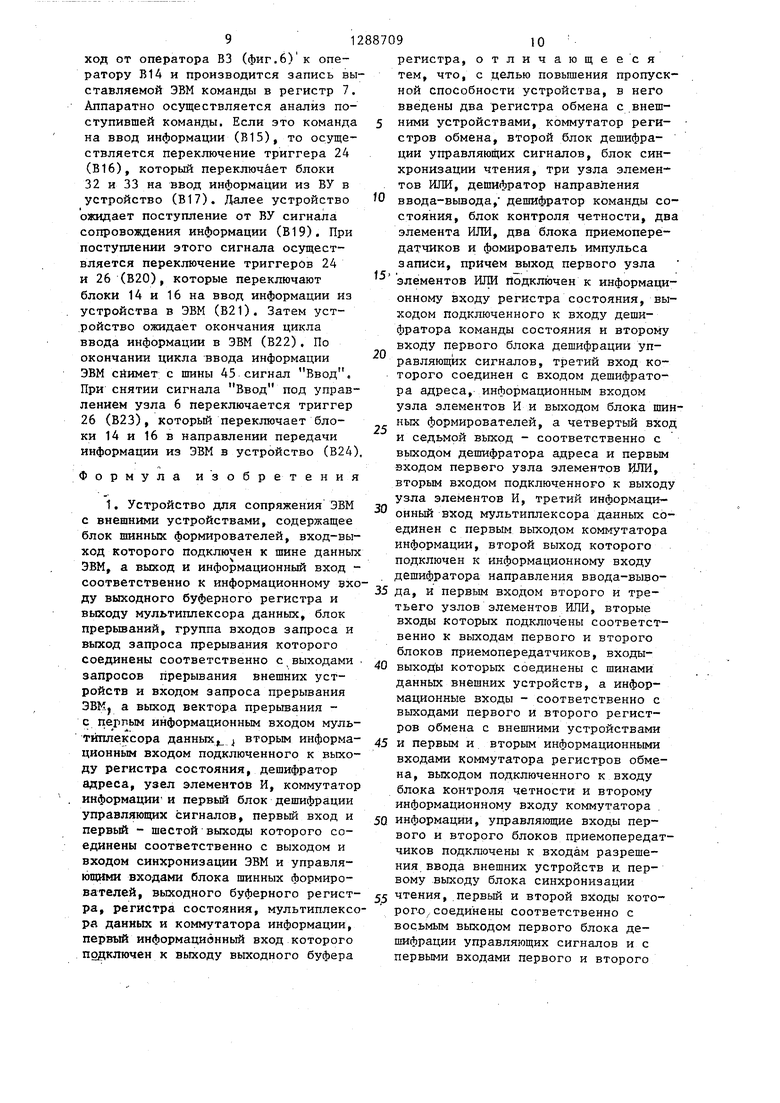

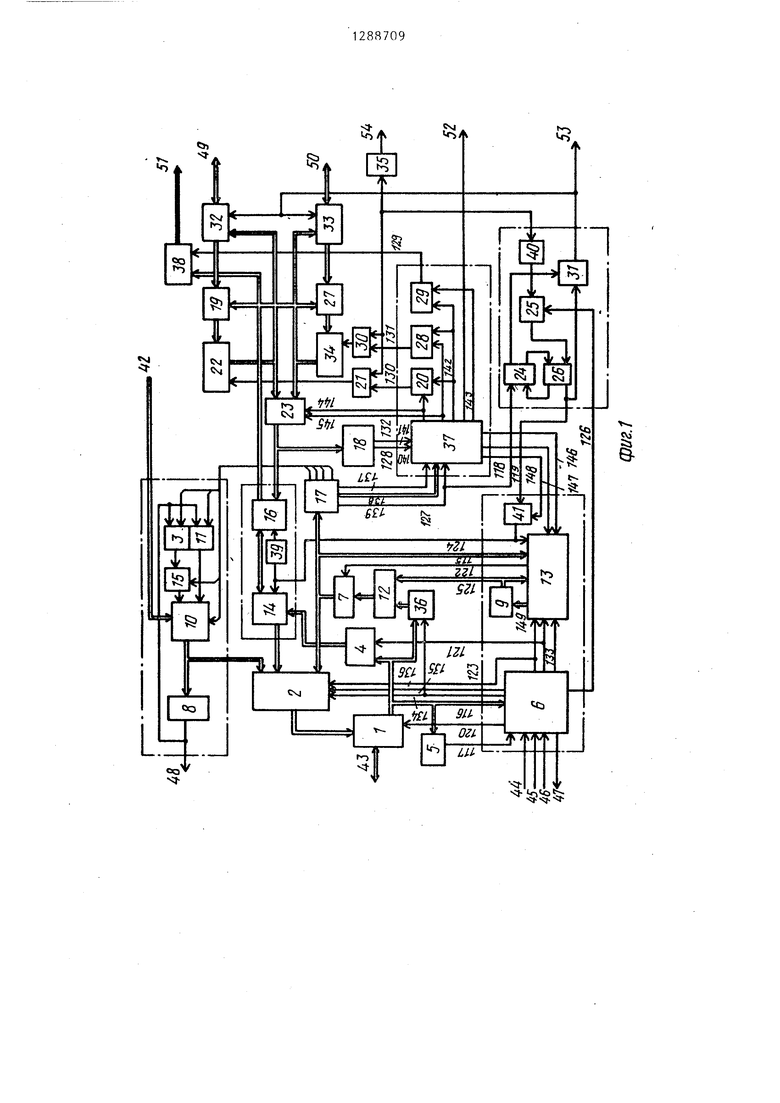

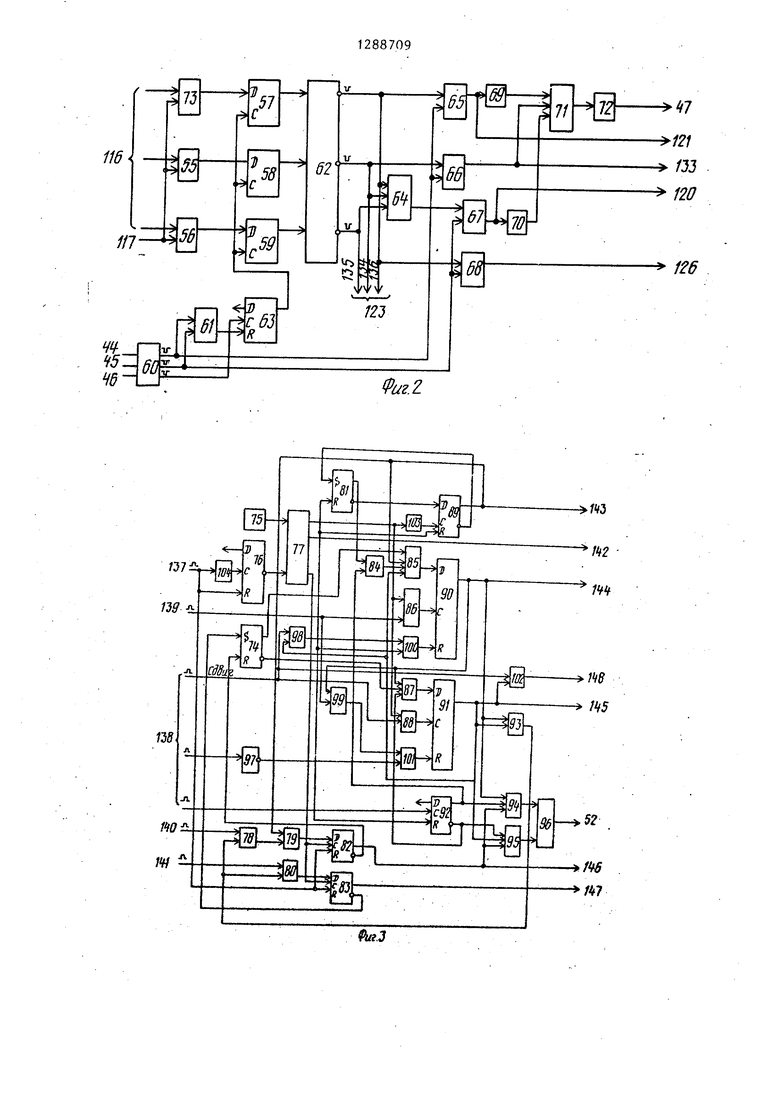

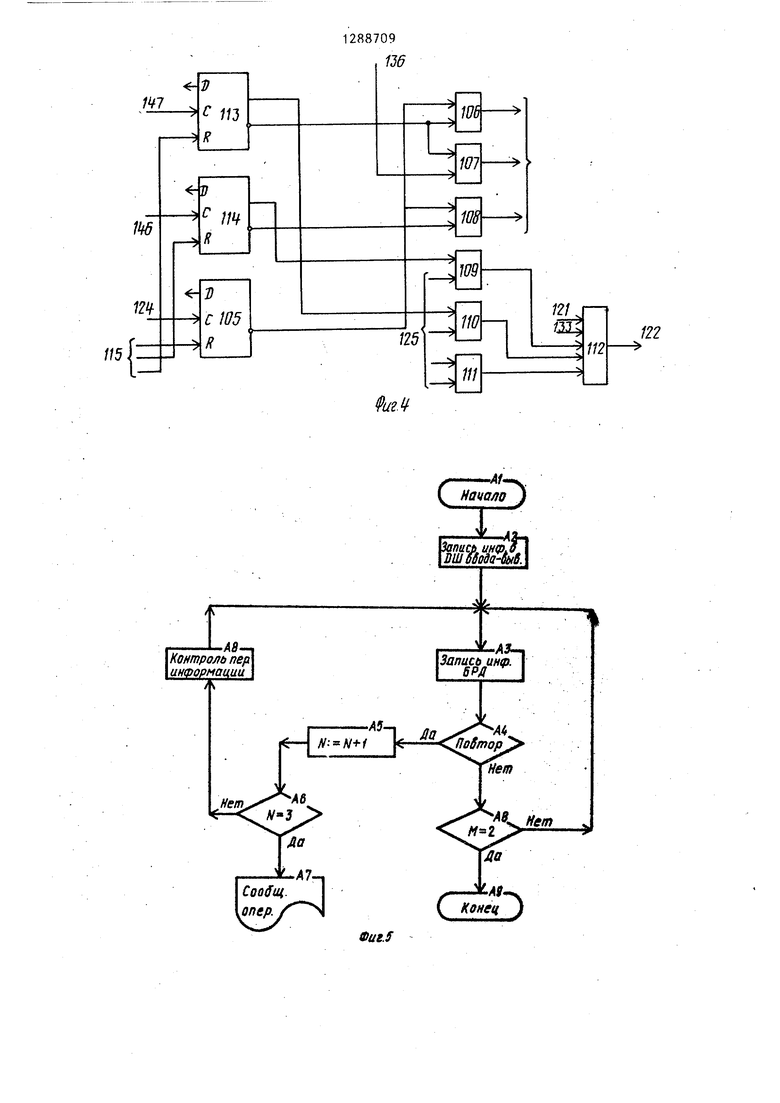

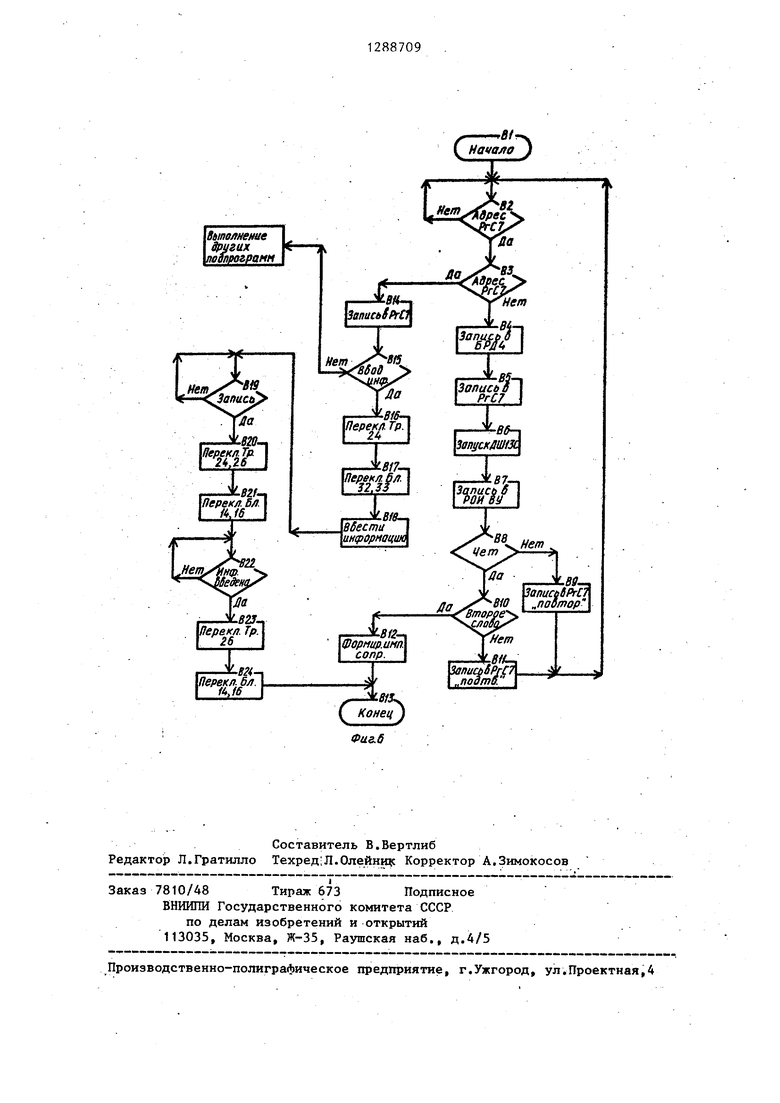

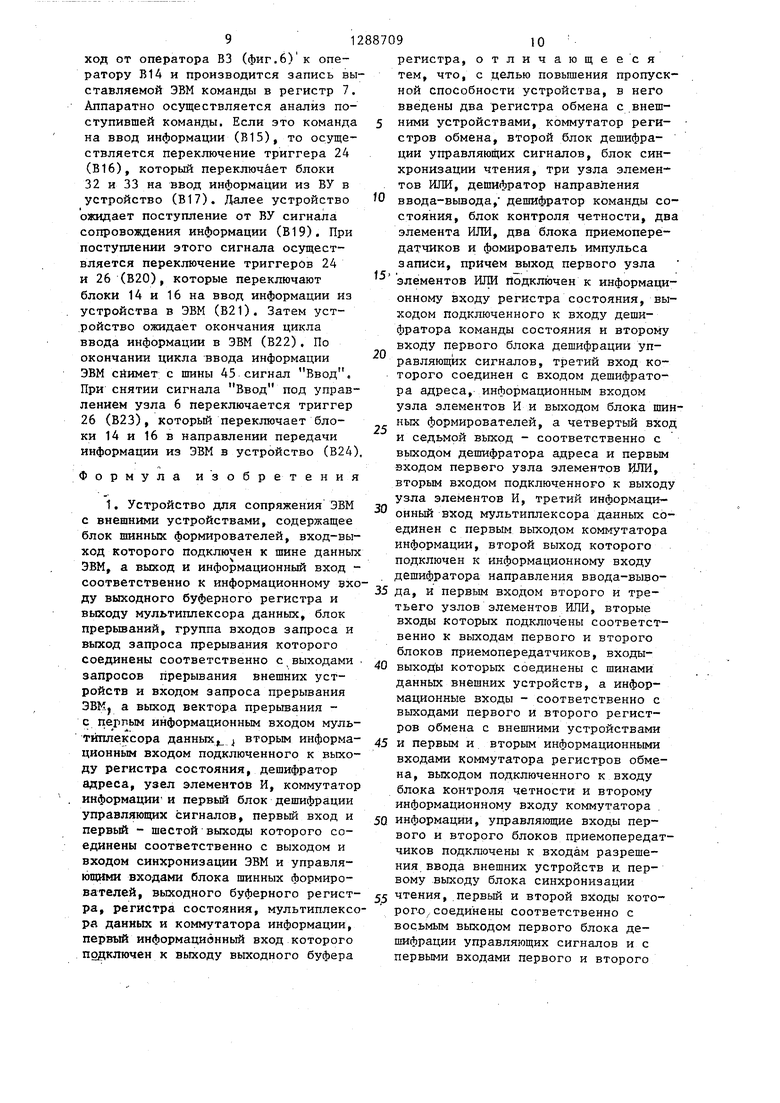

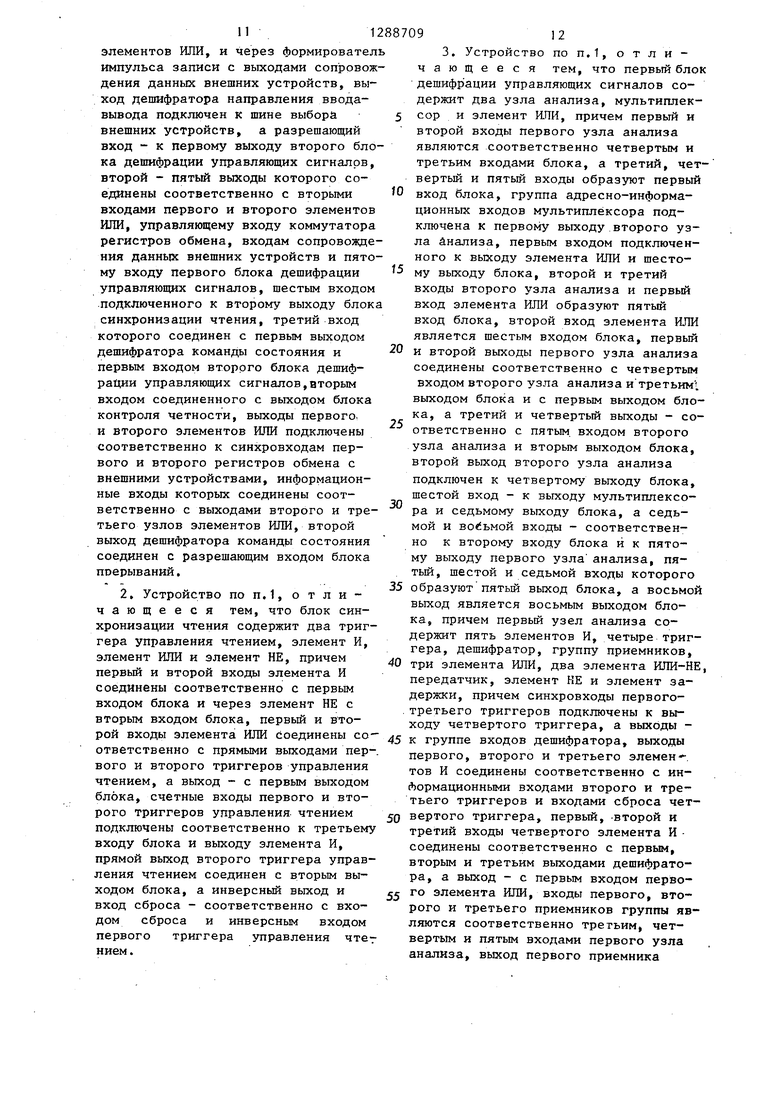

На фиг.1 приведена блок-схема устройства; на фиг.2 и 3 - функциональные схемы первого и второго узлов . анализа первого блока дешифрации управляющих сигналов; на фиг.4 - функ циональная схема узла анализа второго блока дешифрации управляющих сигналов; на фиг. 5 и 6 - блок-схемы алгоритмов вывода информации в устройство из ЭВМ и обмена ЭВМ с внеш- ними устройствами.

Устройство содержит (фиг.1) блок 1 шинных формирователей, мультиплексор 2 данных, первый триггер 3 блока прерываний,, выходной буферный регист 4, дешифратор 5 адреса, первьй узел 6 анализа первого блока дешифрации управляющих сигналов, регистр 7 состояния, шинный формирователь 8 блока прерывания, мультиплексор 9 команд первого блока дешифрации управляющих сигналов, регистр 10 прерываний блока прерываний, второй тригУзел 36 анализа содержит элемент И 56 и 57, триггеры 58 и 59, приемник 60, элемент И 61, дешифратор 62 триггер 63, элементы И 64, ИЛИ-НЕ 6 и 66, ИЛИ 67 и 68, элемент 69 задержки, элементы НЕ 70, ИЛИ 71, передатчик 72 и элементы И 73 (фиг.2 Узел 37 анализа содержит (фиг.3)

гер 11 блока прерываний, первый узел

12 элементов ИЛИ, второй узел 13 ана-з5 ° генератор 75

- г мттлгттт Г /- т TTOTiTat TtT гпмг по-п 7h -

лиза первого блока дешифрации управляющих сигйалов, первый блок 14 при- , емопередатчиков коммутатора информации, элемент И 15 блока прерываний, второй блок 16 приемопередатчиков 40 коммутатора информации, дешифратор 17 команды состояния, блок 18 контроля четности, второй узел 19 элементов ИЛИ, первый элемент И 20 второго блока дешифрации управляющих сиг- 45 налов, первый элемент ИЛИ 21, первьй

импульсов, первый триггер 76, распределитель 77 импульсов, первые элементы И 78 и ИЛИ 79, второй элемент И 80, восьмой, пятьй и шестой триггеры 81 - 83, четвертьй элемен И 84, шестой и первьй элементы ИЛИ 85 и 86,седьмой элемент И 87, второй элемент ИЛИ 88, четвертьй, второй , третий и девятый триггеры 89 - 92, четвертьй элемент ИЛИ 93, восьмой и девятьй элементы И 94 и 95, пятьй элемент ИЖ 96, элемент НЕ 97, элементы И-НЕ 98 и 99, пятьп шестой и третий элементы И 100 - 10 и элементы 103 и 104 задержки.

регистр 22 обмена с внешними устройствами (ВУ), коммутатор 23 регистров обмена, первьй триггер 24 управления чтением блока синхронизации чтения, элемент-И 25 и второй триггер 26 управления чтением блока синхронизации чтения, третий узел 27 элементов Или, второй и третий элементы И 28 и 29 второго блока дешифрации управляющих сигналов, второй элемент ИЛИ 30, элемент ИЛИ 31 блока синхронизации , первьй и второй блоки 32 и 33 приемопередатчи

5

ков, второй регистр 34 обмена с ВУ, формирователь 35 импульса записи,узел 36 элементов И, узел 37 анализа второго блока дешифрации управляющих сигналов,дешифратор 38 направления ввода-вывода, элемент НЕ 39 коммутатора информации, элемент НЕ 40 блока синхронизации чтения, элемент ИЛИ 41 первого блока дешифрации управляющих сигналов, шийЫ 42 группы выходов запросов прерываний ВУ, шину 43 данных ЭВМ, шины 44 - 46 выхода синхронизации ЭВМ для передачи сигналов Синхронизация активного устройства, Ввод и Вывод, шину 47 входа синхронизации ЭВМ для приема сигнала Синхронизация пассивного устройства, шину 48 входа запроса прерывания ЭВМ, шины 49 и 50 данн1 1Х ВУ, шину 51 выбора ВУ, шину 52 сигнала сопровождения данных при передаче информации в ВУ, шину 53 сигнала разрешения ввода информации от ВУ и шину 54 сигнала сопровождения данньгх при вводе информации от ВУ.

Узел 36 анализа содержит элементы И 56 и 57, триггеры 58 и 59, приемник 60, элемент И 61, дешифратор 62, триггер 63, элементы И 64, ИЛИ-НЕ 65 и 66, ИЛИ 67 и 68, элемент 69 задержки, элементы НЕ 70, ИЛИ 71, передатчик 72 и элементы И 73 (фиг.2) Узел 37 анализа содержит (фиг.3)

° генератор 75

г мттлгттт Г /- т TTOTiTat TtT гпмг по-п 7h -

импульсов, первый триггер 76, распределитель 77 импульсов, первые элементы И 78 и ИЛИ 79, второй элемент И 80, восьмой, пятьй и шестой триггеры 81 - 83, четвертьй элемент И 84, шестой и первьй элементы ИЛИ . 85 и 86,седьмой элемент И 87, второй элемент ИЛИ 88, четвертьй, второй , третий и девятый триггеры 89 - 92, четвертьй элемент ИЛИ 93, восьмой и девятьй элементы И 94 и 95, пятьй элемент ИЖ 96, элемент НЕ 97, элементы И-НЕ 98 и 99, пятьп, шестой и третий элементы И 100 - 102 и элементы 103 и 104 задержки.

Узел 13 анализа содержит (фиг.4) первьй триггер 105, элементы И-НЕ 106 - 108, элементы И 109-111, элемент ИЛИ 112, третий и второй триг- геры 113 и 114. Кроме того, устрой- ство содержит шины 115 - 149 внутренних связей между блоками устройства. При работе с системой управления и контроля быс-тро протекающими проI

цессами устройство выполняет следующие функции: вывод информации в ВУ ввод информации от ВУ, обработку прерываний ВУ,

Устройство работает следующим образом.

Вывод информации в ВУ осуществляется под программным управлением цикл передачи начинается с установки процессором на шину 43 адреса ВУ. Через блок 1 адрес поступает на входы дешифратора 5 и узла 6. По старшим разрядам адресного слова дешифратор 5 определяет принадлежность адреса данному устройству. В случае совпадения адреса с номером, присвоенным устройству, дешифратор 5 вырабатывает сигнал Разрешение записи, поступающий на Р1азрешающий вход узла 6. При появлении на шине 44 сигнала Синхронизация активного устройства, выставляемого микроЭВМ в адресном цикле обмена информации, осуществляется анализ младших разрядов адресного слова в узле 6, которые используются для выбора направ- ления передачи информации из микро- ЭВМ. По истечении определенного интервала времени процессор снимает с шины 43 адрес (на этом адресный цикл заканчивается) и выставляет слово передаваемой информации. Слово информации через блок 1 поступает на вход выходного буферного регистра 4 и на элементы И узла 36. Если информация предназначается для записи в регистр 7, то элементы И узла 36 будут открыты сигналом, поступившим из узла 6 в адресном цикле, и информация через элементы ИЛИ узла 12 поступит на вход регистра 7. Запись информации в выходной буферный регистр 4 и в регистр 7 осуществляется под воздействием управляющих сигналов узла 6, который запускается сигналом Вывод, выставляемым мик- роЭВМ в цикле передачи информации на шину 46. По окончании записи узел 6 выставляет на шину 47 сигнал Синхронизация пассивного устройства, информируя микроэвм об окончании записи. На этом цикл записи заканчивается.

Если информация предназначалась для передачи в ВУ,то микроЭВМ будет теперь обращаться к регистру 7,ожидая команды Подтверждение приема или Повтор передачи.

Рассмотрим npo iecc формирования этих команд. Узел 6, получив от микроЭВМ сигнал Вывод, вырабатывает сигнал Запись в выходной буферный 5 регистр, по которому осуществляется запись информации в выходной буферный регистр 4 и запускается узел 13. Под воздействием управляющих сигналов узла 13 осуществляется за0 пись в регистр 7 кода команды Запись в регистр обмена.информацией (22 или 34). Код команды устанавливается распайкой соответствующих входов мультиплексора 9 к шинам источ5 ника питания. Код команды Запись в регистр обмена информацией поступает на дешифратор 17, на выходе которого появляется сигнал, запускающий узел 37.

0 Запись информации в регистры 22 и 34 осуществляется под воздействием управляющих сигналов узла 37 следующим образом. Сигнал выхода узла 37 поступает на вход элемента И 20,раз5 решая прохождение импульса записи на синхровход регистра 22. Сигнал с выхода узла 37 поступает также на вход коммутатора 23, подключая выходы регистра 22 к входам блока 18. По

0 завершении промежутка времени, достаточного для записи информации в

регистр 22, узел 37 читает -состояние вьпсодов блока 18, причем, если информация четна, то вырабатывается

5 сигнал, под воздействием которого узел 13 обеспечивает запись кода Подтверждение приема в регистр 7. Если информация нечетна, то узел 37 вырабатывает сигнал, под воздействи0 ем которого блок 13 обеспечивает за- пись кода Повтор передачи в регистр 7. В зависимости от полученной команды микроэвм либо записывает в устройство второе слово передаваемой

5 информации, либо, устранив ошибку в первом слове, повторно записывает его в устройство. Процесс записи второго слова аналогичен описанному. По окончании записи второго сло0 ва (если оно четно) узел 37 вьфаба- тывает импульсный сигнал сопровождения выдаваемой ВУ информации, выставляемый на шину 52. Запись информации в дешифратор 38 осуществляется

5 аналогично за исключением того, что не- производится ее контроль на чет- нос.ть.

Ввод информации осуществляется следующим образом. МикроЭВМ записывает в регистр 7 команду Ввод информации с внешнего устройства. Код этой команды поступает на дешифратор 17, с выхода которого сигнал в виде перепада из логического ноля в единицу поступает на счетньй вход триггера 2А и на вход узла 37, По этому сигналу триггер 24 устанавливает на своем выходе ур овень логической единицы, поступающий на вход сброса триггера 26 и через элемент ИЛИ 31 на управляющие входы блоков 32 и 33, переключая их на передачу информации от ВУ на регистры 22 и 34, и на шину 53, информируя ВУ о том, что оно должно выставить данные на шины 50 и 49 данньрс. Под воздействием этого же сигнала на выходе узла 37 появляется сигнал, включающий коммутатор 23 таким образом, что выход регистра-22 соединяется с входом блока 16.

При работе с быстродействующими ВУ микроэвм, записав в регистр 7 команду Ввод информации с внешнего устройства, постоянно обращается к нему до появления команды Чтение.

ВУ, получив команду на ввод информации в микроэвм, выставляет ее на шины 50 и 49 данных И вырабатывает сигнал готовности, поступающий через шину 54 на формирователь 35. Сигнал с формирователя 35 поступает через элементы ИЛИ 21 и 30 на входы регистров 22 и 34, обеспечивая запись в них информации. Кроме того, сигнал с формирователя 35 через элемент НЕ 40 и элементы И 25 поступает на счетный вход триггера 26, который устана вливает на своем прямом выходе уровень логической единицы. Логический ноль.с инверсного выхода триггера 26 поступает на вход сброса триггера 24, устанавливая на его выходе уровень логического ноля. Логическая единица с прямого выхода триггера 26 поступает через элемент ИЛИ 41 на вход блока 14 и через элемент НЕ 39 на входы блоков 16 и 13. Под воздействием этого сигнала информация с выхода коммутатора 23 поступает на входы мультиплексора 2, Узел 13 под воздействием этого сигнала осуществляет запись кода команды Чтение в регистр 7.

Микроэвм, считав команду Чтение, обращается по адресу выходного буферного регистра 4. Адресный

цикл аналогичен описанному в режиме вывода информации. По окончании адресного цикла микроэвм выставляет команду Ввод, которая, поступая

через шину 45, запускает узел 6, осуществляет подключение блока 14 через мультиплексор 2 к блоку 1 и переключение блока 1 в режим передачи информации в микроэвм. После выполнения этих операций узел 6 выставляет на шину 47 сигнал Синхронизация пассивного устройства, информируя микроэвм о том, что данные- на шинах 43, По окончании ввода ин-

формации в память микроЭВМ снимает с шины 45 сигнал Ввод. После снятия сигнала Ввод узел 6 вырабатывает сигнал, которьй, проходя через элемент И 25, устанавливает триггер

26 в исходное состояние, т.е. на

его прямом выходе появляется логический ноль. Логический ноль с выхода триггера 24 объединяется с логическим нулем с прямого выхода триггера

26 и через элемент НИИ 31 поступает на шину 53, информируя ВУ о том, что данные занесены в память микроЭВМ. Одновременно этот же сигнал поступает на блоки 32 и 33, переключая их в направлении передачи из устройства в ВУ,. По снятии с шины 45 сигнала Ввод узел 6 снимает с шины 47 СИ1- нал Синхронизация пассивного устрой 0

ства , переключает блок 1 в направле- 35 НИИ передачи информации из микроЭВМ в устройство. Если необходимо считать информацию с регистра 34, то микроэвм записывает в регистр 7 ко- . манду Сдвиг, и процесс повторяется. На этом цикл ввода заканчивается.

При работе с ВУ, требующими значительного времени на подготовку информации для ввода в микроэвм, использу45 ется система прерываний. В этом режиме микроэвм записывает в регистр 7 команду Включить систему прерываний от регистра состояний. Эта команда через дешифратор 17 регистра со50 стояний переключает триггер 3 в состояние логической единицы на выходе, разрешая тем самым прохождение сигнала через элемент И 15. Далее микроэвм записывает в регистр 7 коман55 ДУ на ввод информации, отключается от устройства и продолжает выполнение фоновой программы. ВУ записывает информацию в регистры 22 и 34, при этом в регистр 7 записывается команда Чтение. Через дешифратор 17 и элемент И 15 эта команда записывается в старший разряд регистра 10, с выхода которого через шинный формирователь 3 эта команда уже как за- прос на прерывание поступает на шину 48 требование прерывания по внешнему событию и на триггер 3, возвращая его в исходное состояния. Микро- ЭВМ, получив запрос на прерывание по этой шине, приступает к его обслуживанию. Обслуживание прерывания на чинается со считывания информации с регистра Ю, МикроЭВМ, определив поступление запроса от регистра 7, приступает к считыванию информации. Запросы на прерывание от ВУ поступают на младшие разряды регистра 10 прерываний. Количество ВУ определяет

ся количеством разрядов регистра 10.

Система прерываний работает следующи образом. При поступлении запроса на прерывание от любого из ВУ триггер 11 отключает входы-регистра Ю от ВУ переводя их в высокоимпедансное состояние. Микроэвм приступает к обработке прерывания, считав содержимое регистра 10 и определив тем самым от какого устройства поступил запрос. Выполнив программу, микроЭВМ устанавливает триггер 11 в исходное состояние, записав соответствующую команду в регистр 7.

Алгоритм работы устройства при обмене информацией с ЭВМ представлен блок-схемой (фиг.5). Для микроЭВМ все ВУ представляются как ВУ с заданным номером и одним регистром данных. Поэтому вывод информации из ЭВМ начинается с определения ВУ, которому она предназначена, т.е. перед выдачей данных осуществляется за запись в дешифратор 38 (А2 на фиг.5) номера ВУ. Затем микроЭВМ обращает- ся к буферному регистру данных 4 и заносит в него передаваемую информацию (A3). Далее производится обращение к регистру 7 с целью выяснения запроса на повторную передачу (А4). Если есть запрос на повторную передачу, то индексу N присваивается значение N + 1 (А5), проверяется на равенство N 3, в случае выполнения этого равенства ЭВМ выводит сообще- ние оператору об ошибке передачи (А7), при N ifc 3 ЭВМ программно ис- правляет ошибку (А8) и вновь записывает информацию в регистр 4(A3).

5

0

5

0

г 0 5 Q

Если запроса на повтор передачи не поступило, то ЭВМ по программе,хранящейся в ОЗУ, проверяет передачу первого или второго слова информации, При М 2 вывод информации заканчивается (А8иА9). Если У, Ф 2, то выводится второе слово. При вводе информации ЭВМ также определяет ВУ, а затем заносит в регистр 7 команду на ввод информации и приступает к считыванию его содержимого до появления команды Чтение. По полу- ченнии этой команды ЭВМ обращается к регистру 4 и считывает информацию.

Таким образом ВУ для ЭВМ различаются только номерами, а их регистры данных и состояний не различны, т.е. общие.

Устройство (фиг.6), подключенное к каналу микроЭВМ, ожидает установки своего адреса (В2). После того, как ЭВМ обратилась именно к устройству, определяется к какому регистру она обращается (ВЗ). Данные операции выполняются с помощью дешифратора 5 и узла 6. Если ЭВМ установила адрес регистра 4, а не регистра

7(ВЗ), то под управлением узла 6 осуществляются запись информации в регистр 4 (В4) и запуск узла 13, под управлением которого осуществляется запись в регистр 7 команды Запись в регистр обмена ингЬормацией

с внешними устройствами (В5) . Этой командой осуществляется запуск узла 37, под воздействием сигналов которого осуществляется запись информации в регистры 22 и 34 (В6 и 7) . Далее осуществляется контроль передаваемой информации на четность (В8), т.е. правильность передачи данных из ЭВМ в устройство. Если информация нечетна, то узел 37 вырабатывает сигнал, в соответствии с которым узел 13 осуществляет запись команды Повтор в регистр 7 (В9) .

8этом случае все операции повторяются. Если информация четна, то в случае передачи первого слова информации (В 10) осуществляется запись в регистр 7 команды Подтверждение (В11) и ЭВМ приступает к передаче второго слова. Если информация четна и передавалось второе слово, то устройство сформирует импульс сопровождения выдаваемой информации (В12).

Если выставляется адрес регистра 7, то устройство осуществляет перс

91

ход от оператора ВЗ (фиг.6) к оператору В1А и производится запись выставляемой ЭВМ команды в регистр 7. Аппаратно осуществляется анализ поступившей команды. Если это команда на ввод информации (В15), то осуществляется переключение триггера 24 (В16), который переключает блоки 32 и 33 на ввод информации из ВУ в устройство (В 17). Далее устройство ожидает поступление от ВУ сигнала сопровождения информации (В19). При поступлении этого сигнала осуществляется переключение триггеров 24 и 26 (В20), которые переключают блоки 14 и 16 на ввод информации из устройства в ЭВМ (В21). Затем устройство ожидает окончания цикла ввода информации в ЭВМ (В22). По окончании цикла ввода информации ЭВМ сйимет с шины 45 сигнал Ввод. При снятии сигнала Ввод под управлением узла 6 переключается триггер 26 (В23), который переключает блоки 14 и 16 в направлении передачи

информации из ЭВМ в устройство (В24), Формула изобретения

1. Устройство для сопряжения ЭВМ с внешними устройствами, содержащее блок шинных формирователей, вход-выход которого подключен к шине данных ЭВМ, а выход и информационный вход 30

ходом подключенного к входу дешифратора команды состояния и второму входу первого блока дешифрации управляющих сигналов, третий вход которого соединен с входом дешифратора адреса, информационным входом узла элементов И и выходом блока шин ных формирователей, а четвертый вход и седьмой выход - соответственно с выходом дешифратора адреса и первым входом первого узла элементов ЩШ, вторым входом подключенного к выходу узла элементов И, третий информационный вход мультиплексора данных соединен с первым выходом коммутатора информации, второй выход которого подключен к информационному входу

дешифратора направления ввода-вывосоответственно к информационному вхо- -,,:

-г - ,2 д первым входом второго и третьего узлов элементов ИЛИ, вторые входы которых подключены соответственно к выходам первого и второго блоков приемопередатчиков, входы- 40 выход ы которых соединены с шинами данных внешних устройств, а информационные входы - соответственно с выходами первого и второго регистс перпым информационным входом муль л.

типлексора данных вторым информационным входом подключенного к выходу регистра состояния, дешифратор адреса, узел элементов И, коммутатор информации и первьй блок дешифрации управляющих сигналов, первый вход и первьй - шестой выходы которого соединены соответственно с выходом и

ду выходного буферного регистра и выходу мультиплексора данных, блок прерываний, группа входов запроса и выход запроса прерывания которого соединены соответственно с выходами запросов прерывания внешних устройств и входом запроса прерывания ЭВМ а выход вектора прерывания ров обмена с внешними устройствами 45 и первым и вторым информационными входами коммутатора регистров обмена, выходом подключенного к входу блока контроля четности и второму информационному входу коммутатора 50 информации, управляющие входы первого и второго блоков приемопередатчиков подключены к входам разрешения ввода внешних устройств и; первому выходу блока синхронизации 55 чтения, первьй и второй входы которого , соединены соответственно с восьмым выходом первого блока дешифрации управляющих сигналов и с первыми входами первого и второго

входом синхронизации ЭВМ и управляющими входами блока шинных формирователей, вькодного буферного регистра, регистра состояния, мультиплексора данных и коммутатора информации, первый информационный вход которого подключен к выходу выходного буфера

10

регистра, отличающееся тем, что, с целью повьшения пропускной способности устройства, в него введены два регистра обмена с внешними устройствами, коммутатор регистров обмена, второй блок дешифрации управляющих сигналов, блок синхронизации чтения, три узла элементов ИЛИ, дешифратор направления ввода-вьшода, дешифратор команды состояния, блок контроля четности, два элемента РШИ, два блока приемопередатчиков и фомирователь импульса записи, причем выход первого узла

элементов ИЛИ подключен к информационному входу регистра состояния, вы0

5

0

ходом подключенного к входу дешифратора команды состояния и второму входу первого блока дешифрации управляющих сигналов, третий вход которого соединен с входом дешифратора адреса, информационным входом узла элементов И и выходом блока шинных формирователей, а четвертый вход и седьмой выход - соответственно с выходом дешифратора адреса и первым входом первого узла элементов ЩШ, вторым входом подключенного к выходу узла элементов И, третий информационный вход мультиплексора данных соединен с первым выходом коммутатора информации, второй выход которого подключен к информационному входу

ров обмена с внешними устройствами 45 и первым и вторым информационными входами коммутатора регистров обмена, выходом подключенного к входу блока контроля четности и второму информационному входу коммутатора 50 информации, управляющие входы первого и второго блоков приемопередатчиков подключены к входам разрешения ввода внешних устройств и; первому выходу блока синхронизации 55 чтения, первьй и второй входы которого , соединены соответственно с восьмым выходом первого блока дешифрации управляющих сигналов и с первыми входами первого и второго

111

элементов ИЛИ, и через формировател импульса записи с выходами сопровождения данных внешних устройств, выход дешифратора направления ввода- вывода подключен к шине выбора внешних устройств, а разрешающий вход - к первому выходу второго блока дешифрации управляющих сигналов, второй - пятый выходы которого соединены соответственно с вторыми входами первого и второго элементов ИЛИ, управляющему входу коммутатора регистров обмена, входам сопровождения данньос внешних устройств и пятому входу первого блока дешифрации управляющих сигналов, шестым входом подключенного к второму выходу блок синхронизации чтения, третий вход которого соединен с первым выходом дешифратора команды состояния и первым входом второго блока дешифрации управляющих сигналов,вторым входом соединенного с выходом блока контроля четности, выходы первого, и второго элементов ИЛИ подключены соответственно к синхровходам первого и второго регистров обмена с внешними устройствами, информационные входы которых соединены соответственно с выходами второго и третьего узлов элементов ИЛИ, второй выход дешифратора команды состояния соединен с разрешающим входом блока прерываний.

2. Устройство по П.1, отличающееся тем, что блок синхронизации чтения содержит два триггера управления чтением, элемент И, элемент ИЛИ и элемент НЕ, причем первый и второй входы элемента И соединены соответственно с первым входом блока и через элемент НЕ с вторым входом блока, первьш и вто40 три элемента ИЛИ, два элемента ИЛИпередатчик, элемент КЕ и элемент задержки, причем синхровходы первого- .третьего триггеров подключены к выходу четвертого триггера, а выходы рой входы элемента ИЛИ соединены со- 5 к группе входов дешифратора, вьгходы

ответственно с прямыми выходами пер-, вого и второго триггеров управления чтением, а выход - с первым выходом блока, счетные входы первого и второго триггеров управления чтением подключены соответственно к третьему входу блока и выходу элемента И, прямой выход второго триггера управления чтением соединен с вторым выходом блока, а инверсный выход и вход сброса - соответственно с входом сброса и инверсным входом первого триггера управления чтет нием.

первого, второго и третьего элемен тов И соединены соответственно с ин- Лормационными входами второго и третьего триггеров и входами сброса че

50 вертого триггера, первый, -второй и третий входы четвертого элемента И - соединены соответственно с первым, вторым и третьим выходами дешифратора, а выход - с первым входом перво

го элемента ИЛИ, входы первого, вто рого и третьего приемников группы я ляются соответственно третьим, четвертым и пятым входами первого узла анализа, выход первого приемника

709

12

3. Устройство по П.1, отличающееся тем, что первый блок дешифрации управляющих сигналов содержит два узла анализа, мультиплексор и элемент КПИ, причем первый и второй входы первого узла анализа являются соответственно четвертым и третьим входами блока, а третий, чет- вертьш и пятьш входы образуют первый вход блока, группа адресно-информационных входов мультиплексора подключена к первому выходу второго узла анализа, первым входом подключенного к выходу элемента ИЛИ и шесто- 5 му выходу блока, второй и третий входы второго узла анализа и первый вход элемента РШИ образуют пятый вход блока, второй вход элемента ИЛИ является шестым входом блока, первый и второй выходы первого узла анализа соединены соответственно с четвертым входом второго узла анализа и третьим выходом блока и с первым выходом бло0

25

30

ка, а третий и четвертый выходы - соответственно с пятым, входом второго узла анализа и вторым выходом блока, второй выход второго узла анализа подключен к четвертому выходу блока, шестой вход - к выходу мультиплексора и седьмому выходу блока, а седьмой и входы - соответственно к второму входу блока и к пятому выходу первого узла анализа, пятый, шестой и седьмой входы которого

35 образуют пятый выход блока, а восьмой выход является восьмым выходом блока, причем первый узел анализа содержит пять элементов И, четыре триггера, дешифратор, группу приемников,

40 три элемента ИЛИ, два элемента ИЛИНЕ передатчик, элемент КЕ и элемент задержки, причем синхровходы первого- .третьего триггеров подключены к выходу четвертого триггера, а выходы к группе входов дешифратора, вьгходы

первого, второго и третьего элемен. тов И соединены соответственно с ин- ормационными входами второго и третьего триггеров и входами сброса четвертого триггера, первый, -второй и третий входы четвертого элемента И - соединены соответственно с первым, вторым и третьим выходами дешифратора, а выход - с первым входом первого элемента ИЛИ, входы первого, второго и третьего приемников группы являются соответственно третьим, четвертым и пятым входами первого узла анализа, выход первого приемника

13

группы соединен с первыми входами третьего элемента И и первого и второго элементов ИЛИ-НЕ, выходы которых являются соответственно первым и третьим выходами первого узла анали- за, вмкод второго приемника группы соединен с вторым входом третьего элемента И, вторым входом первого и первьм входом второго элементов ИЛИ, выходы которых являются соответствен но четвертым и восьмым выходами первого узла анализа, выход третьего приемника группы соединен с синхро- входом четвертого триггера, первые входы первого, второгЬ и пятого элементов И образуют второй вход первого узла анализа, информационный вход первого триггера соединен с выходом пятого элемента И, второй вход которого подключен к вторым входам второго элемента И и первому входу первого узла анализа, первьй, второй и третий выходы дешифратора и выход передатчика являются соответственно пятым, седьмым, шестым и вторым выходами первого узла анализа, вторые входы второго и первого элементов ИЛИ-НЕ соединены соответственно с вторым и первым выходами дешифратора, а выходы - соответственно с первым входом третьего элемента ИЛИ и через элемент задержки с вторым входом третьего элемента ИЛИ, выходом и третьим входом подключенного соответственно к входу передатчика и через элемент НЕ - к выходу первого элемента ИЛИ, второй вход второго элемента ИЛИ соединен с первым выходом дешифратора, причем второй узел анализа содержит три триггера,входы сброса и синхровходы которых образуют соответственно седьмой и первый - третий входы второго узла анализа, три элемента И-НЕ, выходы которых образуют первьй выход второго узла анализа, три элемента И и элемент ИЛИ, первый, второй и третий входы которого подключены соответственно к выходам первого - третьего элементов И, первые входы первых элементов И-НЕ и И соединены соответственно с выходами первого и второго триггеров, первые входы вторых элементов И-НЕ и И соединены соответственно с инверсным и прямым выходами второго триггера, второй вход первого и первый и второй входы тртьего элемента И-HR соединены соответственно с инверсным выходом тре

5 О 8709.14

тьего триггера и выходами первого и второго триггеров, второй вход второго элемента И-НЕ, четвертый и пятый входы и выход элемента ИЛИ явля

тым и пятым входами и вторым выходом второго узла анализа, вторые входы первого и второго элементов И и первьй и второй входы третьего элемента И образуют ше стой вход второго узла анализа.

4, Устройство по П.1, о т л и - ч ающе е с я тем, что второй блок дешифрации управляющих сигналов содержит узел анализа и три элемента И, выходы которых являются соответственно вторым, третьим и первым входами блока, первый, второй и третий - пятьй входы узла анализа образуют соответственно второй и пер- - вьй входы блока, второй, третий и гчетвертьй выходы подключены соответ- ственно к первым входам первого - третьего элементов И, пятьй - седьмой входы узла анализа образуют шестой выход блока, а восьмой выход соединен с вторыми входами первого - третьего элементов И, причем узел анализа содержит девять триггеров, девять элементов И, шесть элементов ИЖ, генератор импульсов, два элемента задержки, распределитель импульсов, два элемента И-НЕ и эле- мент -НЕ, причем тактовьй и разрешающий входь распределителя импульсов, подключены соответственно к выходам генератора импульсов и первого триггера, вход сброса которого соединен с третьим входом узла анализа, первьй выход распределителя импульсов подключен к первым входам первого и второго элементов ИЛИ, выходами соединенных соответственно с синхро- входами второго и третьего триггеров, и через первьй элемент задержки - с синхровходом четвертого триггера, прямой выход которого подключен к первому входу третьего элемента ИЛИ, вторым входом подключенного к выходу первого элемента И, первьй вход которого соединен с первым входом второго элемента И и выходом четвертого элемента ИЛИ, .первым и вторым входами подключенного соответственно к выходам второго и третьего триггеров, выходы которых, второй выход распределителя импульсов, прямые выходы четвертого - ше

to

15

стого триггеров и выходы пятого элемента ИЛИ и третьего элемента И являются соответственно вторым, третьим, восьмым, первым, пятым, шестым четвертым и седьмым выходами узла анализа, информационные входы пятого и шестого триггеров соединены соответственно с выходами третьего элемента ИЛИ и второго элемента И,син- хровходы - с третьим выходом распре- деяителя импульсов, а входы сброса - с третьим входом узла анализа и через второй элемент задержки - с син- хровходом первого триггера, установоч- ный вход и вход сброса седьмого триг- -З

гера соединены соответственно с инверсными выходами шестого и пятого триг геров, а прямой выход - с первым входом шестого, элемента ИЛИ, вторым и третьим входами подключенного COOT- 20 ветственно к прямому выходу четвертого триггера и четвертого элемента И, первый и второй входы которого соединены соответственно с прямыми выходами восьмого и девятого триггеров, входы сброса которых подключены к выходу элемента НЕ и первым входам пятого и шестого элементов И, выходами соединенных соответственно с входами сброса второго и третьего триггеров, а вторыми входами - соответственно с выходами первого и вто- рого элементов И-НЕ, первые входы которых соединены соответственно с выходами третьего и второго триггеров, 35 информационный вход второго триггера

додкпючен к выходу шестого элемента

12887

25

30

to

- -З

2035

8870916

ИЛИ, четвертый вход которого соединен с выходом третьего триггера, инфор- мациоиньм входом подключенного к выходу седьмого элемента И, первый вход которого соединен с выходом второго триггера, а второй и третий входа -.соответственно с инверсными выходами седьмого и девятого триггеров, первые входы восьмого и девятого элементов И соединены с прямым выходом пятого триггера, вторые входы - со- , ответственно с прямым и инверсным выходами девятого триггера, третьи входы - соответственно с выходами второго и третьего триггеров, а выход - соответственно с первым и вторым входами пятого элемента ИЛИ, первый вход третьего элемента И подключен к выходу третьего триггера, а второй вход - к вторым входам первого элемента И-НЕ и второго элемента ИЛИ и к четвертому входу узла анализа, инверсньй выход и вход установки восьмого триггера соединен соответственно с информационным входом и инверсным выходом четвертого триггера, входом сброса соединенного с выходом элемента НЕ, подключенного входом к четвертому входу узла анализа, вторые входы первого элемента ИЛИ и второго элемента И-НЕ соединены с пятым входом узла анализа, синхровход девятого триггера соединен с четвертым входом узла анализа, вторые входы первого и второго элементов Исоединены соответственно с первьми вторым входами узла анализа.

25

30

04

tr, sq- sj.-

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения канала ввода-вывода с абонентом | 1989 |

|

SU1695312A1 |

| Устройство для сопряжения ЭВМ с внешним устройством | 1985 |

|

SU1295405A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Устройство для сопряжения внешних устройств с электронной вычислительной машиной | 1983 |

|

SU1100615A1 |

| Устройство для сопряжения ЭВМ с линиями связи | 1988 |

|

SU1536393A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1987 |

|

SU1472913A1 |

| Устройство для сопряжения процессора с устройствами ввода-вывода | 1983 |

|

SU1129602A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1988 |

|

SU1605241A1 |

| Устройство для сопряжения процессораС уСТРОйСТВАМи ВВОдА-ВыВОдА | 1979 |

|

SU845155A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1990 |

|

SU1728867A1 |

Изобретение относится к области вычислительной техники и может быть применено в системах управления и контроля быстропротекающих технологических процессов. Целью изобретения является повышение пропускной способности устройства. Цель достигается тем, что в устройство, содержащее блок прерываний, мультиплексор данных, блок шинных формирователей, дешифратор адреса, первый блок дешифрации управляющих сигналов, узел элементов И, регистр состояния, выходной буферный регистр и коммутатор, состояния, введены два регистра обмена с внешними устройствами, коммутатор регистров обмена, второй блок дешифрации управляющих сигналов, блок синхронизации чтения, три узла элементов ИЛИ, дешифратор направления ввода-вывода, дешифратор команду состояния, блок контроля четности,два элемента ИЛИ, два блока приемопередатчиков и формирователь импульса записи. 3 з.п, ф-лы, 6 ил. с S йл

| Устройство для обмена информацией | 1979 |

|

SU851388A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения источников и приемников с магистралью | 1984 |

|

SU1252788A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-07—Публикация

1985-02-27—Подача