содержит формирующий блок 1, блок 2 управления, блок 11 выявления знака, инвертор 12, элементы 13, 14 И, триггеры 15, 16,вентили 17, Т8,счетчики 19, 20,элементы 21,22 ИЛИ,блоки23 и 24 элементов И,генератор 25 опорных частот,процессор 26,триггеры27, 28,счетчики 29, 30 переполнений,дешифраторы 31, 32, сумматор 33. Введение блоков 34, 35 компенсации постоянньк составляющих гармонических сигналов позволяет измерять фазовые сдвиги гармонических сигналов, превышающих амплитуду постоянных составляющих. Блоки 34, 35 содержат соответственно запоминающие детекторы 36, 57 максимальных значений сигнапа, запоминающие детекторы 38, 39 минимальных значений сумматоры-делители 40,41. Блок 2 управления включает формирователи 3,4 одиночных импульсов, элементы 5, 6 И, триггеры 7-9 элемент 10 ИЛИ. Применение в блоках компенсации постоянных составляющих запоминающих амплитудных детекторов позволяет компенсировать .постоянные составляющие за время, равное периоду входных гармонических сигналов, что не приводит к заметному ухудшению быстродействия. .1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазометр | 1982 |

|

SU1075186A1 |

| Анализатор частотного спектра | 1980 |

|

SU900209A1 |

| Измерительный двухфазный генератор | 1987 |

|

SU1442931A1 |

| Радиоимпульсный фазометр | 1985 |

|

SU1257558A1 |

| Широкополосный цифровой фазометр | 1990 |

|

SU1746325A1 |

| ЦИФРОВОЙ МНОГОКАНАЛЬНЫЙ СИНТЕЗАТОР СЕТКИ ЧАСТОТ | 1995 |

|

RU2108655C1 |

| Цифровой фазометр | 1980 |

|

SU935818A1 |

| Цифровой фазометр мгновенных значений | 1985 |

|

SU1320770A1 |

| Устройство для измерения фазовых сдвигов | 1984 |

|

SU1226341A1 |

| Способ измерения фазового сдвига между двумя гармоническими сигналами и устройство для его осуществления | 1988 |

|

SU1596272A1 |

Изобретение относится к измерительной технике; Может быть использовано в автоматизированных системах контроля. Цель изобретения - повышение точности и расширение функциональных возможностей без ограничения частотного диапазона. Устройство ЛКй5Э Сл ,05 N5

1

Изобретение относится к измерительной технике и может быть использовано в автоматизированных системах контроля и является усовершенствованием устройства по авт.св. W 1075186

Цель изобретения - повьшение точности и расширение функциональных возможностей устройства без ограничения частотного диапазона..

. Указанная цель достигается введением блоков компенсации постоянных составляющих гармонических сигналов, что позволяет измерять фазовьш сдвиги гармонических сигналов, имеющих постоянные составляклцие.

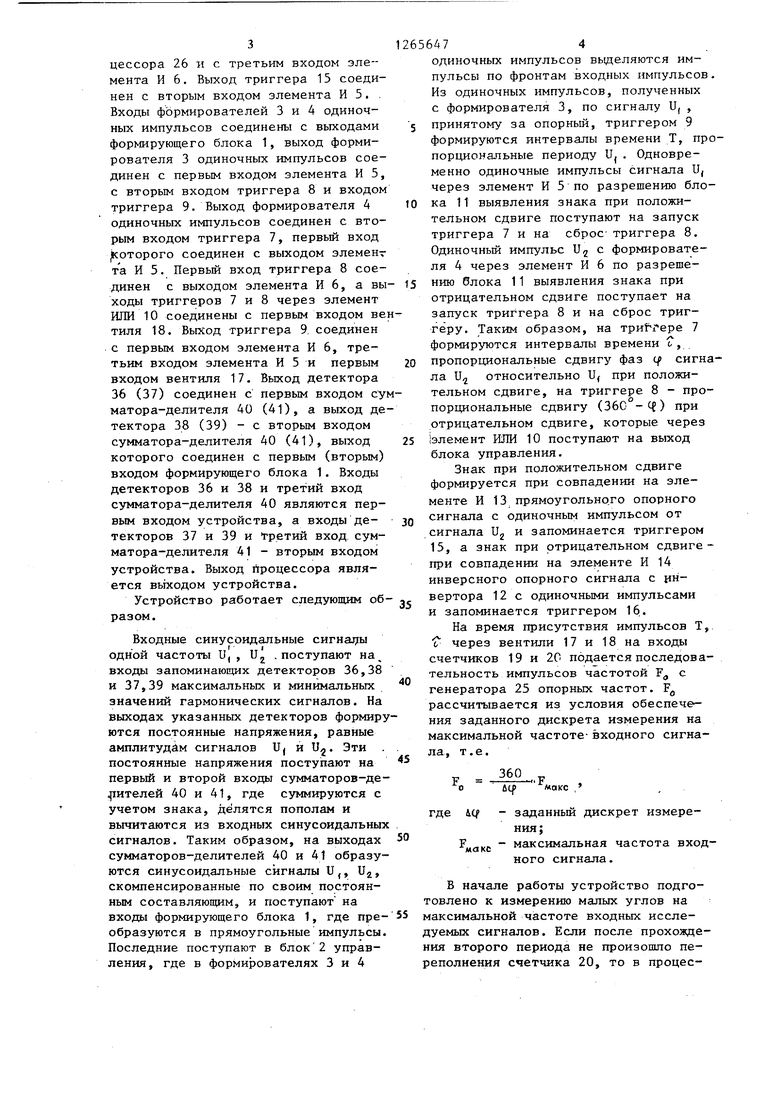

На чертеже приведен структурная схема устройства.

Устройство содержит формирующий блок 1, блок 2 управления, формирователи 3 и 4 одиночных импульсов, элементы И 5 и 6, триггеры 7-9, элемент ИЛИ 10, блок 11 выявления знака, инвертор 12, элементы И 13 и 14, триггеры 15 и 16, вентили 17 и 18, счет-чики 19 и 20, элементы ИЖ 21 и 22, блоки 23 и 24 элементов И, гейератор 25 опорных частот, процессор 26, триггеры 27 и 28, счетчики 29 и 30 переполнений, дешифраторы 31 и 32, сумматор 33, блоки 34 и 35 компенсации постоянных составляющие, запоминающие детекторы 36 и 37 максимальных значений сигнала, запоминающие детекторы 38 и 39 минимальных значений , сумматоры-делители 40 и 41..

Формирующий блок 1 соединен через блок управления с входами вентилей 17 и 18, второй вход вентиля 17 (18) соединен через элемент ИЛИ 21 (22)

и через блок 23 (24) элементов И с генератором 25 опорных частот. Выход вентиля 17 (18) соединен с входом счетчика 19 (20). Счетчик 29 (30) переполнений соединен выходами с

дешифратором. 31 (32), выходы которого соединены с вторыми входами блока 23 (24) элементов И.

Входы сумматора 33 соединены с

выходами счетчиков 29 и 30 переполнений, а выход - с входом процессора 26. Выходы переполнений счетчиков 19 и 20. соединены с входами триггеров 27 и 28 переполнения соответ /гвенно, а выходы последнщ; с входами счетчиков 29 и 30 переполнений, а также с входами сброса счетчиков 19 и 20. Вьгходы счетчиков 19 и 20 соединены с входами процессора 26, выход которого соединен с выходными клеммами устройства. Инвертор 12 соединен своим входом с первым выходом формирующего блока 1 и с цервым входом элемента И 13,

а выходом - с первьм входом элемеГнта И 14. Вторые входы элементов И 13 и 44 соединены с выходом формирователя , а выходы - с входами триггеров 15 и 16. Выход триггера 16 соединен с знаковым входом прОцессора 26 и с третьим входом элемента И 6. Выход триггера 15 соединен с вторым входом элемента И 5, . Входы формирователей 3 и 4 одиночных импульсов соединены с выходами формирующего блока 1, выход формирователя 3 одиночных импульсов соединен с первым входом элемента И 5 с вторым входом триггера 8 и входом триггера 9. Выход формирователя 4 одиночных импульсов соединен с вторым входом триггера 7, первый вход (которого соединен с выходом элемент та И 5, Первьш вход триггера 8 соединен с выходом элемента И 6, а вы ходы триггеров 7 и В через элемент ИЛИ 10 соединены с первым входом ве тиля 18. Выход триггера 9. соединен с первым входом элемента И 6, третьим входом элемента И 5 и первым входом вентиля 17. Выход детектора 36 (37) соединен с первым входом су матора-делителя 40 (41), а выход де тектора 38 (39) - с вторьм входом сумматора-делителя 40 (41), выход которого соединен с первым (вторым) входом формирующего блока 1. Входы детекторов 36 и 38 и третий вход сумматора-делителя 40 являются пер- входом устройства, а входы детекторов 37 и 39 и Третий вход сумматора-делителя 41 - вторым входом устройства. Выход йроцессора является вьЬсодом устройства. Устройство работает следующим об разом. Входные синусоидальные сигнал ы одной частоты U,, U .поступают на входы запоминающих детекторов 36,38 и 37,39 максимальных и минимальных значений гармонических сигналов. На выходах указанных детекторов формиру ются постоянные напряжения, равные амплитудам сигналов U, и U. Эти . постоянные напряжения поступают на первый и второй входы сумматоров-де ителей 40 и 41, где суммируются с учетом знака, делятся пополам и вычитаются из входных синусоидальных сигналов. Таким образом, на выходах сумматоров-делителей 40 и 41 образуются синусоидальные сигналы U,, Ug, скомпенсированные по своим постоянным составляющим, и поступают на входы формирующего блока 1, где преобразуются в прямоугольные импульсы. Последние поступают в блок2 управления, где в формирователях 3 и 4 6474 одиночных импульсов выделяются импульсы по фронтам входных импульсов. Из одиночных импульсов, полученных с формирователя 3, по сигналу U,, принятому за опорный, триггером 9 формируются интервалы времени Т, пропорциональные периоду Uj . Одновременно одиночные импульсы сигнала U, через элемент И 5 по разрешению блока 11 выявления знака при положительном сдвиге поступают на запуск триггера 7 и на сброс- триггера 8. Одиночный импульс Uj с формирователя 4 через элемент И 6 по разрешению блока 11 выявления знака при отрицательном сдвиге поступает на запуск триггера 8 и на сброс триггеру. Таким образом, на три 1ере 7 формируются интервалы времени С, пропорциональные сдвигу фаз cf сигнала U;2 относительно Uf при положительном сдвиге, на триггере 8 - пропорциональные сдвигу (360 - Ч) при отрицательном сдвиге, которые через элемент ИЛИ 10 поступают на выход блока управления. Знак при положительном сдвиге формируется при совпадении на элементе И 13 прямоугольного опорного сигнала с одиночным импульсом от сигнала U и запоминается триггером 15, а знак при отрицательном сдвигепри совпадении на элементе И 14 инверсного опорного сигнала с цнвертора 12 с одиночными импульсами и запоминается триггером 16На время присутствия импульсов Т, Г через вентили 17 и 18 на входы счетчиков 19 и 20 подается последовательность импульсов частотой F с генератора 25 опорных частот. F рассчитывается из условия обеспечения заданного дискрета измерения на максимальной частоте- входного сигнала, т.е. где Щ - заданный дискрет измерения;макс максимальная частота входного сигнала. В начале работы устройство подгоовлено к измерению малых углов на аксимальной частоте входных исслеуемых сигналов. Если после прохождеия второго периода не произошло пееполнения счетчика 20, то в процессор 26 запишется двоичный код N,, со ответствующий числу импульсов частот F. в измеряемом интервале Г . Если при этом не происходит переполнения счетчика 19, в процессор 26 запишетс также и числовой код N, соответствующий числу импуо ьсов частоты Fg в периоде опорного сигнала В процессо ре проводятся операции умножения и- . деления чцсеп, представленных числовыми кодами, по формуле NX 360 где а - поправочный коэффициент, рав ный отношению частот квантования. В рассмотренном случае квантующие частоты одинаковы, т.е. а-1. На выходе процессора цифровой код соответ ствует значению сдвига фаз ср в градусах. Если после первого измерения произошло переполнение счетчика 19, которое фиксируется триггером 27 переполнения, импульс переполнения обнуляет счетчик 19 и записывается счетчиком 29. На соответствующем вы- Йоде дешифратора 31 появляется сигнал, разрешающий прохождение частоты Fo/2 через один из блоков элементов И 23, элемент ИЛИ 21 на вентиль 17 и далее на вход счетчика 19 в течение третьего исследуемого периода опорного сигнала U. Цикл работы повторяется до тех пор, пока не будет выбрана частота Fp/2 из ряда частот . F, F,/2,..., Fo/2, которая не вызовет переполнения счетчика 19. Аналогично происходат выбор частоты квантования временного интервала t вентилем 18, счетчиком 20, триггером 28 переполнения, дешифратором 32 блоком 24 элементов И, элементом ИЖ 22. Пусть частоты квантования интервала Т .оказалась тог; коэффициент отношения частот Pg -Коэффициент вычисляется в сумматоре 33 и представляет собой разность вух двоичных кодов, хранящихся в счетчиках 29 и 30 переполнений после . окончательного выбора частот квантования . Результат вычитания записывается в процессор. Таким образом, в зависимости от величины угла, знака угла и частоты входного сигнала происходит раздельный автоматический выбор частот квантования интервалов времени и Т. Применение в предлагаемом фазометре блоков компенсации постоянных составляющих гармонических сигналов позволяет измерять фазовые сдвиги сигналов, превьш1ающие амплитуду постоянных с оставляющих,, а такие сигналы нередко встречаются при измерении. При этом не сужается диапазон рабочих частот. Ф о рмула изобретения Цифровой фазометр по авт. сб. № 1075186, отличающийся тем, что, с целью расширения функциональных возможностей и повьштения точности без сужения частотного диапазона, в него введены два блока. компенсации постоянных составляющих гармонических сигналов, входы которых являются первым и вторым информационными входами фазометра, а выходы соединены с первым и вторым входами формируклцего блока, причем каждый из блоков компенсации постоянных составляющих содержит запоминающий детектор минимальных значений гармонического сигнала, запоминающий детектор максимальных значений гармонического сигнала, входы которых являются соответствуюшим входом фазометра, а выходы соединены с первым и вторым входами сумйатора-делит ля, третий вход которого является информационным входом фазометра, а выход сумматора-делителя является выходом 1блока компенсации постоянной составляющей о

| Цифровой фазометр | 1982 |

|

SU1075186A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-10-23—Публикация

1985-03-06—Подача