Фм. /

Изобретение относится к электротехнике, в частности к преобразовательной технике, и может быть использовано для построения быстродействующих стабилизаторов переменного напряжения, работающих от частотнонестабильных сетей.

Цель изобретения - повышение качества стабилизации при колебаниях частоты питающего напряжения.

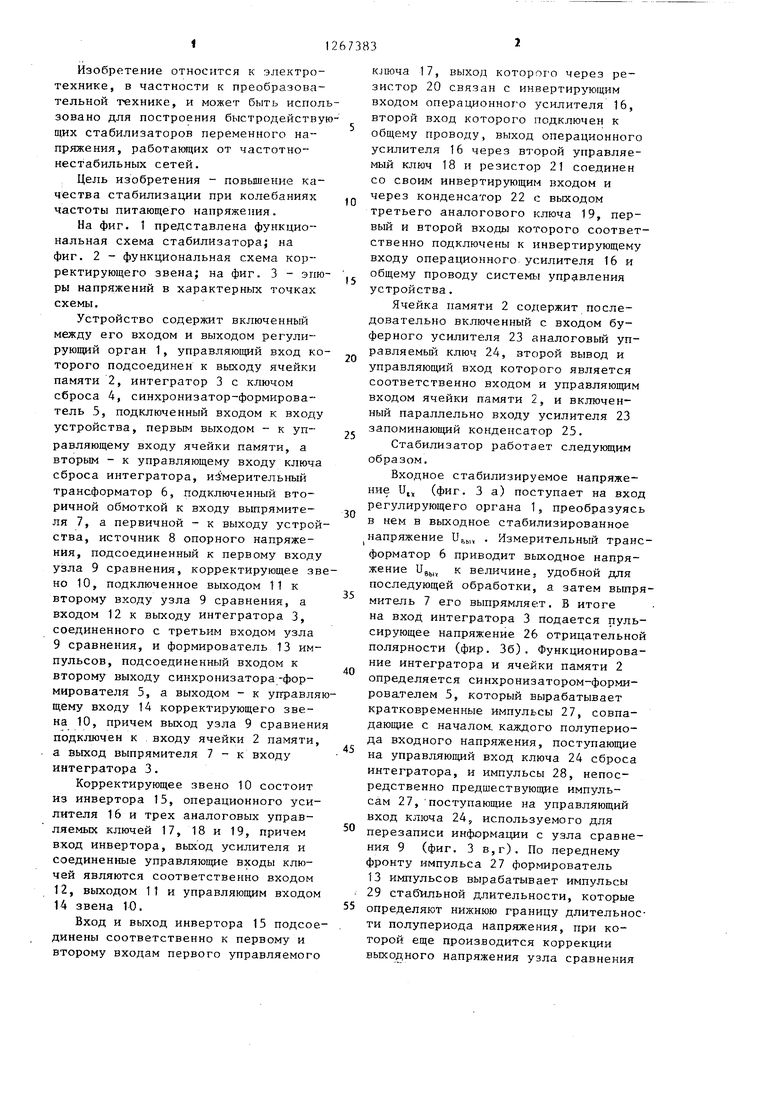

На фиг. 1 представлена функциональная схема стабилизатора; на фиг. 2 - функциональная схема корректирующего звена; на фиг. 3 - эпюры напряжений в характерных точках схемы.

Устройство содержит включенный между его входом и выходом регулирующий орган 1, управляющий вход которого подсоединен к выходу ячейки памяти 2, интегратор 3 с ключом сброса 4, синхронизатор-формирователь 5, подключенный входом к входу устройства, первым выходом - к управляющему входу ячейки памяти, а вторым - к управляющему входу ключа сброса интегратора, иймерительный трансформатор 6, подключенный вторичной обмоткой к входу вьшрямителя 7, а первичной - к выходу устройства, источник 8 опорного напряжения, подсоединенный к первому входу узла 9 сравнения, корректирующее звно 10, подключенное выходом 11 к второму входу узла 9 сравнения, а входом 12 к выходу интегратора 3, соединенного с третьим входом узла 9 сравнения, и формирователь 13 импульсов, подсоединенный входом к второму выходу синхронизатора-формирователя 5, а выходом - к управлящему входу 14 корректирующего звена 10, причем выход узла 9 сравнени подключен к входу ячейки 2 памяти, . а выход выпрямителя 7 - к входу интегратора 3.

Корректирующее звено 10 состоит из инвертора 15, операционного усилителя 16 и трех аналоговых управляемых ключей 17, 18 и 19, причем вход инвертора, выход усилителя и соединенные управляющие входы ключей являются соответственно входом 12, выходом 11 и управляющим входом 14 звена 10.

Вход и выход инвертора 15 подсоединены соответственно к первому и второму входам первого управляемого

KJD04a 17, выход которого через резистор 20 связан с инвертируюгцим входом операционного усилителя 16, второй вход которого подключен к общему проводу, выход операционного усилителя 16 через второй управляемый ключ 18 и резистор 21 соединен со своим инвертирующим входом и через конденсатор 22 с выходом третьего аналогового ключа 19, первый и второй входы которого соответственно подключены к инвертирующему входу операционного усилителя 16 и общему проводу системы управления устройства.

Ячейка памяти 2 содержит последовательно включенный с входом буферного усилителя 23 аналоговый управляемьм ключ 24, второй вывод и управляющий вход которого является соответственно входом и управляющим входом ячейки памяти 2, и включенный параллельно входу усилителя 23 запоминающий конденсатор 25.

Стабилизатор работает следукяцим образом.

Входное стабилизируемое напряжение и,, (фиг. 3 а) поступает на вход регулирующего органа 1, преобразуясь в нем в выходное стабилизированное напряжение Ь,, . Измерительный трансформатор 6 приводит выходное напряжение Ujbi, к величине, удобной для последующей обработки, а затем выпрмитель 7 его выпрямляет. В итоге на вход интегратора 3 Подается пульсирующее напряжение 26 отрицательно полярности (фир. 36). Функционирование интегратора и ячейки памяти 2 определяется синхронизатором-формирователем 5, который вырабатывает кратковременные импульсы 27, совпадаю1дие с началом, каждого полупериода входного напряжения, поступающие на управляющий вход ключа 24 сброса интегратора, и импульсы 28, непосредственно предшествующие импульсам 27,поступающие на управляющий вход ключа 24, используемого для

перезаписи информации с узла сравнения 9 (фиг. 3 в,г). По переднему фронту импульса 27 формирователь 13 импульсов вырабатывает импульсы 29 стабильной длительности, которые определяют нижнюю границу длительности полупериода напряжения, при которой еще производится коррекции вькодного напряжения узла сравнения

31

(фиг. Зд). На фиг, Зе показана форма выходного напряжения 30 интегратора 3, который перед началом цикла измерения обнуляется импульсами 27 посредством ключа сброса 4. Импульсы 29 поступают с формирователя 13 через управляющий вход 14 корректирующего звена 10 на управляющие входы ключей 17, 18, 19, при этом ключ 17 подключает резистор 20 к выходу инвертора 15, ключ 18 замыкает цепь обратной связи усилителя 16 через резистор 21, а ключ 19 подключает конденсатор 22 к общему проводу. На фиг. 3 ж показано напряжение 31 в точке соединения ключа 1 7 и резистора 20, поступающее на вход операционного усилителя 16, который до момента времени t, работ в качестве инвертирующего усилителя с коэффициентом усиления, равным единице, что выполняется при равенстве сопротивлений резисторов 20 и 21. При этом напряжение 28 (фиг. З на конденсаторе 22 полностью повторяет напряжение 30 на выходе интегратора 3. После окончания импульса напряжения 29, т.е. с момента времени t{ , усилитель 16 переходит в режим интегрирования, так как ключ подключает конденсатор 22 к его инвертирующему входу, а ключ 18 размыкается. Так как одновременно напряжение на входе этого интегратора меняет полярность (фиг. Зж), то напряжение на выходе корректирующего звена 10 линейно уменьшается до

окончания полупериода напряжения (фиг. Зз интервал ). Это напряжение пропорционально интервалу времени , представляющем отклонение длительности полупериода от некоторого эталонного его значения, задаваемого формирователем импульсов 13. Суммирование основного напряжения т.е. напряжение 30 интегратора 3 (U ) и корректирующего напряжения 32 (Ua.pp ) с соответствующими коэффициентами КЗ и К2 производится в узле сравнения 9, представляющем собой суммирующий усилитель, к одному из выводов которого подается отрицательное опорное напряжение Uj, (фиг. 3 и).

Выходное напряжение 33 узла сравнения 9 в моменты прохождения импульсов 28 фиксируется на запоминающем конденсаторе 25 и в дальнейшем

3

используется в качестве управляющего напряжения 34 и,„р регулирующего органа 1 (фиг. Зк).

Таким образом, устройство фактически реализует операцию приближенного деления выходного напряжения интегратора, пропорционального вольтсекундной площади полупериода его выходного напряжения (т.е. зависящего от длительности полупериода), на длительность периода, чем обеспечивается независимость управляющего напряжения регулирующего органа от изменения частоты. Стабилизатор с

описанным измерительным органом

Q

обеспечивает хорошие точностные параметры выходного напряжения при допустимом диапазоне изменения частоты не более t 6-8% от ее номинального значения, так как перекрывается реальный диапазон отклонения частоты промышленных сетей.

Формула изобретения

Стабилизатор переменного напряжения, содержащий включенный между входными и выходными выводами регулирующий орган, управляющий вход которого подсоединен к выходу ячейки памяти, интегратор с ключом сброса, синхронизатор-формирователь, подключенный входом к входным выводам, первым выходом - к управляющему входу

ячейки памяти, а вторым выходом - к управляющему входу ключа сброса интегратора, измерительный трансформатор, подключенный вторичной обмоткой к входу выпрямителя, а первичной

к выходным выводам, источник опорного напряжения, подсоединенный тс одному из входов узла сравнения, отличающийся тем, что, с целью повьш1ения качества стабилизации

при колебаниях частоты питающего напряжения, выход узла сравнения подключен к входу ячейки памяти, выход выпрямителя - к входу интегратора, при этом введены корректирующее звено, подключенное выходом к второму входу узла сравнения, а входом - к выходу интегратора, соединенного с третьим входом узла сравнения, и формирователь импульсов,

подсоединенный входом к второму выходу синхронизатора-формирователя, а выходом - к управляющему входу корректирующего звена, причем кор

| название | год | авторы | номер документа |

|---|---|---|---|

| Стабилизатор переменного напряжения | 1985 |

|

SU1272316A1 |

| Стабилизатор переменного напряжения | 1985 |

|

SU1293716A1 |

| Синхронизированный преобразователь напряжения в частоту | 1986 |

|

SU1691946A1 |

| Стабилизатор переменного напряжения | 1987 |

|

SU1458862A1 |

| Стабилизатор переменного напряжения | 1984 |

|

SU1246064A1 |

| Стабилизатор переменного напряжения | 1984 |

|

SU1180858A1 |

| Стабилизатор переменного напряжения | 1980 |

|

SU935892A1 |

| Стабилизатор переменного напряжения | 1979 |

|

SU845145A1 |

| Детектор огибающей амплитудномодулированных сигналов | 1980 |

|

SU866562A1 |

| Стабилизатор переменного напряжения | 1986 |

|

SU1416953A1 |

Изобретение относится к стабилизированным источникам питания переменного тока. Целью изобретения является повьппение качества стабилизации при колебаниях частоты питающего напряжения. Цель достигается тем, что в стабилизатор введено корректирующее звено 10 и формирователь 13 импульсов. Звено 10 осуществляет операцию умножения выходного напряжения интегратора 3 на величину превышения периода над его минимально возможным значением. При этом устройство реализует операцию приближенного деления выходного напряжения интегратора 3, пропорционального вольтсекувдной площади полупериода его входного напряжения на длительность периода. Этим обеспечивается независимость управ(Л ляющего напряжения регулирующего органа от изменений частоты. 3 ил.

| Стабилизатор переменного напряжения | 1980 |

|

SU935892A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Стабилизатор переменного напряжения | 1982 |

|

SU1107111A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1986-10-30—Публикация

1985-06-24—Подача