(54) СТАБИЛИЗАТОР ПЕРЕМЕННОГО НАПРЯЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Стабилизатор переменного напряжения | 1979 |

|

SU845145A1 |

| Стабилизатор переменного напряжения | 1982 |

|

SU1107111A1 |

| Источник питания переменным напряжением | 1976 |

|

SU699505A1 |

| Стабилизатор переменного напряжения | 1985 |

|

SU1267383A1 |

| Стабилизатор переменного напряжения | 1983 |

|

SU1166080A1 |

| Стабилизатор переменного напряжения | 1985 |

|

SU1272316A1 |

| Устройство регулирования трехфазного переменного напряжения | 1976 |

|

SU688901A1 |

| Стабилизатор переменного напряжения | 1976 |

|

SU688902A1 |

| Стабилизатор переменного напряжения | 1985 |

|

SU1293716A1 |

| Стабилизатор переменного напряжения | 1987 |

|

SU1458862A1 |

I

Изобретение относится к электротехнике; в частности к стабилизаторам напряжения, и может быть использовано в качестве источника питания для аппаратуры радиоэлектроники, средств связи, вычислительных устройств, автоматических установок, особенно в тех случаях, где требуется высокое качество стабилизации напряжения.

Известен стабилизатор переменного напряжения, содержащий регулирующий орган с блоком управления, выпрямитель, входом по ислюченный параллельно нагрузке, а выходом - к измерительному органу, выполненному на двух интеграторах с обнулением, осуществляемым ключевыми элементами, источник задающего напряжен ния, схему сравнения, блок компенсации частотной зависимости, включенный в цепь источника задающего напряжения, и синхронизатор, подключенный между зажимами питающей сети и входом формирователя импульсов Г13 .

Упом$шутый блок компенсации частот ной зависимости выполнен в виде последовательно соединенных модулятора, интегратора, выпрямителя, фильтра и усили-геля. Такое выполнение блока компенсации частотной зависимости (наличие сглаживающего фильтра) приводит к существенному осижению быстродействия и точности стабилизации напряжения в динамических режимах (быстрое изменение частоты питающего напряжения) и сужает область применения таких стабилизаторов.

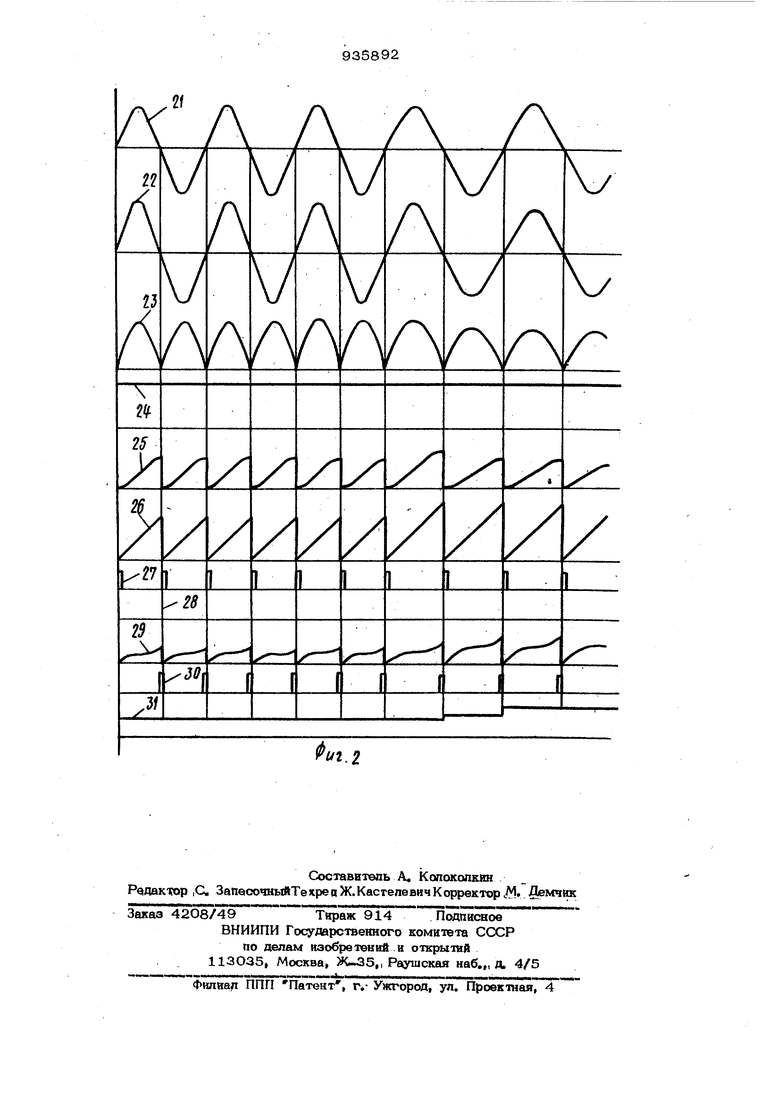

Наиболее близким по технической сущности к изобретению является стабилизатор переменного напряжения, содержащий регулирующий орган, включенный между входными и выходными выводами, выпрямитель, подсоединенный к выходу регулирующего органа, источник задающего напряжения, интегратор с обнулением на ключевом элементе, ячейку памяти, соотоящую из конденсатора, подключе1шого параллельно входу буферного усилителя и последовательного ключа, установлен- ного на входе ячейки памяти, синхрс«иза тор, подключенный между входными выводами и входом формирователя вмпульсюв Г2 . Однако в известном стабилизаторе интегрирование выходного и задающего напряжений происходит поочередно, быстро- действие стабилизатора характеризуется запаздыванием, равным периоду питающего нaпpя keния, что приводит к они- . жению точности стабилизации на интервале запаздывания. Цель изобретения - повышение бысрродействия и точности стабилизации выходного напряжения,, Поставленная цель достигается тем, что 6 стабилизатор переменного напряжения, содержащий регулирующий орган, включенный между входными и выходными выводами, выпрямитель, подсоединенный к выходу регулирующего органа, источник задающего напряжения, интегратор с обнулением на ключевом элементе, ячейку памяти, состоящую из конденсатора, под ключенного параллельно входу буферного усилителя и последовательного ключа, уотановленного на входе ячейки памяти, синхронизатор, подключенный между входными выводами и входом формирователя импульсов, введены второй интегратор с обнулением и узел сравнения, вход Первого интегратора подсоединен к въткоау выпрямителя, вход второго интегратора к выходу источника задающего напряжения а выходы интеграторов через узел срав нения и ячейку памяти подключены к равляющему входу регулирующего органа, при этом оД1ш выход упомянутого форми рователя импульсов подсоединен к цепи управления последовательного 1шюча ячей« ЕЙ памяти, а другой вькод - к цепям управления ключевых элементов интеграторов. На фиг„ 1 приведена функциональная схема стабилизатора переменного напряжения; на фиг. 2 показаны временные диаграммы, иллюстрирующие его работу. Стабилизатор переменного напряжения содержит регулирующий орган 1 с нагруэ кой 2 на выходе, параллельно которой подсоединен вход выпрямителя 3. К вы- ходу выпрямителя 3 подключен вход первого интегратора 4, а вход второго йнтег ратора S подсоединен к выходу источника задающего напряжения 6, Интеграторы 4 .и 5 могут быть аыпол11 ень,(Например, на базе операционных усилителей 7 и 8, в цепи обратной связи которых установлены ижденсаторы 9 и 10, зашуптированные ключевыми элементами 11 и 12. Выходы интеграторов 4 и 5 через узел сравнения 13 и ячейку памяти 14, содержащую последовательный кточ 15, конденсатор 16, в буферный усилитель 17, подкшоченный к управляющему входу 18 регулирующего органа 1, Параллельно входному выводу подключен вход синхронизатора 19, выходом соединенного со входом формирователя импульсов 20, Один выход формирователя 20 подключен к цепи управления ключа 15 ячейки памяти 14, а другой вькод - к цепям управления разртдных 11 и 12 интеграторов 4 и 5, Стабилизатор работает следующим о&1 разом. Напряжение питающей сети 21 (фиг,2) поступает на вход регулирующего органа 1, преобразуясь после фил1 трации на его выходе в напряжение 22, которое после выпрямления (кривая 23) подается на вход первого интегратора 4. На вход второго интегратора 5 при этом с выхода источника 6 поступает задающее напряжение 24, Выходное выпрямленное напря жение 23 и задающее напряжение 24 в течение каждого полупер«ода питающего напряжения 21 интегрируется интеграторами 4 и 5, преобразуясь на их выходах в напряжения 25 и 26. Обнуление напряжений 25 и 26 производится при замыкании ключей 11 и 12, которое происходит при подаче в их цепи управления с выхода формирователя 2О импульсов 27, сформированных по заднему фронту синхроимпульсов 28, генерируемых синхронизато- . ром 19 при каждом переходе через нуль напряжения 21. Выходные напряжения 25 и 26 интеграторов 4 и 5 подаются на вход узла сравнения 13. Их разность (.кривая 29), получившаяся в результате сравнения, поступает на вход ячейки памяти 14, При подаче в цепь управления ключа 15 ячейки памяти 14 с выхода 4юрмирователя 20 импульсов ЗО, сформированных по переднему фронту синхроимпульсов 28, происходит быстрый заряд (разряд) конденсатора 16 до уровня, соответствующего значению напряжения 29 перед началом его обнуления, В результате этого с выхода ячейки памяти 14 (выхода буферного усилителя 17) на управляющий вход 18 поступает напряжение 31, пропорциональное рааяостй интегра лов от выходного 22 и задающего 24 напряжений, вычисленных за полупериод напряжения питающей сети. При изменении частоты на1фяжения питающей сети 21 шзк1еняются соотве.т ственно уровни напряжений 25 и 26 на выходах интеграторов 4 и 5, что в свою очередь, приводит к изменению сигнапа ошибки 31 с попупериодным запаздыванием, что одновременно 1фиводит к по. вышению точности стабилизации выходного напряжения в динамических режимах. Формула изобретения Стабилизатор переменного напряжения содержащий регулирующий оргаи, вхлк ченный между входными и выходными выводами, вЬтпрямитель, подсоединенньй к выходу регулирующего органа, источник задающего напряжения, интегратор с обнулением на ключевом элементе, ячейку памяти, состоящую из конденсатора, подключенного ко входу буферного усилителя, и последовательногоключа, установленного на входе ячейки памяти, синхронизатор, подключенный между вхо ными выводами и входом формировател импульсов, отличающийся тем что, с целью повышения быстродействия и точности стабилизации выходного напряьжения, в него введены второй интегратор с обнулением и узел сравнения, вход первого интегратора подсоединен к выходу выпрямителя, вход второго интегратора к выходу источника задающего напряжения, а выходы интеграторов через узел сравнения и ячейку памяти подключены к управляющему входу регулирующего о{ гана, при этом один из выходов упомянутого формирователя импульсов подсоединен к цепи управления последовательного ключа ячейки Памяти, а другой его выход - к цепям управления ключевых эле, ментов интеграторов. Источники информации, принятые во внимание при экспертизе , l.Daviee V.Stafeieizator naietf i. 5ТТ OllRq RTTioiRi a re C u8ace.4CCP, 1973, № 2, c. 54-56, рис. 1-3. 2. Авторское свидетельство СССР по заявке М 2793748/24-07, кл. СЗ 05 F 1/16, 1979 (прототип). /Х° Л

2425

А

Z

гr

28

29

дО

/

Авторы

Даты

1982-06-15—Публикация

1980-11-04—Подача