(54) СТАБИЛИЗАТОР ПЕРЕМЕННОГО НАПРЯЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Стабилизатор переменного напряжения | 1980 |

|

SU935892A1 |

| Стабилизатор переменного напряжения | 1985 |

|

SU1267383A1 |

| Стабилизатор переменного напряжения | 1985 |

|

SU1293716A1 |

| Стабилизатор переменного напряжения | 1982 |

|

SU1107111A1 |

| Стабилизатор переменного напряжения | 1985 |

|

SU1272316A1 |

| Источник питания переменным напряжением | 1976 |

|

SU699505A1 |

| Стабилизатор переменного напряжения | 1983 |

|

SU1166080A1 |

| Устройство для контроля и регулирования производительности | 1990 |

|

SU1791032A1 |

| Многоканальный стабилизированный источник вторичного электропитания | 1984 |

|

SU1166085A1 |

| Стабилизатор напряжения | 1988 |

|

SU1561069A1 |

I

Изобретение относится к электротехнике, в частности к стабилизаторам напряжения, и может быть использовано в качестве источника питания для аппаратуры радиоэлектроники, средств связи, автоматических установок, особенно в тех случаях, где требуется высокое качество стабилизации напряжения.

Известен стабилизатор переменного напряжения 1, который содержит регулирующий орган с блоком управления, выпрямитель, подсоединенный параллельно нагрузке, интегратор выпрямленного напряжения, синхронизатор, входом подключенный к зажимам питающей сети, а выходом -к входам формирователей импульсов, и распределитель импульсов.

Недостаток стабилизатора заключается в том, что при отклонении частоты питающей сети от номинального значения существенно снижается точность стабилизации выходного напряжения.

Известен также стабилизатор, содержащий регулирующий орган, вход которого подключен к входным выводам, а выход - к выходным выводам, блок управления, выход которого соединен с управляющим входом регулирующего органа, выпрямитель.

входом подключенный к выходным выводам, интегратор, источник задающего напряжения, распределитель импульсов, первый и второй формирователи импульсов, синхронизатор, входом соединенный с входными выводами, выходом - с входами формирователей импульсов, один выход первого формирователя подключен к входу распределителя импульсов 2.

Недостатком известного устройства являются низкое быстродействие и точность

Q стабилизации, а также сложность конструкции.

Целью изобретения являются повышение быстродействия, точности стабилизации и упрощение стабилизатора.

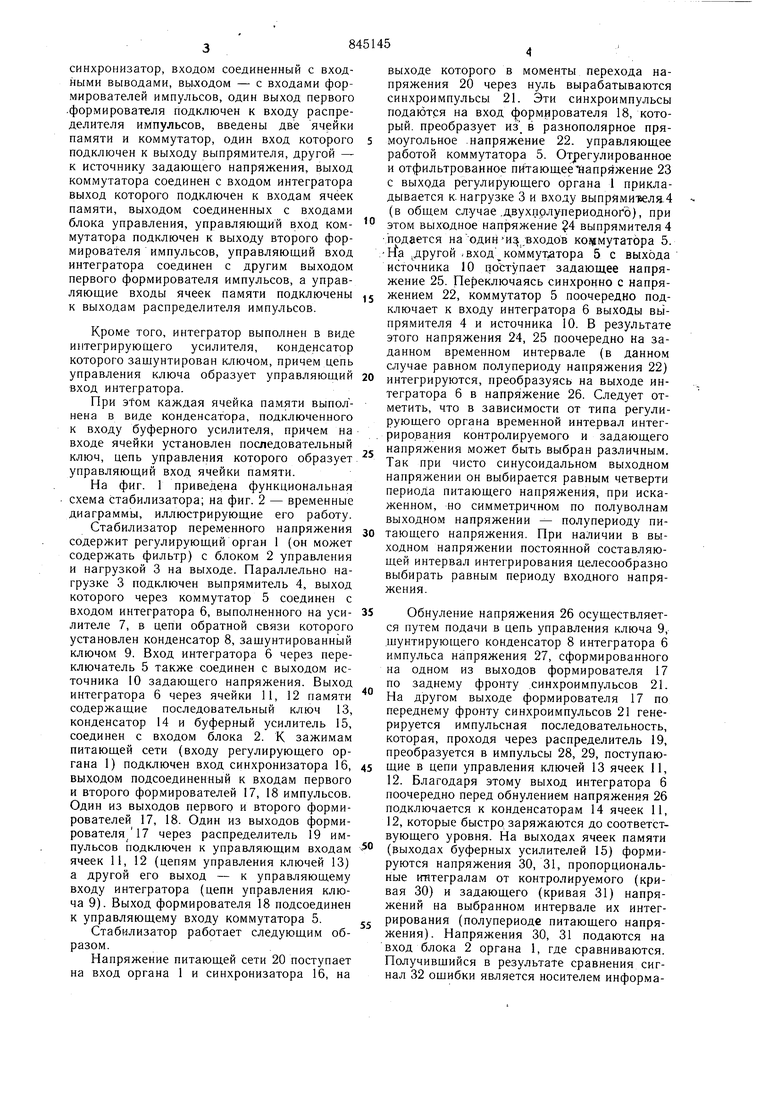

Поставленная цель достигается тем, что

15 в стабилизатор переменного напряжения, содержащий регулирующий орган, вход которого подключен к входным выводам, а выход - к выходным выводам, блок управления, выход которого соединен с управляющим входом регулирующего органа, выпрямитель, входом подключенный к выходным выводам, интегратор, источник задающего напряжения, распределитель импульсов, первый и второй формирователи импульсов. синхронизатор, входом соединенный с входными выводами, выводом - с входами формирователей импульсов, один выход первого .формирователя подключен к входу распределителя импульсов, введены две ячейки памяти и коммутатор, один вход которого подключен к выходу выпрямителя, другой - к источнику задающего напряжения, выход коммутатора соединен с входом интегратора выход которого подключен к входам ячеек памяти, выходом соединенных с входами блока управления, управляющий вход коммутатора подключен к выходу второго формирователя импульсов, управляющий вход интегратора соединен с другим выходом первого формирователя импульсов, а управляющие входы ячеек памяти подключены к выходам распределителя импульсов. Кроме того, интегратор выполнен в виде интегрирующего усилителя, конденсатор которого зашунтирован ключом, причем цепь управления ключа образует управляющий вход интегратора. При этом каждая ячейка памяти выполнена в виде конденсатора, подключенного к входу буферного усилителя, причем на входе ячейки установлен последовательный ключ, цепь управления которого образует управляющий вход ячейки памяти. На фиг. 1 приведена функциональная схема стабилизатора; на фиг. 2 - временные диаграммы, иллюстрирующие его работу. Стабилизатор переменного напряжения содержит регулирующий орган 1 (он может содержать фильтр) с блоком 2 управления и нагрузкой 3 на выходе. Параллельно нагрузке 3 подключен выпрямитель 4, выход которого через коммутатор 5 соединен с входом интегратора 6, выполненного на усилителе 7, в цепи обратной связи которого установлен конденсатор 8, зашунтированный ключом 9. Вход интегратора 6 через переключатель 5 также соединен с выходом источника 10 задающего напряжения. Выход интегратора б через ячейки И, 12 памяти содержащие последовательный ключ 13, конденсатор 14 и буферный усилитель 15, соединен с входом блока 2. К зажимам питающей сети (входу регулирующего органа 1) подключен вход синхронизатора 16, выходом подсоединенный к входам первого и второго формирователей 17, 18 импульсов. Один из выходов первого и второго формирователей 17, 18. Один из выходов формирователя 17 через распределитель 19 импульсов подключен к управляющим входам ячеек 11, 12 (цепям управления ключей 13) а другой его выход - к управляющему входу интегратора (цепи управления ключа 9). Выход формирователя 18 подсоединен к управляющему входу коммутатора 5. Стабилизатор работает следующим образом. Напряжение питающей сети 20 поступает на вход органа 1 и синхронизатора 16, на выходе которого в моменты перехода напряжения 20 через нуль вырабатываются синхроимпульсы 21. Эти синхроимпульсы подаются на вход формирователя 18, который, преобразует из , в разнополярное прямоугольное .напряжение 22. управляющее работой коммутатора 5. Отрегулированное и отфильтрованное питающее йапряжение 23 с выхода регулирующего органа 1 прикладывается к. нагрузке 3 и входу выпрямивеля4 (в общем случае .двухпрлупериодногд), при этом выходное напряжение 4 выпрямителя 4 подается на одини.входов коммутатора 5. rfa другой вход коммутунтора 5 с выхода источника 10 поступает задающее напряжение 25. Переключаясь синхронно с напряжением 22, коммутатор 5 поочередно подключает к входу интегратора 6 выходы вь1прямителя 4 и источника 10. В результате этого напряжения 24, 25 поочередно на заданном временном интервале (в данном случае равном полупериоду напряжения 22) интегрируются, преобразуясь на выходе интегратора 6 в напряжение 26. Следует отметить, что в зависимости от типа регулирующего органа временной интервал интегрирования контролируемого и задающего напряжения может быть выбран различным. Так при чисто синусоидальном выходном напряжении он выбирается равным четверти периода питающего напряжения, при искаженном, но симметричном по полуволнам выходном напряжении - полупериоду питающего напряжения. При наличии в выходном напряжении постоянной составляющей интервал интегрирования целесообразно выбирать равным периоду входного напряжения. Обнуление напряжения 26 осуществляется путем подачи в цепь управления ключа 9, шунтнрующего конденсатор 8 интегратора 6 импульса напряжения 27, сформированного на одном из выходов формирователя 17 по заднему фронту синхроимпульсов 21. На другом выходе формирователя 17 по переднему фронту синхроимпульсов 21 генерируется импульсная последовательность, которая, проходя через распределитель 19, преобразуется в импульсы 28, 29, поступающие в цепи управления ключей 13 ячеек 11, 12. Благодаря этому выход интегратора 6 поочередно перед обнулением напряжения 26 подключается к конденсаторам 14 ячеек И, 12, которые быстро заряжаются до соответствующего уровня. На выходах ячеек памяти (эыходах буферных усилителей 15) формируются напряжения 30, 31, пропорциональные т1тегралам от контролируемого (кривая 30) и задающего (кривая 31) напряжений на выбранном интервале их интегрирования (полупериоде питающего напряжения). Напряжения 30, 31 подаются на вход блока 2 органа 1, где сравниваются. Получивщийся в результате сравнения сигнал 32 ошибки является носителем информации для отработки блоком 2 соответствующего управляющего воздействия для органа 1.

При изменении частоты напряжения питающей сети 20 также изменится общий уровень напряжения 26 на выходе интегратора 6, что приведет к соответствующему изменению сигнала 32. Отработка такого возмущения производится со значительно больщим быстродействием, что положительно влияет на точность стабилизации выходного напряжения, .Данный стабилизатор позволяет осуществить компенсацию частотной зависимости в выходном напряжении простыми средствами, при этом удается повысить быстродействие и точность стабилизации.

Формула изобретения

к источнику задающего напряжения, выход коммутатора соединен с входом интегратора, выход которого подключен к входам ячеек памяти, выходом соединенных с входами блока управления, управляющий вход коммутатора подключен к выходу второго формирователя импульсов, управляющий вход интегратора соединен с другим выходом первого формирователя импульсов, а управляющие входы ячеек памяти подключены к выходам распределителя импульсов.

управления которого образует управляющий вход ячейки памяти.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР по заявке № 2542331/24-07, 10.10.78.

.гз

А

Л

А

W

У

Л

Л

vy

V/

w А

2

28

ч

Авторы

Даты

1981-07-07—Публикация

1979-07-09—Подача