го

О)

4

1

Изобретение относится к вычислительной технике и может быть использовано при создании устройств отображения информации.

Цель.изобретения - расширение области Применения устройства за счет обеспечения возможности редактирования информации пересекающимися группами элементов, объединенных в фрагменты различных уровней обобщения, и повышение быстродействия устройства.

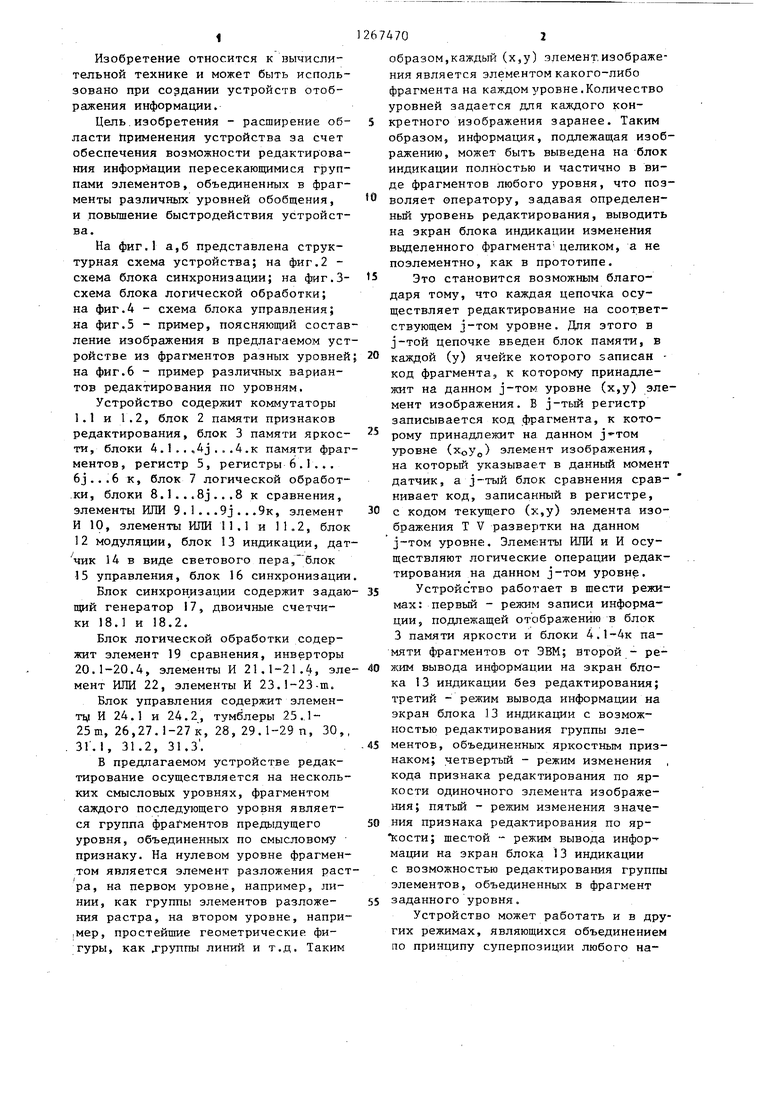

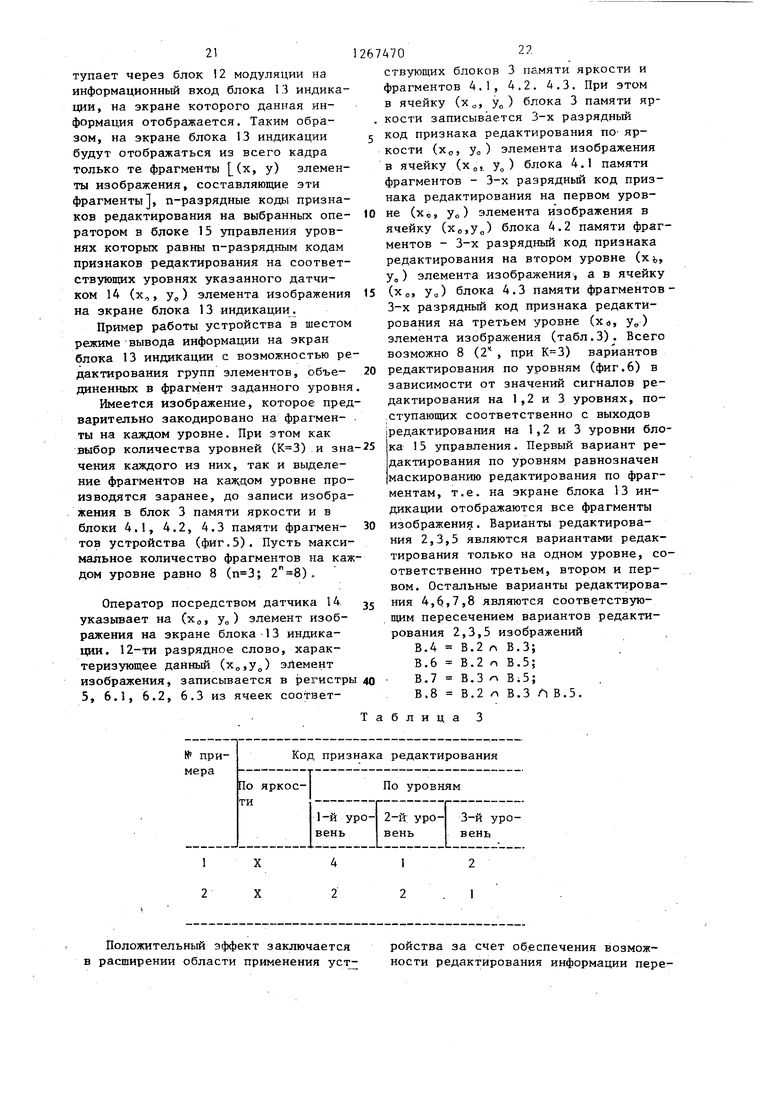

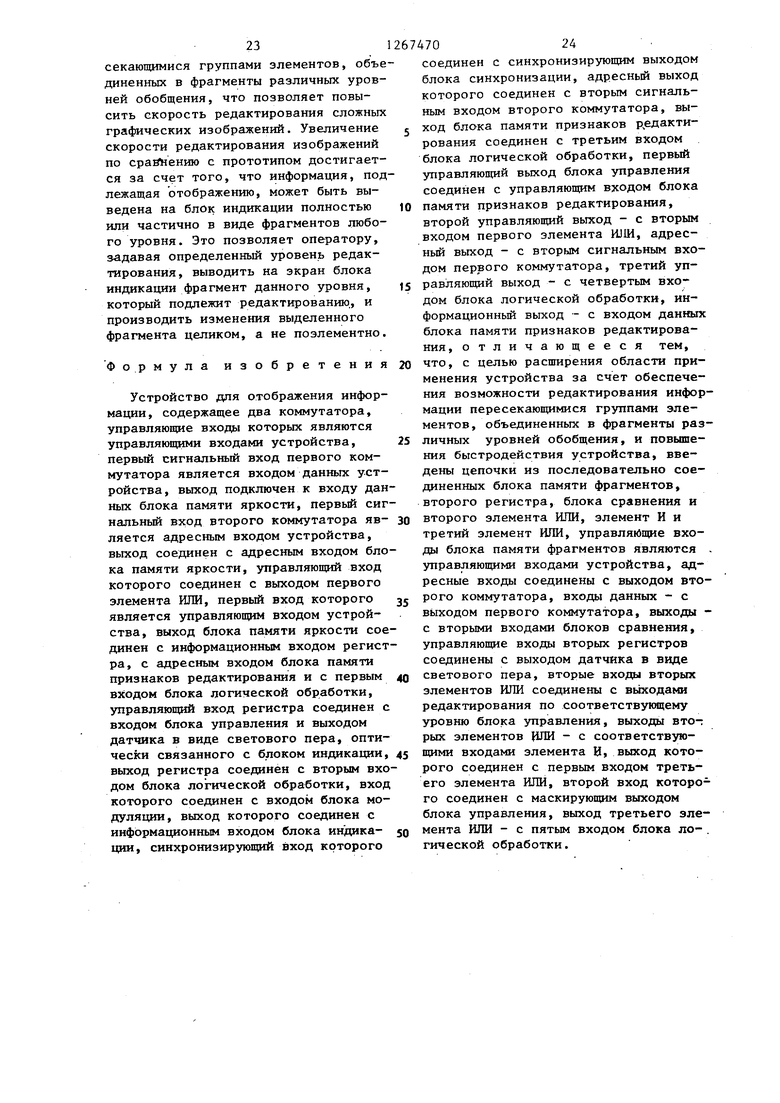

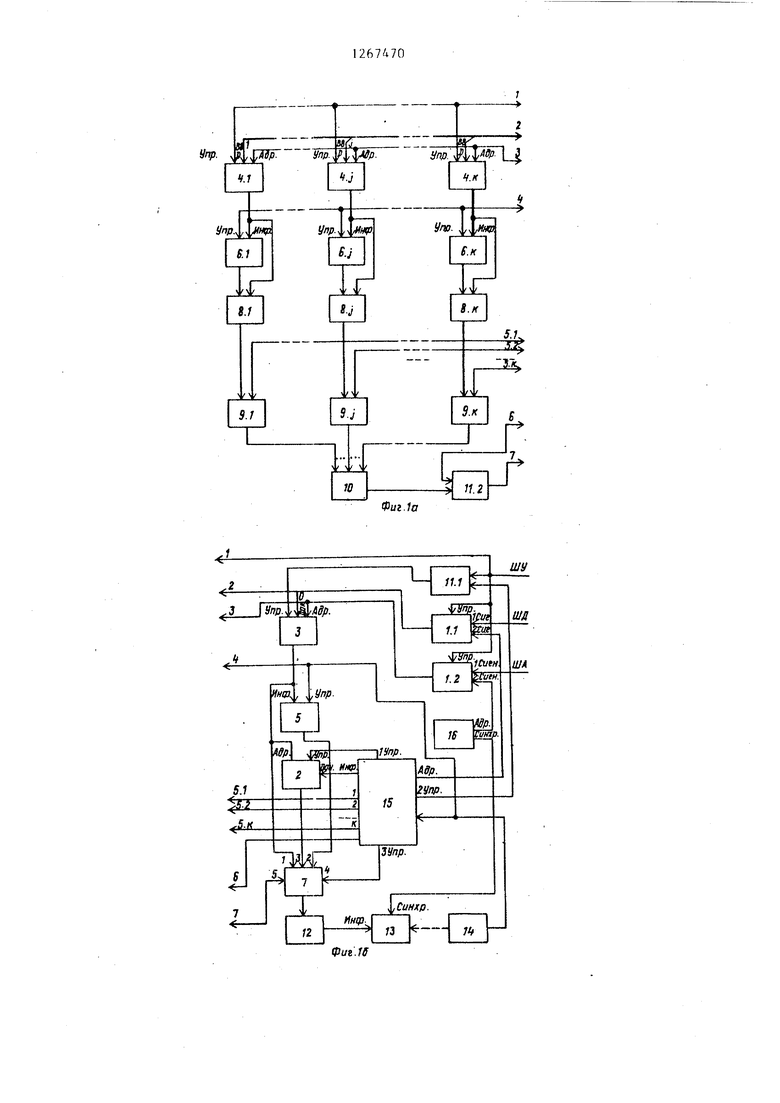

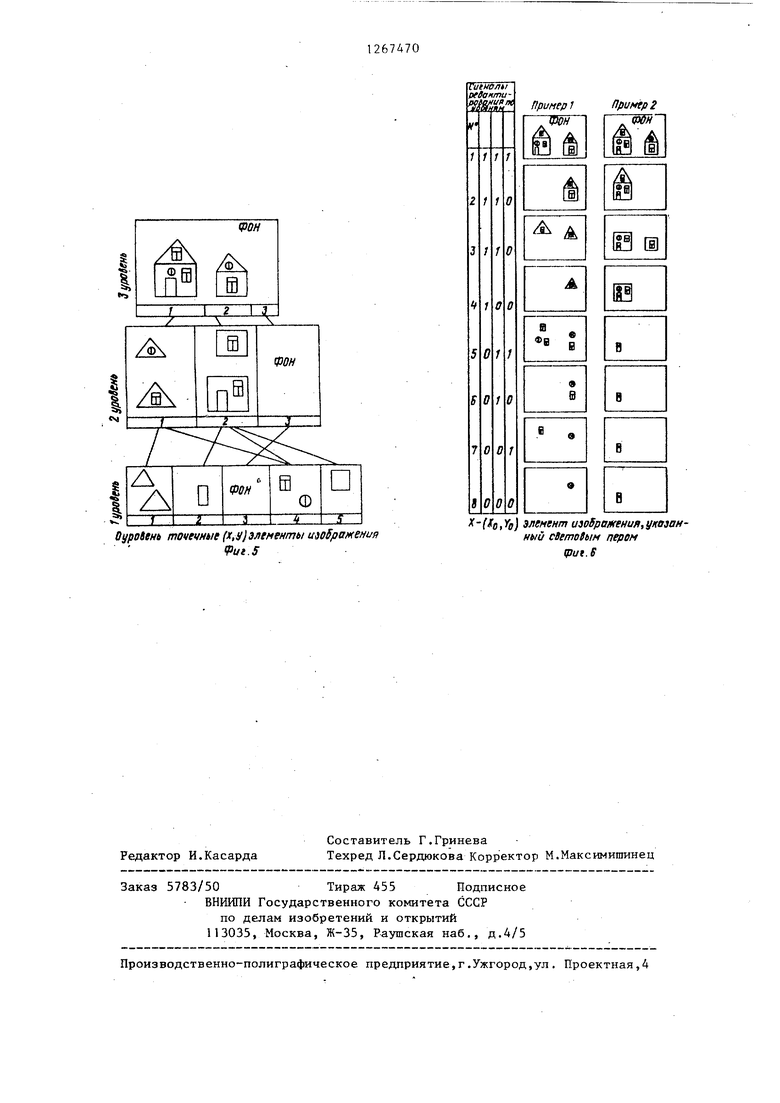

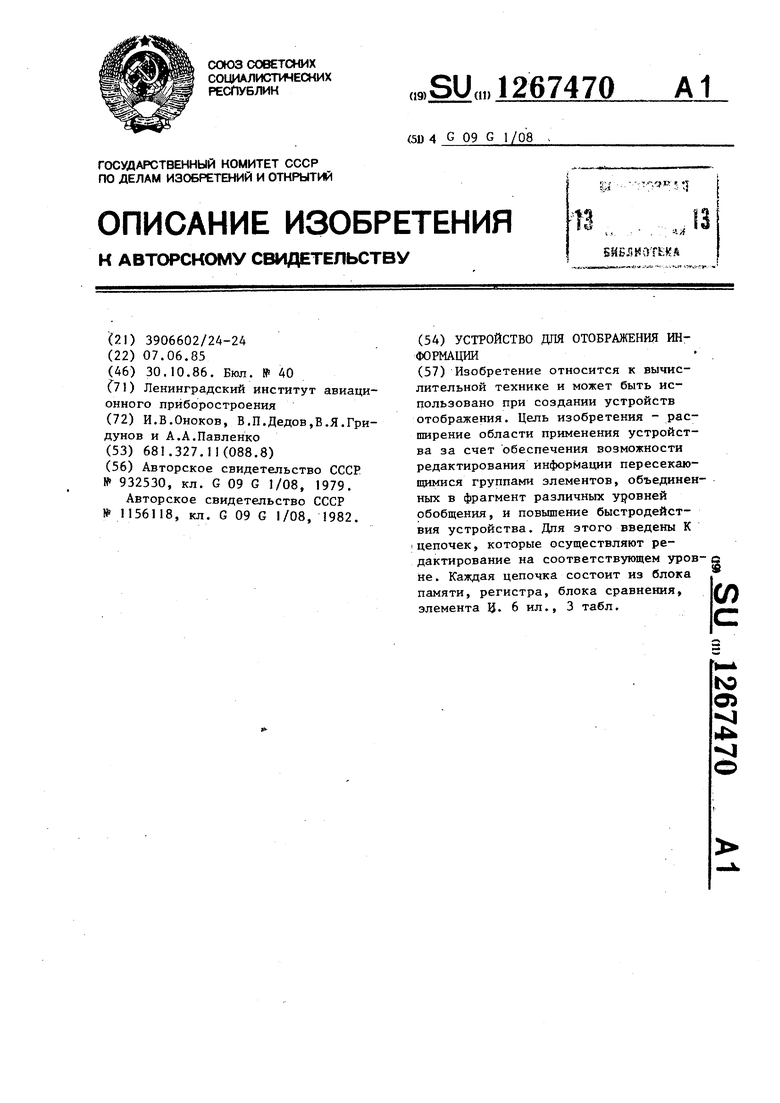

На фиг.1 а,б представлена структурная схема устройства; на фиг.2 схема блока синхронизации; на фиг.Зсхема блока логической обработки; на фиг.4 - схема блока управления; на фиг.5 - пример, поясняющий составление изображения в предлагаемом устройстве из фрагментов разных уровней на фиг.6 - пример различных вариантов редактирования по уровням.

Устройство содержит коммутаторы 1.1 и 1.2, блок 2 памяти признаков редактирования, блок 3 памяти яркости, блоки 4.1 .,,4j,..4.к памяти фрагментов, регистр 5, регистры 6 .1 ... 6J...6 к, блок 7 логической обработ.ки, блоки 8.1...8J...8 к сравнения, элементы ИЛИ 9. 1.. .9j . . .9к, элемент И 10, элементы ИЛИ 11.1 и 11.2, блок 12 модуляции, блок 13 индикации, датчик 14 в виде светового пера,блок 15 управления, блок 16 синхронизации

Блок синхронизации содержит задающий генератор 17, двоичные счетчики 18.1 и 18.2.

Блок логической обработки содержит элемент 19 сравнения, инверторы 20.1-20.4, элементы И 21.1-21.4, элемент ИЛИ 22, элементы И 23.1-23-т.

Блок управления содержит злеменTi, И 24.1 и 24.2, тумблеры 25.125т, 26,27.1-27 к, 28, 29.1-29 п, 30,, 31.1, 31.2, 31.3.

В предлагаемом устройстве редактирование осуществляется на нескольких смысловых уровнях, фрагментом саждого последующего уровня является группа фрагментов предыдущего уровня, объединенных по смысловому признаку. На нулевом уровне фрагментом является элемент разложения растра, на первом уровне, например, линии, как группы элементов разложения растра, на втором уровне, напри,мер, простейшие геометрические фигуры, как группы линий и т.д. Таким

4702

образом,каждый (х,у) элемент,изображения является элементом какого-либо фрагмента на каждом уровне. Количество уровней задается для каждого конкретного изображения заранее. Таким образом, информация, подлежащая изображению, может быть выведена на блок индикации полностью и частично в виде фрагментов любого уровня, что позволяет оператору, задавая определенный уровень редактирования, выводить на экран блока индикации изменения выделенного фрагмента целиком, а не поэлементно, как в прототипе.

Это становится возможным благодаря тому, что каждая цепочка осуществляет редактирование на соответствующем J-TOM уровне. Для этого в j-той цепочке введен блок памяти, в

каждой (у) ячейке которого записан код фрагмента, к которому принадлежит на данном J-TOM уровне (х,у) элемент изображения. В j-тый регистр записывается код фрагмента, к которому принадлежит на данном J-TOM

уровне () элемент изображения, на который указывает в данный момент датчик, а j-тый блок сравнения сравнивает код, записанный в регистре,

с кодом текущего (х,у) элемента изображения Т V развертки на данном J-TOM уровне. Элементы ИЛИ и И осуществляют логические операции редактирования на данном J-TOM уровне.

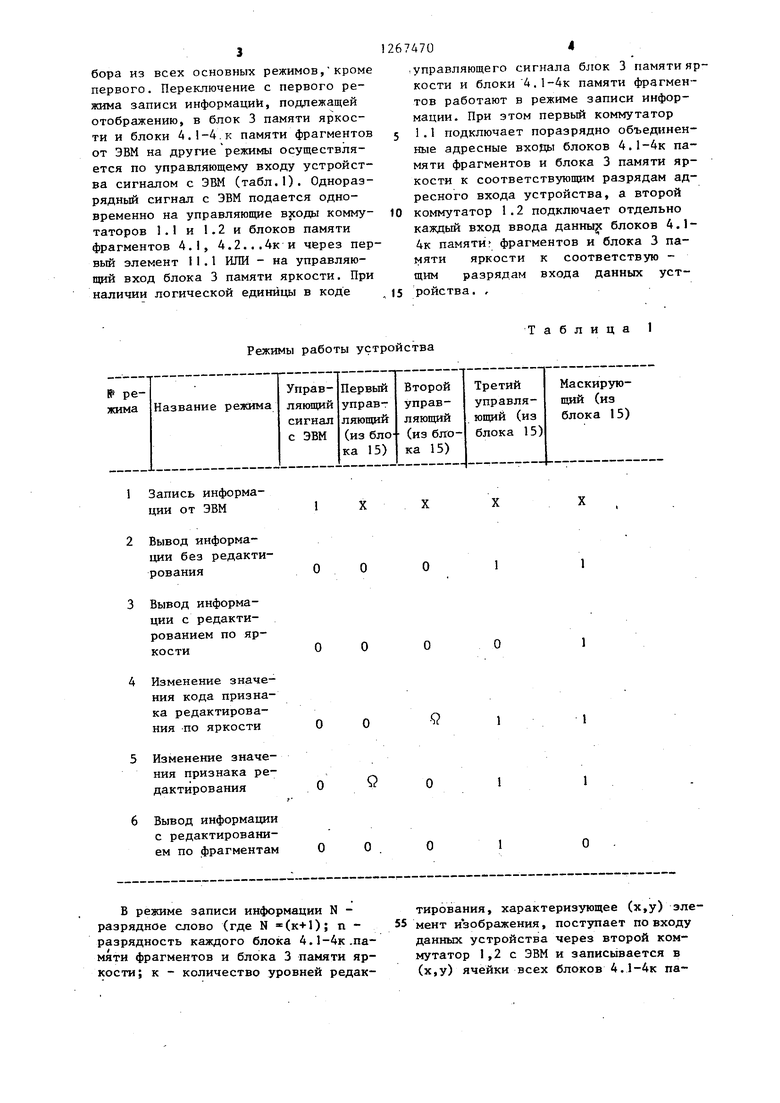

Устройство работает в шести режимах: первый - режим записи информации, подлежащей отображению в блок 3 памяти яркости и блоки 4.1-4к памяти фрагментов от ЭВМ; второй - режим вывода информации на экран блока 13 индикации без редактирования; третий - режим вывода информации на экран блока 13 индикации с возможностью редактирования группы элементов, объединенных яркостным признаком; четвертый - режим изменения кода признака редактирования по яркости одиночного элемента изображения; пятьм - режим изменения значения признака редактирования по яр Кости; шестой - режим вывода информации на экран блока 13 индикации с возможностью редактирования группы элементов, объединенньпс в фрагмент

заданного уровня.

Устройство может работать и в других режимах, являющихся объединением по принципу суперпозиции любого набора из всех основных режимов,кроме первого. Переключение с первого режима записи информации, подлежащей отображению, в блок 3 памяти яркости и блоки 4.1-4.к памяти фрагментов от ЭВМ на другие режимы осуществляется по управляющему входу устройства сигналом с ЭВМ (табл.1). Одноразрядный сигнал с ЭВМ подается одновременно на управляющие входы коммутаторов 1.1 и 1.2 и блоков памяти фрагментов 4.1, 4.2...4ки через первый элемент 11.1 ИЛИ - на управляющий вход блока 3 памяти яркости. При наличии логической единицы в коде

Режимы работы устройства

2674704

,управляющего сигнала блок 3 памяти яркости и блоки4.1-4к памяти фрагментов работают в режиме записи информации. При этом первый коммутатор 5 1.1 подключает поразрядно объединенные адресные входы блоков 4.1-4к памяти фрагментов и блока 3 памяти яркости к соответствующим разрядам адресного входа устройства, а второй 10 коммутатор 1.2 подключает отдельно каждый вход ввода данны с блоков 4.14к памяти фрагментов и блока 3 памяти яркости к соответствую щим разрядам входа данных уст15 ройства. ,

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| ФОРМИРОВАТЕЛЬ СИГНАЛОВ ТЕЛЕВИЗИОННЫХ ИЗОБРАЖЕНИЙ | 1988 |

|

RU1637638C |

| Устройство для отображения информации на экране телевизионного индикатора | 1985 |

|

SU1339627A1 |

| Устройство для отображения информации | 1990 |

|

SU1737499A1 |

| ГИБРИДНАЯ ЯЧЕЙКА ОПТОЭЛЕКТРОННОГО НЕЙРОПРОЦЕССОРА | 1992 |

|

RU2057363C1 |

| Устройство для отображения информации | 1984 |

|

SU1226519A2 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2006 |

|

RU2313128C1 |

| Устройство для формирования изображений на экране телевизионного приемника | 1982 |

|

SU1072092A1 |

| Устройство для отображения информации | 1987 |

|

SU1513439A1 |

| Устройство для отображения полутонового изображения на экране телевизионного приемника | 1988 |

|

SU1522273A1 |

| Устройство для отображения информации | 1986 |

|

SU1432594A1 |

Изобретение относится к вычислительной технике и может быть использовано при создании устройств отображения. Цель изобретения - расширение области применения устройства за счет обеспечения возможности редактирования информации пересекающимися группами элементов, объединенных в фрагмент различных уровней обобщения, и повышение быстродействия устройства. Дпя зтого введены К i цепочек, которые осуществляют редактирование на соответствующем уровне . Каждая цепочка состоит из блока сл памяти, регистра, блока сравнения, злемента IJ. 6 ил., 3 табл.

Запись информации от ЭВМ

Вывод информации без редактирования

Вывод информации с редактированием по яркости

Изменение значения кода признака редактирования по яркости

Изменение значения признака редактирования

Вывод информации с редактированием по фрагментам

в режиме записи информации N разрядное слово (где N (); п разрядность каждого блока 4.1-4к.памяти фрагментов и блока 3 памяти яркости; к - количество уровней редакQ

тирования, характеризующее (х,у) эле55 мент изображения, поступает по входу данных устройства через второй коммутатор 1,2 с ЭВМ и записывается в (х,у) ячейки всех блоков 4.1-4к памяти фрагментов и блока 3 памяти яркости, адрес который поступает по адресному входу устройства через пер вьй коммутатор 1.1 с ЭВМ. При этом в каждую (х,у) ячейку блока 3 памяти яркости записывается разрядный код, являющийся кодом признака редактирования по яркости (х,у) элемента изображения, а в каждую (х,у) ячейку блоков 4.1-4к памяти фрагментов - соответствующий ...к разрядный код, каждый из которых является кодом фрагмента на 1,2 к уровню (кодом признака редактирования по .уровню 1,2. ,. к). Между ячейками блока 3 памяти яркости и блоков 4.1-4к памяти фрагментов и элементами изображения на экране блока 13 индикации установле но взаимно однозначное соответствие X - номер элемента изображения по горизонтали; х (1, X); у - номер элемента изображения по вертикали; У с(1. У). Выбор (х,у) ячейки в блоке 3 памяти яркости, во всех блоках 4.1. 4к памяти фрагментов, в.которую дол на быть записана информация, подлеж щая отображению, осуществляется по адресному входу устройства. При наличии логического нуля в к де управляющего сигнала устройство работает в автономных режимах. Переключение на второй режим вывода информации на экран блока 13 индикации без редактирования осущес вляется сигналами с управляющих и маскирующего выходов блока 15 управления . При этом устанавливаются сигналы логического нуля на первом и втором управляющих выходах, логический нуль на выходах элементов 24.14 и 24.24 соответствует замкнутому положению тумблеров 26 и 30, и сигналы логической единицы в третьем разряде третьего управляющего и маскирующем выходах (табл«1), что соответствует разомкнутому положени тумблеров 28 и 31.3.Сигналы логичес кого нуля с.первого и второго управ ляющих выходов блока 15 управления поступают соответственно на управляющий вход блока 2 памяти признаков редактирования и через первый элемент ИЛИ 11.1 - на управляющий вход блока 3 памяти яркости., Блок п мяти признаков редактирования, блок 3 памяти яркости и блоки 4.1.-4к па70«мяти фрагментов переключаются в реим считывания. При этом второй коммутатор 1.2 подключает адресный вход блока. 3 памяти яркости и блоков 4.1-4к памяти фрагментов к адресному выходу блока 16 синхронизации. Задающий генератор 17 блока 16 синхронизации (фиг.2) вьфабатывает последовательность импульсов с частотой fо. Эта последовательность импульсов подается на вход первого двоичного счетчика 18.1 импульсов на X (X - число элементов разложения в изображении по горизонтали), котЬрый считает эти импульсы и формирует на параллельной выходе сигнал двоичного кода номера каждого элемента разложения по горизонтали, а на выходе переноса - последовательность импульсов с частотой г .. f /,. СТРОКИ .LO / .л. С выхода переноса первого двоичного счетчика 18.1 последовательность импульсов с частотой f строки подается на вход второго двоичного счетчика 18.2 импульсов на У (У - число строк по вертикали в изображении), который считает эти импульсы и формирует на параллельном выходе сигнгш двоичного кода номера каждой строки разложения по вертикали, а на выходе переноса - последовательность импульсов с частотой f кадра f строки/у о(); Параллельные выходы первого и второго двоичных счет.чиков 18.1, 18,2 являются адресньп 1 выходом блока 16 синхронизации, сигналы двоичного кода номера (х,у) каждого элемента изображения по горизонтали и вертикали с которого поступают через второй коммутатор 1.2 на адресный вход блока 3 памяти яркости и блоков 4.1-4к памяти фрагментов 4.1, 4.2...4к. Выходы переноса первого и второго двоичных счетчикаj18.1, 18.2 являются синхронизирующим выходом блока 16 синхронизации, сигналы частоты строк и кадров с которого поступают на сидхронизирующий вход блока 13 индикации. Таким образом, блок 16 синхронизации синхронизирует .работу всего устройства. Сигнал двоичного кода номера элемента по горизонтали и вертикали в .изображении, поступающий с адресного выхода блока 16 синхронизации, производит последовательный

опрос всех (х,у) ячеек одновременно блока 3 памяти яркости и всех блоков 4.1-4к памяти фрагментов синхронно с TV разверткой блока 13 индикации. При этом с выхода блока 3 памяти яркости код признака редактирования по яркости каждого (х,у) элемента изображения поступает на адресный вход блока 2 памяти признаков редактирования, из которого считывается т-разрядный код, характеризующий яркостное значение (х,у) элемента изображения и поступающий на третий вход блока 7 логической обработки. Разрядность кода, характеризующего яркостное значение (х,у) элемента изображения, равна m и всегда не меньше разрядности кода признаков редактирования по яркости m ,так как в противном случае частично теряется информация об изображении, хранящаяся в блоке 3 памяти яркости. От количества разрядов в коде, характеризующем яркостное значение (х,у) элемента изображения, зависит совокупность различных градаций яркости, которые можно задать (х,у) элементу изображения, равная 2. В течении кадра можно выводить на экран блока 13 индикации только 2 признаков редактирования по яркости из всей совокупности 2. Это определяется разрядностью кода признака

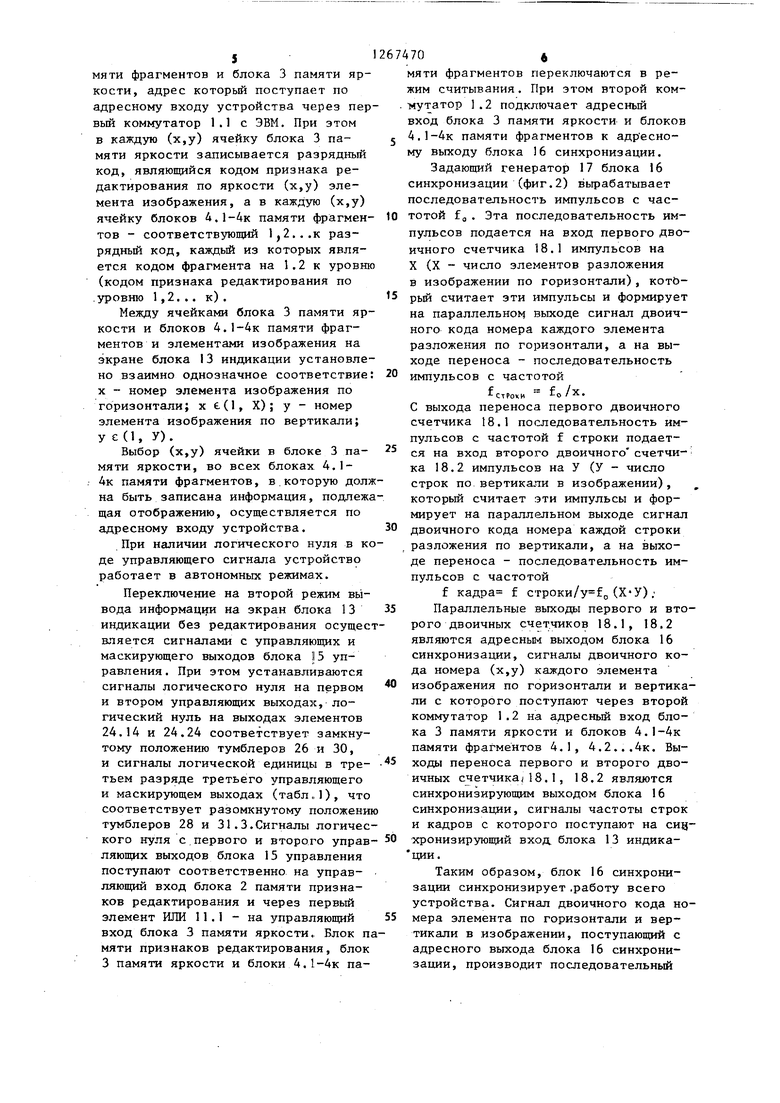

Равенство О 10

Неравен000ство

1 1 О

Меньше

74708

редактирования по яркости, хранящегося в блоке 3памяти яркости и пос гупающего на адресный вход блока 2 памяти признаков редактирования,равной п. Следовательно, в блоке 2 памяти признаков редактирования хранится 2 га-разрядных кодов, характеризующих яркостное значение (х,у) элемента изображения. Последовательный вывод всех 2 возможных градаций осуществляется изменением содержимого 2 ячеек в блоке 2 памяти признаков редактирования по командам с блока 15 управления.

С выхода блока 2 памяти признаков редактирования т-разрядный код, характеризующий яркостное значение (х,у) элемента изображения, поступает на третий вход блока 7 логической обработки, на пятый вход которого в данном режиме через второй элемент ИЛИ 11.2 подается сигнал логической единицы с маскирующего выхода блока 15 управления (тумблер 28 разомкнут) , а на четве;ртый вход - третий управляющий сигнал с выхода блока 15 управления, третий разряд которого равен логической единице.

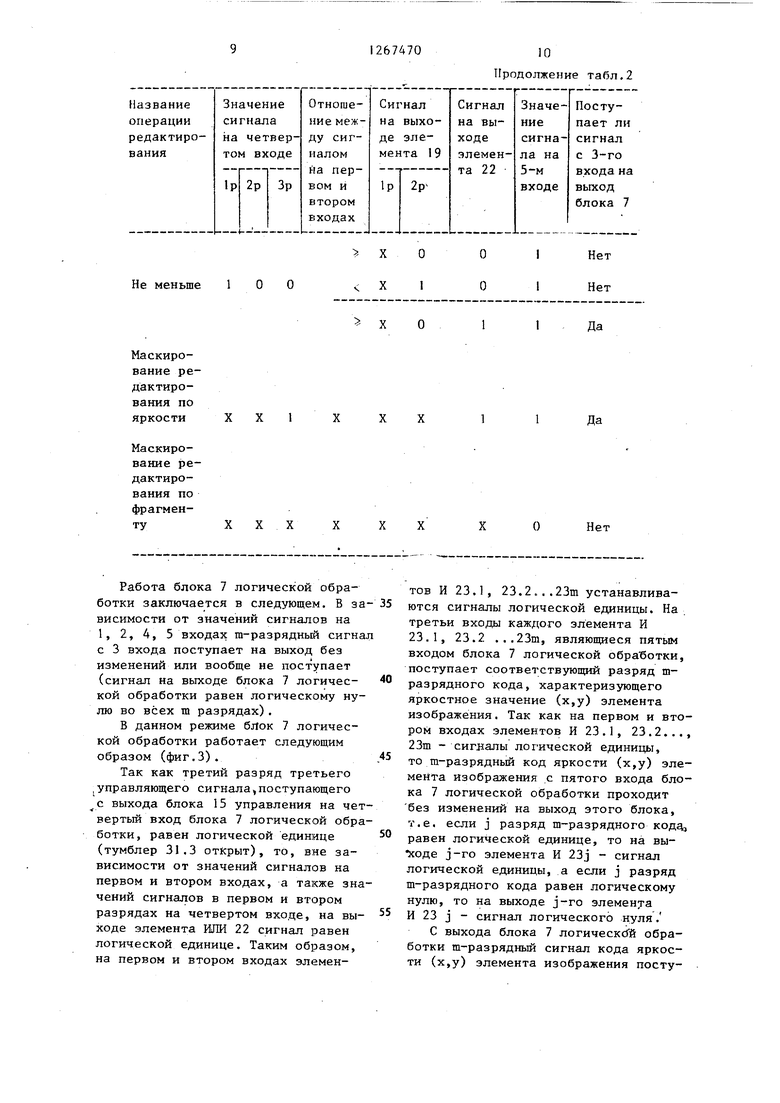

В табл.2 представлено значение сигнала на выходе блока 7 логической обработки в зависимости от значений входных сигналов..

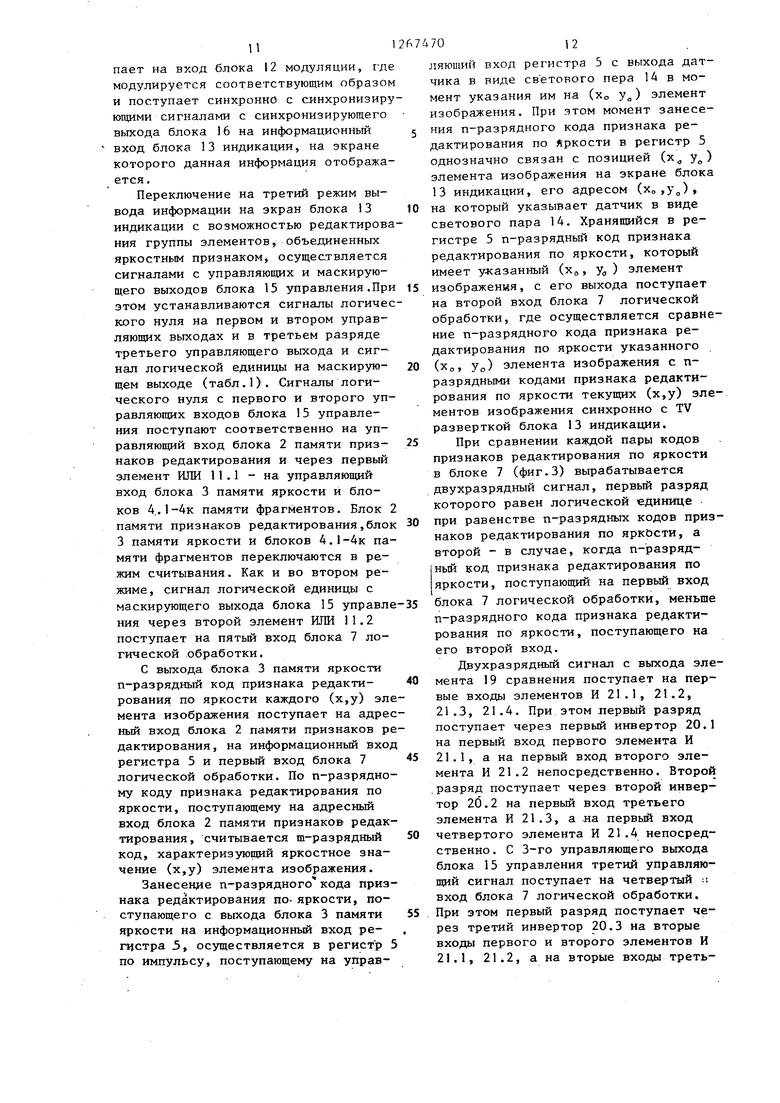

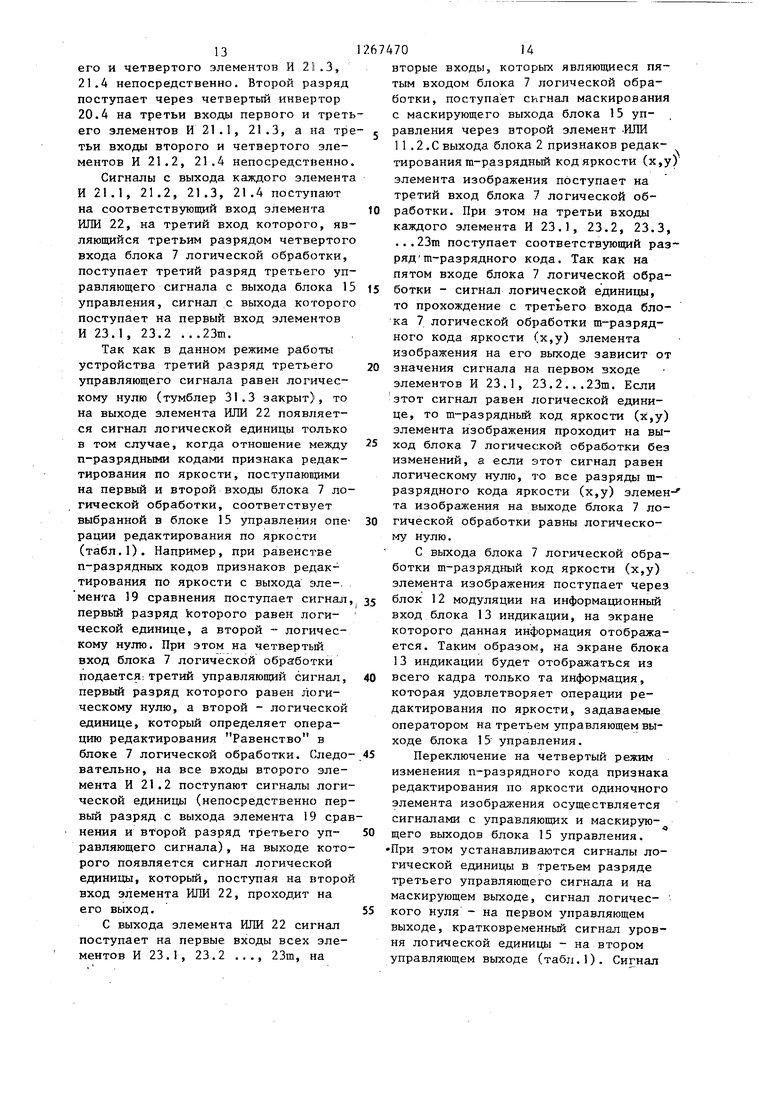

Таблица 2 Работа блока 7 логической обработки заключается в следующем. В з висимости от значений сигналов на 1, 2, 4, 5 входах т-разрядный сигн с 3 входа поступает на выход без изменений или вообще не поступает (сигнал на выходе блока 7 логической обработки равен логическому ну лю во всех та разрядах). В данном режиме блок 7 логической обработки работает следующим образом (фиг.З). Так как третий разряд третьего ,управляющего сигнала,поступающего с выхода блока 15 управления на че вертый вход блока 7 логической обр ботки, равен логической единице (тумблер 31.3 открыт), то, вне зависимости от значений сигналов на первом и втором входах, а также зн чений сигналов в первом и втором разрядах на четвертом входе, на вы ходе элемента ИЛИ 22 сигнал равен логической единице. Таким образом, на первом и втором входах элементов и 23.1, 23.2„..23т устанавливаются сигналы логической единицы. На третьи входы каждого элемента И 23.1, 23.2 ...23т, являющиеся пятым входом блока 7 логической обработки, поступает соответствующий разряд шразрядного кода, характеризующего яркостное значение (х,у) элемента изображения. Так как на первом и втором входах элементов И 23 .1, 23.2.... 23т - сигвалы логической единицы, то т-разрядный код яркости (х,у) элемента Изображения с пятого входа блока 7 логической обработки проходит без изменений на выход этого блока, т.е. если j разряд т-разрядного кода, равен логической единице, то на выводе j-ro элемента И 23j - сигнал логической единицы, а если j разряд т-разрядного кода равен логическому нулю, то на выходе j-ro элемента И 23 j - сигнал логического нуля. С выхода блока 7 логической обработки т-разрядный сигнал кода яркости (х,у) элемента изображения поступает на вход блока 12 модуляции, гд модулируется соответствующим образо и поступает синхронно с слнхронизир ющими сигналами с синхронизирующего выхода блока 16 на информационный вход блока 13 индикации, на экране которого данная информация отобража ется . Переключение на третий режим вывода информации на экран блока 13 индикации с возможностью редактиров ния группы элементов, объединенных яркостным признаком, осуществляется сигналами с управляющих и маскирующего выходов блока 15 управления.Пр этом устанавливаются сигналы логиче кого нуля на первом и втором управляющих выходах и в третьем разряде третьего управляющ.его выхода и сигнал логической единицы на маскирующем выходе (табл,1). Сигналы логического нуля с первого и второго уп равляющих входов блока 15 управления поступают соответственно на управляющий вход блока 2 памяти признаков редактирования и через первый элемент ИЛИ 11.1 - на управляющий вход блока 3 памяти яркости и блоков 4..1-4к памяти фрагментов. Блок памяти признаков редактирования,бло 3 памяти яркости и блоков 4.1-4к па мяти фрагментов переключаются в режим считывания. Как и во втором режиме, сигнал логической единицы с маскирующего выхода блока 15 управл ния через второй элемент PfflH 11.2 поступает на пятый вход блока 7 логической обработки. С выхода блока 3 памяти яркости п-разрядный код признака редактирования; по яркости каждого (х,у) эл мента изображения поступает на адре ный вход блока 2 памяти признаков р дактирования, на информационный вход регистра 5 и первый вход блока 7 логической обработки. По п-разрядно му коду признака редактиррвания по яркости, поступающему на адресный вход блока 2 памяти признаков редак тирования , считывается т-разрядный код, характеризующий яркостное значение (х,у) элемента изображения. SaHeceHjie п-разрядного кода признака редактирования по- яркости, поступающего с выхода блока 3 памяти яркости на информационный вход регистра 3, осуществляется в регистр 5 по импульсу, поступающему на управ70 2ляющий вход регистра 5 с выхода датчика в виде светового пера 14 в момент указания им на (хо у,) элемент изображения. При этом момент занесения п-разрядного кода признака редактирования по Яркости в регистр 5 однозначно связан с позицией (х у) элемента изображения на экране блока 13 индикации, его адресом (х,7), на который указывает датчик в виде светового пара 14. Хранящийся в регистре 5 п-разрядньп1 код признака редактирования по яркости, который имеет указанный (х, у, ) элемент изображения, с его выхода поступает на второй вход блока 7 логической обработки, где осуществляется сравнение п-разрядного кода признака редактирования по яркости указанного (хо, Уо) элемента изображения с празрядными кодами признака редактирования по яркости текущих (х,у) элементов изображения синхронно с TV разверткой блока 13 индикации. При сравнении каждой пары кодов признаков редактирования по яркости в блоке 7 (фиг.З) вырабатывается двухразрядный сигнал, первый разряд которого равен логической единице при равенстве п-разрядных кодов признаков редактирования по яркЬсти, а второй - в случае, когда п-разрядный код признака редактирования по яркости, поступающий на первый вход блока 7 логической обработки, меньше п-разрядного кода признака редактирования по яркости, поступающего на его второй вход. Двухразрядньй сигнал с выхода элемента 19 сравнения поступает на первые входы элементов И 21.1, 21.2, 21.3, 21.4. При этом лервый разряд поступает через первый инвертор 20.1 на первый вход первого элемента И 21.1, а на первый вход второго элемента И 21.2 непосредственно. Второй разряд поступает через второй инвертор 20.2 на первый вход третьего элемента И 21.3, а ла первый вход четвертого элемента И 21.4 непосредственно. С 3-го управляющего выхода блока 15 управления третий управляющий сигнал поступает на четвертый :i вход блока 7 логической обработки. При этом первый разряд поступает через третий инвертор 20.3 на вторые входы первого и второго элементов И 21.1, 21.2, а на вторые входы треть13его и четвертого элементов И 21.3, 21.4 непосредственно. Второй разряд поступает через четвертый инвертор 20.4 на третьи входы первого и треть его элементов И 21.1, 21.3, а на тре тьи входы второго и четвертого элементов И 21.2, 21.4 непосредственно Сигналы с выхода каждого элемента И 21.1, 21.2, 21.3, 21.4 поступают на соответствующий вход элемента ИЛИ 22, на третий вход которого, являющийся третьим разрядом четвертого входа блока 7 логической обработки, поступает третий разряд третьего управляющего сигнала с выхода блока 15 управления, сигнал с выхода которого поступает на первый вход элементов И 23.1, 23.2 ...23т. Так как в данном режиме работы устройства третий разряд третьего управляющего сигнала равен логическому нулю (тумблер 31.3 закрыт), то на выходе элемента ИЛИ 22 появляется сигнал логической единицы только в том случае, когда отношение между п-разрядньми кодами признака редактирования по яркости, поступаюгдами на первый и второй входы блока 7 логической обработки, соответствует выбранной в блоке 15 управления операции редактирования по яркости (табл.1). Например, при равенстве п-разрядных кодов признаков редактирования по яркости с выхода эле-. мента 19 сравнения поступает сигнал первый разряд которого равен логической единице, а второй - логическому нулю. При этом на четвертый вход блока 7 логической обработки подается; третий управляющий сигнал, первый разряд которого равен логическому нулю, а второй - логической единице, который определяет операцию редактирования Равенство в блоке 7 логической обработки. Следо вательно, на все входы второго элемента И 21.2 поступают сигналы логи ческой единицы (непосредственно пер вый разряд с выхода элемента 19 сра нения и второй разряд третьего управляющего сигнала), на выходе кото рого появляется сигнал логической единицы, который, поступая на второ вход элемента ИЛИ 22, проходит на его выход. С выхода элемента ИЛИ 22 сигнал поступает на первые входы всех элементов И 23.1, 23.2 .,., 23т, на 70 вторые входы, которых являющиеся пя тым входом блока 7 логической обработки, поступает сигнал маскирования с маскирующего выхода блока 15 управления через второй элемент -ИЛИ 1 1 .2 .С выхода блока 2 признаков редактирования т-разрядный код яркости (х,у) элемента изображения поступает на третий вход блока 7 логической обработки. При этом на третьи входы каждого элемента И 23.1, 23.2, 23.3, . . . 23тп поступает соответствующий разрядт-разрядного кода. Так как на пятом входе блока 7 логической обработки - сигнал логической единицы, то прохождение с третьего входа блока 7 логической обработки т-разрядного кода яркости (х,у) элемента изображения на его выходе зависит от значения сигнала на первом входе элементов И 23.1, 23.2...23т. Если этот сигнал равен логической единице, то т-разрядный код яркости (х,у) элемента изображения проходит на выход блока 7 логической обработки без изменений, а если этот сигнал равен логическому нулю, то все разряды гаразрядного кода яркости (х,у) элемента изображения на выходе блока 7 логической обработки равны логическому нулю. С выхода блока 7 логической обработки т-разрядный код яркости (х,у) элемента изображения поступает через блок 12 модуляции на информационный вход блока 13 индикации, на экране которого данная информация отображается. Таким образом, на экране блока 13 индикации будет отображаться из всего кадра только та информация, которая удовлетворяет операции редактирования по яркости, задаваемые оператором на третьем управляющем выходе блока 15 управления. Переключение на четвертый режим изменения п-разрядного кода признака редактирования по яркости одиночного элемента изображения осуществляется сигналами с управляющих и маскирующего выходов блока 15 управления. При этом устанавливаются сигналы логической единицы в третьем разряде третьего управляющего сигнала и на маскирующем выходе, сигнал логического нуля - на первом управляющем выходе, кратковременный сигнал уровня логической единицы - на втором управляющем выходе (табл.1). Сигнал 15 логического нуля с первого управляющего выхода блока 15 управления по ступает на управляющий вход блока 2 памяти признаков редактирования и переключает его в режим считывания, а кратковременный сигнал логической единицы с второго управляющего выхо да блока 15 управления поступает через первый элемент ИЛИ 11.1 на уп равляющий вход блока 3 памяти яркос ти, переключая его в режим записи. Этот кратковременный сигнал форм {дуется в блоке 15 управления (фиг.4 В данном режиме на первый вход второго элемента И 24.2 подается сигнал уровня логической единицы (тумблер 3.0 разомкнут) . На второй вход второ го элемента И 24.2, являющийся входом блока 15 управления, подается сигнал логической единицы с выхода светового пера 14 только в момент времени, однозначно определяемый координатами (XQ, Уд), указанный световым пером 14 элемента изображения Следовательно, этот сигнал взаимно однозначно связан с координатами (о Уо) элемента изображения, указанного датчиком в виде светового пера 14 на экране блока 13 индикации, и проходит на выход второго элемента И 24.2, являющегося вторым управляющим выходом блока 15 управления. При этом по адресу (Хо, у ) элемента изображения, указанному датчиком в виде светового пера 14, в ячей ки (хо, Уо) блока 3 памяти яркости записывается п-разрядный код признака редактирования по яркости, которьй с адресного выхода .блока 15 управления через первый коммутатор 1.1 поступает на вход данных блока 3 памяти яркости. Оператором задается значение п-разрядного кода признака редактирования по яркости в блоке 15 управления тумблерами 29.1...29п. Но вое значение.п-разрядного кода признака редактирования по яркости за.писывается в ячейку (х„, Уо) блока 3 памяти яркости. При отсутствии сигнала логической единицы на выходе датчика в виде светового пера 14 блок 3 памяти яркости опять переключается в режим считывания информации. Дри этом в следующих кадрах ( элемент изображения Отображается на экране блока 13 индикации, имея новое установленное оператором значение п-разрядного кода 70 признака редактирования по яркости. Блоки 4.1-4к памяти фрагментов работают в режиме считывания информации, так как сигнал логического нуля с управляющей шины ЭВМ поступает на управляющий вход блоков 4.1-4к памяти. Сигналы логической единицы в третьем разряде на третьем управляющем и на маскирующем выходах блока 15 управления маскируют редактирование по яркости и по фрагментам, как и во втором регистре вывода информации на экран бдока I3 индикации без редактирования. Переключение на пятый режим изменения значения п-разрядного признака редактирования по яркости осуществляется сигналами с управляющих и маскирующего выходов блока 15 управления. При этом устанавливаются сигналы логической единицы в третьем разряде третьего управляющего сигнала и на маскирующем выходе, сигнал логического нуля - на втором управляющем выходе и кратковременный сигнал уровня логической единицы - на первом управляющем выходе (табл.Ц В блоке I5 управления вырабатывается первый управляющий кратковременный сигнал (фиг.4). В данном режиме на первый вход первого элемент И 24.1 подается сигнал уровня логической единиды посредством переключения тумблера 26 (разомкнут). На второй вход первого элемента И 24.1, являющийся входом блока 15 управления, подается сигнал логической единицы с выхода светового пера 14 только в момент времени, однозначно определяемый координатами (х,, у ) элемента изображения, указанного датчиком в виде светового пера 14 на экране блока 13 индикации, и проходит на выход первого элемента И 24.1, являющегося первым управляющим входом блока 15 Управления. Сигнал логического нуля с второго управляющего выхода блока 15 (тумблер 30 замкнут) управления через первый элемент ИЛИ 41.1 поступает на управляющий вход блока 3 памяти яркости, переключая его в-режим считывания. Запись в блок 2 памяти признаков редактирования осуществляется в ячейку, адрес которой поступает на адресный вход с выхода блока 3 памяти яркости и равен п-разрядному коду признака редактирования по яркости, записанного в ячейке (х„,Уд) блока 3 памяти яркости. При ;ITOM по п-разрядиому коду признака редактирования по яркости (ха, у) элвмёнта изображения в ячейку блока 2 памяти признаков редактирования записывается га-разрядный код, характеризующий яркостное значение (хо, Уо) элемента изображения, который с информационного вьпсода блока 15 управления поступает на вход данных блока 2 памяти признаков редактирования. Оператором задается значение га-разрядного кода, характеризующего яркостное значение (хо, Уо) элемента изображения, в блоке 15 управления. Набором тумблеров 25.1...25га новое значение записывается в ячейку блока 2 памяти признаков редактирования. При отсутствии сигнала логической единицы на выходе датчика в виде светового пера 14 блок 2 памяти признаков редактирования опять переключается в режим считывания информа ции. При этом в следующих кадрах (х,у) элементы изображения, имеющие тот же п-разрядный код признака редактирования по яркости, что и (Xj,, УО) элемент изображения, отображаются на экране блока 13 индикации,имея новое установленное оператором яркостное значение. Сигналы логической единицы в тре тьем разряде на третьем управляющем выходе и на маскирующем выходе блока 15 управления маскируют редактирование по яркости и по фрагментам, как и во втором режиме вывода информации на экран блока 13 индикации без редактирования . Переключение на шестой режим вывода информации на экран блока 13 индикации с возможностью редактирования группы элементов, объединенны в фрагмент заданного уровня, осущес вляется сигналами с управляющих и маскирующего выходов блока 15 управ леция.При этом устанавливаются сигналы логического нуля на первом и втором управляющих и на втором маск рующем выходах и сигнал логической единицы - в третьем разряде на трет ем управляющем выходе (табл.1). Сиг налы логического нуля с первого и второго управляющих выходов блока 1 управления поступают соответственно на управляющий вход блока 2 памяти признаков редактирования и через 701В первый элемент ИЛИ 11.1 - на управляющий вход блока 3 памяти яркости. Блоки 4.1-4к памяти фрагментов работают в режиме считывания, так как в данном режиме с управляющеговхода устройства на управляющий вход блоков 4.-4к памяти фрагментов поступает сигнал логического нудя. Блок 2 памяти признаков редактирования, блок 3 памяти яркости и блоки 4,1-4к памяти фрагментов переключаются в режим считывания, как и во втором режиме вывода информации на экран блока 13 индикации без редактирования. Сигнал логической единицы в третьем разряде с третьего управляющего выхода блока 15 управления поступает на четвертый вход блока 7 логической обработки, где через элемент ИЛИ 22 поступает на объединенные первые входы всех элементов И 23.1, 23.2...23га (фиг.З). С выхода блока 3 памяти яркости п-разрядный код признака редактирования по яркости каждого (х,у) элемента изображения поступают на адресный вход блока 2 памяти признаков редактирования,.из которого считывается га-разрядный код, характеризующий яркостное значение (х,у) элемента изображения и поступающий на третий вход блока 7 логической обработки. Все контуры редактирования по уровню работают аналогично. Рассмотрим работу j-ro контура редактирования по уровню. При считывании информации с выхода блока 4 j памяти фрагментов п-разрядный код признака редактирования на J-TOM уровне каждого (х,у) элемента изображения поступает на информационный вход регистра 6 j и первый вход блока 8 j сравнения. Занесение п-разрядного кода признака редактирования, поступающего с выхода блока 4 j памяти фрагментов на информационный вход регистра 6 j, осуществляется в регистр 6 j по импульсу, поступающему с выхода светового пера 14 на управляющий, вход регистра 6 j в момент указания им на (х, у) элемент изображения. При этом момент занесения п-разрядного кода признака редактирования на J-TOM уровне в регистр 6 j однозначно связан с позицией (Хо, Уо) элемента изображения на экране блока 13 индикации, его адресом (хо,Уо) на который указывает световое перо 14. Храняпщйся в регистре 6 j п-разрядный код призна ка редактирования на j-том уровне, который имел указанный (хо, Уо) эле мент изображения, с его выхода пост пает на второй вход блока 8 j сравн НИН, где осуществляется сравнение п-разрядного кода признака редактирования на J-TOM уровне указанного (xd, УО) элемента изображения с празрядными кодами признаков редакти рования на J-TOM уровне (х, у) теку щих элементов изображения синхронно с TV разверткой блока 13 индикации. При сравнении каждой пары п-раз рядных признаков редактирования на уровне в блоке 8 j сравнения вырабатывается сигнал логической еди ницы при равенстве кодов признаков редактирования на J-TOM уровне и си нал логического нуля - в противном случае. Сигнал с выхода блока 8 j сравнения поступает на первый вход j-ro элемента ИЛИ 9 j, на второй вход которого поступает сигнал с выхода редактирования на J-TOM уровне блока 15 управления; Выбор j-ro уров ня редактирования осуществляется сигналом логического нуля, установленным оператором на выходе редактирования на J-TOM уровне блока 15 управления (тумблер 27 j замкнут). В этом случае сигнал с выхода блока 8 j сравнения поступает без изменения через j-тый элемент ИЛИ 9 j на j-тый вход элемента И 10, в противном случае, вне зависимости от сигнала с выхода блока 8 j сравнения, на j-тый вход элемента И 10 будет поступать сигнал логической единицы Таким образом, если на выходе редактирования по j-му уровню блока 15 управления оператором устанавливается сигнал логического нуля, а на выходах редактирования по остальным уровням блока 15 управления - сигна,лы логической единицы, что означает выбор оператором редактирования по j-му уровню, то на экране блока 13 индикации отображаются только те (х, у) текущие элементы изображения у которых п-разрядный код признака редактирования по j-му уровню равен п-разрядному коду признака редактирования по j-му уровню указанного свето1вым пером 14 (х«,уо) элемента изображе ия.Это означает, что на экране блока 13 индикации отображаются только 47020 фрагменты j-ro уровня, п-разрядный код признака редактирования которых равен п-разрядному коду признака редактирования по j-му уровню указанного датчиком 14 (хо, Уо) элемента изображения. При сигнала логического нуля на нескольких выхода х редактирования по уровню на экране блока 13 индикации отображаются только те текущие (х, у) элементы изображения, у которых п-разрядные коды признаков редактирования на всех выбранных уровнях равны п-разрядным кодам признака редактирования на всех выбранных уровнях указанного световым пером 14 (хо, Уо) элемента изображения, так как только в эти моменты времени на все К входы элемента И 10 подаются сигналы логической единицы, 1C выхода которого сигнал логической единицы через второй элемент ИЛИ 1 1 .2 проходит на пятый вход блока 7 логической обработки. С выхода второго элемента ИЛИ 11.2 сигнал поступает на объединенные вторые входы всех элементов И 23.1, 23.2...23т блока 7 логической обработки, являющегося пятым его входом (фиг;3). С выхода блока 2 памяти признаков редактирования разрядный код яркости (х, у) элемента изображения поступает на третий вход блока 7 логической обработки. При этом на третьи входы каждого элемента И 23. 1... 23т поступает соответствующий разряд разрядного кода. Так как на объединенных первых входах элементов И 23.1...23т - сигнал логической единицы, то прохождение с третьего входа блока 7 логической обработки т-разрядного кода яркости (х, у) элемента изображения на его выход зависит от значения сигнала на пятом входе блока 7 логичес- кой обработки. Если сигнал равен логической единице, то т-разрядный код яркости (х, у) элемента изображения проходит на выход блока 7 логической обработки без изменения, а если этот сигнал равен логическому нулю, то все разряды т-разрядного кода яркости (х, у) элемента изображения на выходе блока 7 логической обработки равны логическому нулю (табл.2). С выхода блока 7 логической обработки т-разрядный сигнал кода яркое-, ти (х, у) элемента изображения поступает через блок 2 модуляции на информационный вход блока 13 индикации, на экране которого данная информация отображается. Таким образом, на экране блока 13 индикации будут отображаться из всего кадра только те фрагменты {(х, у) элементы изображения, составляющие эти фрагменты, п-разрядные кодь признаков редактирования на выбранных oneратором в блоке 15 управления уровнях которых равны п-разрядным кодам признаков редактирования на соответствующих уровнях указанного датчиком 14 (х,. Уд) элемента изображения на экране блока 13 индикации.

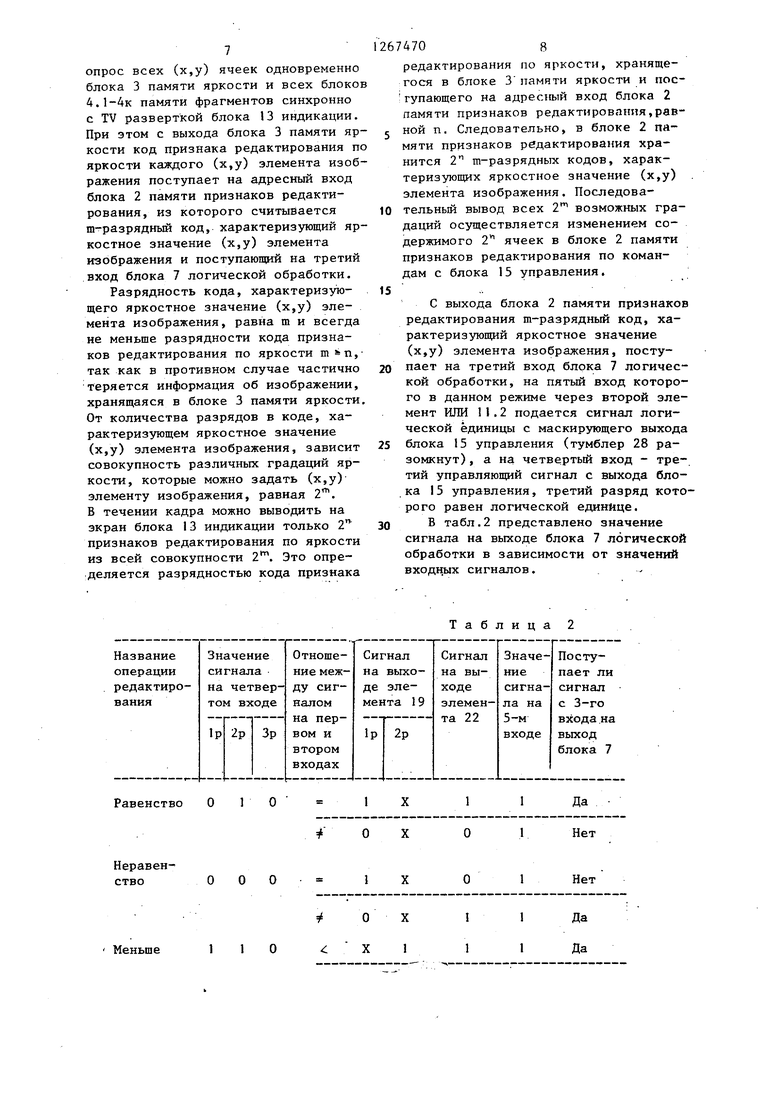

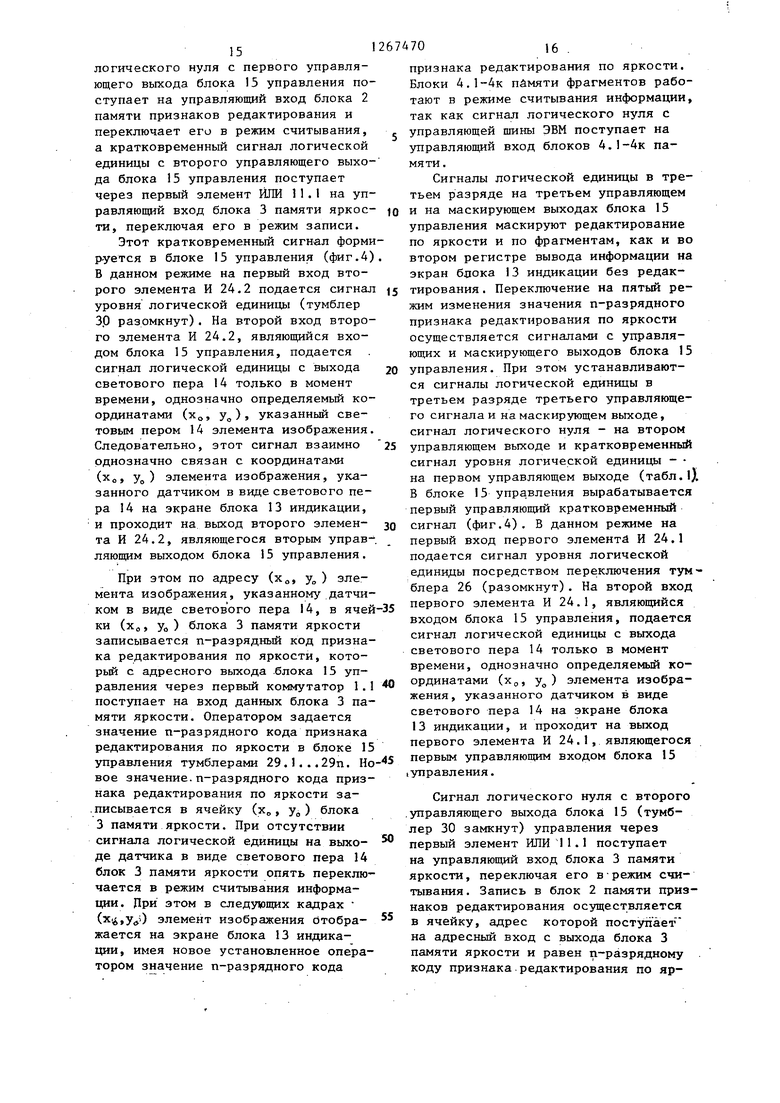

Пример работы устройства в шестом режиме вывода информации на экран блока 13 индикации с возможностью редактирования групп элементов, объединенньпс в фрагмент заданного уровня

Имеется изображение, которое предварительно закодировано на фрагменты на каждом уровне. При этом как выбор количества уровней () и зна чения каждого из них, так и выделение фрагментов на каж.дом уровне производятся заранее, до записи изображения в блок 3 памяти яркости и в блоки 4.1, 4.2, 4.3 памяти фрагментов устройства (фиг.5). Пусть максимальное количество фрагментов на каждом уровне равно 8 )„

Оператор посредством датчика 14. указьгоает на (хо, Уо) элемент изображения на экране блока 13 индикации. 12-ти разрядное слово, характеризующее данный (ХО,У„) элемент изображения, записывается в регистры 5, 6.1, 6.2, 6.3 из ячеек соответПоложительный эффект заключается в расширении области применения устствующих блоков 3 памяти яркости и фрагментов 4.1, 4,2. 4.3. При этом в ячейку (х„, Уо) блока 3 памяти яркости записывается 3-х разрядный код признака редактирования по- яркости (хо, УО) элемента изображения в ячейку (хо, у„ ) блока 4.1 памяти фрагментов - 3-х разрядный код признака редактирования на первом уровне (хо, УО) элемента изображения в ячейку (ХО,У„) блока 4.2 памяти фрагментов - 3-х разрядный код признака редактирования на втором уровне (х,, у,) элемента изображения, а в ячейку (хо УО) блока 4.3 памяти фрагментов3-х разрядный код признака редактирования на третьем уровне (хо, у) элемента изображения (табл.3). Всего возможно 8 (2, при ) вариантов редактирования по уровням (фиг.6) в зависимости от значений сигналов редактирования на 1,2 и 3 уровнях, поступающих соответственно с выходов редактирования на 1,2 и 3 уровни блока 15 управления. Первый вариант редактирования по уровням равнозначен маскированию редактирования по фрагментам, т.е. на экране блока 13 индикации отображаются все фрагменты изображения. Варианты редактирования 2,3,5 являются вариантами редактирования только на одном уровне, соответственно третьем, втором и первом. Остальные варианты редактирования 4,6,7,8 являются соответствующим пересечением вариантов редактирования 2,3,5 изображений В.4 В.2 А В.З;

Таблица 3

ройства за счет обеспечения возможности редактирования информации пересекающимися группами элементов, объ диненных в фрагменты различных уров ней обобщения, что позволяет повысить скорость редактирования сложны графических изображений. Увеличение скорости редактирования изображений по сравнению с прототипом достигает ся за счет того, что информация, под лежащая отображению, может быть выведена на блок индикации полностью или частично в виде фрагментов любо го уровня. Это позволяет оператору, задавая определенный уровень редактирования, выводить на экран блока индикации фрагмент данного уровня, который подлежит редактированию., и производить изменения выделенного фрагмента целиком, а не поэлементно Формула изобретения Устройство для отображения информации, содержащее два коммутатора, управляющие входы которых являются управляющими входами устройства, первый сигнальный вход первого коммутатора является входом данных устройства, выход подключен к входу дан ных блока памяти яркости, первый сиг нальный вход второго коммутатора является адресным входом устройства, выход соединен с адресным входом бло ка памяти яркости, управляющий вход которого соединен с выходом первого элемента ИЛИ, первый вход которого является управляющим входом устройства, выход блока памяти яркости сое динен с информационным входом регист ра, с адресным входом блока памяти признаков редактирования и с первым входом блока логической обработки, управляющий вход регистра соединен с входом блока управления и выходом датчика в виде светового пера, оптически связанного с блоком индикации выход регистра соединен с вторым вхо дом блока логической обработки, вход которого соединен с входом блока модуляции, выход которого соединен с информационным входом блока индикации, синхронизирующий вход которого 47024 соединен с синхронизирующим выходом блока синхронизации, адресный выход которого соединен с вторым сигнальным входом второго коммутатора, выход блока памяти признаков р едактирования соединен с третьим входом блока логической обработки, первьтй У11равляю1ций выход блока управления соединен с управляющим входом блока памяти признаков редактирования, второй управляющий выход - с вторым входом первого элемента ИЛИ, адресный выход - с вторым сигнальным входом первого коммутатора, третий управляющий выход - с четвертым входом блока логической обработки, информационньй выход - с входом данных блока памяти признаков редактирования, отличающееся тем, что, с целью расширения области применения устройства за счет обеспечения возможности редактирования информации пересекающимися группами элементов, объединенных в фрагменты различных уровней обобщения, и повышения быстродействия устройства, введены цепочки из последовательно соединенных блока памяти фрагментов, второго регистра, блока сравнения и второго элемента ИЛИ, элемент И и третий элемент ИЛИ, управляющие входы блока памяти фрагментов являются . управляющими входами устройства, адресные входы соединены с выходом второго коммутатора, входы данных - с выходом первого коммутатора, выходы с вторыми входами блоков сравнения, управляющие входы вторых регистров соединены с выходом датчика в виде светового пера, вторые входы вторых элементов ИЛИ соединены с вьЬсодами редактирования по соответствующему уровню блока управления, выходы вторых элементов ИЛИ - с соответствующими входами элемеита И, выход которого соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с маскирующим выходом блока управления, выход третьего элемента ИЛИ - с пятым входом блока ло- . гической обработки.

Jftxoff

r

Принер;

тг

ФОН

A

A

«sa

s

Oj/pottHt точечные (x,у) элементы uioSpa/ enua .S

В

() Злемент uaoSpai reHufi,указанный cSemotbiM Iput.E

| Устройство для отображения информации | 1979 |

|

SU932530A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Устройство для редактирования алфавитно-цифровой информации на экране электронно-лучевой трубки | 1982 |

|

SU1156118A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1986-10-30—Публикация

1985-06-07—Подача