4 синхронизации, блока 5 задержки и формирователя 6 строб-импульсов. . Входной сигнал с клеммы 7 подается на блок А синхронизации и на неинвертирующий вход компаратора 1 , инвертирующий вход которого соединен с выходной клеммой 8, соединенной с выходом интегратора 10. На неинверти- рующий вход интегратора 10 (операционный усилитель 11 и конденсатор 12) подключен источник 9 смещения, а На инвертирующий вход его - инвертирующий выход D-триггера 2 через резистор 14. Тактовый вход -Т -триггера 2 соединен с неинвертирующими вы

ходом формирователя 3 строб-импульсов, инвертирующий которого подключен к тактовому входу реверсивного регистра 13 сдвига. Выходы первого и последнего разрядов регистра 13 сдвига через диоды 15 и 17 и резисторы 16 и 18 соединены с инвертирующим входом интегратора 10. Введение регистра 13 сдвига, диодов 15 и 17 и резистора 18 существенно повышает скорость интегрирования в интеграторе 10 за счет увеличения скорости интегрирования в основной части периода, нарастания выходного напряжения . 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Стабилизированный многофазный импульсный преобразователь постоянного напряжения | 1986 |

|

SU1355965A1 |

| УЛЬТРАЗВУКОВОЙ РАСХОДОМЕР | 2002 |

|

RU2210062C1 |

| Стабилизатор переменного напряжения | 1988 |

|

SU1534434A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ИНТЕРВАЛЫ ВРЕМЕНИ | 2014 |

|

RU2552605C1 |

| Преобразователь напряжение - интервал времени | 1986 |

|

SU1483638A1 |

| ДАТЧИК ТЕМПЕРАТУРЫ С ЧАСТОТНЫМ ВЫХОДОМ | 1991 |

|

RU2017087C1 |

| Преобразователь тока в частоту | 1989 |

|

SU1695504A1 |

| Цифровой регистратор повторяющихся сигналов | 1987 |

|

SU1610279A1 |

| ПИКОВЫЙ ДЕТЕКТОР | 2012 |

|

RU2506598C1 |

| УРАВНОВЕШИВАЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1995 |

|

RU2101859C1 |

Изобретение может быть использовано для измерения мгновенных значений напряжения периодических сигналов произвольной формы. Цель изобрения - повышение быстродействия преобразователя. Он содержит компаратор 1, 13 -триггер 2, формирователь 3 строб-импульсов, состоящий из блока

Изобретение относится к электроизмерительной технике и может быть использовано для измерения мгновенных значений напряжения периодических сигналов произвольной формы.

Цель изобретения - повыгаение быстродействия преобразователя,

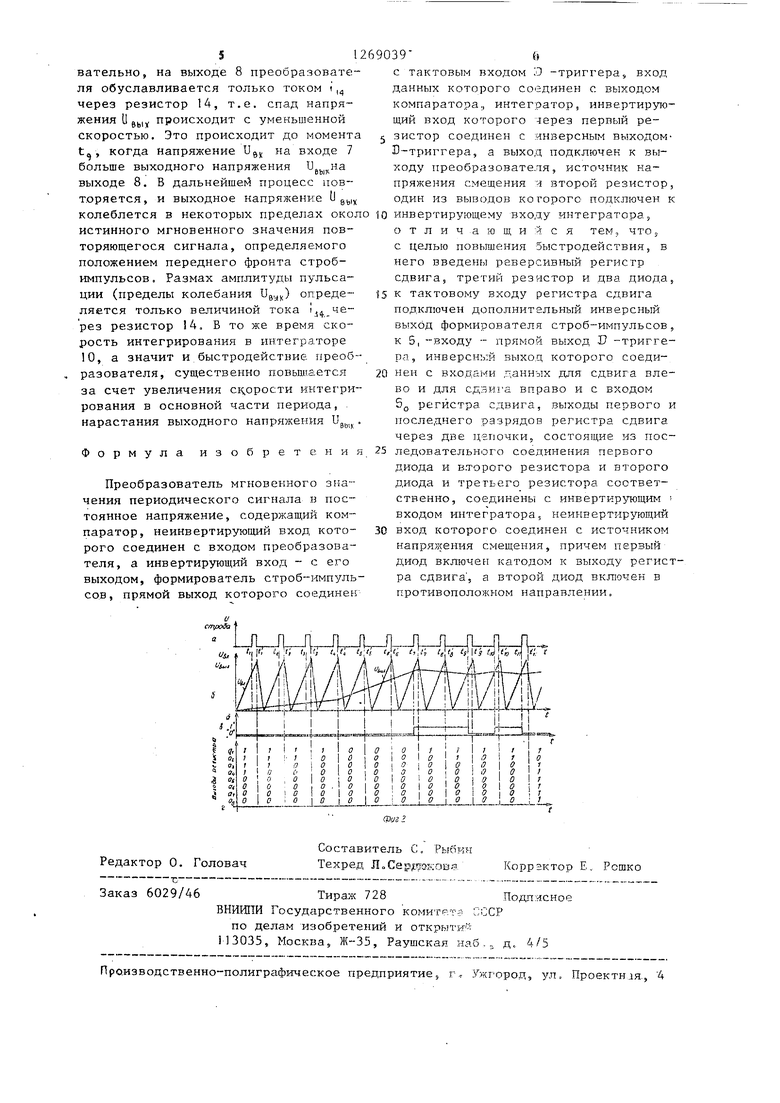

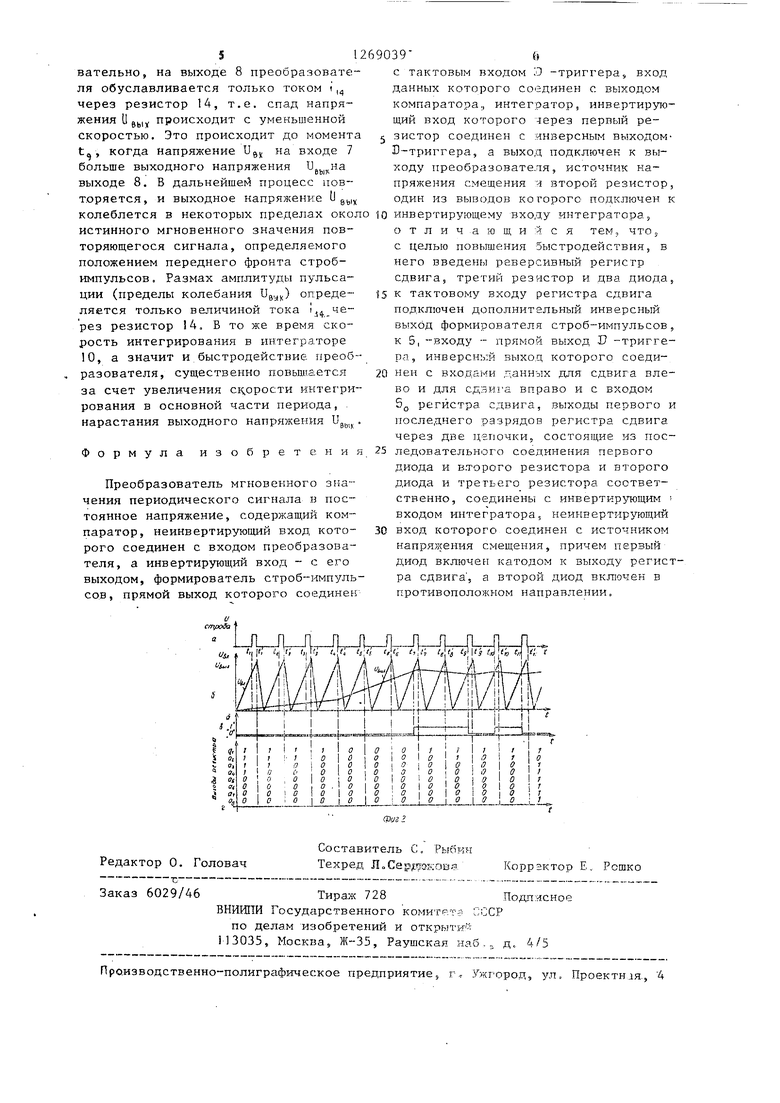

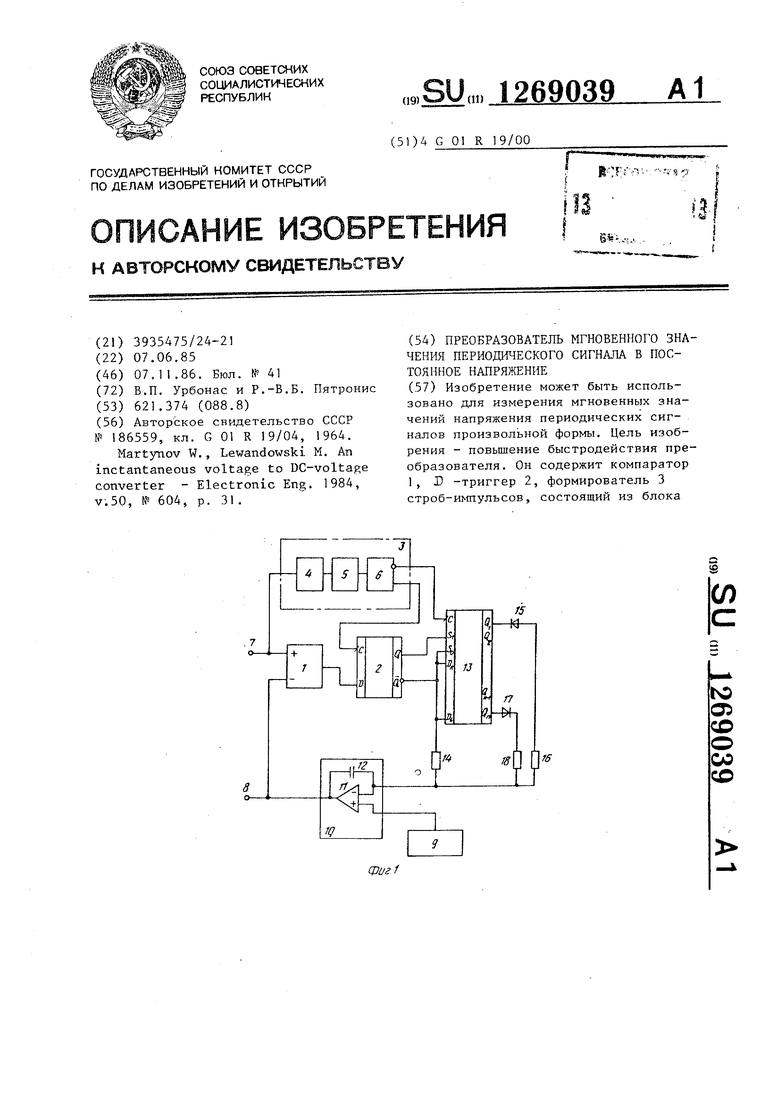

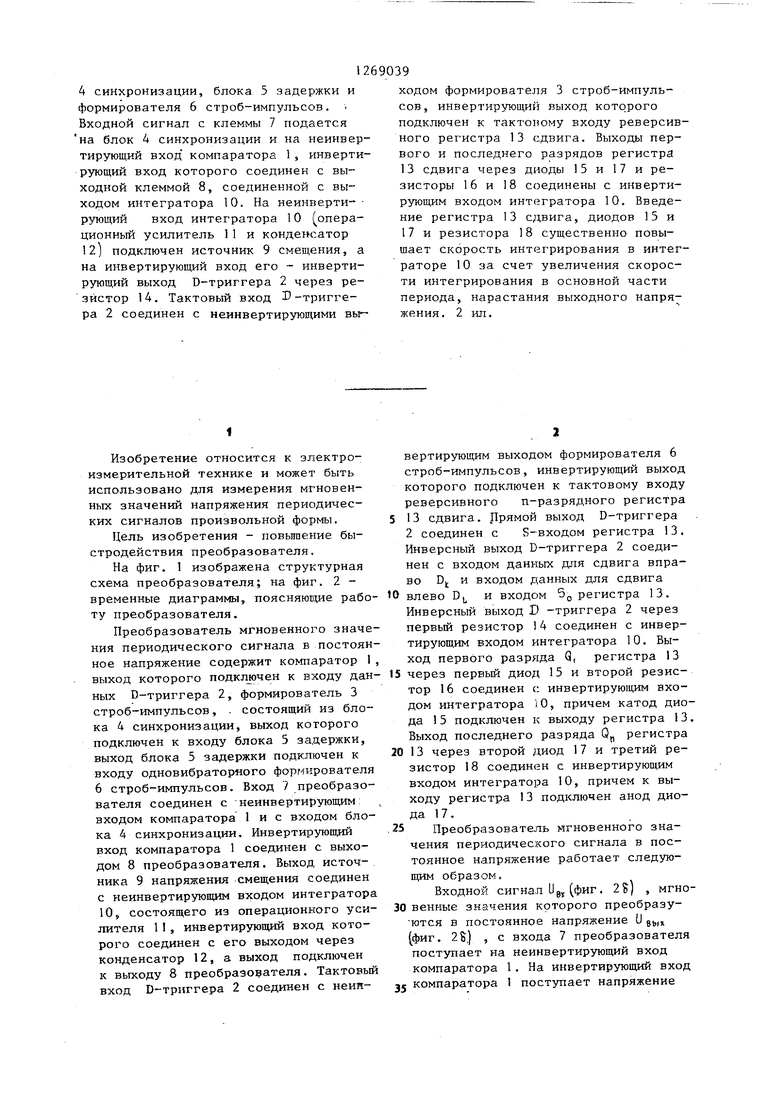

На фиг. 1 изображена структурная схема преобразователя; на фиг. 2 временные диаграммы, поясняюи ие работу преобразователя.

Преобразователь мгновенного значения периодического сигнала в постоянное напряжение содержит компаратор I, выход которого пoдклJoчeн к входу данных D-триггера 2, формирователь 3 строб-импульсов, . состоящий из блока 4 синхронизации, выход которого подключен к входу блока 5 задержки, выход блока 5 задержки подключен к входу одновибраторного формирователя 6 строб-импульсов. Вход 7 преобразователя соединен с неинвертирующим: входом компаратора 1 и с входом блока 4 синхронизации. Инвертируюшдш вход компаратора 1 соединен с выходом 8 преобразователя. Выход источника 9 напряжения смещения соединен с неинвертирующим входом интегратора 10 5, состоящего из операционного усилителя 11, инвертирующий вход которого соединен с его выходом через конденсатор 12, а выход подключен к выходу 8 преобразователя. Тактовый вход D-триггера 2 соединен с неиявертирующим выходом формирователя 6 строб-импульсов, инвертирующий выход которого подключен к тактовому входу реверсивного п-разрядного регистра

5 13 сдвига. РРЯМОЙ выход D-триггера 2 соединен с S-входом регистра 13. Инверсный выход D-триггера 2 соединен с входом данных для сдвига вправо DIJ и входом данных для сдвига

О влево Т) и входом З регистра 13. Инверсный выход I) -триггера 2 через первый резистор 14 соединен с инвертирующим входом интегратора 10. Выход первого разряда Q, регистра 13

15 через первый диод 15 и второй резистор 16 соединен с инвертируюнщм входом интегратора 50, причем катод диода 15 подключен к выходу регистра 13 Выход последнего разряда Q регистра

20 13 через второй диод 17 и третий резистор 18 соединен с инвертирующим входом интегратора 10, причем к выходу регистра 13 подключен анод диода 17.

,25 Преобразователь мгновенного значения периодического сигнала в постоянное напряжение работает следующим образом.

Входной сигнал иg (фиг. 2) , мгно30 венные значения которого преобразуются в постоянное напряжение U gj,, (фиг. 2fii , с входа 7 преобразователя поступает на неинвертирующий вход компаратора 1. На инвертирующий вход

JJ компаратора 1 поступает напряжение

(Jgj , которое одновременно подается на выход 8 преобразователя и является выходным напряжением, величина к торого равна мгновенному значению периодического сигнала в моменты вр меня, определяемые положением стробимпульсов. В результате сравнения сигналов Ujj и выходе компаратора 1 формируется соответствующий логический сигнал: сигнал высокого уровня (логическая 1), если напряжение на неинвертирующем входе превышает напряжение на инвертирующем входе (U g Ug) , или сигнал низкого уровня (логический О), если имеет место обратное соотношение входных уровней (Ug аык

В момент поступления на тактовый вход Г -триггера 2 фронта строб-импульса с неинвертирующего входа формирователя 6 строб-импульсов (моменты t, , t,..., t,, , фиг. 2 а ), результат сравнения напряжений U и и,, фиксируется Р -триггером 2 и сохраняется неизменным вплоть до прихода на него следующего строб-импульса. В момент поступления среза строб-импульсов (моменты t, , t , . . . , tl, ) состояние Е -триггера 2 перезаписывается в регистр 13. При наличии ло- гического О на инвертирующем выходе Q D -триггера 2 этот сигнал в регистр 13 вводится только через вход D( в разряд Q j и по мере поступления строб-импульсов сдвигается в левую сторону регистра 13 (в направлении разряда Q,). При наличии логической 1 на инвертирующем выходе Q D-триггера 2 этот сигнал в резистр 13 вводится только через вход Dj, в разряд Q, и по мере поступления строб-импульсов сдвигается вправо (в направлении разряда Q). Описание изменения состояния выходов регистра 13 по мере поступления строб-импульсов показано на фиг.2 г , на фиг.26 показано состояние инвертирующего выхода Q D-триггера 2. При этом необходимо, чтобы длительность строб-импульсов была не менее времени задерж ки распространения сигнала в D-триггере 2 и не более Т/п.

На инвертирующий вход интегратора 10 одновременно поступают логические сигналы с инвертирующего выхода D -триггера 2 и с выходов Q, и 0 регистра 13. На неинвертирующий вход интегратора 10 от источника 9 смешения поступает напряжение, равное среднему арифметическому значению напряжений логического О и логической 1.

Преобразователь при подаче на вход 7 положительных импульсов (фиг.2 при разрядности регистра 13 п 8 работает следующим образом. Допустим, что в исходном состоянии разряды регистра 13 Q,- Q имеют информацию логической 1, а разряды - информацию логического О (первая колонка цифр, фиг. 2 г) .В момент t, напряжение на входе 7 превышает напряжение на выходе 8. На выходе Q D-триггера 2 фиксируется логический О fфиг.21), и через вход Р регистра 13 он записывается в разряд Og . Одновременно логический О сдвигается в разряд Q регистра 13 (вторая колонка цифр фиг. 2lJ , Скорость изменения выходного напряжения интегратора 10 при этом определяется суммарным входным током через резисторы 14, 16 и 18. Поскольку диоды 15 и 17 заперты, то ток через резисторы 16 и 18 не протекает, и скорость интегрирования в рассматриваемый момен времени определяется только током через резистор 14. Аналогичная картина наблюдается до прихода четвертого строб-импульса. После момента t логический О сдвигается в разряд Q,. Диод 15 открывается, начинает протекать ток через, резистор 16. Скорость изменения выходного напряжения интегратора 10 увеличивается. Для надежной работы схемы необходимо, чтобы выполнялось условие

.i6 п

1„ 2 где i|q , (б токи через резисторы 14

и 16 соответственно. В этом случае скорость изменения выходного напряжения интегратора 10 увеличивается в п/2 раз, что дает увеличение быстродействия преобразователя почти в п/2 раза.

При превышении входного напряжения Ugx на входе 7 выходным напряжением на выходе 8дТ.е. Ug, (момент t), на выходе Q D-триггера 2 и на выходе (Э, регистра 13 появляется логическая 1. При этом диод 15 закрывается, и ток через резистор 16 прекращается (1,0). Б результате этого спад выходного напряжения на выходе интегратора 10 и, следо

| 0 |

|

SU186559A1 | |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Martynov W., Lewandowski М | |||

| An inctantaneous voltage to DC-voltage converter - Electronic Eng | |||

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

| Способ очистки нефти и нефтяных продуктов и уничтожения их флюоресценции | 1921 |

|

SU31A1 |

Авторы

Даты

1986-11-07—Публикация

1985-06-07—Подача