Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах.

Цель изобретения - расширение диапазона изменения входных сигналов.

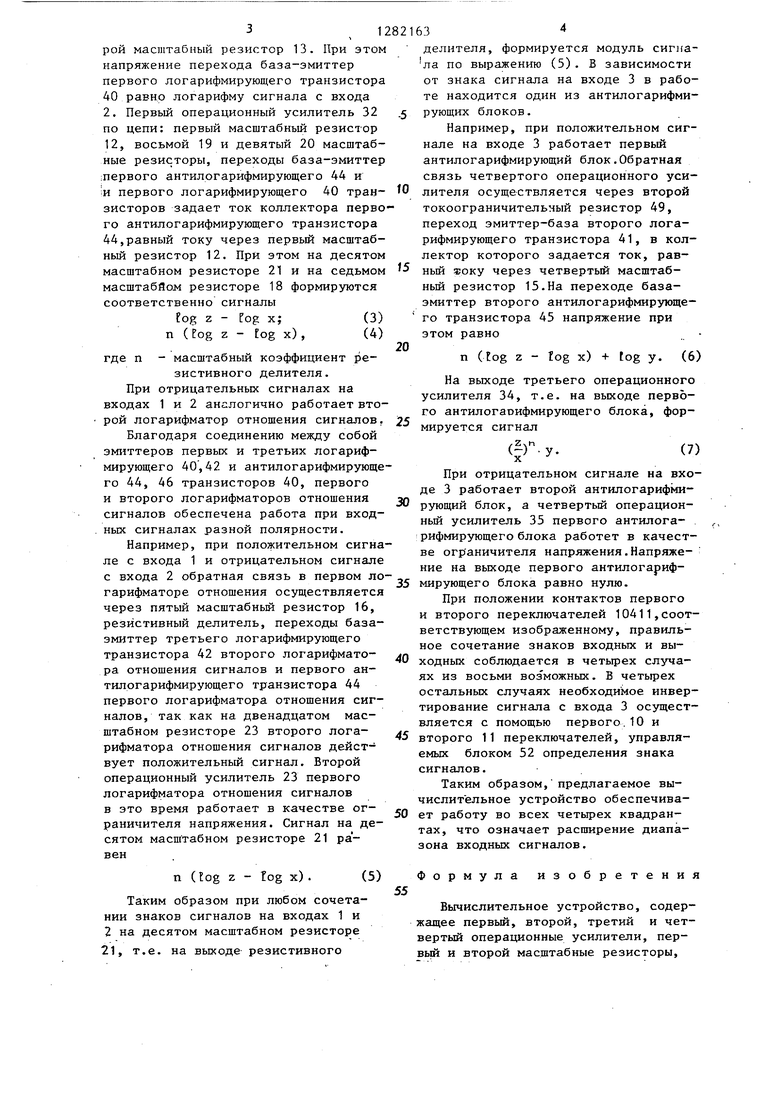

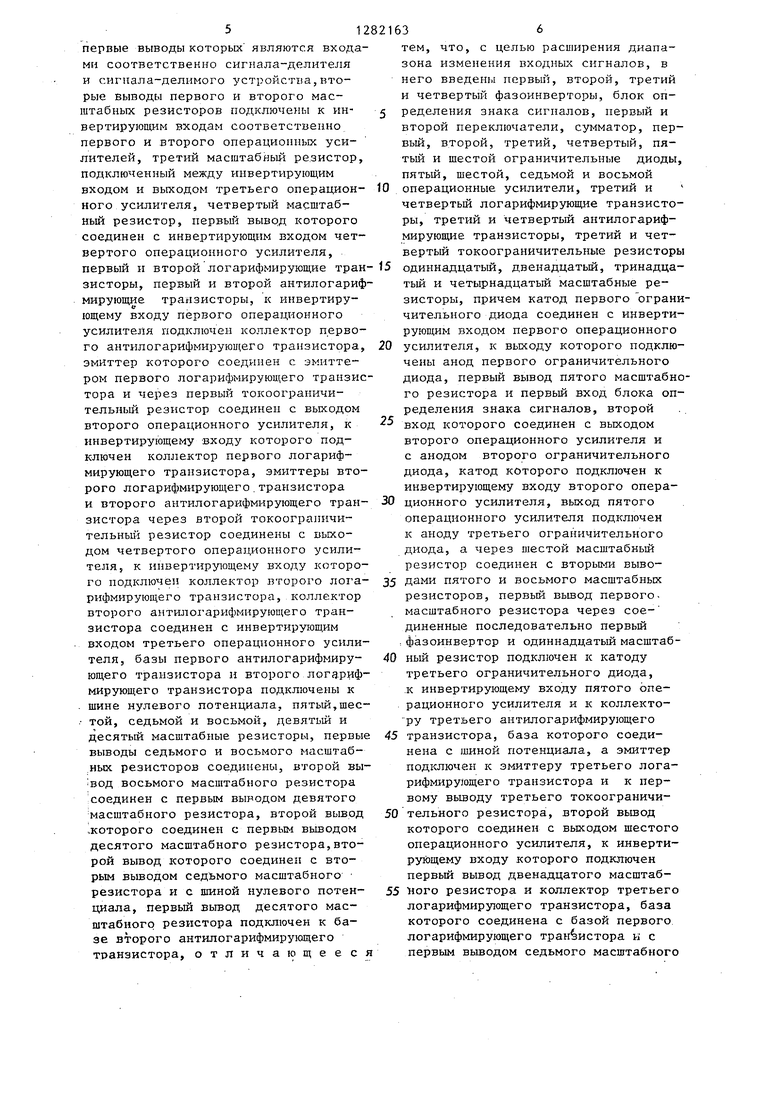

На чертеже изображена функциональная схема вычислительного устройства. Устройство содержит вход 1 сигнала-делителя, вход 2 сигнала-делимого, вход 3 сигнала-сомножителя, выход 4, сумматор 5, первый 6., второй 7, третий 8 и четвертый 9 фазоинверторы, первый 10 и второй 11 переключатели.

Ш

и четвертым 15 масштабньми резисторами, пятым ограничительным диодом 30, вторым логарифмирующим 41 и вторым 45 антилогарифмирующим транзисторами, вторым токоограничи- тельным резистором 49 образуют первый антилогарифмирующий блок.Седьмой 38 и восьмой 39 операционные усилители совместно с тринадцатым 24 и четырнадцатым 25 масштабными резисторами, шестым ограничительным диодом 31, четвертым логарифмирующим 43 и четвертым антилогарифмирующим 47 транзисторами,чет - .- ,

первый 12, второй 13, третий 14, чет- вертым токоограничительным резисто- вертый 15, пятый 16, шестой 17, седь- ром 51 образуют второй антилогарифмой 18, восьмой 19, девятый 20, деся- тьй 21, одиннадцатый 22, двенадцатый 23, тринадцатый 24 и четырнадцатый 25 масштабные резисторы, первый 26, второй 27, третий 28,четвертый 29, пятый 30 и шестой 31 ограничительные диоды, первьш 32, второй 33, третий 34, чёт вертый 35, пятьш 36, шестой 37, седьмой 38 и восьмой 39 операционные усилители, первый 40, втлрой 41, третий 42 и четвертый 43 логарифмирующие транзисторы,первый 44, второй 45, третий 46 и четвертый 47 антилогарифмирующие транзисторы, первый 48, второй 49,третий 50 и четвертый 51 токоограничи- тельные резисторы, блок 52 определения знака сигналов, шину 53 нулевого потенциала.

Вычислительное устройство работает следующим образом.

Первый 32 и второй 33 операционные усилители совместно с первым 12 и вторым 13 масштабными резисторами, первым 26 и вторым 27 ограничительными диодами, первым логарифмирующим 40 и первым антилогарифми- рующимГ 44 транзисторами, первым токоограничительным резистором 48 образуют первый логарифматор отношения сигналов. Пятый 36 и шестой 37 операционные усилители.совместно с одиннадцатым 22 и двенадцатым 23 масштабными резисторгми, третьим 28 и четвертым 29 ограничительными диодами , третьим логарифмирующим 42 и третьим антилогарифмирующим 46 транзисторами, третьим токоограничительным резистором 50 образуют второй логарифматор отношения сигна- лов.Третий 34 и четвертый 35 операционные усилители совместно с третьим 14

20

мирующий блок.

Восьмой 19 и девятый 20 масштабные резисторы могут быть заменены потенциометром для плавного изменения коэффициента деления резистив- ного делителя, образованного седьмым 18, восьмым 19, девятым 20 и уг десятым 21 масштабными резисторами.

Вычисление выражения вида

/2,и F (-) . У,

где Z, X, у

30

35

40

45

50

(1

- входные знакопеременные сигналы; п - показатель степени

(0,2 п 5),

реализуется в устройство с помощью логарифмического алгоритма

F antitog п (fog Z - fog х) + + fog у .(2)

Первый и второй логарифматоры от ношения сигналов и первый и второй антилогарифмирующие блоки работают только при положительных сигналах на их входах.

При входных сигналах одной полярности в рабочем состоянии находятся один из логарифматоров отношения си налов, а операционные усилители дру гого работают в качестве ограничите ля напряжения. Например, при положи тельных сигналах с входов 1 и 2 работает только первый логарифматор отношения сигналов. При этом сигналы с помощью первого 12 и второго 13 масштабных резисторов преобразуются в ток. Второй операционный усилителЪ 22 по цепи: первый токоограничитель ный резистор 48, переход база-эмиттер первого логарифмирующего транзистора 40, задает ток коллектора, оавный току, протекающему через вто

и четвертым 15 масштабньми резисторами, пятым ограничительным диодом 30, вторым логарифмирующим 41 и вторым 45 антилогарифмирующим транзисторами, вторым токоограничи- тельным резистором 49 образуют первый антилогарифмирующий блок.Седьмой 38 и восьмой 39 операционные усилители совместно с тринадцатым 24 и четырнадцатым 25 масштабными резисторами, шестым ограничительным диодом 31, четвертым логарифмирующим 43 и четвертым антилогарифмирующим 47 транзисторами,чет

мирующий блок.

Восьмой 19 и девятый 20 масштабные резисторы могут быть заменены потенциометром для плавного изменения коэффициента деления резистив- ного делителя, образованного седьмым 18, восьмым 19, девятым 20 и десятым 21 масштабными резисторами.

Вычисление выражения вида

/2,и F (-) . У,

где Z, X, у

(1)

- входные знакопеременные сигналы; п - показатель степени

(0,2 п 5),

реализуется в устройство с помощью логарифмического алгоритма

F antitog п (fog Z - fog х) + + fog у .(2)

0

5

0

Первый и второй логарифматоры отношения сигналов и первый и второй антилогарифмирующие блоки работают только при положительных сигналах на их входах.

При входных сигналах одной поляр ности в рабочем состоянии находятся один из логарифматоров отношения сигналов, а операционные усилители другого работают в качестве ограничителя напряжения. Например, при положительных сигналах с входов 1 и 2 работает только первый логарифматор отношения сигналов. При этом сигналы с помощью первого 12 и второго 13 масштабных резисторов преобразуются в ток. Второй операционный усилителЪ 22 по цепи: первый токоограничитель- ный резистор 48, переход база-эмиттер первого логарифмирующего транзистора 40, задает ток коллектора, оавный току, протекающему через вто3 12

рой масштабный резистор 13. При этом напряжение перехода база-эмиттер первого логарифмирующего транзистора 40 равно логарифму сигнала с входа 2. Первый операционный усилитель 32 по цепи: первый масштабный резистор 12, восьмой 19 и девятый 20 масштабные резисторы, переходы база-эмиттер :первого антилогарифмирующего 44 и iH первого логарифмирующего 40 тран- зисторов задает ток коллектора первого антилогарифмирующего транзистора 44,равный току через первый масштабный резистор 12. При этом на десятом масштабном резисторе 21 и на седьмом масштабЯом резисторе 18 формируются соответственно сигналы

fog Z - fog х; п (fog Z - fog х) ,

где п - масштабный коэффициент ре- зистивного делителя.

При отрицательных сигналах на входах 1 и 2 аналогично работает второй логарифматор отношения сигналов.

Благодаря соединению между собой эмиттеров первых и третьих логарифмирующего 40,42 и антилогарифмирующего 44, 46 транзисторов 40, первого и второго логарифматоров отношения сигналов обеспечена работа при входных сигналах разной полярности.

Например, при положительном сигнале с входа 1 и отрицательном сигнале с входа 2 обратная связь в первом ло гарифматоре отношения осуществляется через пятый масштабный резистор 16, резистивный делитель, переходы база- эмиттер третьего логарифмирующего транзистора 42 второго логарифмато- pa отношения сигналов и первого антилогарифмирующего транзистора 44 первого логарифматора отношения сигналов, так как на двенадцатом масштабном резисторе 23 второго лога- рифматора отношения сигналов действует положительный сигнал. Второй операционный усилитель 23 первого логарифматора отношения сигналов в это время работает в качестве ог- раничителя напряжения. Сигнал на десятом масш табном резисторе 21 ра - вен

п (og Z - tog х).

Таким образом при любом сочетании знаков сигналов на входах 1 и 2 на десятом масштабном резисторе

21, т.е. на выходе резистивного

821

.5 О

20

25

JQ 634

делителя, формируется модуль сигла- ла по выражению (5). В зависимости от знака сигнала на входе 3 в работе находится один из антилогарифми- рующих блоков.

Например, при положительном сигнале на входе 3 работает первый антилогарифмирующий блок.Обратная связь четвертого операционного усилителя осуществляется через второй токоограничительный резистор 49, переход эмиттер-база второго логарифмирующего транзистора 41, в коллектор которого задается ток, равный жоку через четвертый масштабный резистор 15.На переходе база- эмиттер второго антилогарифмирующего транзистора 45 напряжение при этом равно

п (Eog Z - tog х) + tog у. (6)

На выходе третьего операционного усилителя 34, т.е. на выходе первого антилогаоифмирующего блока, формируется сигнал

(7)

,2чП

(-) -у.

35

JQ - Q rg

55

При отрицательном сигнале на входе 3 работает второй антилогарифмирующий блок, а четвертый операционный усилитель 35 первого антилога- : рифмирующего блока работет в качестве огр аничителя напряжения. Напряже- ние на выходе первого антилогарифмирующего блока равно нулю.

При положении контактов первого и второго переключателей 10411,соответствующем изображенному, правильное сочетание знаков входных и выходных соблюдается в четырех случаях из восьми возможных. В четьфех остальных случаях необходимое инвертирование сигнала с входа 3 осуществляется с помощью первого.10 и второго 11 переключателей, управляемых блоком 52 определения знака сигналов.

Таким образом, предлагаемое вычислительное устройство обеспечивает работу во всех четырех квадрантах, что означает расширение диапазона входных сигналов.

Формула изобретения

Вычислительное устройство, содержащее первый, второй, третий и четвертый операционные усилители, пер- вьш и второй масштабные резисторы.

первые выводы которых являются входами соответственно сигнала-делителя и сигнала-делимого устройства,вторые выводы первого и второго масштабных резисторов подключены к инвертирующим входам соответственно первого и второго операционных усилителей, третий масштабный резистор, подключенный между инвертирующим входом и выходом третьего операционного усилителя, четвертый масштаб- ньй резистор, первьш вывод которого соединен с инвертирующим входом четвертого операционного усилителя, первый и второй логарифмирующие трак зисторы, первый и второй антилогариф мирующие транзисторы, к инвертирующему входу первого операционного усилителя подключен коллектор первого антилогарифмируюи1;его транзистора, эмиттер которого соединен с эмиттером первого логарифмирующего транзистора и через первый токоограничи- тельньй резистор соединен с выходом второго операционного усилителя, к инвертирующему входу которого подключен коллектор первого логарифмирующего транзистора, эмиттеры второго логарифмирующего.транзистора и второго антилогарифмирующего транзистора через второй токоограничи- тельный резистор соединены с выходом четвертого операционного усилителя, к инвертирующему входу которого нодключен коллектор второго логарифмирующего транзистора, коллектор второго антш1О1 арифмирующего транзистора соединен с инвертирующим входом третьего операционного усилителя, базы первого антилогарифмирующего транзистора и второго логариф мирующего транзистора подключены к . щине нулевого потенциала, пятый,щес- . той, седьмой и восьмой, девятый и десятый масщтабные резисторы, первые выводы седьмого и восьмого масштабных резисторов соединены, второй вы- вод восьмого масштабного резистора :Соединен с первым выводом девятого масштабного резистора, второй вывод ,которого соединен с первым выводом десятого масщтабного резистора,второй вывод которого соединен с вторым вьшодом седьмого масштабного резистора и с шиной нулевого потенциала, первый вывод десятого масштабного резистора подключен к базе второго антилогарифмирующего транзистора, отличающеес

15

21636

тем, что, с целью расширения диапазона изменения входных сигналов, в него введены первый, второй, третий и четвертый фазоинверторы, блок определения знака сигналов, нервый и второй переключатели, сумматор, первый, второй, третий, четвертый, пятый и шестой ограничительные диоды.

0

0

25

15

пятый, шестой, седьмой и восьмой

30

операционные усилители, третий и четвертьш логарифмирующие транзисторы, третий и четвертый антилогариф- мирующие транзисторы, третий и четвертый токоограничительные резисторы одиннадцатый, двенадцатый, тринадцатый и четырнадцатый масштабные резисторы, причем катод первого ограничительного диода соединен с инвертирующим входом первого операционного усилителя, к выходу которого подключены анод первого ограничительного диода, первый вывод пятого масштабного резистора и первый вход блока определения знака сигналов, второй вход которого соединен с выходом второго операционного усилителя и с анодом второго ограничительного диода, катод которого подключен к инвертирующему входу второго операционного усилителя, выход пятого операционного усилителя подключен к аноду третьего ограничительного диода, а через шестой масштабный резистор соединен с вторыми выво35 дами пятого и восьмого масштабных резисторов, первый вьшод первого- масштабного резистора через сое- диненные последовательно первый : фазоинвертор и одиннадцатый масштабный резистор подключен к катоду третьего ограничительного диода, к инвертирующему входу пятого операционного усилителя и к коллектору третьего антилогарифмирующего транзистора, база которого соединена с шиной потенциала, а эмиттер подключен к эмиттеру третьего лога- рифмиру/ощего транзистора и к первому вьшоду третьего токоограничи- тельного резистора, второй вьшод которого соединен с вькодом шестого операционного усилителя, к инвертирующему входу которого подключен первый вывод двенадцатого масштаб55 Мого резистора и коллектор третьего логарифмирующего транзистора, база которого соединена с базой первого логарифмирующего транзистора и с первым выводом седьмого масштабного

40

45

50

резистора, первый вывод второго масштабного резистора через второй фазоинвертор соединен с вторым выводом дренадцатого масштабного резистора, катод четвертого рграничи- тельного диода подключен к инвертирующему входу шестого операционного усилителя, выход которого соединен с анодом четвертого ограничителного диода, выход третьего операционного усилителя через третий фазоинвертор подключен к первому входу сумматора, выход которого является выходом вычислительного устройства, катод пятого ограничительного диода соединен с инвертирующим входом чевертого операционного усилителя, к выходу которого подключен анод пятого ограничительного диода, к инвертирующему входу седьмого операционного усилителя подключен первый вывод тринадцатого масштабного резистора и коллектор четвертого антило- гарифмирующего транзистора, база которого соединена с базой второго антилогарифмирующего транзистора, эмиттер четвертого антилогарифмирующего транзистора соединен с эмиттером четвертого логарифмирующего транзистора и с первым выводом, четвертого- токоограничительного резис-

,

fO

28216 38

тора, второй вывод которого подключен к выходу восьмого операционного усилителя и к аноду шестого ограничительного диода, катод которого соединен с инвертирующим входом восьмого операционного усилителя, с первым вьшодом четырнадцатого масштабного резистора и с коллектором четвертого логарифмирующего транзистора, база которого подключена к шине нулевого потенциала, второй вьшод три- надцатого масштабного резистора соединен с выходом седьмого операционного усилителя и с вторым входом t5 сумматора, вход четвертого фазоин- вертора является входом сигнала-сомножителя устройства и соединен с информационным входом первого переключателя, информационный вход вто 20 рого переключателя подключен к выходу четвертого фазоинвертора, первые выходы первого и второго переключателей соединены с вторым выводом четвертого масштабного резистора, второй вывод четырнадцатого масштабного резистора подключен к вторым :выходам первого и второго переключателей, управляющие входы которых соединены с выходом блока определения знака сигна - лов.

30

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1987 |

|

SU1462364A1 |

| Вычислительное устройство | 1987 |

|

SU1539798A1 |

| Множительно-делительное устройство | 1987 |

|

SU1543426A1 |

| Четырехквадратное множительно-делительное устройство | 1987 |

|

SU1474686A1 |

| Среднеквадратический преобразователь | 1989 |

|

SU1659884A2 |

| Устройство с регулируемым усилением | 1988 |

|

SU1741257A1 |

| Логарифмическое вычислительное устройство | 1987 |

|

SU1543425A1 |

| Устройство усиления | 1985 |

|

SU1338001A1 |

| Устройство регулирования уровня сигнала | 1982 |

|

SU1104653A1 |

| Перемножающее устройство | 1983 |

|

SU1168971A1 |

Изобретение относится к электрическим вычислительным устройствам и может быть использовано в- аналоговых вычислительных машинах. Целью изобретения является расширение диапазона величин входных сигналов.Вычислительное устройство содержит первый и второй операционные усилители, к инвертирующему входу каждого из которых подключены соответствующие масштабные резисторы. Коллектор первого логарифмирующего транзистора подключен к инвертирующему входу второго операционного усилителя,выход которого через первый токоогра- ничительный резистор соединен с эмиттером первого логарифмирующего транзистора и эмиттером первого ан- тилогарифмирующего транзистора.Коллектор последнего соединен с инвертирующим входом первого операционного усилителя. База первого анти- логарифмирующего транзистора подключена к шине нулевого потенциала, а также третий и четвертый операционные усилители. Между инвертирующим входом и выходом третьего операционного усилителя подключен третий масштабный р- зистор.Первый вывод четвертого масштабного резистора подключен к инвертирующему входу четвертого операционного усилителя. Выход последнего через второй токоограничительный резистор соединен с эмиттерами второго логарифмирующего и второго антилогарифмиру- ющего транзисторов, коллекторы которых подключены к инвертирующим входам соответственно четвертого и третьего операционных усилителей. А также пятый, шестой, седьмой, восьмой, девятый и десятый масштабные резисторы, пятый, шестой, седьмой и вось- :мой операционные усилители, сумма- гор, первый, второй, третий и четвертый фазоинверторы, первый и второй переключатели, блок определения знака сигналов, первый, второй, третий, четвертый, пятьй и шестой огра- ничительные диоды, одиннадцатый,двенадцатый, тринадцатый и четырнадцатый масштабные резисторы. Выходы первого и второго фазоинверторов через одиннадцатый и двенадцатый масштабные резисторы подключены к инвертирующим входам пятого и шестого операционных усилителей. Вькод третьего фазоинвертора соединен с первым входом сумматора, второй вход которого подключен к выходу седьмого операционного усилителя. Устройство позволяет вычислять функцию F fz/x) y. 1 ил. I СЛ

Составитель О. Отраднов Редактор Н.Бобкова Техред М.Ходанич Корректор Е.Сирохман

Заказ 7269/49 Тираж 670Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Бон-Бруевич A.M | |||

| и др.Бесконтактные элементы самонастраивающихся систем | |||

| - М.: Машиностроение, 1967, с | |||

| Регулятор для ветряного двигателя в ветроэлектрических установках | 1921 |

|

SU136A1 |

| Фальцовая черепица | 0 |

|

SU75A1 |

| Справочник по нелинейным схемам | |||

| /Под ред | |||

| Д.Шейнголда | |||

| М.: Мир, 1977, с | |||

| Дальномер | 1922 |

|

SU379A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-01-07—Публикация

1985-07-01—Подача