tftuSi

Изобретение относится с контрольно-измерительной технике и может быть использовано для контроля электронных схем..

Цель изобретения расширение функциональных возможностей за счет возможности контроля совпадения результатов из1 ерения с ожидаемым значением с ограничением одновременно испытательных тока и напрЯ5 Сения.

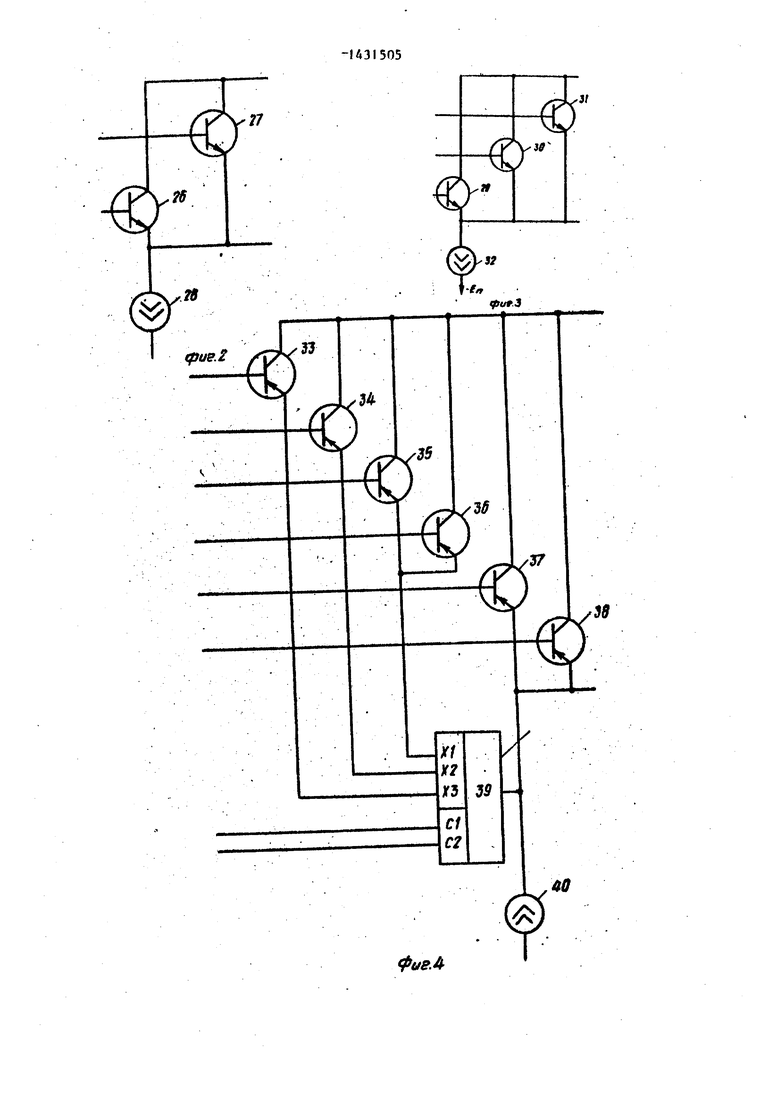

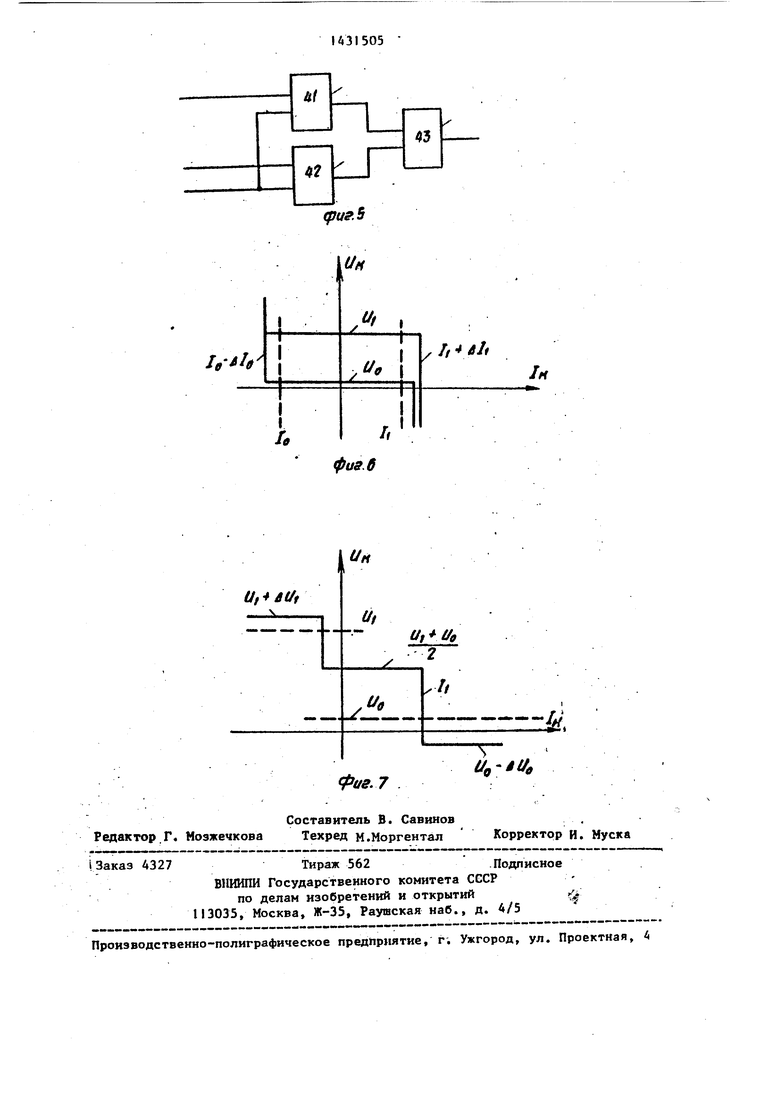

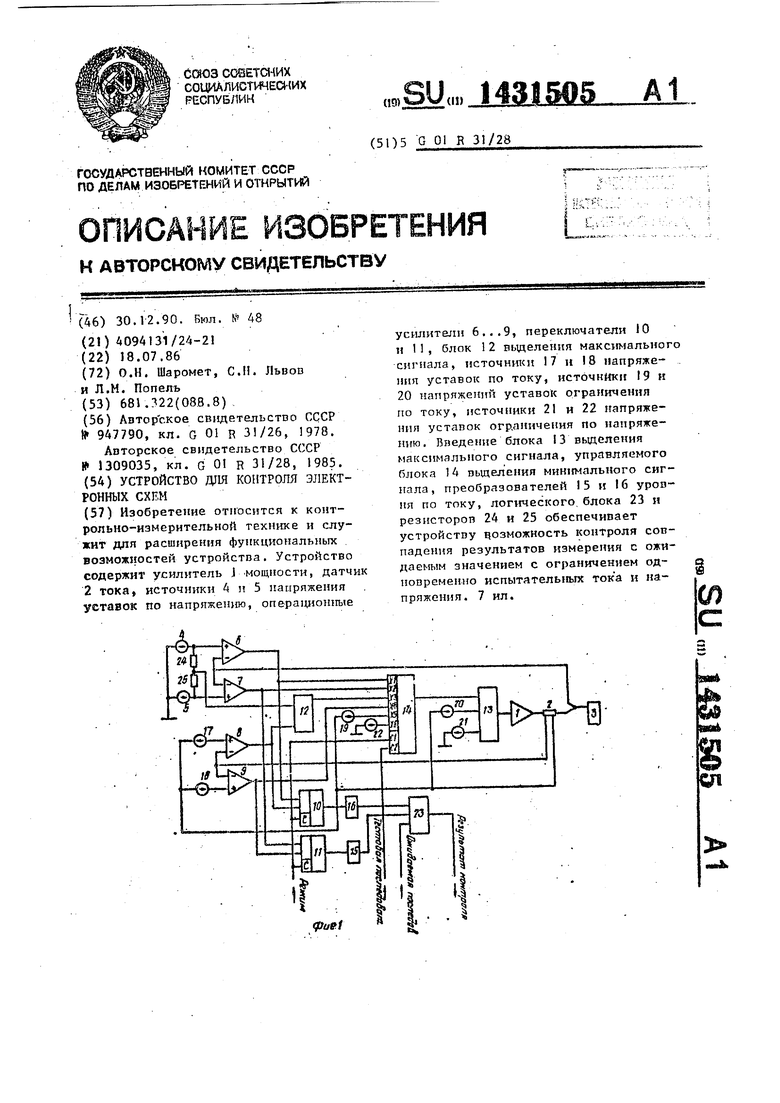

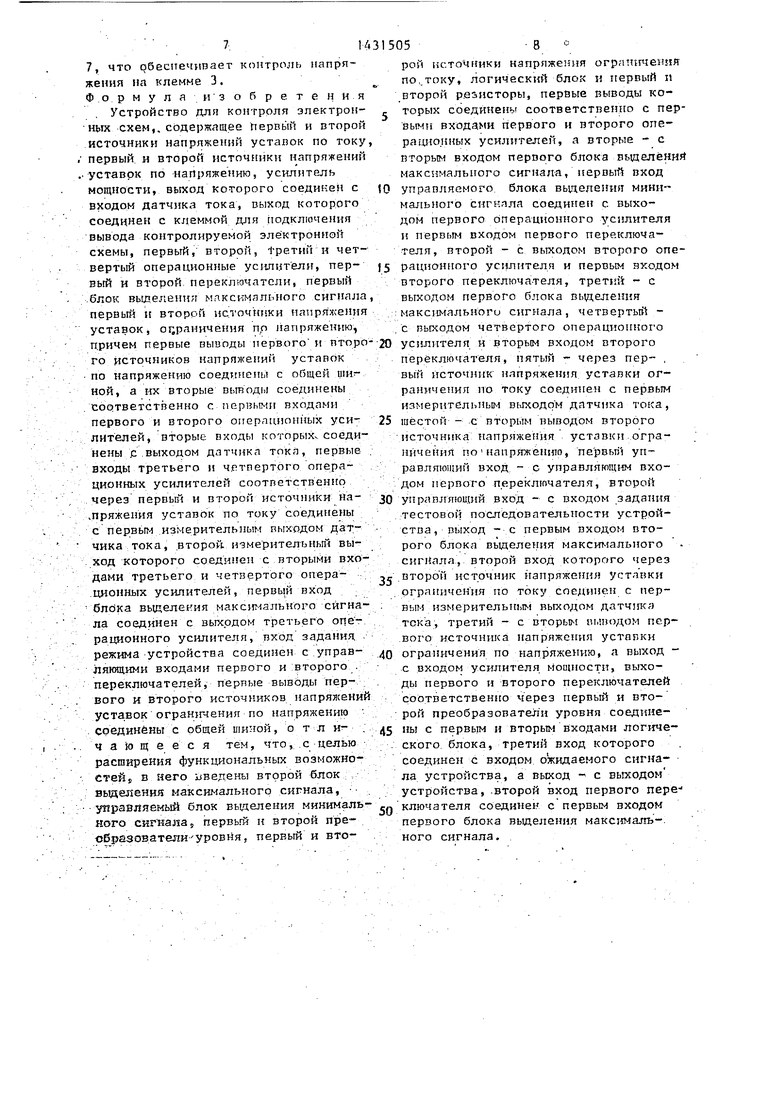

На фиг. I показана общая схема устройства контроля} на фиг. 2 - схе а первого блока вьщеления максималь ного сигнала , на фиг. 3 - схема второго блока -вьщеления максимального сигналаJ на фиг. 4 - схема управляемого блока вьщеления минимального сигнала; на фиг. 5 - схема логического блока; на фиг. 6 и 7 даны вольт-амперные характеристики устройства в режимах подключения соответственно к входам и выходам конт ролнруемой схемы..

Устройство (см. фиг. 1) для конт роля электронных схем содержит усилитель 1 мощности, выход которого соединен с первым входом датчика 2 тока, выход которого соединен с клеммой -) для подключения вьшода контролируемой электронной схемы, источ- 4 и 5 напряжения уставок по напряжению, первый 6, второй 7, третий 8, четвертый 9 операционные усилители, первый 10 и второй П пе- реключатели, первьй 12 и второй 13 . блоки вьщеления максимального сиг- Нала, управляемьй блок 14 вьщеления минимального сигнала, первьй 15 и второй 16 преобразователи уровня по току, первый 17 и второй 18 источники напряжения уставок по току, первый I9 и второй 20 источники напряжения у ставок ограничения по току и первьй 21 и второй 22 источники напряжения уставок ограничения по на- пряжению, логический блок 23, первьй 24 и второй 25 резисторы.

Первый блок 12 вьщеления макси- 1 ального сигнала (фиг. 2) содержит первый 26 и второй 27 транзисторы п - р - п-типа, первьй источник 28 тока.

Второй 13 вьщеления максимального сигнала (фиг. 3) содержит третий 29, четвертьй 30, пятьй 31 транзисторы типа п - р - п, второй источник 32 тока.

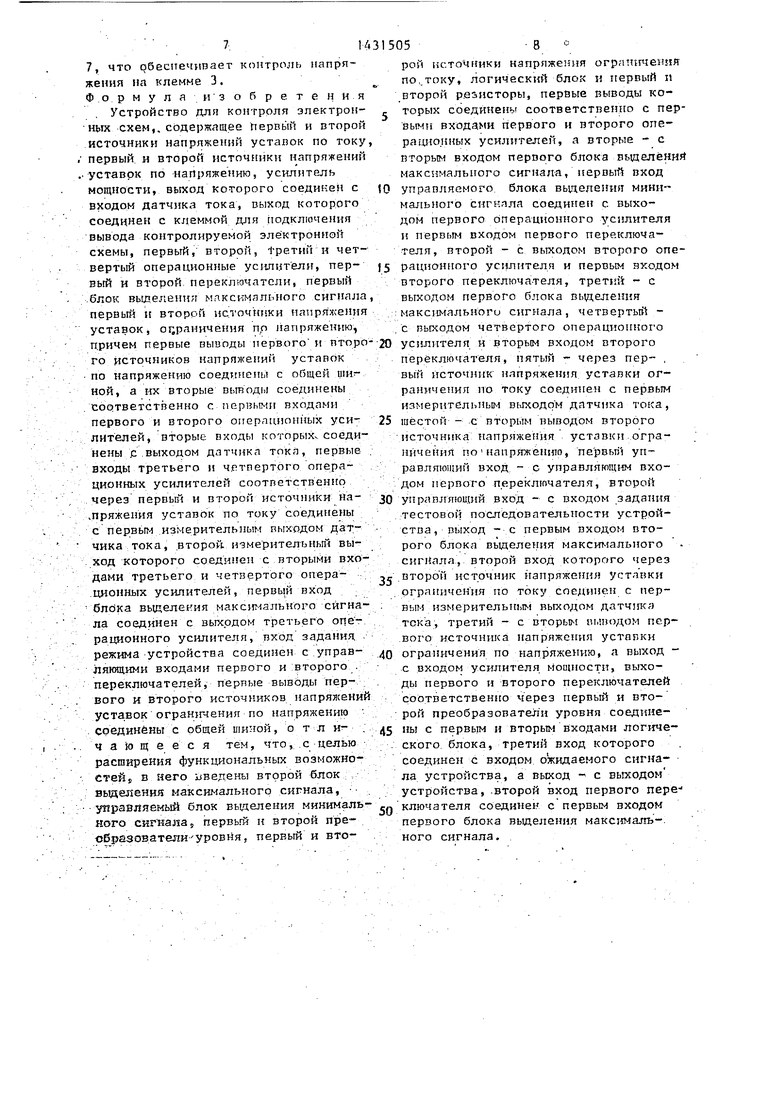

Управляемьй блок 14 вьщеления минимального сигнала (фиг. 4) содержит первьй 33, второй- 34, тий 35, четвертый 36, пятьй 37,

шестой 38 транзисторы р - п - р-ти- па, переключатель 39, источник 40 тока.

Клемма 3 для подключения вывода

10 контролируемой схемы соединена с инвертирующими входами первого 6 и второго 7 операцирнных усилителей, выходы которых соединены соответственно с первыми входами перво15 го 10 и второго И переключателей н с первым и BTopbtM входами управля- емого блока 14 вьщеления Мининаль-. ного сигнала, третий и четвертый выходы которого соединены соответ20 ственно с выходом четвертого операционного усилителя 9 и выходом первого блока 12 вьщеления максимального сигнала, первьй вход которого сое- динен с выходом делителя напряже25

Нин, включенного входами между выводами источников 4 и 5 напряжений уставок по напряжению, второй вход блока 12 выделения максимального сигнала соединен с вторым входом первого переключателя 10 и выходом треть- его операционного усилителя 8. Неинвертирующий вход третьего операционного усилителя 8 соединен с первым вьшодом первого источника 7 напряжения уставки по току, второй вьгоод которого соединен с первьм выводом второго источника 18 напряжения уставки по току и с первым выходом датчика 2 тока, соединенного вторьм ;

выходом с инвертирующими входами

третьего 8 и четвертого 9 операционных усилителей. Неинвертирующий вход четвертого операционного усилителя 9 соединен с вторым вьшодом

второго источника 18 напряжения уставок по току, а выход операционного усилителя 9 соединен с вторым входом - торого переключателя 11, выход второго переключателя 11 соединен с входом первого преобразовате-. ля 15 уровня, соединенного выходом с первым входом логического блока- 23, второй вход которого соединен с выходом второго преобразователя 16

УРОВН., СОеДИНеННОГО входом с ВЫХОДОМ

первого переключателя 10. Входы управления переключателей 10 и И соединены с входом управления режимо Т . устройства и с первым входом управления управляемого блока выделении минимального сигнала, подключенньго nHTbiNJ вxoдo ; к первому вьшоду первого viCTO4HHKa 19 иапряженип уставки ограничения по току, второй вывод которого соединен с первым выходом датчика 2 тока, соединенным также с первым вьгаодом второго источника 20 напряжения уставки ограничения по току, соединенного вторьм выводом с первым входом второго блока 13 вьщеления максимального сигнала. Выход блока 13 соединен с входом усилителя 1 мощности, второй, вход блока 13 соединен с первым источником 21 напряжения уставки ограничении по напряжению, третий вход - с . выходом управляемого блока выделения минимального сигнала, шестой вход которого соединен с первым выводом второго источника 22 напряжения ус- тавки огр.аниченип по шпрпжени1о, соединенного вторым выводом, вместе с вторым выводом первого источника 21 напряжения уставки ограничения по напряжению с общим яыподом контролируемой схемы. Третий вход логического блока 23 соединен с входом ожидаемого сигнала устройстня, а пы- ход - с выходом результата контроля устройства. Второй вход управления управляемого блока пыделе-. ния минимального сигнлла соединен с входом задания уровня выходного сигнала устройства.

В первом блоке 12 выделения максимального сигнала базы транзисторов 26 и 27 соединены с входами управления блока 12, эмиттеры транзисторов 26 и 27 соединены с источнико.м 28 тока, а коллекторы - с тююй литания

Во втором блоке 13 тзыделения максимального сигнала базы транзисторов 29, 30, 31 являются входами блока -13 эмиттеры транзисторов 29, 30 и 31 соединены с выходом источника 32 тока, а-коллекторы этих транзисторов -, с . .шиной питания, jr .. :

В управляемом блоке 14 выделения минимального сигнала базы первого 33 второго 34, третьего 35, четвертого 36, пятого 37 и шестого 38 транзисторов р - п - р-типа соединены соответственно с первым, вторым, третьим четвертым, пятым и шестым входами блока 14, коллекторы транзисторов соединены с шиной питания, эмиттеры первого 33, второго 34 и третьего

35 транзисторов р - п - п-типа соединены с входами переключателя 39, соединенного первым и вторым входа- 5 ми управления соответственно с первым и вторым входами упрарления блока 14. Выход переключателя 39 соединен с выходом источника тока 40, выходом блока 1 и эмиттерами 10 четвертого 36, пятого 37 и шестого 38 транзисторов р п - р-типа. Пер- вьш вход логического блока 23 соединен с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 41 и 42, вторые входы 5 которых соединены соответственно с третьим и четвертым входами блока 23, а их выходы - с первым и вторым входами элемента И 43 соответственно, В1,ход которого соединен с выходом 0 блока 23.

Устройство работает следующим обра 3 ом.

Операционные усилители 6 и 7 усиливают Сигналы разности напряжений 5 на выходах источников 4 и 5 соответственно и на клемме 3, соединенной с контролируемой схемой. Операционные усилители 8 и 9 усиливают разность напряжений на выходах источ- 0 НИКОВ 17 и 18 соответственно и датчика 2 тока.

1 тлписимости от логического сигнала, подаваемого на вход управления режимом, устройство может рабо- 5 тать в двух режимах: задание входного уровня напряжения и контроля уровня входного тока (контроль входа) и задания тока нагрузки и контроля выходного напряжения (контроль 0 выхода).

В первом случае на входы преобразователей 15 и 16 уровня через переключатели 10 и 11 проходят выход- , ные сигналы операционных усилителей 5 8 и 9, гд : они приводятся к нормализованным логическим сигналам, кото- рые передаются далее на входы логи-. ческого блока 23, где логическое состояние на клемме 3 сравнивается П с oжи ;aeмым, задаваемым на третий вход логического блока 23уИ вьшо- дится дале(2 на выход устройства как результат контроля.

Сигнал управления режимом устрой- 5 ства, подаваемьй на первый вход уп- равленля управляемого блока 14 выделения минимального сигнала, в первом случае блокирует сигналы, подаваемые на третий и четвертый вхо

5I

ды блока 14, отключая эмиттеры тран эисторой 35 и 36. В этом режиме в 9авис 1мости от сигнала на втором входе управления блока 14, т.е. на входе переключения задаваемого уровня выходного сигнала устройства, в блоке I4 выходной сигнал первого 6 или втррого 7 операционного усилителя сравниваются с сигналами источников напряжения уставок ограничения по току 19 и по напряжению 22. МинимальнЬ1й и указанных трех сигналов с вьтхода блока 14 посту- : пает на вход второго блока ,13.выделения максимального Сигнала, где сравнивается с сигналами ;источкик6в нап ряжения уставок ограничения по . току.20 и по напряжению 21. j ;

tepы транзисторов 35 и 36, благодаря чему в блок 14 для сравнения по минимальному уровню поступают выходные- сигналы операционного усилителя 9 и блока 13 выделения максимального сигнала. Пока напряжение на клемме 3 для под ключения вьгаода контролируемой схемь меньше уровня, установленного с пс мрвдью делителя напряжения между уровнями и,, и и,-, на выход блока i 2 поступает выходной сигнал операционного усилителя 8 заведомо меньший по, уровню, .чем сигнал на вьгходе one- рационного усилителя 9. Если к тому же этот сигнал меньше уровня U + 4U, и больше уровня и,.- &U,, то на вход усилителя 1 мощности поступит сигнал именно с вькода усилителя 8, благо

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля электронных схем | 1985 |

|

SU1270732A1 |

| Устройство для контроля электронных схем | 1984 |

|

SU1302870A1 |

| Устройство для контроля параметров электронных схем | 1982 |

|

SU1112324A1 |

| Нагрузочное устройство для контроля источников питания | 1987 |

|

SU1430896A1 |

| Устройство для контроля цифровых схем | 1986 |

|

SU1522130A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1619208A1 |

| Устройство для сигнализации | 1988 |

|

SU1644193A1 |

| Устройство для защиты от однофазного замыкания на землю в электрической сети переменного тока | 1983 |

|

SU1171896A1 |

| Электропривод постоянного тока | 1984 |

|

SU1239820A1 |

| Аналого-цифровой интегратор | 1978 |

|

SU805345A1 |

Изобретение относится к контрольно-измерительной технике и служит для расширения функциональных возможностей устройства. Устройство содержит усилитель j .мощности, датчик 2 тока, источники А и 5 напряжения уставок по напряжению, операщюшше ycmiHTEJiH 6...9, переключатели 10 и 11, блок 12 выделения макс1мальиого сигнала, источники 17 и 18 напряже- . нип уставок по току, источники 19 и 20 напряжештй уставок ограничения по току, источники 21 и 22 напряжения уставок ограничения по напряжению . Введение блока I3 выделения максимального сигнала, управляемого блока 14 выделения минимального сигнала, преобразователей 15 и 16 уровня по току, логического, блока 23 и резисторов 24 и 25 обеспечивает устройству возможность контроля совпадения результатов измерения с ожидаемым значением с ограничением одновременно испытательных ток а и напряжения. 7 ил.

Максимальный из этих сигналов про- 20 даря чему в цепи вывода контрол ируходит на вход усилителя 1 мощности и далее Через датчик 2 вьшод контролируемой схемы..

.Если выходные напряжения источников 19 и 22 соответствуют макси- мальньш (с учетрм знака) вьтходному току и напряжению устройства соответственно, а выходные напряжения источников и .21 соответствуют . минимальным (с учетом знака) вых од-. ному току и напряжению устррйства; соответственно,- то выходная вопьт-; амперная характеристика устройства будет соответствовать изображенной на фиг. 6, где. I,, ,- максималь- , но возможный ток устррйства, .знячё- . ние котррогр-задается источником 19J. IP - А IP - минимально, возможней выходной ток устройства, значение ко- торогр задается источником 20. Если дО выходной ток 1 устройства лежит в пределах 1,, - йТ 1 1, +Д1, , то выходное: напряжение устройства под-. . держивается на уровне U или U, .в зависимости от сигнала на входе ожиг дд даемого .сигнала устройства, Однако . в этом режиме напряжение на выходе

устррйства ограничено уровнем Uo -MJo снизу и и, + AU, сверху.в переходных режимах и при неправильном JQ Программировании.

В режиме задания тока нагрузки и контроля выходного напряжения (контроля выхода) прохождение выходных сигналов операционных усили- jj телей 6 7 в .блоке 14 вьщеления ми- нимальнотс сигнала блокируется отключением эмиттеров транзисторов 33 и 34. Вместо этого подключаются эмитемрй схемы будет поддерживаться

... ::-ток- 1о,л. :: . . - . 1л :

: В том случае, Кргда напряжение на выврде Контролируемой схемы больше

25 уровня, задаваемого делителем напряжения, образованным резисторами 24 и 25, например (и + и,.)/2, на выход блока 12 пройдет именно этот уро вень напр . Во всех случаях,

30 когда ток 1ц в цепи вывода к.онтро-лйруемой схемы меньше Тока ту, на . вход усилителя 1 мощности, пройдет тот же сигнал .с выхода делителя, на- пряжения, благодаря чему напряжение на вь1в6де контролируемой схемы бу-.. Дет поддерживаться на уровне, зада- ваемом делителем, с некоторой погреш .ностыь. При увеличении тока I ц До уровня- ;If напряжение на вьтод е опе рационного усилителя 9 уменьшаетсяJ становится меньше напряжения на выходе делителя и йроходит на вход усилителя 1 мощности, благодаря чему в цепи, вывода контролируемой схе- мы устанавливается ток ,, I, .Та- кнм образом, при изменении напряже- ния на вьшоде контролируемой схемы сверх установленных уровней и и происходит переключение тока нагрузки между значениями 1 и I,. Обеспечена также возможность ограничения напряжения на выводе контролируемой схемы уровнями UQ - ЛУо „ и, + fl.Ui . Одновременно в режиме контроля выход.а на первый и второй входы логического блока 23 через преобразователи уровня 15 и 16 и переключатели 10, 1.1 подаются выходные сигналы операционных усилителей 6,

, . дО дд .

емрй схемы будет поддерживаться

... ::-ток- 1о,л. :: . . - . 1л :

: В том случае, Кргда напряжение на выврде Контролируемой схемы больше

25 уровня, задаваемого делителем напряжения, образованным резисторами 24 и 25, например (и + и,.)/2, на выход блока 12 пройдет именно этот уровень напр . Во всех случаях,

30 когда ток 1ц в цепи вывода к.онтро-лйруемой схемы меньше Тока ту, на . вход усилителя 1 мощности, пройдет тот же сигнал .с выхода делителя, на- пряжения, благодаря чему напряжение . на вь1в6де контролируемой схемы бу-.. Дет поддерживаться на уровне, зада- ваемом делителем, с некоторой погреш .ностыь. При увеличении тока I ц До уровня- ;If напряжение на вьтод е операционного усилителя 9 уменьшаетсяJ становится меньше напряжения на выходе делителя и йроходит на вход усилителя 1 мощности, благодаря чему в цепи, вывода контролируемой схе- мы устанавливается ток ,, I, .Та- кнм образом, при изменении напряже- ния на вьшоде контролируемой схемы сверх установленных уровней и и происходит переключение тока нагрузки между значениями 1 и I,. Обеспечена также возможность ограничения напряжения на выводе контролируемой схемы уровнями UQ - ЛУо „ и, + fl.Ui . Одновременно в режиме контроля выход.а на первый и второй . входы логического блока 23 через преобразователи уровня 15 и 16 и переключатели 10, 1.1 подаются выходные сигналы операционных усилителей 6,

7, что обеспечивает контроль напряения на клемме 3.

орм ула и з о б р е т е ния Устройство для контроля электрон- ных схем,, содержащее 11ервый и второй источники напряжений устапок по току, первый и второй источники напряжений уставок по напряжению, усилитель мощности, выход которого соединен с входом датчика тока, выход которого соединен с клеммой для гтодключения вывода контролируемой электронной схемы, первый, второй, Третий и четвертый операционные усилители, первый и второй переключатели, первый блок вьщелент1;г максимального сигнала, первый и второй источники иапряхсеиия уставок, О1;раничения п,о напряжению.

причем первые выводы первого и второ--20 усилителя и вторым входом второго го источников напрпжеииГ) уставок

по напряжению соединены с общей шиной, а их вторые выводы соединены соответст1зенно с первыми входами первого и второго операцион11ых уси- 25 , лит елей, вторые входы которых-., соединены с .выходом датчика тока, первые . входы третьего и четвертого операционных усилителей соответственно через первьй и второй источники на- jO

пряжения уставок по току соединены с первым .измерительпь ; выходом дат,- . чика тока, второй измерительньй выход которого соединен с вторыми входами третьего и четвертого операционных усилителей, первый вход

блбка вьщеленип макси 1ального сигна ла соединен с выходом третьего операционного усилителя, вход задания режима-устройства соединен с управляющими входами первого и :второго . переключателей, первые выводы пер-. : . вого и второго источников напряжений . уставок ограН1гчения по напряжению . соединены с общей шизюй, о т л и- . .45 чающееся тем, что, с целью расширения функциональных возможностей,, в него введены второй блок, выделения максимального сигнала, .

35

40

переключателя, пятый - через первый Источник напряжения уставки ог раничения по току соединен с первы измерительным выходом датчика тока шестой - с вторым выводом второго источника напряжения уставки огра ничения по напряжению, пе рвы)) управляющий вход - с управляющим вхо дом первого переключателя, второй управляющий вход - с входом задани тестовой последовательности устрой ства, выход - с первым входом второго блока выделения максиьшльиого сигнала, второй вход которого чере .второй источник напряжении уставки ограничения по току соединен с пер вым измерительным выходом датчика тока, третий - с вторым 11||П)одом пе вого источника напряжения уставки ограничения по напряжению, а выход с входом усилителя Мощности, выходы первого и второго переключателе соответственно через первый и второй преобразователи уровня соедине ны с nepBbiM и вторым входами логич ского блока. Третий вход которого соединен с входом ожидаемого сигнала устройства, а выход - с выходом устройства, .второй вход нервого пер

управляемый блок выделения минималь- д ключателя соединен с первым входом кого сигналаS первый и второй пре- первого блока выделения максималь-. сбразователи-уровня, первый и вто- ного сигнала.

рой источники напряжения огратпменля по ..току, логический блок и ггервыЙ п второй р.езисторы, первые выводы ко- торых соединены соответственно с первыми входами первого и второго опе- рагдаонных усилителей, а вторые - с вторым входом первого блока вьщелени максимального сигнала, первый вход

управляемого блока вьделения минимального сигнала соединен с выходом первого операционного усилителя и первьп-1 входом первого переключателя, второй - с выходом второго операционного усилителя и первым нходом

второго переключа.теля, третий - с

выходом первого блока вьиеления

:максимального сигнала, четвертьй , с пьскодом четвертого операционного

0 усилителя и вторым входом второго

5 O

.

5

5

0

переключателя, пятый - через первый Источник напряжения уставки ограничения по току соединен с первым измерительным выходом датчика тока, шестой - с вторым выводом второго источника напряжения уставки ограничения по напряжению, пе рвы)) управляющий вход - с управляющим входом первого переключателя, второй управляющий вход - с входом задания тестовой последовательности устройства, выход - с первым входом второго блока выделения максиьшльиого сигнала, второй вход которого через .второй источник напряжении уставки ограничения по току соединен с первым измерительным выходом датчика тока, третий - с вторым 11||П)одом первого источника напряжения уставки ограничения по напряжению, а выход - с входом усилителя Мощности, выходы первого и второго переключателей соответственно через первый и вто рой преобразователи уровня соединены с nepBbiM и вторым входами логического блока. Третий вход которого соединен с входом ожидаемого сигнала устройства, а выход - с выходом устройства, .второй вход нервого пере77

S

JB

ue.2

n

ffuf.3

ЗД

35

Ъб

37

-38

39

V

C1 C2

40

ФиеЛ

фиа.б

и, ft/t

Г uV

Редактор г4 Мозжечкова

фиг.7 .

Составитель В. Савинов Техред м.Моргентал

2

Ue

.It

««.«.«.-. /

Корректор И. Муска

| Устройство для контроля электрических параметров электронных схем | 1978 |

|

SU947790A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для моделирования процесса обслуживания заявок | 1985 |

|

SU1309035A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1990-12-30—Публикация

1986-07-18—Подача