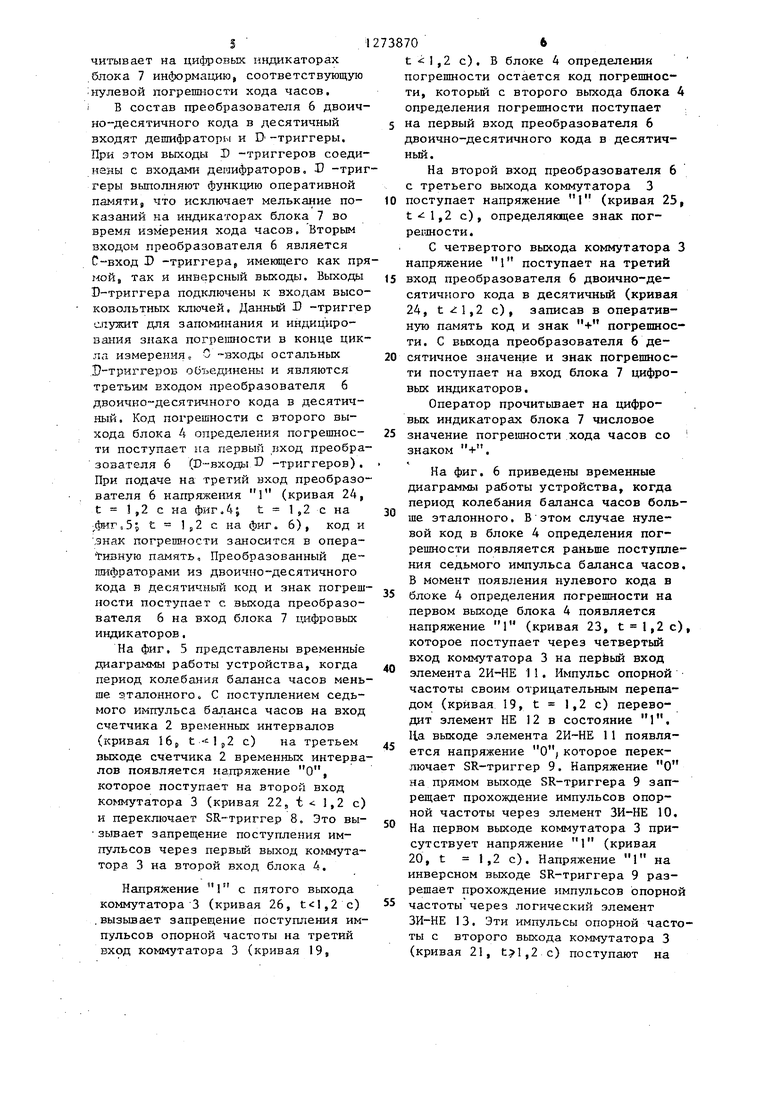

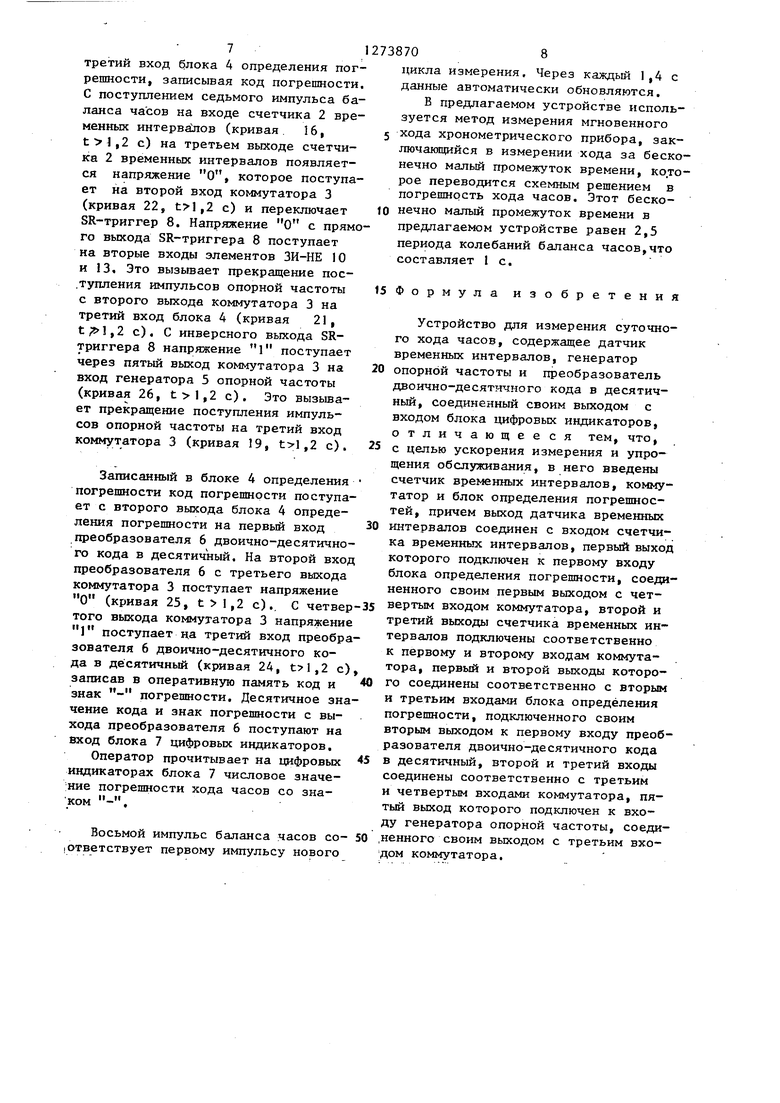

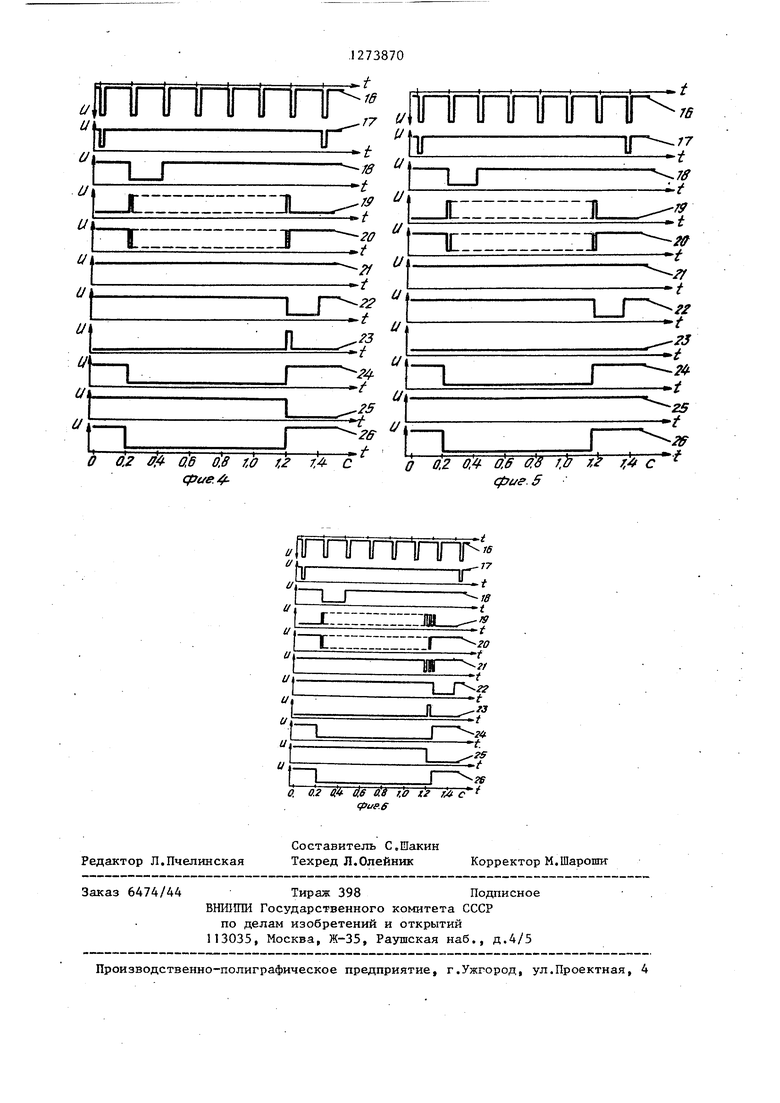

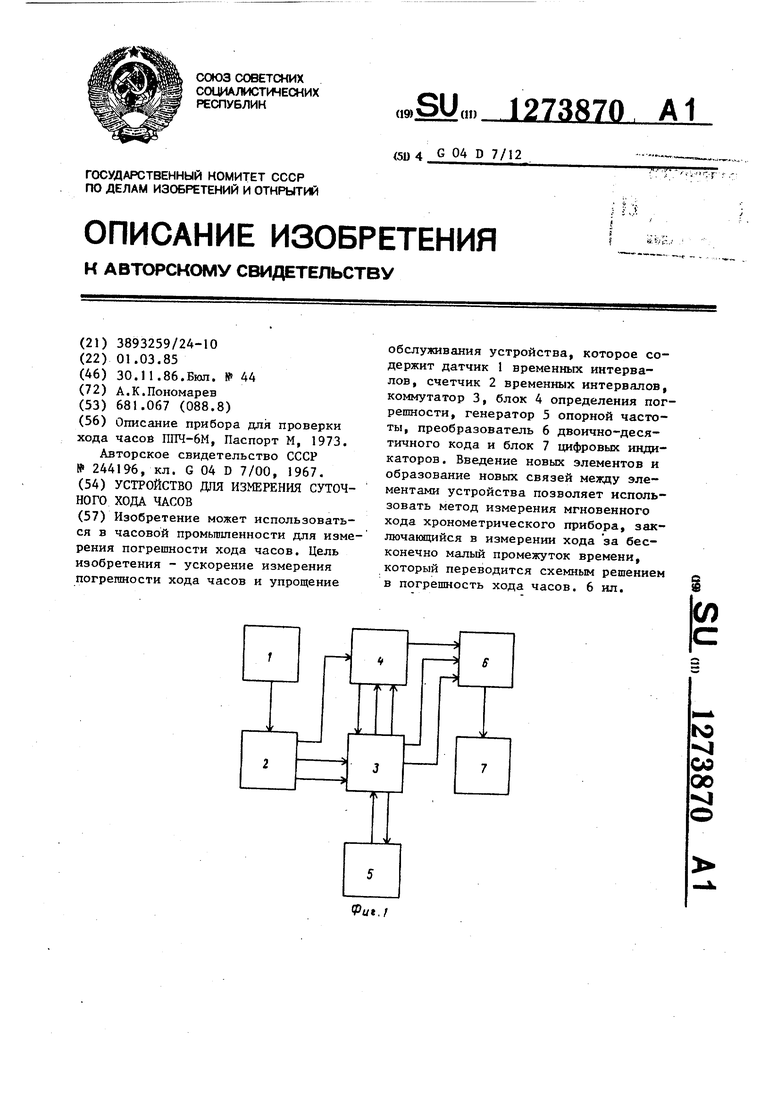

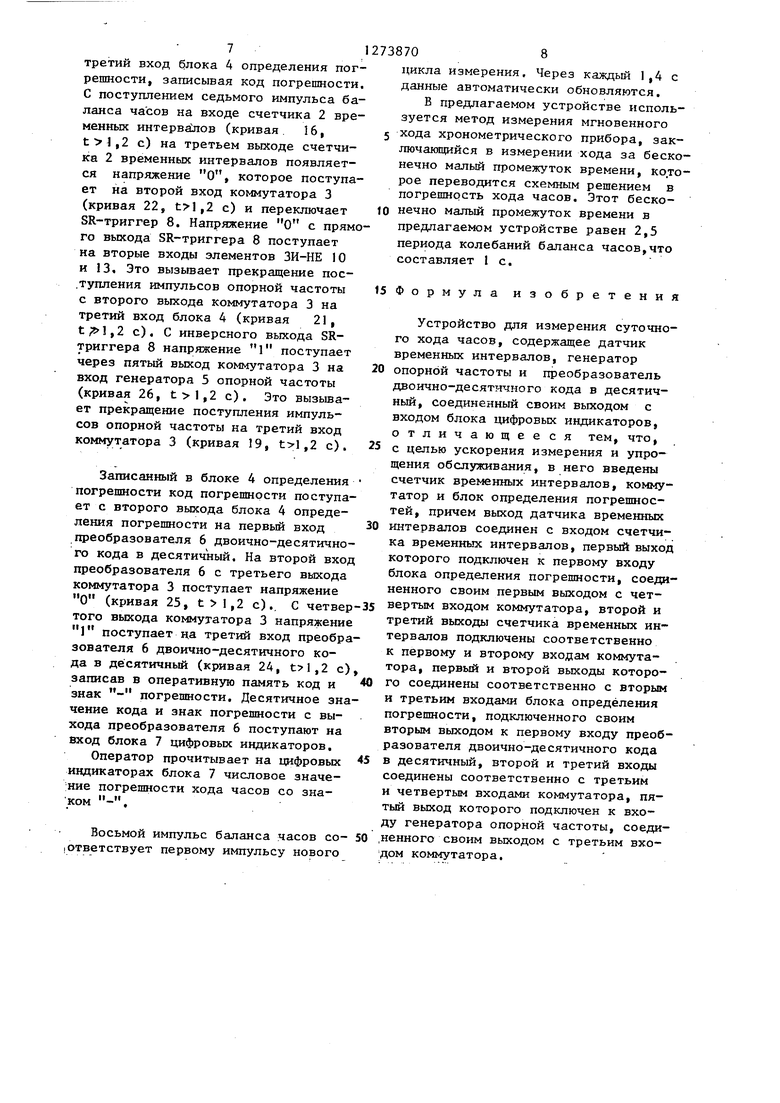

Изобретение относится к приборостроению и может быть использовано в часовой промьшшенности и в ремонтных часовых мастерских для измерения погрешности хода часов. Цель изобретения - ускорение измерения погрешности хода часов и упрощение обслуживания устройства. На фиг. 1 представлена блок-схема устройства; на фиг.2 - принципиальная схема коммутатора; на фиг, 3 - схема счетчика временных интервалов; на фиг о 4 - 6 - временные диаграммы иллюстрирукнцие работу устройства при частоте колебаний баланса измеряемых часов, равной эталонной частоте, а также меньшей или большей эталонной частоты соответственно „ Устройство содержит датчик 1 временных интервалов, счетчик 2 временных интервалов с элементом 15, коммутатор 3, блок 4 определения погрешности j, генератор 5 опорной частоты, преобразователь 6 двоично-десятичного кода в десятичный и блок 7 цифровых индикаторов. ( Коммутатор состоит из SR-триггеров 8 и 9, элемента ЗИ-НЕ 10, элемента 2И-НЕ 115 элемента НЕ 12, -элемента ЗИ-НЕ 13 и линии 14 задержки. Вькод датчика 1 временньЕХ интервалов соединен с входом счетчика 2 временных интервалов. Первый выход счетчика 2 временных интервалов подключен к первому входу блока 4 определения погрешности, второй выход - к первому входу коммутатора 3, третий выход - к второму входу коммутатора 3, первый выход которого соединен с вто рым входом блока 4 определения погрешности, второй выход - с третьим входом блока 4 определения погрешности, первым выходом подключенного к четвертому входу коммутатора 3. генератора 5 опорной частоты соединен с третьим входом коммутатора 3, а второй выход блока 4 определения погрешности подключен к первому входу преобразователя 6 двоичнодесятичного кода в десятичный.Выход преобразователя 6 соединен с входом .блока цифровых индикаторов. Третий выход коммутатора 3 подключен к второму входу преобразователя 6, четвер тый выход коммутатора 3 - ..третьему входу преобразо.вателя 6, Пятый выход коммутатора 3 подключен к входу ге702ератора 5 опорной частоты. Прямой выход SR-триггера 8 соединен с вторым входом элемента ЗИ-НЕ 10 и вторым входом элемента ЗИ-НЕ 13. Инверсньй выход SR-триггера 8 соединен с входом линии 14 задержки, а прямой выход SR-триггера 9 подключен к первому входу элемента ЗИ-НЕ 10. Инверсньй выход SR-триггера 9 соедииен с третьим входом элемента ЗИ-НЕ 13, а выход элемента 2И-НЕ 11 подключен к R-входу SR-триггера 9. Выход элемента НЕ 12 соединен с вторым входом элемента 2И-НЕ 11, а S-вход SR-триггера 8 подключен к Б-входу SR-триггера 9 и является первым входом коммутатора 3, R-вход SR-триггера 8 является вторым входом коммутатора 3, а инверсный выход SR-триггера 8 является пятым выходом . коммутатора 3. Третий вход элемента ЗИ-НЕ 10 соединен с первым входом элемента ЗИ-НЕ 13 и входом элемента НЕ 12 и является третьим входом коммутатора 3. Первьм вход элемента 2И-НЕ 11 является четвертым входом коммутатора 3, выход элемента ЗИ-НЕ 10 - первым выходом коммутатора 3, выход элемента ЗИ-НЕ 13 - вторым выходом коммутатора 3, прямой выход SR-триггера 9 - третьим выхрдом коммутатора 3, выход линии 14 задержки - четвертым выходом коммутатора 3, Устройство работает следукяцим образом. При частоте колебаний баланса, равной эталонной (фиг.4) первый выделенный импульс баланса часов с выхода датчика 1 временных интервалов (от часов, положенных на датчик 1) поступает на вход счетчика 2 временных интервалов (кривая 1, t 0), а с первого выхода счетчика 2 врем.енных интервалов напряжение О поступает на первый вход блока 4 определения погрешности (кривая 17, t 0), записывая в него значения двоично-десятичного кода интервала эталонного времени. Этот код равен 86400 (1000 ОНО 0100 0000 0000) и представляет собой число секунд в сутках. Значение его по времени равно интервалу между вторым и седьмым импульсами баланса часов (фиг.4). Второй выделенный импульс баланса часов, поступивший на вход счетчика 2 временных интервалов (кривая 16, t 0,2 с) поступает с второго выхода счетчика 2 временных интервалов в виде напряжения О на первый вход коммутатора 3 (кривая 18, t 0,2 с) и переключает SR-тригге ры 8 и 9. При этом напряжение 1 с прямого выхода SR-триггера 8 поступает на вторые входы элементов ЗИ-НЕ 10 и 13, а напряжение 1 с прямого выхода SR-триггера 9 поступает на первый вход элемента ЗИ-НЕ 10. С инверсного выхода SR-триггера 9 напряжение О поступает на третий вход элемента ЗИ-НЕ 13, ас инверсного выхода RS-триггера 8 (пятый выход коммутатора 3) на вход генератора 5 опорной частоты поступает напряжение О (кривая 26, t 0,2 с), включив генератор 5. Гейератор 5 опорной частоты сос тоит из задающего генератора, частота которого стабилизирована кварцевым резонатором и делителя частоты. Задающий генератор генерирует импульсы с частотой повторения 8640 кГц, Для того, чтобы на выходе генератора 5 опорной частоты получить частоту 86,4 кГц, т,е. 86400 колебаний за 1 с интервала эталонно го времени, импульсы с выхода задаю щего генератора поступают на вход делителя частоты, состоящего из дву соединенных последовательно двоично-десятичных счетчиков с общим коэффициентом деления К 100, При этом выход старшего счетчика являет ся выходом генератора 5 опорной час тоты. Частота колебаний генератора 5 .опорной частоты выбрана такой, что цена деления младшего разряда счетчиков соответствует 1 с погрешности хода часов. Второй вход блока 4 определения погрешности является вычи тазащцм входом счетчика, а третий вход блока 4 определения погрешности - входом прямого счета. Последовательность импульсов час тотой 86400 Гц (кривая 19, t 0,2 с поступает с выхода генератора 5 опо ной частоты на третий вход элемента ЗИ-НЕ 10 и первый вход элемента ЗИ-НЕ 13 (на третий вход коммутатора 3), Эти импульсы через третий вход и выход элемента ЗИ-НЕ 10 поступают с первого выхода коммутато-i ра 3 на второй вход блока 4 определения погрепшости (кривая 20, от 04 t 0,2cдot l,2c). В блоке 4 определения погрешности начинается уменьшение (вычитание) записанного кода эталонного времени, которое стремится к нулю. На выходе элемента ЗН-НЕ 13 присутствует напряжение 1 (кривая 21),так как на первый вход элемента ЗИ-НЕ 13 поступает О. С поступлением седьмого импульса баланса часов на вход счетчика 2 временных интервалов (кривая 16,t 1,2 с) на третьем выходе счетчика 2 временных интервалов появится напряжение О, которое поступает на второй вход коммутатора 3 (кривая 22, t 1,2 с) и переключает SR-триггер 8. С прямого выхода SRтриггера 8 напряжение О поступит на второй вход элемента ЗИ-НЕ 10 и второй вход элемента ЗИ-НЕ 13, Напряжение I с инверсного выхода SR-триггера 8 поступает через пятый выход коммутатора 3 на вход генератора 5 опорной частоты и запрещает поступление импульсов опорной частоты на третий вход коммутатора 3 (t 1,2 с, кривые 26 и 19), Отключение генератора 5 опорной частоты происходит в момент, когда в блоке 4 определения погрешности остается код нулевой погрешности. Напряжение 1 с первого входа блока 4 определения погрешности поступает на четвертый вход коммутатора 3 (кривая 23, t 1,2 с), это вызывает переключение SR-триггера 9, так как в этот момент времени на выходе элемента НЕ 12 присутствует напряжение Напряжение О с прямого выхода SR-триггера 9 поступает через третий выход коммутатора 3 на второй вход преобразователя 6 (кривая 25, t 1,2 с). Код ± нулевой погрешности с второго выхода блока 4 определения погрешности поступает на первый вход преобразователя 6 двоично-десятичного кода в десятичный, а с четвертого выхода коммутатора 3 (выход линии 14 задержки) напряжение 1 поступает на третий вход преобразователя 6 (кривая 24, t 1,2 с), занеся в опеативную память код ± нулевой погешности. Этот код, преобразованный в десяичное значение, поступает с выхоа преобразователя 6 на вход блока цифровых индикаторов. Оператор проs , читывает на цифровых индикаторах блока 7 информацию, соответствующую :нулевой погрешности хода часов, i В состав преобразователя 6 двоично-десятичного кода в десятичный входят дешифраторы и D-триггеры. При этом выходы I) -триггеров соединены с входами дешифраторов, D -триг геры выполняют функцию оперативной памяти, что исключает мелькание показаний на индикаторах блока 7 во время измерения хода часов. Вторьм входом преобразователя 6 является С-вход D -триггера5 имеющего как пря мой, так и инверсный выходы. Выходы D-триггера подключены к входам высоковольтных ключей. Данный В -триггер спужит для запоминания и индицирования знака погрешности в конце цик ла измерения с О -входы остальных 1 -триггерОБ объединены и являются третьим входом преобразователя 6 двоично-десятичного кода в десятичный. Код погрешности с второго выхода блока 4 определения погрешности поступает на первый ,вход преобра зозателя 6 (Г-входы D -триггеров). При подаче на третий вход преобразо вателя 6 напряжения 1 (кривая 24, t 1,2 с на фиг.4; t 1,2 с на &1И.г,5у t ,2 с на фиг 6), код и знак погрепзности заносится в опера ивную паг-1ять. Преобразованный дешифраторами из двоично-десятичного кода в десятичный код и знак погреш ности поступает с выхода преобразователя 6 на вход блока 7 цифровых индикаторов. На фиг. 5 представлены временные диаграммы работы устройства, когда период колебания баланса часов мень ше эталонного. С поступлением седьмого импульса баланса часов на вход счетчика 2 временных интервалов (кривая 16j t -15,2 с) на третьем выходе счетчика 2 временных интерва лов появляется напрял ение О, которое поступает на второй вход коммутатора 3 (кривая 22, t 1,2 с) и переключает SR-триггер 8. Это вызывает запрещение поступления импульсов через первый выход коммутатора 3 на второй вход блока 4. Напряжение 1 с пятого выхода коммутатора 3 (кривая 26, ,2 с) .вызьшает запрещение поступления импульсов опорной частоты на третий вход коммутатора 3 (кривая 19, 706 t 1,2 с). В блоке 4 определения погрешности остается код погрешности, которьм с второго вьпсода блока 4 определения погрешности поступает на первый вход преобразователя 6 двоично-десятичного кода в десятичный. На второй вход преобразователя 6 с третьего выхода коммутатора 3 поступает напряжение 1 (кривая 25, t«il,2 с), определяющее знак погрегшости. С четвертого выхода коммутатора 3 напряжение 1 поступает на третий вход преобразователя 6 двоично-десятичного кода в десятичный (кривая 24, t 1,2 с), записав в оперативную память код и знак + погрешности. С выхода преобразователя 6 десятичное значение и знак погрешности поступает на вход блока 7 цифровых индикаторов. Оператор прочитьшает на цифровых индикаторах блока 7 числовое значение погрешности хода часов со знаком +. На фиг. 6 приведены временные диаграммы работы устройства, когда период колебания баланса часов больше эталонного. В этом случае нулевой код в блоке 4 определения погрешности появляется раньше поступления седьмого импульса баланса часов. В момент появления нулевого кода в блоке 4 определения погрешности на первом выходе блока 4 появляется напряжение 1 (кривая 23, t 1,2 с), которое поступает через четвертый вход коммутатора 3 на перйый вход элемента 2И-НЕ 11. Импульс опорной частоты своим отрицательным перепадом (кривая 19, t 1,2 с) переводит элемент НЕ 12 в состояние 1. Ца выходе элемента 2И-НЕ 11 появляется напряжение О) которое переключает SR-триггер 9. Напряжение О на прямом выходе SR-триггера 9 запрещает прохождение импульсов опорной частоты через элемент ЗИ-НЕ 10. На первом выходе коммутатора 3 присутствует напряжение 1 (кривая 20, t 1,2 с). Напряжение 1 на инверсном выходе SR-триггера 9 разрешает прохождение импульсов опорной частоты через логический элемент ЗИ-НЕ 13. Эти импульсы опорной частоты с второго выхода коммутатора 3 (кривая 21, ,2 с) поступают на третий вход блока А определения погрешности, записывая код погрешности С поступлением седьмого импульса баланса часов на входе счетчика 2 временных интерва:Лов (кривая. 16, ,2 с) на третьем выходе счетчика 2 временных интервалов появляется напряжение О, которое поступает на второй вход коммутатора 3 (кривая 22, ,2 с) и переключает SR-триггер 8. Напряжение О с прямо го выхода SR-триггера 8 поступает на вторые входы элементов ЗИ-НЕ 10 и 13, Это вызывает прекращение пос.тупления импульсов опорной частоты с второго выхода коммутатора 3 на третий вход блока 4 (кривая 21, t,2 с). С инверсного выхода SRтриггера 8 напряжение 1 поступает через пятый выход коммутатора 3 на вход генератора 5 опорной частоты (кривая 26, ,2 с). Это вызьшает прекращение поступления импульсов опорной частоты на третий вход коммутатора 3 (кривая 19, ,2 с). Записанный в блоке 4 определения погрешности код погрешности поступает с второго выхода блока 4 определения погрешности на первый вход преобразователя 6 двоично-десятичного кода в десятичный. На второй вход преобразователя 6 с третьего выхода коммутатора 3 поступает напряжение 0 (кривая 25, t 1,2 с),, С четвер того выхода коммутатора 3 напряжение 1 поступает на третий вход преобра зователя 6 двоично-десятичного кода в десятичный (кривая 24, ,2 с) записав в оперативную память код и знак - погрешности. Десятичное зна чение кода и знак погрешности с выхода преобразователя 6 поступают на вход блока 7 цифровых индикаторов. Оператор прочитывает на цифровых индикаторах блока 7 числовое значение погрешности хода часов со знаком -. Восьмой импульс баланса часов со Ответствует первому импульсу нового

дом коммутатора. цикла измерения. Через каждый 1,4 с данные автоматически обновляются, В предлагаемом устройстве используется метод измерения мгновенного хода хронометрического прибора, заключакшщйся в измерении хода за бесконечно малый промежуток времени, которое переводится схемным решением в погрешность хода часов. Этот бесконечно малый промежуток времени в предлагаемом устройстве равен 2,5 периода колебаний баланса часов,что составляет 1 с, Формула изобретения Устройство для измерения суточного хода часов, содержащее датчик временных интервалов, генератор опорной частоты и преобразователь двоично-десятичного кода в десятичный, соединенный своим выходом с входом блока цифровых индикаторов, отличающееся тем, что, с целью ускорения измерения и упрощения обслуживания, в него введены счетчик временных интервалов, коммутатор и блок определения погрешностей, причем выход датчика временных интервалов соединен с входом счетчика временных интервалов, первый выход которого подключен к первому входу блока определения погрешности, соединенного своим первым выходом с четвертым входом коммутатора, второй и третий выходы счетчика временных интервалов подключены соответственно к первому и второму входам коммутатора, первый и второй выходы которого соединены соответственно с вторым и третьим входами блока определения погрешности, подключенного своим вторым выходом к первому входу преобразователя двоично-десятичного кода в десятичный, второй и третий входы соединены соответственно с третьим и четвертым входами коммутатора, пятый выход которого подключен к входу генератора опорной частоты, соединенного своим выходом с третьим вхо

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения суточного хода часов | 1987 |

|

SU1508097A1 |

| Устройство для определения мгновенного суточного хода механических часов | 1987 |

|

SU1509824A1 |

| Устройство для определения содержания связующего в стеклопластиках | 1984 |

|

SU1265538A1 |

| Устройство для измерения суточного хода часов | 1988 |

|

SU1613998A1 |

| ОПЕРАТИВНЫЙ КОНТРОЛЛЕР СУММАРНОЙ МОЩНОСТИ НАГРУЗКИ ГРУППЫ ЭНЕРГОПОТРЕБИТЕЛЕЙ | 1998 |

|

RU2145717C1 |

| Малогабаритный цифровой твердомер | 1984 |

|

SU1359716A1 |

| Анализатор гистограммы отклонений напряжения | 1982 |

|

SU1104530A1 |

| Преобразователь активной мощности трехфазной электрической цепи в цифровой код | 1987 |

|

SU1597759A1 |

| Цифровой измеритель температуры | 1982 |

|

SU1111038A1 |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

Изобретение может использоваться в часовой промьгошенности для измерения погрешности хода часов. Цель изобретения - ускорение измерения погрешности хода часов и упрощение обслуживания устройства, которое содержит датчик 1 временных интервалов, счетчик 2 временных интервалов, коммутатор 3, блок 4 определения погрешности, генератор 5 опорной частоты, преобразователь 6 двоично-десятичного кода и блок 7 цифровых индикаторов . Введение новых элементов и образование новых связей между элементами устройства позволяет использовать метод измерения мгновенного хода хронометрического прибора, заключающийся в измерении хода за бесконечно малый промежуток времени, который переводится схемным решением в погрешность хода часов. 6 ил. to О9 00

i/e.S

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| УСТРОЙСТВО для ОПРЕДЕЛЕНИЯ СУТОЧНОГО ХОДА ЧАСОВ | 0 |

|

SU244196A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-11-30—Публикация

1985-03-01—Подача